Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### ADBM-A350

## **Optical Finger Navigation**

## **Data Sheet**

### **Description**

The ADBM-A350 sensor is a small form factor (SFF) optical finger navigation system.

The ADBM-A350 is a low- power optical finger navigation sensor. It has a new, low-power architecture and automatic power management modes, making it ideal for battery-and power-sensitive applications such as mobile phones.

The ADBM-A350 is capable of high-speed motion detection – up to 20ips. In addition, it has an on-chip oscillator and integrated LED for optical navigation to minimize external components.

There are no moving parts, thus provide high reliability and less maintenance for the end user. In addition, precision optical alignment is not required, facilitating high volume assembly.

The sensor is programmed via registers through either a serial peripheral interface or a two wire interface port. It is packaged into a 17-pin FPC module for ease of assembly via ZIF connector.

### **Theory of Operation**

The ADBM-A350 is based on Optical Finger Navigation (OFN) Technology, which measures changes in position by optically acquiring sequential surface images (frames) and mathematically determining the direction and magnitude of movement.

The ADBM-A350 contains an Image Acquisition System (IAS), a Digital Signal Processor (DSP), and a communication system.

The IAS acquires microscopic surface images via the lens and illumination system. These images are processed by the DSP to determine the direction and distance of motion. The DSP calculates the  $\Delta x$  and  $\Delta y$  relative displacement values.

The host reads the  $\Delta x$  and  $\Delta y$  information from the sensor serial port if a motion interrupt is published. The microcontroller then translates the data into cursor navigation, rocker switch, scrolling or other system dependent navigation data.

#### **Features**

- Low power architecture

- Self-adjusting power-saving modes for longer battery life

- High speed motion detection up to 20ips

- Self-adjusting frame rate for optimum performance

- Motion detect interrupt

- Finger detect interrupt

- Soft click and Tap detect interrupt

- Single Interrupt pin

- Optional PWM output to control LED driver to enable illumination feature when finger is on the sensor

- Optional switch input for center click function

- Internal oscillator no clock input needed

- Selectable 125, 250, 500, 750, 1000 and 1250 cpi resolution

- Single 1.8V supply voltage for analog and digital

- Internal power up reset (POR)

- Selectable Input/Output voltage at 1.8V or 2.8V nominal

- 4-wire Serial peripheral interface (SPI) or Two wire interface (TWI)

- Integrated chip-on-board LED with wavelength of 870nm

- 17-pin FPC module

### **Applications**

- Finger input devices

- Mobile devices

- Integrated input devices

- Battery-powered input device

Avago customers purchasing the ADBM-350 OFN product are eligible to receive a royalty free license to our US patents 6977645, 6621483, 6950094, 6172354 and 7289649, for use in their end products.

**CAUTION:** It is advised that normal static precautions be taken in handling and assembly of this component to prevent damage and/or degradation which may be induced by ESD.

## Pinout of ADBM-A350 Optical Sensor

| Pin | Name        | Description                               | Input/Output pin                                 | Function                                                                                                                  |

|-----|-------------|-------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| 1   | GND_SHIELD  | Ground shield                             |                                                  |                                                                                                                           |

| 2   | GPIO        | General Purpose<br>Input/ Output pin      | I (Schmitt trigger input)/<br>O (CMOS output)    | Pin can be used for FPD output, PWM output or Dome/Button click input. If configure as input do not leave pin unconnected |

| 3   | GND         | Ground                                    |                                                  |                                                                                                                           |

| 4   | IO_NCS_A1   | TWI address set<br>or Chip Select         | I (Schmitt trigger input)                        | SPI : NCS (chip select) active low signal<br>TWI Address Select, A1<br>Do no leave pin unconnected                        |

| 5   | IO_MISO_SDA | TWI serial data<br>or Master In Slave Out | In SPI – CMOS output. In<br>TWI – open drain I/O | SPI : MISO (Master Input Slave Out) signal<br>TWI : serial data signal                                                    |

| 6   | IO_MOSI_A0  | TWI address set<br>or Master Out Slave In | I (Schmitt trigger input)                        | SPI : MOSI (Master Out Slave In) signal<br>TWI Address Select, A0<br>Do no leave pin unconnected                          |

| 7   | IO_CLK      | Serial clock input                        | I (Schmitt trigger input)                        | Serial clock signal                                                                                                       |

| 8   | NRST        | Hardware Chip Reset                       | I (Schmitt trigger input)                        | Set to high when not used<br>Active low signal                                                                            |

| 9   | DOME-       | Dome -                                    |                                                  |                                                                                                                           |

| 10  | EVENT_INT   | Event Interrupt<br>(active low output)    | O (CMOS output)                                  | Open when not used Default active low signal, can be changed in Event control register 0x1d                               |

| 11  | SHTDWN      | Shutdown<br>(active high input)           | I (Schmitt trigger input)                        | Set to low when not used<br>Active high signal                                                                            |

| 12  | NC          | No Connect                                |                                                  | No connection                                                                                                             |

| 13  | VDD         | Voltage supply                            |                                                  | Supply 1.8V                                                                                                               |

| 14  | DOME+       | Dome +                                    |                                                  |                                                                                                                           |

| 15  | IO_SELECT   | SPI / TWI Select                          | I (Schmitt trigger input)                        | TWI : GND or SPI : High                                                                                                   |

| 16  | VDDIO       | Voltage supply<br>for Input/ Output       |                                                  | Supply 1.8V or 2.8V                                                                                                       |

| 17  | NC          | No Connect                                |                                                  | No connection                                                                                                             |

Note:

<sup>1.</sup> NC pins can be tied to VDD, GND or left open/ unconnected.

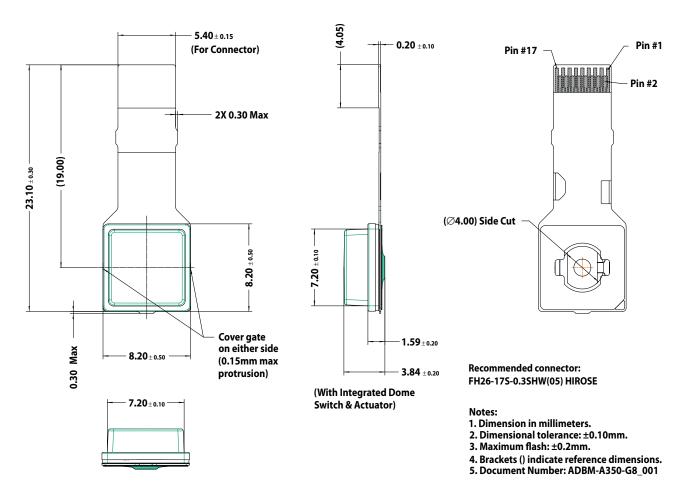

Figure 1. Package outline drawing

Note: Dome + must be connected to MCU to detect button change state and Dome - can be connected to GND.

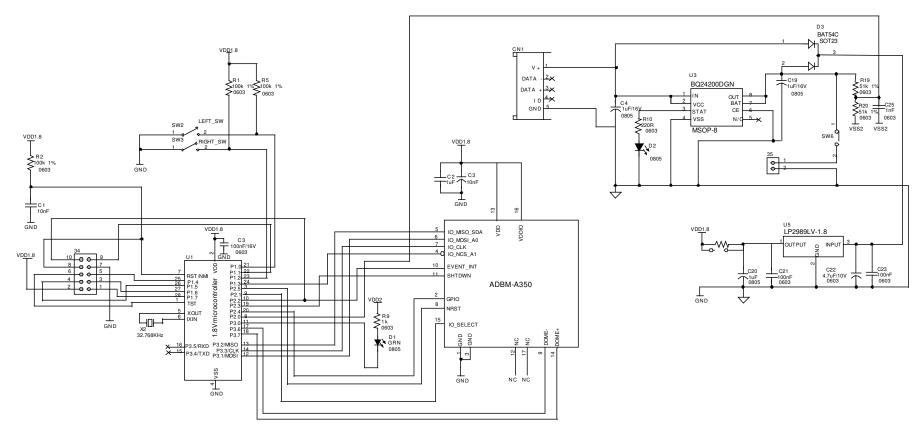

Figure 2. Schematic diagram for interface between ADBM-A350 and 1.8V microcontroller via SPI

### **Regulatory Requirements**

- Passes FCC or CISPR 22 Class B emission limits when assembled following Avago Technologies recommendations.

- Passes IEC 61000-4-3 and IEC61000-4-6 Class A Immunity limits when assembled following Avago Technologies recommendations.

### **Absolute Maximum Ratings**

| Parameter                         | Symbol            | Minimum | Maximum                | Units | Notes                                       |

|-----------------------------------|-------------------|---------|------------------------|-------|---------------------------------------------|

| Storage Temperature               | T <sub>S</sub>    | -40     | 85                     | °C    |                                             |

| Analog and Digital Supply Voltage | VDD               | -0.5    | 2.1                    | V     |                                             |

| I/O Supply Voltage                | V <sub>DDIO</sub> | -0.5    | 3.7                    | V     |                                             |

| ESD (sensor only)                 |                   |         | 2                      | kV    | All pins, human body model<br>JESD22-A114-E |

| Input Voltage                     | $V_{IN}$          | -0.5    | V <sub>DDIO</sub> +0.5 | V     |                                             |

| Latchup Current                   | lout              |         | 20                     | mA    | All Pins                                    |

Note: Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are the stress ratings only and functional operation of the device at these or any other condition beyond those indicated may affect device reliability.

### **Recommended Operating Conditions**

| Parameter                                                 | Symbol            | Minimum | Typical        | Maximum | Units                            | Notes                                                                               |

|-----------------------------------------------------------|-------------------|---------|----------------|---------|----------------------------------|-------------------------------------------------------------------------------------|

| Operating Temperature                                     | T <sub>A</sub>    | -20     |                | 70      | °C                               |                                                                                     |

| Analog and Digital<br>Supply Voltage [1]                  | 3                 |         | 2.1 Volts Incl |         | Including V <sub>NA</sub> noise. |                                                                                     |

| I/O Supply Voltage [2]                                    | V <sub>DDIO</sub> | 1.65    | 1.8 or 2.8     | 3.6     | Volts                            | Including V <sub>NA</sub> noise. Sets I/O voltages. See fig 7.                      |

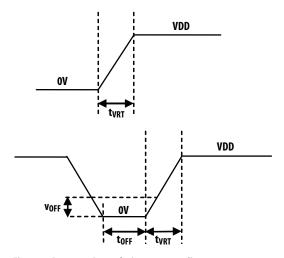

| Power Supply Rise Time                                    | t <sub>VRT</sub>  | 0.001   |                | 10      | ms                               | 0 to VDD. At minimum rise time, s/'                                                 |

| Power Supply Off Time for<br>Valid POR (Power on Reset)   | t <sub>OFF</sub>  | 10      |                |         | ms                               | Refer to section "POR During Power Cycling"                                         |

| Power Off Voltage Level for<br>Valid POR (Power on Reset) | V <sub>OFF</sub>  | 0       |                | 300     | mV                               | Refer to section "POR During Power Cycling"                                         |

| Supply Noise (Sinusoidal)                                 | V <sub>NA</sub>   |         |                | 100     | mV p-p                           | 10 kHz - 50 MHz                                                                     |

| Speed                                                     | S                 |         |                | 20      | in/sec                           | Using prosthetic finger as surface                                                  |

| Transient Supply Current                                  | I <sub>DDT</sub>  |         |                | 80      | mA                               | Max supply current for 500 μsec<br>for each supply voltages ramp from<br>0 to 1.8 V |

#### Notes

- 1. Operating temperature of less than -20°C down to -30°C, minimum VDD of 1.8V must be met.

- 2. To ensure minimum leakage current, VDDIO should be greater than or equal to VDD

## **Timing Specifications**

Electrical Characteristics at 25° C, VDD=VDDIO=1.8V.

| Parameter                                      | Symbol                   | Minimum | Typical | Maximum | Units | Notes                                                                                                            |

|------------------------------------------------|--------------------------|---------|---------|---------|-------|------------------------------------------------------------------------------------------------------------------|

| Motion Delay After Reset                       | t <sub>MOT-RST</sub>     | 3.5     |         | 23      | ms    | From Hard reset or SOFT_RESET register write to valid register write/read and motion, assuming motion is present |

| Shutdown                                       | t <sub>SHTDWN</sub>      |         |         | 50      | ms    | From SHTDWN pin active to low current                                                                            |

| Wake from Shutdown                             | twakeup                  | 100     |         |         | ms    | From SHTDWN pin inactive to valid motion. Refer to section "Notes on Shutdown", also note t <sub>MOT-RST</sub>   |

| EVENT_INT Rise Time                            | t <sub>r-EVENT_INT</sub> |         | 150     | 300     | ns    | C <sub>L</sub> = 100 pF                                                                                          |

| EVENT_INT Fall Time                            | t <sub>f-EVENT_INT</sub> |         | 150     | 300     | ns    | C <sub>L</sub> = 100 pF                                                                                          |

| SHTDWN Pulse Width                             | t <sub>P-SHTDWN</sub>    | 150     |         |         | ms    |                                                                                                                  |

| NRST Pulse Width                               | t <sub>NRST</sub>        | 20      |         |         | μs    | From edge of valid NRST pulse                                                                                    |

| Reset Wait Time After<br>Stable Supply Voltage | t <sub>VRT-NRST</sub>    | 100     |         |         | ms    |                                                                                                                  |

## **DC Electrical Specifications**

Electrical Characteristics at 25° C, VDD=VDDIO=1.8V at default LED setting 13 mA.

| Parameter                               |                              | Typical | Max  | Units | Notes                                         |

|-----------------------------------------|------------------------------|---------|------|-------|-----------------------------------------------|

| DC average supply current in Run mode   | $I_{VDD}$                    | 2.90    | 4.03 | mA    | GPIO=SHTDWN=pull low, IO_MISO=NRST=pull high. |

| DC average supply current in Rest1 mode | $I_{VDD}$                    | 0.35    | 0.50 | mA    | GPIO=SHTDWN=pull low, IO_MISO=NRST=pull high. |

| DC average supply current in Rest2 mode | I <sub>VDD</sub>             | 0.07    | 0.12 | mA    | GPIO=SHTDWN=pull low, IO_MISO=NRST=pull high. |

| DC average supply current in Rest3 mode | I <sub>VDD</sub>             | 0.03    | 0.06 | mA    | GPIO=SHTDWN=pull low, IO_MISO=NRST=pull high. |

| Analog shutdown supply current          | I <sub>DDSHTDWN</sub><br>VDD | 1.54    | 26.7 | μΑ    | GPIO=pull low, SHTDWN=IO_MISO=NRST=pull high. |

### **DC Electrical Specifications**

Electrical Characteristics at 25° C, VDD=VDDIO=1.8V at default LED setting 13 mA.

| Parameter                           | Symbol                     | Minimum                | Typical                | Maximum                 | Units | Notes                                                               |

|-------------------------------------|----------------------------|------------------------|------------------------|-------------------------|-------|---------------------------------------------------------------------|

| V <sub>DDIO</sub> DC Supply Current | $IV_{DDIO}$                |                        |                        | 20                      | μΑ    |                                                                     |

| Digital peak supply current         | I <sub>PEAK</sub> VDD      |                        |                        | 10                      | mA    |                                                                     |

| LED+ peak supply current            | I <sub>PEAK</sub> LED+     |                        |                        | 35                      | mA    | At LED register setting of 27 mA                                    |

| Input Low Voltage                   | V <sub>IL</sub>            | -0.05                  | 0                      | V <sub>DDIO</sub> *0.35 | V     | IO_MOSI_A0, IO_CLK, IO_MISO_SDA, IO_NCS_A1, NRST, SHTDWN, IO_SELECT |

| Input High Voltage                  | gh Voltage V <sub>IH</sub> |                        | V <sub>DDIO</sub>      | V <sub>DDIO</sub> +0.05 | V     | IO_MOSI_A0, IO_CLK, IO_MISO_SDA, IO_NCS_A1, NRST, SHTDWN, IO_SELECT |

| Input hysteresis                    | $V_{HYS}$                  | 100                    |                        |                         | mV    |                                                                     |

| Input leakage current               | l <sub>leak</sub>          |                        | ±1                     | ±10                     | μΑ    | IO_MOSI_A0, IO_CLK, IO_MISO_SDA, IO_NCS_A1, NRST, SHTDWN, IO_SELECT |

| Output Low Voltage                  | V <sub>OL</sub>            |                        |                        | 0.2                     | V     | I <sub>out</sub> = 1.2 mA                                           |

| Output High Voltage                 | $V_{OH}$                   | V <sub>DDIO</sub> -0.2 | V <sub>DDIO</sub> -0.1 |                         | V     | $I_{out} = 600 \mu A$                                               |

| Input Capacitance                   | C <sub>in</sub>            |                        |                        | 10                      | pF    | MOSI, NCS, SCLK, SHTDWN                                             |

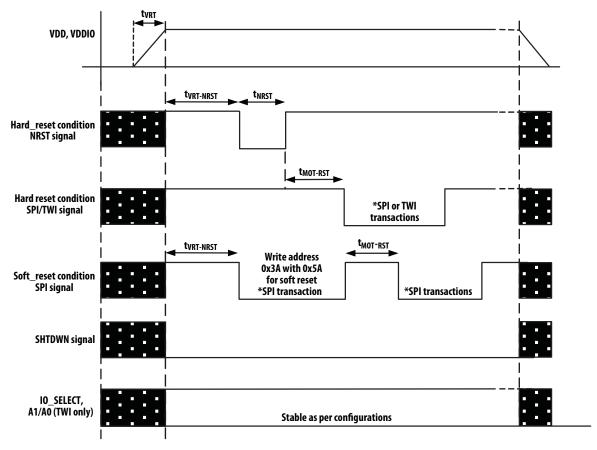

### **Notes on Power-up Sequence**

Below is the power up sequence for ADBS-A350:

For SPI:

- 1. Apply power. Refer timing diagram on power up sequence below.

- 2. Set IO\_NCS\_A1 pin high. Set SHTDWN pin low. Set IO\_SELECT pin high.

- 3. Perform reset by driving NRST low then high OR by writing 0x5A to address 0x3A.

- 4. Read Product ID (PID) to ensure sensor is powered up and communicating properly with host.

- 5. Write 0xE4 to address 0x60

- 6. Write 0xC9 to address 0x61

#### For TWI:

- 1. Apply power. Refer timing diagram on power up sequence below.

- 2. Set SHTDWN and IO\_SELECT pin low.

- 3. Set A0 and A1 according to the desired TWI slave address (from TWI slave address table in datasheet).

- 4. Drive NRST pin low then high. TWI slave address will only be valid and according to the address set in step 3 after a NRST toggle is applied.

- 5. Read Product ID (PID) to ensure sensor is powered up and communicating properly with host.

- 6. Write 0xE4 to address 0x60

- 7. Write 0xC9 to address 0x61

Note: Not to scale

#### Note on register settings

Please refer to the OFN A350 firmware design guide for tuning of Speed Switching, Assert/De-assert, Finger Presence Detect and XY Quantization register settings.

#### **Notes on Shutdown and Reset**

The ADBM-A350 can be set in Shutdown mode by asserting or setting SHTDWN pin high. During the shutdown state, supply voltages VDD must be maintained above the minimum level. If these conditions are not met, then the sensor must be restarted by powering down then powering up again for proper operation. Any register settings must then be reloaded.

During the shutdown state, supply voltage VDD must be maintained above the minimum level. For proper operation, SHTDWN pulse width must be at least tp\_SHTDWN. Shorter pulse widths may cause the chip to enter an undefined state. In addition, the SPI or TWI port of the sensor should not be accessed when SHTDWN is asserted. Other devices on the same SPI bus can be accessed, as long as the sensor's NCS pin is not asserted. The table below shows the state of various pins during shutdown. After deasserting SHTDWN, wait twakeup before accessing

the SPI port. Reinitializing the sensor from shutdown state will retain all register data that were written to the sensor prior to shutdown.

The reset of the sensor via SOFT\_RESET register or through the NRST pin would reset all registers to the default value. Any register settings must then be reloaded.

| Pin         | SHTDWN active       |

|-------------|---------------------|

| IO_NCS_A1   | Functional          |

| IO_MISO_SDA | Undefined           |

| IO_CLK      | Undefined           |

| IO_MOSI_A0  | Undefined           |

| XY_LED      | Low current         |

| EVENT_INT   | Undefined           |

| NRST        | High                |

| IO_Select   | SPI: High, TWI: Low |

| GPIO        | Undefined           |

Note: There are long wakeup times from shutdown. These features should not be used for power management during normal sensor motion.

### Power on Reset (POR) During Power Cycling

$t_{VRT}$  is the power supply (VDD) rise time specification for a valid power on reset to happen when the sensor is powered up from 0V to VDD. At condition whereby the VDD of the sensor is cycled from VDD to 0 V and then to VDD again, the two parameters that govern a valid power on reset are  $v_{OFF}$  and  $t_{OFF}$ . Refer to timing diagram below.

Figure 3. Power on Reset during power cycling

### Power management modes

The ADBM-A350 has three power-saving modes. Each mode has a different motion detection period, affecting response time to sensor motion (Response Time). The sensor automatically changes to the appropriate mode, depending on the time since the last reported motion (Downshift Time). The parameters of each mode are shown in the following table.

| Mode   | Response Time<br>(nominal) | Downshift Time<br>(nominal) |

|--------|----------------------------|-----------------------------|

| Rest 1 | 19.5 ms                    | 250 ms                      |

| Rest 2 | 96 ms                      | 9.5 s                       |

| Rest 3 | 482 ms                     | 582 s                       |

### **EVENT INT Pin**

The Event\_Int pin is a level-sensitive interrupt output that is used to trigger the host micro-controller when one of these events occurs:

- FPD A change in finger state (finger on to finger off and vice versa) is detected

- Soft Click Soft Click is detected

- Button Mechanical button is asserted or de-asserted

- Motion Motion delta is present.

A read to event register is required to determine the specific event that toggles the interrupt for user to act upon.

The EVENT\_INT will be reset after the user responds to it by reading the respective event status register:

- FPD reading FPD\_STATUS register (0x7a)

- Soft Click reading SC\_STATUS register (0x7f)

- Button reading BUTTON\_STATUS register (0x12)

- Motion reading DELTA\_X and DELTA\_Y registers until motion are cleared.

#### **GPIO Pin**

The GPIO pin is a level-sensitive input/output that can be used as

- FPD output to display FPD status

- Pulse Width Modulated (PWM) output to control LED driver to enable illumination feature in a product eg mobile phone

- Dome/ Button click input can be connected to a dome switch that provides an input to the sensor and when a click is detected, sensor can respond by triggering button interrupt and channel the interrupt status through EVENT pin.

Refer to A350 Firmware Design Guide for more details and settings of registers for these features.

### **LED Mode**

For power savings, the LED will not be continuously on. ADBM-A350 will flash the LED only when needed.

### I/O Pin Status Test

This feature allows the user to verify the connectivity and the state of the I/O pin.

To run the test for input pins such as GPIO, SHUTDOWN, NRST and IO\_SELECT, first enable the PAD\_Chk\_On bit (or bit-1) of OFN\_ENGINE2 (0x61) register. Then write any value to PAD\_STATUS (0x31) register to start the test. Wait for approximately 12us before reading the actual pin status and PAD\_STATUS register. The test will be considered a PASS to indicate the sensor is responding accordingly if the actual pin status matches PAD\_STATUS register content. Refer to the table below for I/O pin status definition

For output pins (EVENT\_INT, GPIO, MOSI and MISO) testing, first enable bit-4 of PAD\_FUNCTION (0x34) register. Then program or set the output state via PAD\_TEST\_OUT register (0x33) and do a READ on the actual pin status. Actual pin status results should match the output set in PAD\_TEST\_OUT. (Note: SPI/TWI communication will be disabled after this test is enabled. Once this test is completed, an external hardware reset on sensor is required)

| Bit(s) | Name            | Reset | Description  | Remarks                                        |

|--------|-----------------|-------|--------------|------------------------------------------------|

| 7:6    | NRST_STATE      | 0x0   | 0x0: unknown |                                                |

|        |                 |       | 0x1: Low     | Invalid as the chip will be in reset state.    |

|        |                 |       | 0x2: High    |                                                |

|        |                 |       | 0x3: Hi-Z    | Indicate a floating high                       |

| 5:4    | SHUTDOWN_STATE  | 0x0   | 0x0: unknown |                                                |

|        |                 |       | 0x1: Low     |                                                |

|        |                 |       | 0x2: High    | Invalid as the chip will be in shutdown state. |

|        |                 |       | 0x3: Hi-Z    | Indicate a floating low                        |

| 3:2    | GPIO_STATE      | 0x0   | 0x0: unknown |                                                |

|        |                 |       | 0x1: Low     |                                                |

|        |                 |       | 0x2: High    |                                                |

|        |                 |       | 0x3: Hi-Z    |                                                |

| 1:0    | IO_SELECT_STATE | 0x0   | 0x0: unknown |                                                |

|        |                 |       | 0x1: Low     |                                                |

|        |                 |       | 0x2: High    |                                                |

|        |                 |       | 0x3: Hi-Z    |                                                |

### **Fast Video Dump**

ADBS-A350 comes with a unique feature that enables user to capture the image the optical sensor is seeing on the tracking surface. This is achieved through storing the pixel data, transferring or dumping the pixels data out to the host for processing and rebuilding the video dump image. The rebuilding of video dump image is mainly converting each 8-bit pixel data to form a grayscale digital image.

Some useful applications for this feature are sensor contamination inspection at manufacturing lines, image recognition, motion sensing applications and etc.

### **Fast Video Dump Setups and Commands**

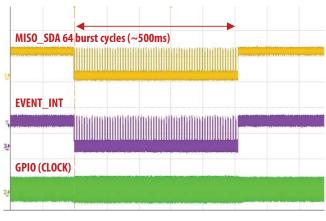

Fast Video Dump (FVD) in the sensor requires three main signal lines for communications with host MCU as shown below.

| Pin       | Status | Description            |

|-----------|--------|------------------------|

| GPIO      | Input  | 24MHz clock signal     |

| MISO_SDA  | Output | Pixel data bits 7 to 4 |

| EVENT_INT | Output | Pixel data bits 3 to 0 |

Connect an external clock signal of up to 24MHz to GPIO pin. Execute the FVD commands below and capture the 64burst cycles of data clocked out on the two output pins (MISO\_SDA and EVENT\_INT).

#### **FVD Commands**

- 1. Power up sensor

- 2. Read register 0x00, to get returned value of 0x88 for correct product ID (ensure communication with sensor is established)

- 3. Write register 0x3a with 0x5a

- 4. Write register 0x11 with 0x53

- 5. Write register 0x30 with 0x13

- 6. Write register 0x2b with 0x30

- 7. Write register 0x2c with 0x13

- 8. Write register 0x28 with 0x01 to initiate video dump.

- 9. Sensor will start to video dump for about 500ms (see timing diagram on signals decoding versus actual signal captured).

- 10. Once video dump is completed, write register 0x3a with 0x5a to soft reset sensor back to normal operation. (Note: During FVD, the sensor is in 3-wire SPI communication with host MCU by design. Therefore a soft reset is necessary to reset back to 4-wire SPI communication for normal operation or to perform another FVD)

- 11. To capture another 64 burst cycles, repeat Step 2- Step 10.

### **Video Dump Signals Capturing and Decoding**

64 burst cycles of FVD will be present on the MISO\_SDA and EVENT\_INT pins after executing the fast video dump commands.

Zooming into each burst cycle, 3 frames in each burst cycle will be observed.

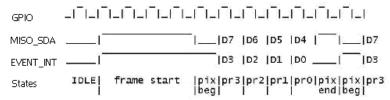

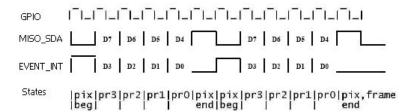

Figure 4. Signals for frame start

As shown in Figure 4 above, frame start of video dump is denoted by MISO\_SDA pin and EVENT\_INT pin clocking high for 4 clock cycles or 4 x b'11 (binary 11). Then after 4 clock cycles, MISO\_SDA pin will go low and EVENT\_INT pin remains high. This indicates pixel begin state.

The pixel read data will start to clock thereafter. Subsequent 4 bits are D7-D4 (on MISO\_SDA) and D3-D0 (on EVENT\_INT) followed by b'10 for pixel end (b'1 in MISO\_SDA, b'0 in EVENT\_INT). This completes the first pixel data (address 0). The next pixel data (address 1) will begin with pixel begin state (b'01- 0 in MISO\_SDA, 1 in EVENT\_INT) header followed by the 4 clock cycles of data followed by a pixel end state in the same manner. This will continue until all the 361 pixels (19x19 pixel array) data is read. Once done, the pixel end of the pixel data (address 360) will be followed by frame end state (b'00 – 0 in MISO\_SDA, 0 in EVENT\_INT). Refer to Figure 5.

Below is the pixel array address map. The figure shows the view of the chip from the top of the OFN aperture. Rows are read from top to bottom and columns from left to right.

| D | ÷ | n |  |

|---|---|---|--|

| М | I | п |  |

| 111 1 |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

|-------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0     | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 9   | 10  | 11  | 12  | 13  | 14  | 15  | 16  | 17  | 18  |

| 19    | 20  | 21  | 22  | 23  | 24  | 25  | 26  | 27  | 28  | 29  | 30  | 31  | 32  | 33  | 34  | 35  | 36  | 37  |

| 38    | 39  | 40  | 41  | 42  | 43  | 44  | 45  | 46  | 47  | 48  | 49  | 50  | 51  | 52  | 53  | 54  | 55  | 56  |

| 57    | 58  | 59  | 60  | 61  | 62  | 63  | 64  | 65  | 66  | 67  | 68  | 69  | 70  | 71  | 72  | 73  | 74  | 75  |

| 76    | 77  | 78  | 79  | 80  | 81  | 82  | 83  | 84  | 85  | 86  | 87  | 88  | 89  | 90  | 91  | 92  | 93  | 94  |

| 95    | 96  | 97  | 98  | 99  | 100 | 101 | 102 | 103 | 104 | 105 | 106 | 107 | 108 | 109 | 110 | 111 | 112 | 113 |

| 114   | 115 | 116 | 117 | 118 | 119 | 120 | 121 | 122 | 123 | 124 | 125 | 126 | 127 | 128 | 129 | 130 | 131 | 132 |

| 133   | 134 | 135 | 136 | 137 | 138 | 139 | 140 | 141 | 142 | 143 | 144 | 145 | 146 | 147 | 148 | 149 | 150 | 151 |

| 152   | 153 | 154 | 155 | 156 | 157 | 158 | 159 | 160 | 161 | 162 | 163 | 164 | 165 | 166 | 167 | 168 | 169 | 170 |

| 171   | 172 | 173 | 174 | 175 | 176 | 177 | 178 | 179 | 180 | 181 | 182 | 183 | 184 | 185 | 186 | 187 | 188 | 189 |

| 190   | 191 | 192 | 193 | 194 | 195 | 196 | 197 | 198 | 199 | 200 | 201 | 202 | 203 | 204 | 205 | 206 | 207 | 208 |

| 209   | 210 | 211 | 212 | 213 | 214 | 215 | 216 | 217 | 218 | 219 | 220 | 221 | 222 | 223 | 224 | 225 | 226 | 227 |

| 228   | 229 | 230 | 231 | 232 | 233 | 234 | 235 | 236 | 237 | 238 | 239 | 240 | 241 | 242 | 243 | 244 | 245 | 246 |

| 247   | 248 | 249 | 250 | 251 | 252 | 253 | 254 | 255 | 256 | 257 | 258 | 259 | 260 | 261 | 262 | 263 | 264 | 265 |

| 266   | 267 | 268 | 269 | 270 | 271 | 272 | 273 | 274 | 275 | 276 | 277 | 278 | 279 | 280 | 281 | 282 | 283 | 284 |

| 285   | 286 | 287 | 288 | 289 | 290 | 291 | 292 | 293 | 294 | 295 | 296 | 297 | 298 | 299 | 300 | 301 | 302 | 303 |

| 304   | 305 | 306 | 307 | 308 | 309 | 310 | 311 | 312 | 313 | 314 | 315 | 316 | 317 | 318 | 319 | 320 | 321 | 322 |

| 323   | 324 | 325 | 326 | 327 | 328 | 329 | 330 | 331 | 332 | 333 | 334 | 335 | 336 | 337 | 338 | 339 | 340 | 341 |

| 342   | 343 | 344 | 345 | 346 | 347 | 348 | 349 | 350 | 351 | 352 | 353 | 354 | 355 | 356 | 357 | 358 | 359 | 360 |

Pin 18

The signal to indicate the end of the video dump frame is shown in Figure 5 below where pix end state is followed by a low in both MISO\_SDA and EVENT\_INT. This will inform the Host of the pixel end and frame end state.

Figure 5. Frame End

Note: It is advisable to have a counter at the Host to keep count of the number of pixel addresses and data byte. If the number of pixel data byte does not correspond to the sensor number of pixel then this video dump data is invalid. In this case the sensor must be reset and a new video dump must be initiated.

### **Fast Video Dump Image**

These are some examples of grayscale images captured using fast video dump on an object 'A' (size of 1mmx1mm) at the surface of the sensor that is converted from the fast video dump data.

## 4-wire Serial Peripheral Interface (SPI)

## **SPI Specifications**

Electrical Characteristics over recommended operating conditions. Typical values at  $25^{\circ}$  C, VDD = 1.8 V.

| Parameter                                     | Symbol                               | Minimum | Typical | Maximum             | Units | Notes                                                                                                                            |

|-----------------------------------------------|--------------------------------------|---------|---------|---------------------|-------|----------------------------------------------------------------------------------------------------------------------------------|

| Serial Port Clock<br>Frequency                | f <sub>sclk</sub>                    |         |         | 1                   | MHz   | Active drive, 50% duty cycle                                                                                                     |

| MISO rise time                                | t <sub>r-MISO</sub>                  |         | 150     | 300                 | ns    | C <sub>L</sub> = 100 pF                                                                                                          |

| MISO fall time                                | t <sub>f-MISO</sub>                  |         | 150     | 300                 | ns    | C <sub>L</sub> = 100 pF                                                                                                          |

| MISO delay after SCLK                         | t <sub>DLY_MISO</sub>                |         |         | 120                 | ns    | From SCLK falling edge to MISO data valid, no load conditions                                                                    |

| MISO hold time                                | t <sub>hold_MISO</sub>               | 0.5     |         | 1/f <sub>SCLK</sub> | μs    | Data held until next falling SCLK edge                                                                                           |

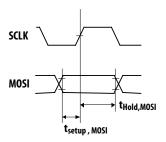

| MOSI hold time                                | t <sub>hold_MOSI</sub>               | 200     |         |                     | ns    | Amount of time data is valid after SCLK rising edge                                                                              |

| MOSI setup time                               | t <sub>setup_MOSI</sub>              | 120     |         |                     | ns    | From data valid to SCLK rising edge                                                                                              |

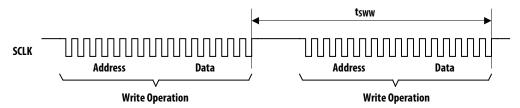

| SPI time between write commands               | t <sub>SWW</sub>                     | 30      |         |                     | μs    | From rising SCLK for last bit of the first data byte, to rising SCLK for last bit of the second data byte.                       |

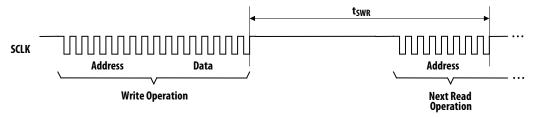

| SPI time between write and read commands      | t <sub>SWR</sub>                     | 20      |         |                     | μs    | From rising SCLK for last bit of the first data byte, to rising SCLK for last bit of the second address byte.                    |

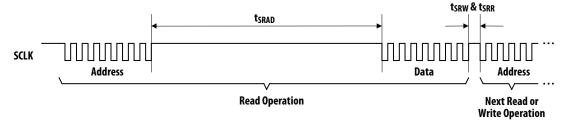

| SPI time between read and subsequent commands | t <sub>SRW</sub><br>t <sub>SRR</sub> | 500     |         |                     | ns    | From rising SCLK for last bit of the first data byte, to falling SCLK for the first bit of the address byte of the next command. |

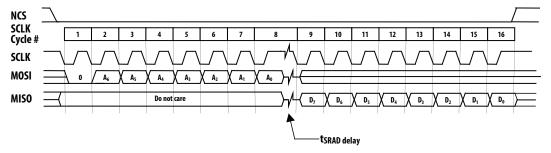

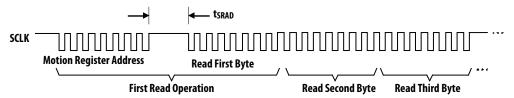

| SPI read address-data<br>delay                | t <sub>SRAD</sub>                    | 4       |         |                     | μs    | From rising SCLK for last bit of the address byte, to falling SCLK for first bit of data being read.                             |

| NCS inactive after motion burst               | t <sub>BEXIT</sub>                   | 500     |         |                     | ns    | Minimum NCS inactive time after motion burst before next SPI usage                                                               |

| NCS to SCLK active                            | t <sub>NCS-SCLK</sub>                | 120     |         |                     | ns    | From NCS falling edge to first SCLK falling edge                                                                                 |

| SCLK to NCS inactive (for read operation)     | t <sub>SCLK-NCS</sub>                | 120     |         |                     | ns    | From last SCLK rising edge to NCS rising edge, for valid MISO data transfer                                                      |

| SCLK to NCS inactive (for write operation)    | t <sub>SCLK-NCS</sub>                | 20      |         |                     | us    | From last SCLK rising edge to NCS rising edge, for valid MOSI data transfer                                                      |

| NCS to MISO high-Z                            | t <sub>NCS-MISO</sub>                |         |         | 500                 | ns    | From NCS rising edge to MISO high-Z state                                                                                        |

### **Synchronous Serial Port**

The synchronous serial port is used to set and read parameters in the ADBM-A350, and to read out the motion information.

The port is a four wire serial port. The host micro-controller always initiates communication; the ADBM-A350 never initiates data transfers. SCLK, MOSI, and NCS may be driven directly by a micro-controller. The port pins may be shared with other SPI slave devices. When the NCS pin is high, the inputs are ignored and the output is tri-stated.

The lines that comprise the 4-wire SPI port:

SCLK: Clock input. It is always generated by the master (the micro-controller).

MOSI: Input data. (Master Out/Slave In)

MISO: Output data. (Master In/Slave Out)

NCS: Chip select input (active low). NCS needs to be low to activate the serial port; otherwise, MISO will be high Z, and MOSI & SCLK will be ignored. NCS can also be used to reset the serial port in case of an error.

### **Chip Select Operation**

The serial port is activated after NCS goes low. If NCS is raised during a transaction, the entire transaction is aborted and the serial port will be reset. This is true for all transactions. After a transaction is aborted, the normal address-to-data or transaction-to-transaction delay is still required before beginning the next transaction. To improve communication reliability, all serial transactions should be framed by NCS. In other words, the port should not remain enabled during periods of non-use because ESD events could be interpreted as serial communication and put the chip into an unknown state. In addition, NCS must be raised after each burst-mode transaction is complete to terminate burst-mode. The port is not available for further use until burst-mode is terminated.

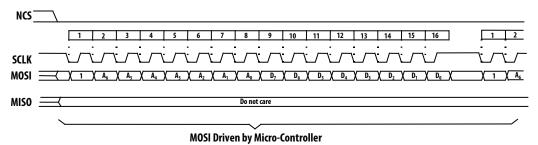

### Write Operation

Write operation, defined as data going from the micro-controller to the ADBM-A350, is always initiated by the micro-controller and consists of two bytes. The first byte contains the address (seven bits) and has a "1" as its MSB to indicate data direction. The second byte contains the data. The ADBM-A350 reads MOSI on rising edges of SCLK.

Figure 6. Write Operation

Figure 7. MOSI Setup and Hold Time

### **Read Operation**

A read operation, defined as data going from the ADBM-A350 to the micro-controller, is always initiated by the micro-controller and consists of two bytes. The first byte contains the address, is sent by the micro-controller over MOSI, and has a "0" as its MSB to indicate data direction. The second byte contains the data and is driven by the ADBM-A350 over MISO. The sensor outputs MISO bits on falling edges of SCLK and samples MOSI bits on every rising edge of SCLK.

Figure 8. Read Operation

NOTE: The 0.5/ $f_{SCLK}$  minimum high state of SCLK is also the minimum MISO data hold time of the ADBM-A350. Since the falling edge of SCLK is actually the start of the next read or write command, the ADBM-A350 will hold the state of data on MISO until the falling edge of SCLK.

Figure 9. MISO Delay and Hold Time

### Required timing between Read and Write Commands

There are minimum timing requirements between read and write commands on the serial port.

Figure 10. Timing between two write commands

If the rising edge of the SCLK for the last data bit of the second write command occurs before the required delay (t<sub>SWW</sub>), then the first write command may not complete correctly.

Figure 11. Timing between write and read commands

If the rising edge of SCLK for the last address bit of the read command occurs before the required delay (t<sub>SWR</sub>), the write command may not complete correctly.

Figure 12. Timing between read and either write or subsequent read commands

During a read operation SCLK should be delayed at least  $t_{SRAD}$  after the last address data bit to ensure that the ADBM-A350 has time to prepare the requested data. The falling edge of SCLK for the first address bit of either the read or write command must be at least  $t_{SRR}$  or  $t_{SRW}$  after the last SCLK rising edge of the last data bit of the previous read operation.

#### **Burst Mode Operation**

Burst mode is a special serial port operation mode that may be used to reduce the serial transaction time for a motion read. The speed improvement is achieved by continuous data clocking from multiple registers without the need to specify the register address, and by not requiring the normal delay period between data bytes.

Burst mode is activated by writing 0x10 to register 0x1c IO\_MODE. Then the burst mode data can be read by reading the Motion register 0x02. The ADBM-A350 will respond with the contents of the Motion, Delta\_Y, Delta\_X, SQUAL, Shutter Upper, Shutter Lower and Maximum Pixel registers in that order. The burst transaction can be terminated after the first 3 bytes of the sequence are read by bringing the NCS pin high. After sending the register address, the micro-controller must wait t<sub>SRAD</sub> and then begin reading data. All data bits can be read with no delay between bytes by driving SCLK at the normal rate. The data is latched into the output buffer after the last address bit is received. After the burst transmission is complete, the micro-controller must raise the NCS line for at least t<sub>BEXIT</sub> to terminate burst mode. The serial port is not available for use until it is reset with NCS, even for a second burst transmission.

Figure 13. Motion Burst Timing

### Two – Wire Interface (TWI)

ADBM-A350 uses a two-wire serial control interface compatible with I2C. The parameters are listed below.

### **TWI Specifications**

Electrical Characteristics over recommended operating conditions. Typical values at 25° C, VDD = 1.8 V.

| Parameter                                                                                   | Symbol               | Minimum                             | Maximum | Units | Notes |

|---------------------------------------------------------------------------------------------|----------------------|-------------------------------------|---------|-------|-------|

| SCL clock frequency                                                                         | fscl                 |                                     | 400     | kHz   |       |

| Hold time (repeated) START condition. After this period, the first clock pulse is generated | t <sub>HD_</sub> STA | 0.6                                 | -       | μs    |       |

| LOW period of the SCL clock                                                                 | t <sub>LOW</sub>     | 1.0                                 | _       | μs    |       |

| HIGH period of the SCL clock                                                                | t <sub>HIGH</sub>    | 0.6                                 | -       | μs    |       |

| Set up time for a repeated START condition                                                  | t <sub>SU_STA</sub>  | 0.6                                 | -       | μs    |       |

| Data hold time                                                                              | t <sub>HD_DAT</sub>  | 0 <sup>(2)</sup>                    | 0.9(3)  | μs    |       |

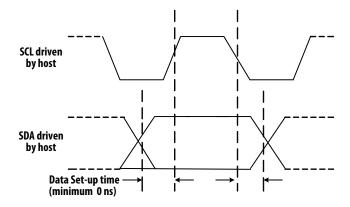

| Data set-up time                                                                            | t <sub>SU_DAT</sub>  | 100                                 | -       | ns    |       |

| Rise time of both SDA and SCL signals                                                       | t <sub>r</sub>       | 20+0.1C <sub>b</sub> <sup>(4)</sup> | 300     | ns    |       |

| Fall time of both SDA and SCL signals                                                       | t <sub>f</sub>       | 20+0.1C <sub>b</sub> <sup>(4)</sup> | 300     | ns    |       |

| Set up time for STOP condition                                                              | t <sub>SU_STO</sub>  | 0.6                                 | -       | μs    |       |

| Bus free time between a STOP and START condition                                            | t <sub>BUF</sub>     | 1.3                                 | _       | μs    |       |

| Capacitive load for each bus line                                                           | C <sub>b</sub>       | -                                   | 400     | рF    |       |

| Noise margin at the LOW level for each connected device (including hysteresis)              | V <sub>NL</sub>      | 0.1 VDD                             | -       | V     |       |

| Noise margin at the HIGH level for each connected device (including hysteresis)             | V <sub>NH</sub>      | 0.2 VDD                             |         | V     |       |

#### Notes:

- 1. All values referred to V<sub>IHMIN</sub> and V<sub>ILMAX</sub> levels.

- 2. A device must internally provide a hold time of at least 300 ns for the SDA signal (referred to the V<sub>IHMIN</sub> of the SCL signal) to bridge the undefined region of the falling edge of SCL.

- 3. The maximum has  $t_{HD\ DAT}$  only to be met if the device does not stretch the LOW period ( $t_{LOW}$ ) of the SCL signal.

- 4.  $C_B = \text{total capacitance of one bus line in pF.}$

The ADBM-A350 responds to one of the following selectable slave device addresses depending on the IO\_MOSI\_ A0 and IO\_NCS\_A1 input pin state. These pins should be set to avoid conflict with any other devices that might be sharing the bus.

Table 1. TWI slave address

| A0 | A1 | Slave Address (Hex) |

|----|----|---------------------|

| 0  | 0  | 33                  |

| 0  | 1  | 3b                  |

| 1  | 0  | 53                  |

| 1  | 1  | 57                  |

### **Serial Transfer Clock and Serial Data signals**

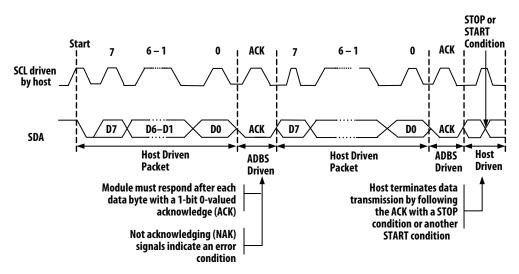

The serial control interface uses two signals: a serial transfer clock (SCL) signal and a serial data (SDA) signal. Always driven by the master, SCL synchronizes the serial transmission of data bits on SDA. The frequency of SCL may vary throughout a transfer, as long as the timing is greater than the minimum timing.

SDA is bi-directional. The host (master) can read from or write to the ADBM-A350. The host (typically a microcontroller) drives SCL and SDA in a write operation or requesting information from the ADBM-A350. The ADBM-A350 drives the SDA only under two conditions. First, when responding with an acknowledge (ACK) bit after receiving data from the host, or second, when sending data to the host at the host's request. Data is sent in Eight-bit packets.

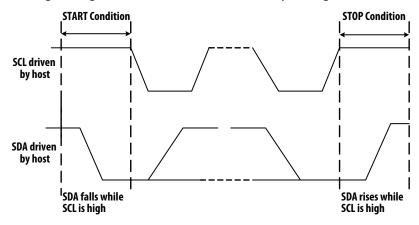

## **Start and Stop of Synchronous Operation**

The host initiates and terminates all data transfers. Data transfers are initiated by driving SDA from high to low while holding SCL high. Data transfers are terminated by driving SDA from low to high while SCL is held high.

Figure 14. TWI Start and Stop operation

### Acknowledge/Not Acknowledge Bit

After a start condition, a single acknowledge/not acknowledge bit follows each Eight-bit data packet. The device receiving the data drives the acknowledge/not acknowledge signal on SDA. Acknowledge (ACK) is defined as 0 and not acknowledge (NAK) is defined as 1.

#### **Packet Formats**

Read and write operations between the host and the ADBM-A350 use three types of host driven packets and one type of ADBM-A350 driven packet. All packets are eight bits long with the most significant bit first, followed by an acknowledge bit.

#### Slave Device Address (DA)

Command packets contain a 7-bit ADBM-A350 device address and an active low read/write bit (R/W).

| First bit of packet |       |       |                |       |       |       | Last bit of packet    |

|---------------------|-------|-------|----------------|-------|-------|-------|-----------------------|

|                     |       |       | Device Address | i     |       |       | R/W                   |

| DA[6]               | DA[5] | DA[4] | DA[3]          | DA[2] | DA[1] | DA[0] | Write = 0<br>Read = 1 |

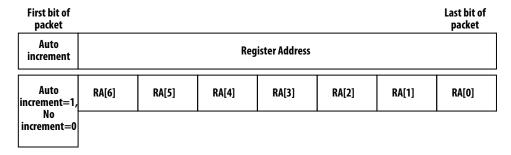

### Register Address Packets (RA)

The address packets contain an auto-increment (ai) bit and a 7-bit address. If the 'ai' bit is set, the slave will process data from successive addresses in successive bytes. For example, registers 0x01, 0x02, and 0x03 can be written by setting the 'ai' bit to one with address 0x01. The host would send three bytes of data, and the host would terminate with a P condition.

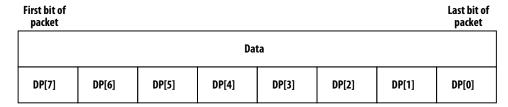

### Data Packet (DP)

Contains 8 data bits and may be sent by the host or the ADBM-A350.

### **Host Driven Packets**

The host initiates all data transmission with a START condition. Next, slave address and register address packets are sent. If there is a device address match, the ADBM-A350 then responds to each Eight-bit data transmission with an acknowledge signal (SDA = 0). Data is transmitted with the most significant bit first.

To terminate the transfer of host driven packets, the host follows the ADBM-A350's ACK with a STOP condition. The host can also issue a START condition after the ADBM-A350's ACK if it wants to start a new data transfer.

Figure 15. Host packets

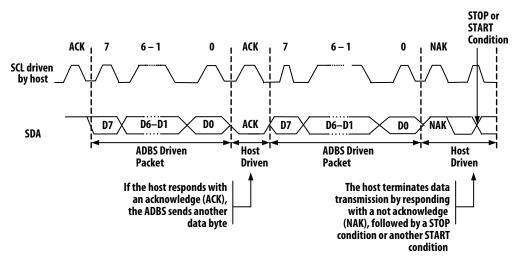

#### **ADBM-A350 Driven Packets**

By request of the host, the ADBM-A350 acknowledges a read request and then outputs a data byte transmitting the most significant bit (7) first. If the host intends to continue the data transfer, the host acknowledges the ADBM-A350. If the host intends to terminate the transfer, it responds with not acknowledge (SDA = 1), and then drives SDA to generate a STOP condition. The host can also drive a START condition if it wants to begin a new data transfer with the same ADBM-A350.

Figure 16. Sensor packets

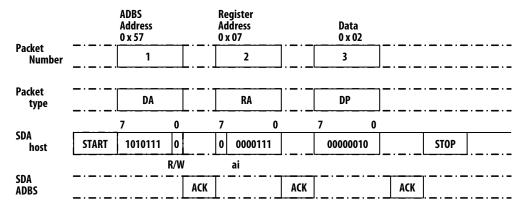

### **Example: Writing Data to Sensor Registers**

The host writes a value of 0x02 to address 0x07 in the following illustration.

The example ADBM-A350 address is 0x57.

Figure 17. TWI write

## **Example: Single Byte Read from Sensor Register**

The sensor reads a value 0x01 from the register address 0x02 in the following illustration. Again, the example ADBM-A350 address is 0x57.

|                  | ADBS<br>Addre | ss 0 x 57 | Reg<br>0 x ( | jister Addre<br>02 | ss            | <br>          |                   |

|------------------|---------------|-----------|--------------|--------------------|---------------|---------------|-------------------|

| Packet<br>number |               | 1         |              | 2                  |               | <br>          |                   |

| Packet<br>type   |               | DA        | :[           | RA                 | · - · - · - · | <br>. <b></b> |                   |

|                  | 7             | 0         | 7            | 0                  |               |               |                   |

| SDA<br>host      | START 1010    | 0111 0    | 0            | 0000010            |               | <br>          | – . – . – . – . – |

|                  |               | R/W       | ai           |                    |               |               |                   |

| SDA<br>ADBS      |               | ACH       |              |                    | ACK           | <br>          |                   |

|                  |               |           |              |                    |               |               |                   |

|                  |       | ADBS<br>Address 0 x | 57       |                  | Data 0 x 01 |     |            |                       |                |                        |             |   |

|------------------|-------|---------------------|----------|------------------|-------------|-----|------------|-----------------------|----------------|------------------------|-------------|---|

| Packet<br>number |       | 3                   |          | - · <b>-</b> · · | 4           | ]   |            |                       | . <b>_</b>     |                        | ·· <b>-</b> |   |

|                  |       |                     |          |                  |             |     |            |                       |                |                        | Host could  |   |

| Packet<br>type   |       | DA                  |          | <b>.</b>         | DP          | ]:_ | · <b>-</b> |                       | · <b>–</b> · · |                        | also drive  |   |

|                  |       | 7                   | 0        |                  |             |     |            |                       |                |                        | START       |   |

| SDA<br>host      | START | 1010 111            | 1        | <b>–</b>         |             | N/  | AK         | STOP                  | <br>           | - · - · -<br>- · - · - | condition   | 2 |

|                  |       | R                   | /W       |                  | 7           | 0   |            |                       |                |                        | STOP        | u |

| SDA<br>ADBS      |       |                     | <u> </u> | ACK              | 00000001    | ]:_ | · <b>-</b> | · <b>-</b> · <b>-</b> | · <b>–</b> · · |                        | condition   |   |

Figure 18. TWI single byte read

## **Example: Polling of Status register (X-Y Motion Bit and Button bits)**

To poll the STATUS register, the following structure can be used:

|                  |       | ADBS<br>Address 0 x | ι 57         |     | I        | Register<br>Address 0 x | 02  |             |                         |  |

|------------------|-------|---------------------|--------------|-----|----------|-------------------------|-----|-------------|-------------------------|--|

| Packet<br>number |       | 1                   |              | [   |          | 2                       |     |             | · <b>-</b> · <b>-</b> · |  |

| Packet<br>type   |       | DA                  |              | [   |          | RA                      |     | ·-·-        | · — · — ·               |  |

|                  |       | 7                   | 0            |     | 7        | 0                       |     |             |                         |  |

| SDA<br>host      | START | 1010111             | 0            |     | 0        | 0000010                 |     |             | . <b></b>               |  |

|                  |       | F                   | R/W          |     | ai       |                         |     |             |                         |  |

| SDA<br>Adbs      |       |                     | <b>-</b> · · | ACK | <u> </u> |                         | ACK | ]. <b>_</b> | · <b>-</b> · <b>-</b> · |  |

|                  |       | ADBS Address<br>0 x 57 |                 | ADBS<br>STATUS<br>register |               | ADBS<br>STATUS<br>register |     |      |                                              |

|------------------|-------|------------------------|-----------------|----------------------------|---------------|----------------------------|-----|------|----------------------------------------------|

| Packet<br>number |       | 3                      | [: <u>-</u> ::] | 4                          |               | 5                          | ]   |      |                                              |

| Packet<br>type   |       | DA                     | [: <u>-</u> :]  | DP                         | : <u>-</u> :- | DP                         | ]   |      | Host could<br>also drive<br>another<br>START |

| SDA<br>host      | START | 1010111 1              | [: <u>-</u> :   | - · - · - · - · - · - · -  | ACK           | ]                          | NAK | STOP | condition<br>instead of a                    |

|                  |       | R/W                    | '               | 7 0                        |               | 7 0                        |     |      | STOP                                         |

| SDA<br>ADBS      |       |                        | ACK             | 00000000                   | <br>          | 00010001                   | ]   |      | condition                                    |

Figure 19. TWI polling

In this case, the host read ADBM-A350 data packets until the update bit (bit 4). Then the host could read successive registers using the ai bit example below.

Note: polling the Status register rather than using the DATA\_RDY pin increases power consumption

## Example: Multiple-Byte Read from Sensor Register using 'ai' bit

The ai is a useful feature, especially in the case of reading Delta\_X, Delta\_Y, and Delta\_HI in succession once either the DATA\_RDY interrupt pin and/or update bit in the STATUS register bit are set.

Once the ai bit is set, the slave will deliver data packets from successive addresses until the 'STOP' condition from the host.

In the example below, 3 bytes are read successively from registers 0x03, 0x04, and 0x05.

|                  |       | ADBS Addr<br>0 x 57 | ess      |     |     | gister Addr<br>: 03            | ess         |              |      |

|------------------|-------|---------------------|----------|-----|-----|--------------------------------|-------------|--------------|------|

| Packet<br>number |       | 1                   |          |     |     | 2                              | ]:_:_       |              | <br> |

|                  |       |                     |          |     |     |                                |             |              |      |

| Packet<br>type   |       | DA                  |          |     |     | RA                             | ]           |              | <br> |

|                  |       | 7                   | 0        |     | 7   | 0                              |             |              |      |

| SDA<br>host      | START | 1010111             | 0        |     | 1   | 0000011                        | ]: <u> </u> |              | <br> |

|                  |       | R                   | /W       |     | ai  |                                |             |              | <br> |

| SDA<br>Adbs      |       | · — · — · — · ·     | <u> </u> | ACK | I., | - · - · - · -<br>- · - · - · - | ACK         | ). <b></b> . | <br> |

|                  |       | ADBS<br>Address 0 x             | 57        |               | ADBS Data<br>from address<br>0 x 03 |       | ADBS Data<br>from address<br>0 x 04 |     | ADBS Data<br>from address<br>0 x 05 |                |      |                          |

|------------------|-------|---------------------------------|-----------|---------------|-------------------------------------|-------|-------------------------------------|-----|-------------------------------------|----------------|------|--------------------------|

| Packet<br>number |       | 3                               | $\coprod$ | . <u> </u>    | 4                                   | ]     | 5                                   | ]   | 6                                   | I: <u>-</u> :: |      |                          |

| Packet<br>type   |       | DA                              | $\Box$    | : <u>-</u> :] | DP                                  | ]:_:_ | DP                                  | ]   | DP                                  | I:_:           |      | Host could<br>also drive |

| SDA              |       | 7                               | 0_        |               |                                     |       |                                     |     |                                     |                | _    | another<br>START         |

| host             | START | 1010111                         | 1         |               |                                     | ACK   |                                     | ACK |                                     | NAK            | STOP | condition                |

|                  |       | R                               | /W        |               | 7 0                                 |       | 7 0                                 |     |                                     |                |      | instead of a             |

| SDA<br>ADBS      |       | · <b>-</b> · <b>-</b> · - · - · | <u> </u>  | ACK           | 10101101                            | ]:_:_ | 0000001                             | ]   | 10000101                            | [: <u>-</u> :: | -    | STOP condition           |

Figure 20. TWI ai bit

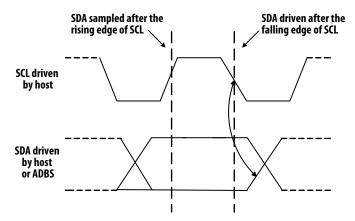

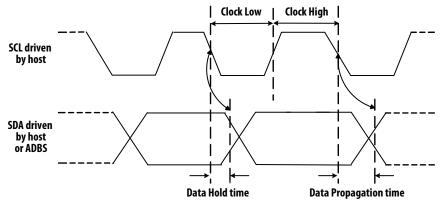

## **SCL and SDA Timing**

Figure 21. TWI SCL and SDA Timing

### ADBM-A350 driven SDA

Figure 22. Sensor driven SDA

Registers

The ADBM-A350 registers are accessible via the serial port. The registers are used to read motion data and status as well as to set the device configuration.

| Address       | Register            | Read/<br>Write | Default<br>Value | Address   | Register         | Read/<br>Write | Default<br>Value |

|---------------|---------------------|----------------|------------------|-----------|------------------|----------------|------------------|

| 0x00          | Product_ID          | R              | 0x88             | 0x40-0x5f | Reserved         |                |                  |

| 0x01          | Revision_ID         | R              | 0x00             | 0x60      | OFN_Engine1      | R/W            | 0x84             |

| 0x02          | EVENT               | R/W            | Any              | 0x61      | OFN_Engine2      | R/W            | 0x89             |

| 0x03          | Delta_X             | R              | Any              | 0x62      | Resolution       | R/W            | 0x22             |

| 0x04          | Delta_Y             | R              | Any              | 0x63      | Speed_Ctrl       | R/W            | 0x0e             |

| 0x05          | SQUAL               | R              | Any              | 0x64      | Speed_ST12       | R/W            | 0x08             |

| 0x06          | Shutter_Upper       | R              | Any              | 0x65      | Speed_ST21       | R/W            | 0x06             |

| 0x07          | Shutter_Lower       | R              | Any              | 0x66      | Speed_ST23       | R/W            | 0x40             |

| 0x08          | Maximum_Pixel       | R              | Any              | 0x67      | Speed_ST32       | R/W            | 0x08             |

| 0x09          | Pixel_Sum           | R              | Any              | 0x68      | Speed_ST34       | R/W            | 0x48             |

| 0x0a          | Minimum_Pixel       | R              | Any              | 0x69      | Speed_ST43       | R/W            | 0x0a             |

| 0x0b          | Pixel_Grab          | R/W            | Any              | 0х6а      | Speed_ST45       | R/W            | 0x50             |

| 0х0с          | CRC0                | R              | 0x00             | 0x6b      | Speed_ST54       | R/W            | 0x48             |

| 0x0d          | CRC1                | R              | 0x00             | 0х6с      | GPIO_CTRL        | R/W            | 0x80             |

| 0x0e          | CRC2                | R              | 0x00             | 0x6d      | AD_CTRL          | R/W            | 0xc4             |

| 0x0f          | CRC3                | R              | 0x00             | 0x6e      | AD_ATH_HIGH      | R/W            | 0x3a             |

| 0x10          | Self_Test           | W              | 0x00             | 0x6f      | AD_DTH_HIGH      | R/W            | 0x40             |

| 0x11          | Reserved            |                |                  | 0x70      | AD_ATH_LOW       | R/W            | 0x35             |

| 0x12          | BUTTON_STATUS       | R/W            | 0x00             | 0x71      | AD_DTH_LOW       | R/W            | 0x3b             |

| 0x13          | Run_Downshift       | R/W            | 0x04             | 0x72      | QUANTIZE_CTRL    | R/W            | 0x99             |

| 0x14          | Rest1_Period        | R/W            | 0x01             | 0x73      | XYQ_THRESH       | R/W            | 0x02             |

| 0x15          | Rest1_Downshift     | R/W            | 0x1f             | 0x74      | MOTION_CTRL      | R/W            | 0x00             |

| 0x16          | Rest2_Period        | R/W            | 0x09             | 0x75      | FPD_CTRL         | R/W            | 0xfa             |

| 0x17          | Rest2_Downshift     | R/W            | 0x2f             | 0x76      | FPD_THRESH       | R/W            | 0x2c             |

| 0x18          | Rest3_Period        | R/W            | 0x31             | 0x77      | ORIENT_CTRL      | R/W            | 0x00             |

| 0x19          | Reserved            |                |                  | 0x78      | FPD_SQUAL_THRESH | R/W            | 0x40             |

| 0x1a          | LED_CTRL            | R/W            | 0x00             | 0x79      | FPD_VALUE        | R/W            | 0x00             |

| 0x1b          | Reserved            |                |                  | 0x7a      | FPD_STATUS       | R              | 0x20             |

| 0x1c          | IO_Mode             | R/W            | 0x00             | 0x7b      | SC_CTRL          | R/W            | 0x25             |

| 0x1d          | EVENT_CTRL          | R/W            | 0x04             | 0x7c      | SC_T_TAPNHOLD    | R/W            | 0x45             |

| 0x28          | Fast_Video_Dump     | R/W            | 0x00             | 0x7d      | SC_T_DOUBLE      | R/W            | 0x1e             |

| 0x2e          | Observation         | R/W            | Any              | 0x7e      | SC_DELTA_THRESH  | R/W            | 0x19             |

| 0x31          | Pad_Status          | R              | 0x00             | 0x7f      | SC_STATUS        | R/W            | 0x00             |

| 0x32          | Reserved            |                |                  |           |                  |                |                  |

| 0x33          | Pad_Test_Out        | RW             | 0x00             |           |                  |                |                  |

| 0x34          | Pad_Function        | W              | 0x00             |           |                  |                |                  |

| 0x3a          | SOFT_RESET          | W              | 0x00             |           |                  |                |                  |

| 0x3b          | Shutter_Max_Hi      | R/W            | 0x0b             |           |                  |                |                  |

| 0x3c          | Shutter_Max_Lo      | R/W            | 0x71             |           |                  |                |                  |

| 0x3d          | Reserved            |                |                  |           |                  |                |                  |

| 0x3e          | Inverse_Revision_ID | R              | 0xFF             |           |                  |                |                  |

| $\overline{}$ |                     | R              | 0x77             |           |                  |                |                  |