Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 3-Channel, Isolated, Sigma-Delta ADC with SPI

**Data Sheet**

ADE7912/ADE7913

#### **FEATURES**

Two (ADE7912) or three (ADE7913) isolated, Σ-Δ analog-todigital converters (simultaneously sampling ADCs) Integrated *iso*Power, isolated dc-to-dc converter On-chip temperature sensor 4-wire SPI serial interface Up to 4 ADE7912/ADE7913 devices clocked from a single

crystal or an external clock

Synchronization of multiple ADE7912/ADE7913 devices ±31.25 mV peak input range for current channel ±500 mV peak input range for voltage channels Reference drift: 10 ppm/°C typical

Single 3.3 V supply

20-lead, wide-body SOIC package with 8.3 mm creepage

Operating temperature: -40°C to +85°C Safety and regulatory approvals

UL recognition

5000 V rms for 1 minute per UL 1577 CSA Component Acceptance Notice 5A IEC 61010-1: 300 V rms

VDE certificate of conformity

DIN VDE V 0884-10 (VDE V 0884-10):2006-12 V<sub>IORM</sub> = 846 V peak

### APPLICATIONS

Shunt-based polyphase meters

Power quality monitoring

Solar inverters

Process monitoring

Protective devices

Isolated sensor interfaces

Industrial PLCs

#### **GENERAL DESCRIPTION**

The ADE7912/ADE7913¹ are isolated, 3-channel  $\Sigma$ - $\Delta$  ADCs for polyphase energy metering applications using shunt current sensors. Data and power isolation are based on the Analog Devices, Inc., iCoupler $^{\circ}$  technology. The ADE7912 features two ADCs, and the ADE7913 features three ADCs. The current ADC provides a 67 dB signal-to-noise ratio (SNR) over a 3 kHz signal bandwidth, whereas the voltage ADCs provide an SNR of 72 dB over the same bandwidth. One channel is dedicated to measuring the voltage

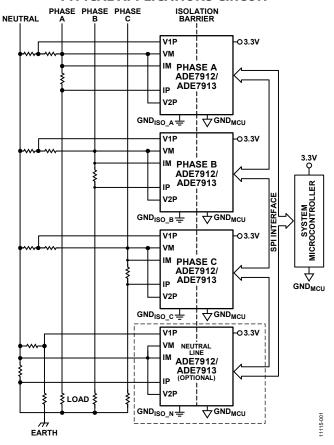

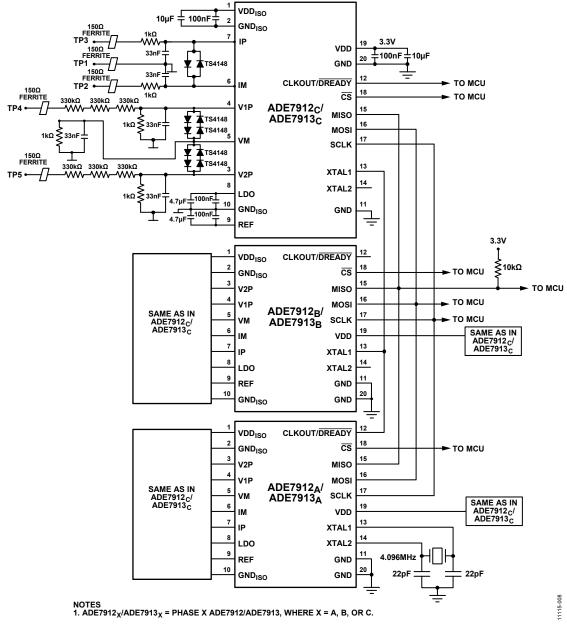

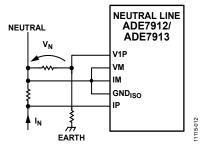

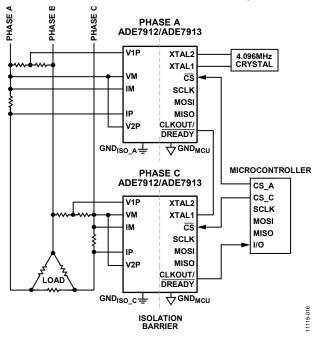

#### TYPICAL APPLICATIONS CIRCUIT

Figure 1.

across a shunt when the shunt is used for current sensing. Up to two additional channels are dedicated to measuring voltages, which are usually sensed using resistor dividers. One voltage channel can measure the temperature of the die via an internal sensor. The ADE7913 includes three channels: one current and two voltage channels. The ADE7912 has one voltage channel but is otherwise identical to the ADE7913.

Trademarks and registered trademarks are the property of their respective owners.

Protected by U.S. Patents 5,952,849; 6,873,065; 7,075,329; 6,262,600; 7,489,526; 7,558,080; 8,892,933. Other patents are pending.

| TA | DΙ | C ( | וו | C ( | P | NI | UΤ         |   | N٦ | C |

|----|----|-----|----|-----|---|----|------------|---|----|---|

| IA | DL | E ( | UI | Г   | U | UΙ | <b>1</b> I | L | v  | J |

| Features                                                                  | Temperature Sensor                                                           | 21 |

|---------------------------------------------------------------------------|------------------------------------------------------------------------------|----|

| Applications1                                                             | Protecting the Integrity of Configuration Registers                          | 21 |

| Typical Applications Circuit1                                             | CRC of Configuration Registers                                               | 21 |

| General Description1                                                      | ADE7912/ADE7913 Status                                                       | 22 |

| Revision History                                                          | Insulation Lifetime                                                          | 22 |

| Functional Block Diagrams4                                                | Applications Information                                                     |    |

| Specifications                                                            | ADE7912/ADE7913 in Polyphase Energy Meters                                   |    |

| Regulatory Approvals                                                      | ADE7912/ADE7913 Clock                                                        |    |

|                                                                           |                                                                              |    |

| Insulation and Safety Related Specifications                              | SPI-Compatible Interface                                                     |    |

| DIN V VDE V 0884-10 (VDE V 0884-10):2006-12 Insulation<br>Characteristics | Synchronizing Multiple ADE7912/ADE7913 Devices                               |    |

|                                                                           | Power Management                                                             |    |

| Timing Characteristics 9                                                  | DC-to-DC Converter                                                           | 31 |

| Absolute Maximum Ratings10                                                | Magnetic Field Immunity                                                      | 32 |

| Thermal Resistance                                                        | Power-Up and Initialization Procedures                                       | 33 |

| ESD Caution                                                               | Hardware Reset                                                               | 36 |

| Pin Configuration and Function Descriptions11                             | Software Reset                                                               | 36 |

| Typical Performance Characteristics                                       | Power-Down Mode                                                              | 36 |

| Test Circuit                                                              | Layout Guidelines                                                            |    |

| Terminology 16                                                            | ADE7913 Evaluation Board                                                     |    |

| Theory of Operation18                                                     |                                                                              |    |

| Analog Inputs18                                                           | ADE7912/ADE7913 Version                                                      |    |

| Analog-to-Digital Conversion                                              | Register List                                                                |    |

|                                                                           | Outline Dimensions                                                           |    |

| Reference Circuit                                                         | Ordering Guide                                                               | 41 |

| CRC of ADC Output Values20                                                |                                                                              |    |

| REVISION HISTORY                                                          |                                                                              |    |

| 8/2016—Rev. A to Rev. B                                                   | Changes to Pin 15 Description, Table 9                                       |    |

| Added Patent Note, Note 1                                                 | Changes to Figure 9 and Figure 11                                            |    |

| Change to Table 9                                                         | Changes to Terminology Section                                               |    |

| Change to Figure 12                                                       | Changes to ADC Transfer Function Section and CRC of Al Output Values Section |    |

| Changes to DC-to-DC Converter Section                                     | Changes to Temperature Sensor Section                                        |    |

| 4/2015—Rev. 0 to Rev. A                                                   | Changes to Insulation Lifetime Section                                       |    |

| Changes to Features Section and General Description Section 1             | Deleted Figure 31; Renumbered Sequentially                                   |    |

| Changes Table 15                                                          | Changes to SPI-Compatible Interface Section                                  |    |

| Changed Regulatory Approvals (Pending) Section to Regulatory              | Changes to SPI Read Operation in Burst Mode Section                          |    |

| Approvals Section                                                         | Changes to Power-Down Mode Section                                           |    |

| Changes to Regulatory Approvals Section, Table 2, and Tracking            | Changes to Layout Guidelines Section                                         |    |

| Resistance (Comparative Tracking Index) Parameter, Table 3 7              | Deleted Figure 54                                                            |    |

| Changed DIN V VDE V 0884-10 (VDE V 0884-10) Insulation                    | Deleted Figure 55 and Figure 56                                              |    |

| Characteristics Section to DIN V VDE V 0884-10 (VDE V                     | Deleted Figure 57 and Figure 58                                              |    |

| 0884-10):2006-12 Insulation Characteristics Section 8                     | Deleted Figure 59 and Figure 60                                              |    |

| Changes to Table 4 and Figure 48                                          | - v                                                                          |    |

| Changes to Table 810                                                      | 11/2013—Revision 0: Initial Version                                          |    |

The ADE7912/ADE7913 include *iso*Power\*, an integrated, isolated dc-to-dc converter. Based on the Analog Devices *i*Coupler technology, the dc-to-dc converter provides the regulated power required by the first stage of the ADCs at a 3.3 V input supply. *iso*Power eliminates the need for an external dc-to-dc isolation block. The *i*Coupler chip scale transformer technology also isolates the logic signals between the first and second stages of the ADC. The result is a small form factor, total isolation solution.

The ADE7912/ADE7913 configuration and status registers are accessed via a bidirectional SPI serial port for easy interfacing with microcontrollers.

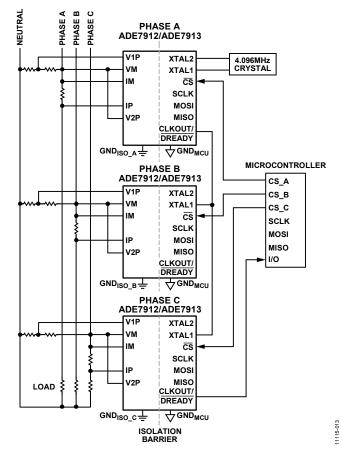

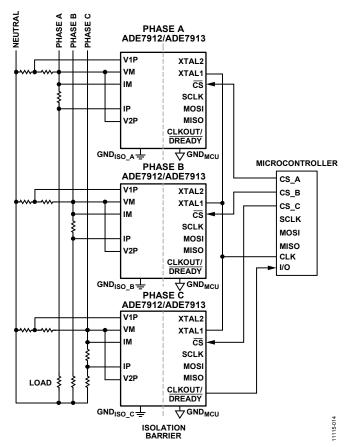

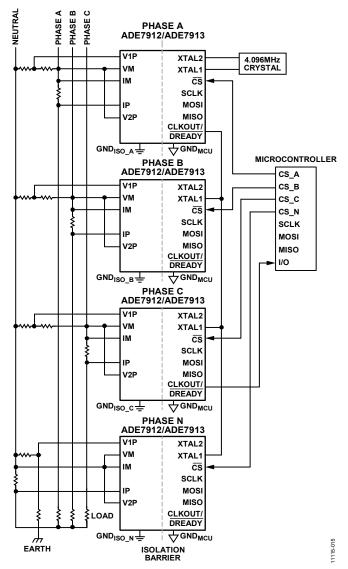

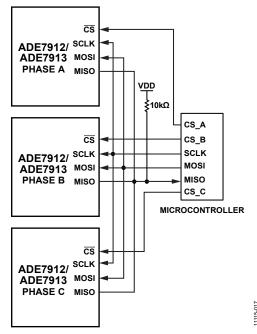

The ADE7912/ADE7913 can be clocked from a crystal or an external clock signal. To minimize the system bill of materials, the master ADE7912/ADE7913 can drive the clocks of up to three additional ADE7912/ADE7913 devices.

Multiple ADE7912/ADE7913 devices can be synchronized to sample at the same moment and provide coherent outputs.

The ADE7912/ADE7913 are available in a 20-lead, Pb-free, wide-body SOIC package with 8.3 mm creepage.

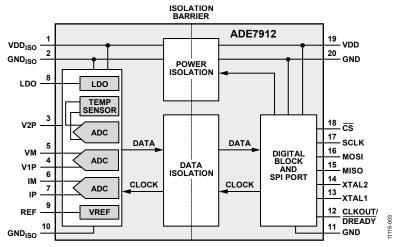

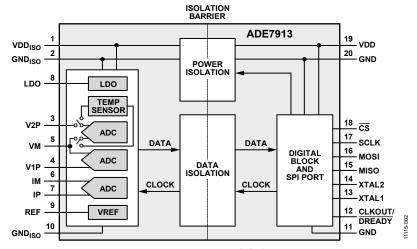

# **FUNCTIONAL BLOCK DIAGRAMS**

Figure 2. ADE7912 Functional Block Diagram

Figure 3. ADE7913 Functional Block Diagram

# **SPECIFICATIONS**

$VDD = 3.3~V \pm 10\%, GND = 0~V, on\text{-}chip~reference, XTAL1 = 4.096~MHz, T_{MIN}~to~T_{MAX} = -40^{\circ}C~to~+85^{\circ}C, T_{A} = 25^{\circ}C~(typical).$

Table 1.

| Parameter                                                                                          | Min    | Тур  | Max    | Unit    | Test Conditions/Comments                                                                                                                                                         |

|----------------------------------------------------------------------------------------------------|--------|------|--------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ANALOG INPUTS <sup>1</sup>                                                                         |        |      |        |         |                                                                                                                                                                                  |

| Pseudo Differential Signal Voltage Range<br>Between IP and IM Pins                                 | -31.25 |      | +31.25 | mV peak | IM pin connected to GND <sub>IsO</sub>                                                                                                                                           |

| Pseudo Differential Signal Voltage Range<br>Between V1P and VM Pins and Between<br>V2P and VM Pins | -500   |      | +500   | mV peak | Pseudo differential inputs between V1P and VM pins and between V2P and VM pins; VM pin connected to GND <sub>ISO</sub>                                                           |

| Maximum VM and IM Voltage                                                                          | -25    |      | +25    | mV      |                                                                                                                                                                                  |

| Crosstalk                                                                                          |        | -90  |        | dB      | IP and IM inputs set to 0 V (GND <sub>ISO</sub> ) when V1P and V2P inputs at full scale                                                                                          |

|                                                                                                    |        | -105 |        | dB      | V2P and VM inputs set to 0 V (GND <sub>ISO</sub> ) when IP and V1P inputs at full scale; V1P and VM inputs set to 0 V (GND <sub>ISO</sub> ) when IP and V2P inputs at full scale |

| Input Impedance to GND <sub>ISO</sub> (DC)                                                         |        |      |        |         |                                                                                                                                                                                  |

| IP, IM, V1P, and V2P Pins                                                                          | 480    |      |        | kΩ      |                                                                                                                                                                                  |

| VM Pin                                                                                             | 240    |      |        | kΩ      |                                                                                                                                                                                  |

| Current Channel ADC Offset Error                                                                   |        | -2   |        | mV      |                                                                                                                                                                                  |

| Voltage Channels ADC Offset Error                                                                  |        | -35  |        | mV      | V2 channel applies to the ADE7913 only                                                                                                                                           |

| ADC Offset Drift over Temperature                                                                  |        | ±200 |        | ppm/°C  | V1 channel only                                                                                                                                                                  |

| Gain Error                                                                                         | -4     |      | +4     | %       |                                                                                                                                                                                  |

| Gain Drift over Temperature                                                                        | -135   |      | +135   | ppm/°C  | Current channel                                                                                                                                                                  |

|                                                                                                    | -85    |      | +85    | ppm/°C  | V1 and V2 channels                                                                                                                                                               |

| AC Power Supply Rejection (PSR)                                                                    |        | -90  |        | dB      | VDD = 3.3 V + 120 mV rms (50 Hz/100 Hz),<br>IP = V1P = V2P = GND <sub>ISO</sub>                                                                                                  |

| DC Power Supply Rejection (PSR)                                                                    |        | -80  |        | dB      | VDD = 3.3 V ± 330 mV dc, IP = 6.25 mV rms, V1P = V2P = 100 mV rms                                                                                                                |

| TEMPERATURE SENSOR                                                                                 |        |      |        |         |                                                                                                                                                                                  |

| Accuracy                                                                                           |        | ±5   |        | °C      |                                                                                                                                                                                  |

| WAVEFORM SAMPLING—CURRENT CHANNEL <sup>1</sup>                                                     |        |      |        |         |                                                                                                                                                                                  |

| Signal-to-Noise Ratio (SNR)                                                                        |        | 67   |        | dBFS    | ADC_FREQ = 8 kHz, BW = 3300 Hz                                                                                                                                                   |

|                                                                                                    |        | 68   |        | dBFS    | ADC_FREQ = 8 kHz, BW = 2000 Hz                                                                                                                                                   |

|                                                                                                    |        | 72   |        | dBFS    | ADC_FREQ = 2 kHz, BW = 825 Hz                                                                                                                                                    |

|                                                                                                    |        | 74   |        | dBFS    | $ADC_FREQ = 2 \text{ kHz}, BW = 500 \text{ Hz}$                                                                                                                                  |

| Signal-to-Noise-and-Distortion Ratio (SINAD)                                                       |        | 66   |        | dBFS    | ADC_FREQ = 8 kHz, BW = 3300 Hz                                                                                                                                                   |

|                                                                                                    |        | 68   |        | dBFS    | ADC_FREQ = 8 kHz, BW = 2000 Hz                                                                                                                                                   |

|                                                                                                    |        | 72   |        | dBFS    | $ADC_FREQ = 2 \text{ kHz}, BW = 825 \text{ Hz}$                                                                                                                                  |

|                                                                                                    |        | 73   |        | dBFS    | $ADC_FREQ = 2 \text{ kHz}, BW = 500 \text{ Hz}$                                                                                                                                  |

| Total Harmonic Distortion (THD)                                                                    |        | -79  |        | dBFS    | ADC_FREQ = 8 kHz, BW = 3300 Hz                                                                                                                                                   |

|                                                                                                    |        | -78  |        | dBFS    | ADC_FREQ = 8 kHz, BW = 2000 Hz                                                                                                                                                   |

|                                                                                                    |        | -82  |        | dBFS    | $ADC_FREQ = 2 \text{ kHz}, BW = 825 \text{ Hz}$                                                                                                                                  |

|                                                                                                    |        | -82  |        | dBFS    | $ADC_FREQ = 2 \text{ kHz}, BW = 500 \text{ Hz}$                                                                                                                                  |

| Spurious-Free Dynamic Range (SFDR)                                                                 |        | 83   |        | dBFS    | ADC_FREQ = 8 kHz, BW = 3300 Hz                                                                                                                                                   |

|                                                                                                    |        | 83   |        | dBFS    | $ADC_FREQ = 8 \text{ kHz}, BW = 2000 \text{ Hz}$                                                                                                                                 |

|                                                                                                    |        | 85   |        | dBFS    | $ADC_FREQ = 2 \text{ kHz}, BW = 825 \text{ Hz}$                                                                                                                                  |

|                                                                                                    |        | 85   |        | dBFS    | ADC_FREQ = 2 kHz, BW = 500 Hz                                                                                                                                                    |

| VOLTAGE CHANNELS <sup>1</sup>                                                                      |        |      |        |         |                                                                                                                                                                                  |

| Signal-to-Noise Ratio (SNR)                                                                        |        | 72   |        | dBFS    | ADC_FREQ = 8 kHz, BW = 3300 Hz                                                                                                                                                   |

|                                                                                                    |        | 74   |        | dBFS    | ADC_FREQ = 8 kHz, BW = 2000 Hz                                                                                                                                                   |

|                                                                                                    |        | 77   |        | dBFS    | ADC_FREQ = 2 kHz, BW = 825 Hz                                                                                                                                                    |

|                                                                                                    |        | 79   |        | dBFS    | $ADC_FREQ = 2 \text{ kHz}, BW = 500 \text{ Hz}$                                                                                                                                  |

| Parameter                                    | Min  | Тур   | Max  | Unit | Test Conditions/Comments                                                       |

|----------------------------------------------|------|-------|------|------|--------------------------------------------------------------------------------|

| Signal-to-Noise-and-Distortion Ratio (SINAD) |      | 72    |      | dBFS | ADC_FREQ = 8 kHz, BW = 3300 Hz                                                 |

|                                              |      | 74    |      | dBFS | ADC_FREQ = 8 kHz, BW = 2000 Hz                                                 |

|                                              |      | 77    |      | dBFS | ADC_FREQ = 2 kHz, BW = 825 Hz                                                  |

|                                              |      | 78    |      | dBFS | ADC_FREQ = 2 kHz, BW = 500 Hz                                                  |

| Total Harmonic Distortion (THD)              |      | -83   |      | dBFS | ADC_FREQ = 8 kHz, BW = 3300 Hz                                                 |

|                                              |      | -83   |      | dBFS | ADC_FREQ = 8 kHz, BW = 2000 Hz                                                 |

|                                              |      | -85   |      | dBFS | ADC_FREQ = 2 kHz, BW = 825 Hz                                                  |

|                                              |      | -85   |      | dBFS | ADC_FREQ = 2 kHz, BW = 500 Hz                                                  |

| Spurious-Free Dynamic Range (SFDR)           |      | 86    |      | dBFS | ADC_FREQ = 8 kHz, BW = 3300 Hz                                                 |

|                                              |      | 86    |      | dBFS | ADC_FREQ = 8 kHz, BW = 2000 Hz                                                 |

|                                              |      | 87    |      | dBFS | ADC_FREQ = 2 kHz, BW = 825 Hz                                                  |

|                                              |      | 87    |      | dBFS | ADC_FREQ = 2 kHz, BW = 500 Hz                                                  |

| CLKIN <sup>2</sup>                           |      |       |      |      | All specifications for CLKIN = 4.096 MHz                                       |

| Input Clock Frequency, CLKIN                 | 3.6  | 4.096 | 4.21 | MHz  |                                                                                |

| CLKIN Duty Cycle                             | 45   | 50    | 55   | %    |                                                                                |

| XTAL1 Logic Inputs                           |      |       |      |      |                                                                                |

| Input High Voltage, V <sub>INH</sub>         | 2.4  |       |      | V    |                                                                                |

| Input Low Voltage, V <sub>INL</sub>          |      |       | 0.8  | V    |                                                                                |

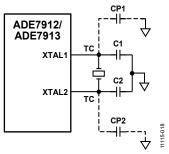

| XTAL1 Total Capacitance <sup>3</sup>         |      | 40    |      | pF   |                                                                                |

| XTAL2 Total Capacitance <sup>3</sup>         |      | 40    |      | pF   |                                                                                |

| CLKOUT Delay from XTAL1 <sup>4</sup>         |      |       | 100  | ns   |                                                                                |

| LOGIC INPUTS—MOSI, SCLK, CS                  |      |       |      |      |                                                                                |

| Input High Voltage, V <sub>INH</sub>         | 2.4  |       |      | V    |                                                                                |

| Input Low Voltage, V <sub>INL</sub>          |      |       | 0.8  | V    |                                                                                |

| Input Current, I <sub>IN</sub>               |      | 0.015 | 1    | μΑ   |                                                                                |

| Input Capacitance, C <sub>IN</sub>           |      |       | 10   | pF   |                                                                                |

| LOGIC OUTPUTS—CLKOUT/DREADY AND MISO         |      |       |      |      |                                                                                |

| Output High Voltage, V <sub>OH</sub>         | 2.5  |       |      | V    | I <sub>SOURCE</sub> = 800 μA                                                   |

| Output Low Voltage, V <sub>OL</sub>          |      |       | 0.4  | V    | $I_{SINK} = 2 \text{ mA}$                                                      |

| POWER SUPPLY                                 |      |       |      |      | For specified performance                                                      |

| VDD Pin                                      | 2.97 |       | 3.63 | V    | Minimum = 3.3 V – 10%; maximum = 3.3 V + 10%                                   |

| I <sub>DD</sub>                              |      | 12.5  | 19   | mA   | Bit 2 (PWRDWN_EN) in CONFIG register cleared to 0                              |

|                                              | 1    | 2.7   | 3    | mA   | Bit 2 (PWRDWN_EN) in CONFIG register set to 1                                  |

|                                              |      | 50    |      | μΑ   | Bit 2 (PWRDWN_EN) in CONFIG register set to 1 and no CLKIN signal at XTAL1 pin |

<sup>&</sup>lt;sup>1</sup> See the Terminology section for a definition of the parameters. <sup>2</sup> CLKIN is the internal clock of the ADE7912/ADE7913. It is the frequency at which the part is clocked at the XTAL1 pin.

<sup>&</sup>lt;sup>3</sup> XTAL1/XTAL2 total capacitances refer to the net capacitances on each pin. Each capacitance is the sum of the parasitic capacitance at the pin and the capacitance of

the ceramic capacitor connected between the pin and GND. See the ADE7912/ADE7913 Clock section for more details.

4 CLKOUT delay from XTAL1 is the delay that occurs from a high to low transition at the XTAL1 pin to a synchronous high to low transition at the CLKOUT/DREADY pin when CLKOUT functionality is enabled.

#### **REGULATORY APPROVALS**

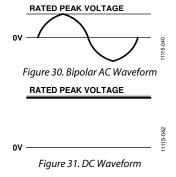

The ADE7912/ADE7913 are approved by the organizations listed in Table 2. Refer to Table 8 and the Insulation Lifetime section for more information about the recommended maximum working voltages for specific cross-isolation waveforms and insulation levels.

Note that Table 8 presents the maximum working voltages for 50-year minimum lifetime: 400 V rms for ac voltages and 1173 V peak for dc voltages. Greater working voltages shorten the lifetime of the product (see the Insulation Lifetime section). Some certifications in Table 2 state greater maximum working voltages than the values presented in Table 8. Therefore, use the ADE7912/ADE7913 only for working voltages lower than those presented in Table 8 (400 V rms for ac voltages and 1173 V peak for dc voltages).

**Table 2. Regulatory Approvals**

| UL                                                                        | CSA                                                                                                                                                      | VDE                                                                           |

|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| Recognized Under UL 1577<br>Component Recognition<br>Program <sup>1</sup> | Approved under CSA Component Acceptance Notice 5A                                                                                                        | Certified according to DIN VDE V 0884-10 <sup>2</sup> (VDE V 0884-10):2006-12 |

| Single Protection, 5000 V rms<br>Isolation Voltage                        | Basic insulation per CSA 60950-1-07+A1+A2 and IEC 60950-1<br>2 <sup>nd</sup> Ed.+A1+A2:                                                                  | Reinforced insulation, 846 V peak <sup>4</sup>                                |

|                                                                           | 830 V rms (1173 V peak) maximum working voltage <sup>3</sup> Basic insulation per CSA 61010-1-12 and IEC 61010-1 3 <sup>rd</sup> Ed.                     |                                                                               |

|                                                                           | (Pollution Degree 2, Material Group III, Overvoltage Category II, III, and IV):                                                                          |                                                                               |

|                                                                           | 300 V rms (424 V peak) maximum working voltage.                                                                                                          |                                                                               |

|                                                                           | Reinforced insulation per CSA 60950-1-07+A1+A2 and IEC 60950-1 2 <sup>nd</sup> Ed.+A1+A2:                                                                |                                                                               |

|                                                                           | 415 V rms (586 V peak) maximum working voltage                                                                                                           |                                                                               |

|                                                                           | Reinforced insulation per CSA 61010-1-12 and IEC 61010-1 3 <sup>rd</sup> Ed. (Pollution Degree 2, Material Group III, Overvoltage Category II, and III): |                                                                               |

|                                                                           | 300 V rms (424 V peak) maximum working voltage.                                                                                                          |                                                                               |

| FILE E214100                                                              | FILE 2758945                                                                                                                                             | FILE 2471900-4880-0001                                                        |

<sup>&</sup>lt;sup>1</sup> In accordance with UL 1577, each ADE7912/ADE7913 is proof tested by applying an insulation test voltage ≥ 6000 V rms for 1 second (current leakage detection limit = 15 μA).

#### **INSULATION AND SAFETY RELATED SPECIFICATIONS**

Table 3. Critical Safety Related Dimensions and Material Properties

| Parameter                                        | Symbol | Value     | Unit  | Test Conditions/Comments                                                                                                                        |

|--------------------------------------------------|--------|-----------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Rated Dielectric Insulation Voltage              |        | 5000      | V rms | 1-minute duration                                                                                                                               |

| Minimum External Air Gap (Clearance)             | L(I01) | 8.3       | mm    | Distance measured from input terminals to output terminals, shortest distance through air along the PCB mounting plane, as an aid to PCB layout |

| Minimum External Tracking (Creepage)             | L(l02) | 8.3       | mm    | Measured from input terminals to output terminals, shortest distance path along body                                                            |

| Minimum Internal Gap (Internal Clearance)        |        | 0.017 min | mm    | Insulation distance through insulation                                                                                                          |

| Tracking Resistance (Comparative Tracking Index) | CTI    | 400       | V     | IEC 60112                                                                                                                                       |

| Isolation Group                                  |        | II        |       | Material group (DIN VDE 0110, 1/89, Table 1)                                                                                                    |

<sup>&</sup>lt;sup>2</sup> In accordance with DIN V VDE V 0884-10, each ADE7912/ADE7913 is proof tested by applying an insulation test voltage ≥ 1590 V peak for 1 second (partial discharge detection limit = 5 pC). The asterisk (\*) marking branded on the component designates DIN VDE V 0884-10 (VDE V 0884-10):2006-12 approval.

<sup>&</sup>lt;sup>3</sup> At this maximum working voltage, the approximate predicted lifetime is 0.2 years under 50 Hz, 60 Hz ac voltages.

<sup>&</sup>lt;sup>4</sup> At this maximum working voltage, the approximate predicted lifetime is 8 years under 50 Hz, 60 Hz ac voltages.

#### **DIN V VDE V 0884-10 (VDE V 0884-10):2006-12 INSULATION CHARACTERISTICS**

The ADE7912/ADE7913 are suitable for reinforced electrical isolation only within the safety limit data. Maintenance of the safety data is ensured by the protective circuits.

**Table 4. VDE Characteristics**

| Description                                               | Test Conditions/Comments                                                                                        | Symbol            | Characteristic | Unit   |

|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------|----------------|--------|

| Installation Classification per DIN VDE 0110              |                                                                                                                 |                   |                |        |

| For Rated Mains Voltage ≤ 150 V rms                       |                                                                                                                 |                   | I to IV        |        |

| For Rated Mains Voltage ≤ 300 V rms                       |                                                                                                                 |                   | I to IV        |        |

| For Rated Mains Voltage ≤ 400 V rms                       |                                                                                                                 |                   | l to III       |        |

| Climatic Classification                                   |                                                                                                                 |                   | 40/085/21      |        |

| Pollution Degree per DIN VDE 0110, Table 1                |                                                                                                                 |                   | 2              |        |

| Maximum Working Insulation Voltage                        |                                                                                                                 | VIORM             | 846            | V peak |

| Input-to-Output Test Voltage, Method B1                   | $V_{IORM} \times 1.875 = V_{pd(m)}$ , 100% production test, $t_{ini} = t_m = 1$ sec, partial discharge $< 5$ pC | $V_{pd(m)}$       | 1592           | V peak |

| Input-to-Output Test Voltage, Method A                    |                                                                                                                 | $V_{pd(m)}$       |                |        |

| After Environmental Tests Subgroup 1                      | $V_{IORM} \times 1.5 = V_{pd(m)}$ , $t_{ini} = 60$ sec, $t_m = 10$ sec, partial discharge $< 5$ pC              |                   | 1273           | V peak |

| After Input and/or Safety Tests Subgroup 2 and Subgroup 3 | $V_{IORM} \times 1.2 = V_{pd(m)}$ , $t_{ini} = 60$ sec, $t_m = 10$ sec, partial discharge $< 5$ pC              |                   | 1018           | V peak |

| Highest Allowable Overvoltage                             |                                                                                                                 | V <sub>IOTM</sub> | 6000           | V peak |

| Surge Isolation Voltage                                   | $V_{PEAK} = 10$ kV, 1.2 $\mu$ s rise time, 50 $\mu$ s, 50% fall time                                            | V <sub>IOSM</sub> | 6250           | V peak |

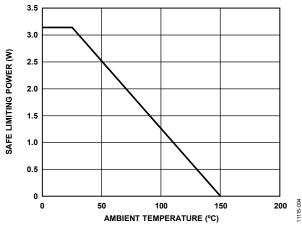

| Safety Limiting Values                                    | Maximum value allowed in the event of a failure (see Figure 4)                                                  |                   |                |        |

| Maximum Junction Temperature                              |                                                                                                                 | Ts                | 150            | °C     |

| Total Power Dissipation at 25°C                           |                                                                                                                 | Ps                | 2.78           | W      |

| Insulation Resistance at T <sub>s</sub>                   | $V_{10} = 500 \text{ V}$                                                                                        | Rs                | >109           | Ω      |

Figure 4. Thermal Derating Curve, Dependence of Safety Limiting Values on Case Temperature, per DIN V VDE V 0884-10

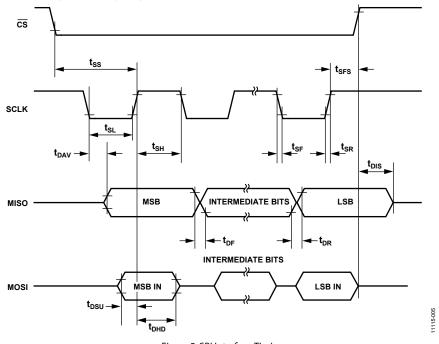

#### **TIMING CHARACTERISTICS**

$VDD = 3.3~V \pm 10\%, GND = 0~V, on\text{-chip reference, CLKIN} = 4.096~MHz, T_{MIN}~to~T_{MAX} = -40^{\circ}C~to~+85^{\circ}C.$

**Table 5. SPI Interface Timing Parameters**

| Parameter                              | Symbol           | Min | Max  | Unit |

|----------------------------------------|------------------|-----|------|------|

| CS to SCLK Positive Edge               | tss              | 50  |      | ns   |

| SCLK Frequency <sup>1</sup>            |                  | 250 | 5600 | kHz  |

| SCLK Low Pulse Width                   | t <sub>S</sub> ∟ | 80  |      | ns   |

| SCLK High Pulse Width                  | tsн              | 80  |      | ns   |

| Data Output Valid After SCLK Edge      | t <sub>DAV</sub> |     | 80   | ns   |

| Data Input Setup Time Before SCLK Edge | t <sub>DSU</sub> | 70  |      | ns   |

| Data Input Hold Time After SCLK Edge   | t <sub>DHD</sub> | 20  |      | ns   |

| Data Output Fall Time                  | t <sub>DF</sub>  |     | 20   | ns   |

| Data Output Rise Time                  | t <sub>DR</sub>  |     | 20   | ns   |

| SCLK Rise Time                         | t <sub>sr</sub>  |     | 20   | ns   |

| SCLK Fall Time                         | t <sub>SF</sub>  |     | 20   | ns   |

| MISO Disable After CS Rising Edge      | t <sub>DIS</sub> | 5   | 40   | ns   |

| CS High After SCLK Edge                | tsfs             | 0   |      | ns   |

<sup>&</sup>lt;sup>1</sup> Minimum and maximum specifications are guaranteed by design.

Figure 5. SPI Interface Timing

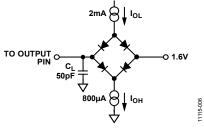

Figure 6. Load Circuit for Timing Specifications

### ABSOLUTE MAXIMUM RATINGS

$T_A = 25$ °C, unless otherwise noted.

Table 6.

| Parameter                                                            | Rating                |

|----------------------------------------------------------------------|-----------------------|

| VDD to GND                                                           | -0.3 V to +3.7 V      |

| Analog Input Voltage to GND <sub>ISO</sub> , IP, IM,<br>V1P, V2P, VM | -2 V to +2 V          |

| Reference Input Voltage to GND <sub>ISO</sub>                        | -0.3 V to VDD + 0.3 V |

| Digital Input Voltage to GND                                         | -0.3 V to VDD + 0.3 V |

| Digital Output Voltage to GND                                        | -0.3 V to VDD + 0.3 V |

| Common-Mode Transients <sup>1</sup>                                  | -100 kV/μs to         |

|                                                                      | +100 kV/μs            |

| Operating Temperature                                                |                       |

| Industrial Range                                                     | -40°C to +85°C        |

| Storage Temperature Range                                            | −65°C to +150°C       |

| Lead Temperature (Soldering, 10 sec) <sup>2</sup>                    | 260°C                 |

<sup>&</sup>lt;sup>1</sup> Refers to common-mode transients across the insulation barrier. Common-mode transients exceeding the absolute maximum ratings may cause latch-up or permanent damage.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

$\theta_{JA}$  and  $\theta_{JC}$  are specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

Table 7. Thermal Resistance

| Package Type    | θιΑ  | <b>Ө</b> зс | Unit |

|-----------------|------|-------------|------|

| 20-Lead SOIC_IC | 48.0 | 6.2         | °C/W |

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

Table 8. Maximum Continuous Working Voltage Supporting a 50-Year Minimum Lifetime<sup>1</sup>

| Parameter                    | Max  | Unit   |

|------------------------------|------|--------|

| AC Voltage, Bipolar Waveform | 400  | V rms  |

| DC Voltage, Basic Insulation | 1173 | V peak |

$<sup>^1</sup>$  Refers to the continuous voltage magnitude imposed across the isolation barrier. See the Insulation Lifetime section for more details.

Note that greater working voltages than the values presented in Table 8 shorten the lifetime of the product (see the Insulation Lifetime section). Therefore, although some certifications in Table 2 state bigger maximum working voltages, use the ADE7912/ADE7913 only for working voltages lower than the values presented in this Table 8.

<sup>&</sup>lt;sup>2</sup> Analog Devices recommends that reflow profiles used in soldering RoHS compliant devices conform to J-STD-020D.1 from JEDEC. Refer to JEDEC for the latest revision of this standard.

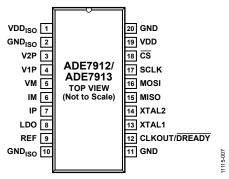

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 7. Pin Configuration

**Table 9. Pin Function Descriptions**

| Pin No. | Mnemonic           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | VDD <sub>ISO</sub> | Isolated Secondary Side Power Supply. This pin provides access to the 2.8 V on-chip isolated power supply. Do not connect external load circuitry to this pin. Decouple this pin with a 10 µF capacitor in parallel with a ceramic 100 nF capacitor using Pin 2, GND <sub>Iso</sub> .                                                                                                                                                                                                                                                                                                                                                                    |

| 2, 10   | GND <sub>ISO</sub> | Ground Reference of the Isolated Secondary Side. These pins provide the ground reference for the analog circuitry. Use these quiet ground references for all analog circuitry. These two pins are connected together internally.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3, 4, 5 | V2P, V1P, VM       | Analog Inputs for the Voltage Channels. The voltage channels are used with the voltage transducers. V2P and V1P are pseudo differential voltage inputs with a maximum signal level of ±500 mV with respect to VM for specified operation. Use these pins with the related input circuitry, as shown in Figure 20. If V1P or V2P is not used, connect it to the VM pin. On the ADE7912, connect the V2P pin to the VM pin because the V2P voltage channel is not available. The second voltage channel is available on the ADE7913 only.                                                                                                                  |

| 6, 7    | IM, IP             | Analog Inputs for the Current Channel. The current channel is used with shunts. IM and IP are pseudo differential voltage inputs with a maximum differential level of $\pm 31.25$ mV. Use these pins with the related input circuitry, as shown in Figure 20.                                                                                                                                                                                                                                                                                                                                                                                            |

| 8       | LDO                | $2.5$ V Output of Analog Low Dropout (LDO) Regulator. Decouple this pin with a $4.7~\mu$ F capacitor in parallel with a ceramic 100 nF capacitor to GND <sub>ISO</sub> , Pin 10. Do not connect external load circuitry to this pin.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 9       | REF                | Voltage Reference. This pin provides access to the on-chip voltage reference. The on-chip reference has a nominal value of 1.2 V. Decouple this pin to $GND_{ISO}$ , Pin 10, with a 4.7 $\mu F$ capacitor in parallel with a ceramic 100 nF capacitor.                                                                                                                                                                                                                                                                                                                                                                                                   |

| 11, 20  | GND                | Primary Ground Reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 12      | CLKOUT/DREADY      | Clock Output (CLKOUT). When CLKOUT functionality is selected (see the Synchronizing Multiple ADE7912/ADE7913 Devices section for details), the ADE7912/ADE7913 generate a digital signal synchronous to the master clock at the XTAL1 pin. Use CLKOUT to provide a clock to other ADE7912/ADE7913 devices on the board.  Data Ready, Active Low (DREADY). When DREADY functionality is selected (see the Synchronizing Multiple ADE7912/ADE7913 Devices section for details), the ADE7912/ADE7913 generate an active low signal synchronous to the ADC output frequency. Use this signal to start reading the ADC outputs of the ADE7912/ADE7913.        |

| 13      | XTAL1              | Master Clock Input. An external clock can be provided at this logic input. The CLKOUT/DREADY signal of another appropriately configured ADE7912/ADE7913 (see the Synchronizing Multiple ADE7912/ADE7913 Devices section for details) can be provided at this pin. Alternatively, a crystal with a maximum drive level of 0.5 mW and an equivalent series resistance (ESR) of 20 $\Omega$ can be connected across XTAL1 and XTAL2 to provide a clock source for the ADE7912/ADE7913. The clock frequency for specified operation is 4.096 MHz, but lower frequencies down to 3.6 MHz can be used. See the ADE7912/ADE7913 Clock section for more details. |

| 14      | XTAL2              | Crystal, Second Input. A crystal with a maximum drive level of 0.5 mW and an ESR of 20 $\Omega$ can be connected across XTAL2 and XTAL1 to provide a clock source for the ADE7912/ADE7913.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 15      | MISO               | Data Output for SPI Port. Pull up this pin with a 10 k $\Omega$ resistor (see the SPI-Compatible Interface section for details).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 16      | MOSI               | Data Input for SPI Port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Pin No. | Mnemonic                                                                                                                         | Description                                                                                                                                                                                                                                                                       |  |

|---------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 17      | 7 SCLK Serial Clock Input for SPI Port. All serial data transfers are synchronized to this clock ADE7912/ADE7913 Clock section). |                                                                                                                                                                                                                                                                                   |  |

| 18      | CS                                                                                                                               | Chip Select for SPI Port.                                                                                                                                                                                                                                                         |  |

| 19      | VDD                                                                                                                              | Primary Supply Voltage. This pin provides the supply voltage for the ADE7912/ADE7913. Maintain the supply voltage at $3.3 \text{ V} \pm 10\%$ for specified operation. Decouple this pin to GND, Pin 20, with a 10 $\mu$ F capacitor in parallel with a ceramic 100 nF capacitor. |  |

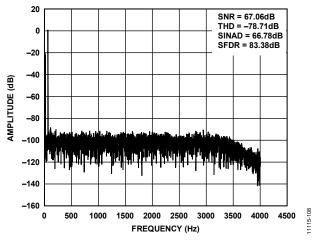

### TYPICAL PERFORMANCE CHARACTERISTICS

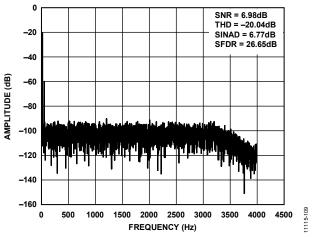

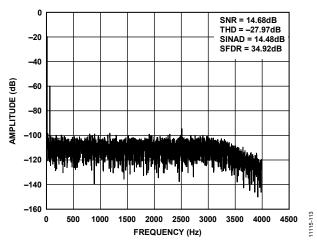

Figure 8. Current Channel FFT,  $\pm 31.25$  mV, 50 Hz Pseudo Differential Input Signal, ADC\_FREQ = 8 kHz, BW = 3300 Hz

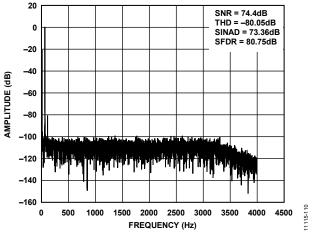

Figure 9. Current Channel FFT,  $\pm 31.25 \,\mu V$ , 50 Hz Pseudo Differential Input Signal, ADC\_FREQ = 8 kHz, BW = 3300 Hz

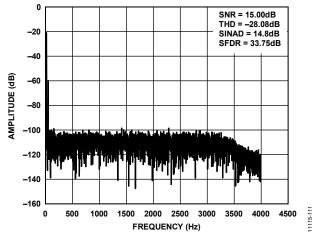

Figure 10. Voltage Channel V1 FFT,  $\pm 500$  mV, 50 Hz Pseudo Differential Input Signal, ADC\_FREQ = 8 kHz, BW = 3300 Hz

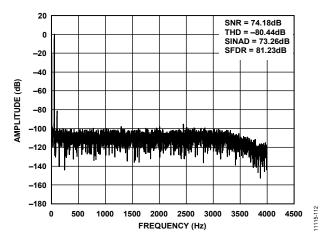

Figure 11. Voltage Channel V1 FFT,  $\pm 500~\mu V$ , 50 Hz Pseudo Differential Input Signal, ADC\_FREQ = 8~kHz, BW = 3300~Hz

Figure 12. Voltage Channel V2 FFT,  $\pm 500$  mV, 50 Hz Pseudo Differential Input Signal, ADC\_FREQ = 8 kHz, BW = 3300 Hz

Figure 13. Voltage Channel V2 FFT,  $\pm 500 \,\mu\text{V}$ , 50 Hz Pseudo Differential Input Signal, ADC\_FREQ = 8 kHz, BW = 3300 Hz

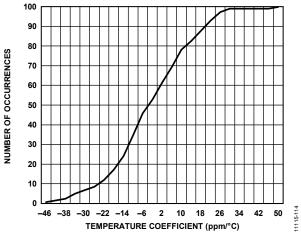

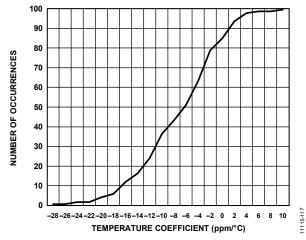

Figure 14. Cumulative Histogram of the Current Channel ADC Gain Temperature Coefficient for Temperatures Between  $-40^{\circ}$ C and  $+25^{\circ}$ C

Figure 15. Cumulative Histogram of the Current Channel ADC Gain Temperature Coefficient for Temperatures Between 25°C and 85°C

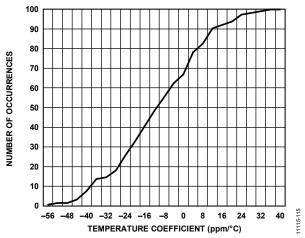

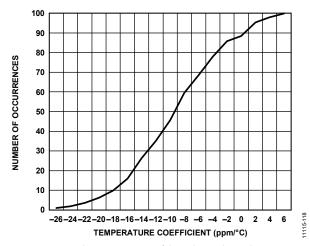

Figure 16. Cumulative Histogram of the Voltage Channel V1 ADC Gain Temperature Coefficient for Temperatures Between  $-40^{\circ}$ C and  $+25^{\circ}$ C

Figure 17. Cumulative Histogram of the Voltage Channel V1 ADC Gain Temperature Coefficient for Temperatures Between 25°C and 85°C

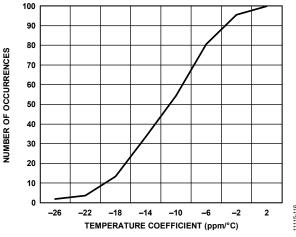

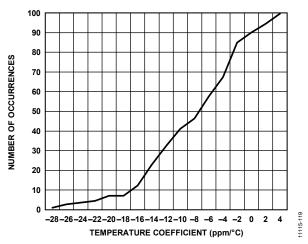

Figure 18. Cumulative Histogram of the Voltage Channel V2 ADC Gain Temperature Coefficient for Temperatures Between  $-40^{\circ}$ C and  $+25^{\circ}$ C

Figure 19. Cumulative Histogram of the Voltage Channel V2 ADC Gain Temperature Coefficient for Temperatures Between 25°C and 85°C

# **TEST CIRCUIT**

Figure 20. Test Circuit

### **TERMINOLOGY**

# Pseudo Differential Signal Voltage Range Between IP and IM, V1P and VM, and V2P and VM Pins

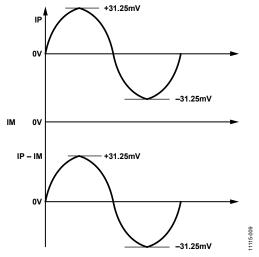

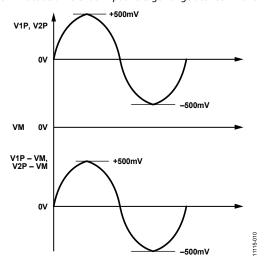

The range represents the peak-to-peak pseudo differential voltage that must be applied to the ADCs to generate a full-scale response when the IM and VM pins are connected to GND<sub>ISO</sub>, Pin 2. The IM and VM pins are connected to GND<sub>ISO</sub> using antialiasing filters (see Figure 20). Figure 21 illustrates the input voltage range between IP and IM; Figure 22 illustrates the input voltage range between V1P and VM and between V2P and VM.

Figure 21. Pseudo Differential Input Voltage Range Between IP and IM Pins

Figure 22. Pseudo Differential Input Voltage Range Between V1P and VM Pins and Between V2P and VM Pins

#### Maximum VM and IM Voltage Range

The range represents the maximum allowed voltage at VM and IM pins relative to GND<sub>ISO</sub>, Pin 10.

#### Crosstalk

Crosstalk represents leakage of signals, usually via capacitance between circuits. Crosstalk is measured in the current channel by setting the IP and IM pins to GND<sub>ISO</sub>, Pin 10, supplying a full-scale alternate differential voltage between the V1P and VM pins and between the V2P and VM pins of the voltage channel, and measuring the output of the current channel. It is measured in the V1P voltage channel by setting the V1P and VM pins to GND<sub>ISO</sub>, Pin 10, supplying a full-scale alternate differential voltage at the IP and V2P pin, and measuring the output of the V1P channel. Crosstalk is measured in the V2P voltage channel by setting the V2P and VM pins to GND<sub>ISO</sub>, Pin 10, supplying a fullscale alternate differential voltage at the IP and V1P pins, and measuring the output of the V2P channel. The crosstalk is equal to the ratio between the grounded ADC output value and the ADC full-scale output value. The ADC outputs are acquired for 2 sec. Crosstalk is expressed in decibels.

#### Input Impedance to Ground (DC)

The input impedance to ground represents the impedance measured at each ADC input pin (IP, IM, V1P, V2P, and VM) with respect to GND<sub>ISO</sub>, Pin 10.

#### **ADC Offset Error**

ADC offset error is the difference between the average measured ADC output code with both inputs connected to  $GND_{\rm ISO}$  and the ideal ADC output code. The magnitude of the offset depends on the input range of each channel.

#### **ADC Offset Drift over Temperature**

The ADC offset drift is the change in offset over temperature. It is measured at  $-40^{\circ}$ C,  $+25^{\circ}$ C, and  $+85^{\circ}$ C. The offset drift over temperature is computed as follows:

Drift =

$$\max \left[ \left. \frac{Offset(-40) - Offset(25)}{Offset(25) \times (-40 - 25)} \right|, \left| \frac{Offset(85) - Offset(25)}{Offset(25) \times (85 - 25)} \right| \right]$$

Offset drift is expressed in ppm/°C.

#### **Gain Error**

The gain error in the ADCs represents the difference between the measured ADC output code (minus the offset) and the ideal output code when the internal voltage reference is used (see the Analog-to-Digital Conversion section). The difference is expressed as a percentage of the ideal code. It represents the overall gain error of one current or voltage channel.

#### **Gain Drift over Temperature**

This temperature coefficient includes the temperature variation of the ADC gain and of the internal voltage reference. It represents the overall temperature coefficient of one current or voltage channel. With the internal voltage reference in use, the ADC gain is measured at  $-40^{\circ}$ C,  $+25^{\circ}$ C, and  $+85^{\circ}$ C. The temperature coefficient is computed as follows:

$$Drift = \max \left[ \frac{|Gain(-40) - Gain(25)|}{|Gain(25) \times (-40 - 25)|}, \frac{|Gain(85) - Gain(25)|}{|Gain(25) \times (85 - 25)|} \right]$$

Gain drift is measured in ppm/°C.

#### Power Supply Rejection (PSR)

PSR quantifies the measurement error as a percentage of reading when the power supplies are varied. For the ac PSR measurement, a reading at nominal supplies (3.3 V) is taken when the voltage at the input pins is 0 V. A second reading is obtained with the same input signal levels when an ac signal (120 mV rms at 50 Hz or 100 Hz) is introduced onto the supplies. Any error introduced by this ac signal is expressed as a percentage of the reading (power supply rejection ratio, PSRR). PSR =  $20 \log_{10}$  (PSRR).

For the dc PSR measurement, a reading at nominal supplies (3.3 V) is taken when the voltage between the IP and IM pins is 6.25 mV rms, and the voltages between the V1P and VM pins and between the V2P and VM pins are 100 mV rms. A second reading is obtained with the same input signal levels when the power supplies are varied by  $\pm 10\%$ . Any error introduced is expressed as a percentage of the reading (PSRR). Then PSR =  $20 \log_{10}$  (PSRR).

#### Signal-to-Noise Ratio (SNR)

SNR is the ratio of the rms value of the actual input signal to the rms sum of all other spectral components below the Nyquist frequency, excluding harmonics and dc. The waveform samples are acquired over a 1 sec window, and then a Hanning window is applied. The value for SNR is expressed in decibels.

#### Signal-to-Noise-and-Distortion (SINAD) Ratio

SINAD is the ratio of the rms value of the actual input signal to the rms sum of all other spectral components below the Nyquist frequency, including harmonics but excluding dc. The waveform samples are acquired over a 1 sec window, and then a Hanning window is applied. The value for SINAD is expressed in decibels.

#### **Total Harmonic Distortion (THD)**

THD is the ratio of the rms sum of all harmonics (excluding the noise components) to the rms value of the fundamental. The waveform samples are acquired over a 1 sec window, and then a Hanning window is applied. The value for THD is expressed in decibels.

#### Spurious-Free Dynamic Range (SFDR)

SFDR is the ratio of the rms value of the actual input signal to the rms value of the peak spurious component over the measurement bandwidth of the waveform samples. The waveform samples are acquired over a 1 sec window, and then a Hanning window is applied. The value of SFDR is expressed in decibels relative to full scale, dBFS.

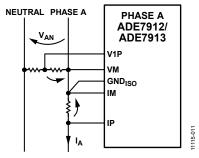

# THEORY OF OPERATION ANALOG INPUTS

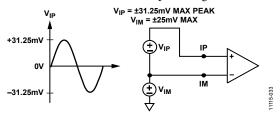

The ADE7913 has three analog inputs: one current channel and two voltage channels. The ADE7912 does not include the second voltage channel. The current channel has two fully differential voltage input pins, IP and IM, that accept a maximum differential signal of  $\pm 31.25$  mV.

The maximum  $V_{\rm IM}$  signal level is also  $\pm 31.25$  mV. The maximum  $V_{\rm IM}$  signal level allowed at the IM input is  $\pm 25$  mV. Figure 23 shows a schematic of the input for the current channel and the relation to the maximum IM pin voltage.

Figure 23. Maximum Input Level, Current Channel

Note that the current channel senses the voltage across a shunt. In this case, one pole of the shunt becomes the ground of the meter (see Figure 32) and, therefore, the current channel is used in a pseudo differential configuration, similar to the voltage channel configuration (see Figure 24).

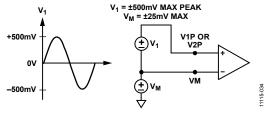

The voltage channel has two pseudo differential, single-ended voltage input pins: V1P and V2P. These single-ended voltage inputs have a maximum input voltage of  $\pm 500$  mV with respect to VM. The maximum signal allowed at the VM input is  $\pm 25$  mV. Figure 24 shows a schematic of the voltage channel inputs and their relation to the maximum VM voltage.

Figure 24. Maximum Input Level, Voltage Channels

#### ANALOG-TO-DIGITAL CONVERSION

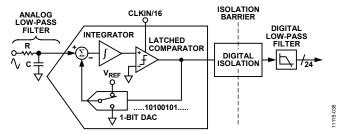

The ADE7912/ADE7913 have three second-order  $\Sigma$ - $\Delta$  ADCs. For simplicity, the block diagram in Figure 25 shows a first-order  $\Sigma$ - $\Delta$  ADC. The converter is composed of the  $\Sigma$ - $\Delta$  modulator and the digital low-pass filter, separated by the digital isolation block.

Figure 25. First-Order Σ-Δ ADC

A  $\Sigma$ - $\Delta$  modulator converts the input signal into a continuous serial stream of 1s and 0s at a rate determined by the sampling clock. In the ADE7912/ADE7913, the sampling clock is equal to CLKIN/4 (1.024 MHz when CLKIN = 4.096 MHz). The 1-bit DAC in the feedback loop is driven by the serial stream. The DAC output is subtracted from the input signal. If the loop gain is high enough, the average value of the DAC output (and, therefore, the bit stream) can approach that of the input signal level. For any given input value in a single sampling interval, the data from the 1-bit ADC is virtually meaningless. A meaningful result is obtained only when a large number of samples is averaged. This averaging is completed in the second part of the ADC, the digital low-pass filter, after the data passes through the digital isolators. By averaging a large number of bits from the modulator, the low-pass filter can produce 24-bit data-words that are proportional to the input signal level.

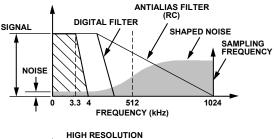

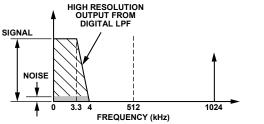

The  $\Sigma$ - $\Delta$  converter uses two techniques to achieve high resolution from what is essentially a 1-bit conversion technique. The first technique is oversampling. Oversampling means that the signal is sampled at a rate (frequency) that is many times higher than the bandwidth of interest. For example, when CLKIN = 4.096 MHz, the sampling rate in the ADE7912/ADE7913 is 1.024 MHz, and the bandwidth of interest is 40 Hz to 3.3 kHz. Oversampling has the effect of spreading the quantization noise (noise due to sampling) over a wider bandwidth. With the noise spread more thinly over a wider bandwidth, the quantization noise in the bandwidth of interest is lowered, as shown in Figure 26.

However, oversampling alone is not sufficient to improve the signal-to-noise ratio (SNR) in the band of interest. For example, an oversampling factor of 4 is required to increase the SNR by a mere 6 dB (1 bit). To keep the oversampling ratio at a reasonable level, it is possible to shape the quantization noise so that the majority of the noise lies at the higher frequencies. Noise shaping is the second technique that achieves high resolution. In the  $\Sigma$ - $\Delta$  modulator, the noise is shaped by the integrator, which has a high-pass type response for the quantization noise. The result is that most of the noise is at the higher frequencies where it can be removed by the digital low-pass filter. This noise shaping is shown in Figure 26.

Figure 26. Noise Reduction Due to Oversampling and Noise Shaping in the Analog Modulator

The bandwidth of interest is a function of the input clock frequency, the ADC output frequency (selectable by Bits[5:4] (ADC\_FREQ) in the CONFIG register; see the ADC Output Values section for details), and Bit 7 (BW) of the CONFIG register. When CLKIN is 4.096 MHz and the ADC output frequency is 8 kHz, if BW is cleared to 0 (the default value) the ADC bandwidth is 3.3 kHz. If BW is set to 1, the ADC bandwidth is 2 kHz. Table 10 shows the ADC output frequencies and the ADC bandwidth function of the input clock (CLKIN) frequency. Three cases are shown: one for CLKIN = 4.096 MHz (the typical clock input frequency value), one for CLKIN = 4.21 MHz (the maximum clock input frequency.)

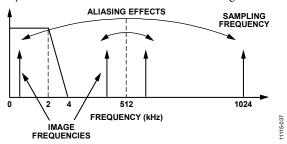

#### **Antialiasing Filter**

Figure 25 also shows an analog low-pass filter (RC) on the input to the ADC. This filter is placed outside the ADE7912/ADE7913, and the role is to prevent aliasing. Aliasing is an artifact of all sampled systems, as shown in Figure 27. Aliasing refers to the frequency components in the input signal to the ADC that are higher than half the sampling rate of the ADC and appear in the sampled signal at a frequency below half the sampling rate. Frequency components above half the sampling frequency (also known as the Nyquist frequency, that is, 512 kHz) are imaged or folded back down below 512 kHz. This happens with all ADCs, regardless of the architecture. In Figure 27, only frequencies near the sampling frequency of 1.024 MHz move into the bandwidth of interest for metering, that is, 40 Hz to 3.3 kHz, or 40 Hz to 2 kHz. To attenuate the high frequency noise (near 1.024 MHz) and prevent the distortion of the bandwidth of interest, a lowpass filer (LPF) must be introduced. It is recommended that one RC filter with a corner frequency of 5 kHz be used for the attenuation to be sufficiently high at the sampling frequency of 1.024 MHz. The 20 dB per decade attenuation of this filter is usually sufficient to eliminate the effects of aliasing.

Figure 27. Aliasing Effects

Table 10. ADC Output Frequency and ADC Bandwidth as a Function of CLKIN Frequency

| CLKIN<br>(MHz) | Bits ADC_FREQ in CONFIG Register | ADC Output<br>Frequency (Hz) | ADC Bandwidth When Bit BW in CONFIG Register Cleared to 0 (Hz) | ADC Bandwidth When Bit BW in CONFIG Register Set to 1 (Hz) |

|----------------|----------------------------------|------------------------------|----------------------------------------------------------------|------------------------------------------------------------|

| 4.096          | 00                               | 8000                         | 3300                                                           | 2000                                                       |

|                | 01                               | 4000                         | 1650                                                           | 1000                                                       |

|                | 10                               | 2000                         | 825                                                            | 500                                                        |

|                | 11                               | 1000                         | 412                                                            | 250                                                        |

| 4.21           | 00                               | 8222                         | 3391                                                           | 2055                                                       |

|                | 01                               | 4111                         | 1695                                                           | 1027                                                       |

|                | 10                               | 2055                         | 847                                                            | 513                                                        |

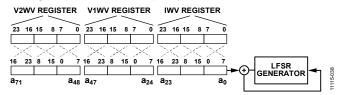

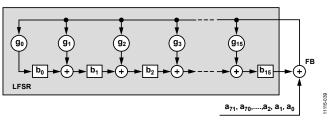

|                | 11                               | 1027                         | 423                                                            | 256                                                        |