Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# High Performance FSK/ASK Transceiver IC

ADF7020-1

#### **FEATURES**

Low power, low IF transceiver Frequency bands

135 MHz to 650 MHz, direct output 80 MHz to 325 MHz, divide-by-2 mode

**Data rates supported**

0.15 kbps to 200 kbps, FSK

0.15 kbps to 64 kbps, ASK

2.3 V to 3.6 V power supply

**Programmable output power**

-20 dBm to +13 dBm in 63 steps

**Receiver sensitivity**

- -119 dBm at 1 kbps, FSK, 315 MHz

- -114 dBm at 9.6 kbps, FSK, 315 MHz

- -111.8 dBm at 9.6 kbps, ASK, 315 MHz

Low power consumption

17.6 mA in receive mode

21 mA in transmit mode (10 dBm output)

**On-chip VCO and fractional-N PLL**

On-chip 7-bit ADC and temperature sensor

Fully automatic frequency control loop (AFC) compensates for lower tolerance crystals

**Digital RSSI**

Integrated TRx switch

Leakage current <1 µA in power-down mode

#### **APPLICATIONS**

Low cost wireless data transfer

Wireless medical applications

Remote control/security systems

**Wireless metering**

**Keyless entry**

**Home automation**

**Process and building control**

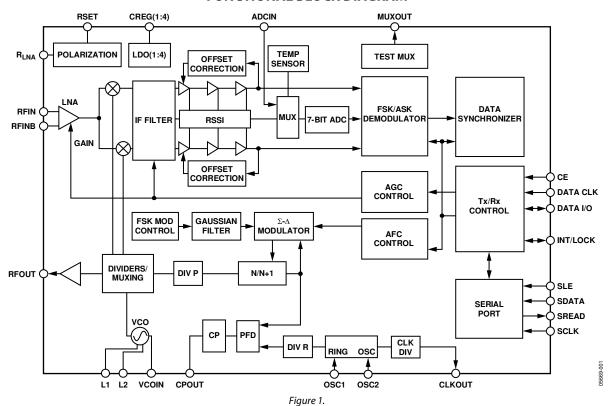

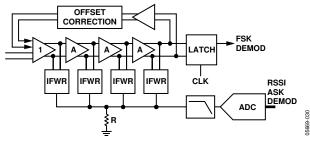

#### **FUNCTIONAL BLOCK DIAGRAM**

# ADF7020-1\* PRODUCT PAGE QUICK LINKS

Last Content Update: 02/23/2017

# COMPARABLE PARTS 🖳

View a parametric search of comparable parts.

# **EVALUATION KITS**

· ADF7020-1 Evaluation Boards

### **DOCUMENTATION**

#### **Application Notes**

- AN-1389: Recommended Rework Procedure for the Lead Frame Chip Scale Package (LFCSP)

- AN-772: A Design and Manufacturing Guide for the Lead Frame Chip Scale Package (LFCSP)

- AN-852: Using the Test DAC on the ADF702x to Implement Functions Such as Analog FM DEMOD, SNR Measurement, FEC Decoding, and PSK/4FSK Demodulation

- AN-859: RF Port Impedance Data, Matching, and External Component Selection for the ADF7020-1, ADF7021, and ADF7021-N

- AN-915: CDR Operation for ADF7020, ADF7020-1, ADF7021, and ADF7025

#### **Data Sheet**

ADF7020-1: High Performance, FSK/ASK Transceiver IC Data Sheet

### SOFTWARE AND SYSTEMS REQUIREMENTS $\Box$

- ADF70xx Evaluation Software

- ADIismLINK Development Platform

# TOOLS AND SIMULATIONS 🖵

ADIsimSRD Design Studio

### REFERENCE MATERIALS 🖵

#### **Solutions Bulletins & Brochures**

Emerging Energy Applications Solutions Bulletin, Volume 10, Issue 4

#### **Technical Articles**

- Innovative Line Sensor Design with ADI Energy Harvesting and Low Power Signal Chain

- RF Meets Power Lines: Designing Intelligent Smart Grid Systems that Promote Energy Efficiency

- Smart Metering Technology Promotes Energy Efficiency for a Greener World

- The Use of Short Range Wireless in a Multi-Metering System

- Understand Wireless Short-Range Devices for Global License-Free Systems

- Wireless Short Range Devices and Narrowband Communications

- Wireless Technologies for Smart Meters: Focus on Water Metering

### DESIGN RESOURCES $\Box$

- · ADF7020-1 Material Declaration

- PCN-PDN Information

- · Quality And Reliability

- · Symbols and Footprints

# DISCUSSIONS 🖳

View all ADF7020-1 EngineerZone Discussions.

# SAMPLE AND BUY 🖳

Visit the product page to see pricing options.

# TECHNICAL SUPPORT 🖵

Submit a technical question or find your regional support number.

# DOCUMENT FEEDBACK 🖳

Submit feedback for this data sheet.

# **TABLE OF CONTENTS**

| Features                                                                                                                      | 1        |

|-------------------------------------------------------------------------------------------------------------------------------|----------|

| Applications                                                                                                                  | 1        |

| Functional Block Diagram                                                                                                      | 1        |

| Revision History                                                                                                              | 2        |

| General Description                                                                                                           | 3        |

| Specifications                                                                                                                | 4        |

| Timing Characteristics                                                                                                        | 8        |

| Absolute Maximum Ratings                                                                                                      | 10       |

| ESD Caution                                                                                                                   | 10       |

| Pin Configuration and Function Descriptions                                                                                   | 11       |

| Typical Performance Characteristics                                                                                           | 13       |

| Frequency Synthesizer                                                                                                         | 15       |

| Reference Input                                                                                                               | 15       |

| Charaina Charaila fan Bast Castana Banfanna a                                                                                 |          |

| Choosing Channels for Best System Performance                                                                                 | 17       |

| Transmitter                                                                                                                   |          |

|                                                                                                                               | 18       |

| Transmitter                                                                                                                   | 18       |

| Transmitter                                                                                                                   | 18<br>18 |

| Transmitter                                                                                                                   |          |

| Transmitter                                                                                                                   |          |

| Transmitter  RF Output Stage  Modulation Schemes  Receiver Section  RF Front End                                              |          |

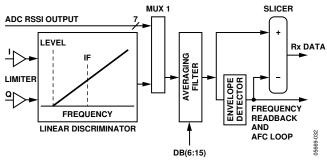

| Transmitter  RF Output Stage  Modulation Schemes  Receiver Section  RF Front End  RSSI/AGC                                    |          |

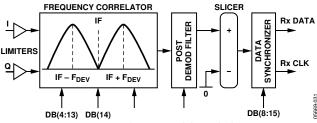

| Transmitter  RF Output Stage  Modulation Schemes  Receiver Section  RF Front End  RSSI/AGC  FSK Demodulators on the ADF7020-1 |          |

| Transmitter                                                                                                                   |          |

| Transmitter                                                                                                                   |          |

| LNA/PA Matching                                          |

|----------------------------------------------------------|

| Transmit Protocol and Coding Considerations              |

| Device Programming after Initial Power-Up                |

| Interfacing to Microcontroller/DSP                       |

| Serial Interface                                         |

| Readback Format                                          |

| Register 0—N Register                                    |

| Register 1—Oscillator/Filter Register31                  |

| Register 2—Transmit Modulation Register (ASK/OOK Mode)   |

| Register 2—Transmit Modulation Register (FSK Mode) 33    |

| Register 2—Transmit Modulation Register (GFSK/GOOK Mode) |

| Register 3—Receiver Clock Register                       |

| Register 4—Demodulator Set-up Register                   |

| Register 5—Sync Byte Register                            |

| Register 6—Correlator/Demodulator Register               |

| Register 7—Readback Set-up Register                      |

| Register 8—Power-Down Test Register 40                   |

| Register 9—AGC Register41                                |

| Register 10—AGC 2 Register                               |

| Register 11—AFC Register                                 |

| Register 12—Test Register                                |

| Register 13—Offset Removal and Signal Gain Register 44   |

| Outline Dimensions                                       |

| Ordering Guide45                                         |

#### **REVISION HISTORY**

12/05—Revision 0: Initial Version

### **GENERAL DESCRIPTION**

The ADF7020-1 is a low power, highly integrated FSK/GFSK/ASK/OOK/GOOK transceiver designed for operation in the low UHF and VHF bands. The ADF7020-1 uses an external VCO inductor that allows users to set the operating frequency anywhere between 135 MHz and 650 MHz. Using the divideby-2 circuit allows users to operate the device as low as 80 MHz. The typical range of the VCO is about 10% of the operating frequency. A complete transceiver can be built using a small number of external discrete components, making the ADF7020-1 very suitable for price-sensitive and area-sensitive applications.

The transmit section contains a VCO and low noise fractional-N PLL with output resolution of <1 ppm. This frequency agile PLL allows the ADF7020-1 to be used in frequency-hopping spread spectrum (FHSS) systems. The VCO operates at twice the fundamental frequency to reduce spurious emissions and frequency pulling problems.

The transmitter output power is programmable in 63 steps from -20 dBm to +13 dBm. The transceiver RF frequency, channel spacing, and modulation are programmable using a simple 3-wire interface. The device operates with a power supply range of 2.3 V to 3.6 V and can be powered down when not in use.

A low IF architecture is used in the receiver (200 kHz), minimizing power consumption and the external component count and avoiding interference problems at low frequencies. The ADF7020-1 supports a wide variety of programmable features, including Rx linearity, sensitivity, and IF bandwidth, allowing the user to trade off receiver sensitivity and selectivity for current consumption, depending on the application. The receiver also features a patent-pending automatic frequency control (AFC) loop, allowing the PLL to compensate for frequency error in the incoming signal.

An on-chip ADC provides readback of an integrated temperature sensor, an external analog input, the battery voltage, or the RSSI signal, which provides savings on an ADC in some applications. The temperature sensor is accurate to  $\pm 10^{\circ}$ C over the full operating temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C. This accuracy can be improved by doing a 1-point calibration at room temperature and storing the result in memory.

# **SPECIFICATIONS**

$V_{DD}$  = 2.3 V to 3.6 V, GND = 0 V,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical specifications are at  $V_{DD}$  = 3 V,  $T_A$  = 25°C. All measurements are performed using the EVAL-ADF7020-1-DBX and PN9 data sequence, unless otherwise noted.

Table 1.

| Parameter                                    | Min    | Тур        | Max             | Unit    | Test Conditions                                                           |

|----------------------------------------------|--------|------------|-----------------|---------|---------------------------------------------------------------------------|

| RF CHARACTERISTICS                           |        |            |                 |         |                                                                           |

| Frequency Ranges (Direct Output)             | 135    |            | 650             | MHz     | See Table 5 for VCO bias settings at different frequencies                |

| Frequency Ranges<br>(Divide-by-2 Mode)       | 80     |            | 325             | MHz     |                                                                           |

| VCO Frequency Range                          | 1.1    | 1.2        |                 | Ratio   | F <sub>MAX</sub> /F <sub>MIN</sub> , using VCO bias settings in Table 5   |

| Phase Frequency Detector Frequency           | RF/256 |            | 20.96           | MHz     | PFD must be less than direct output frequency/31                          |

| TRANSMISSION PARAMETERS                      |        |            |                 |         |                                                                           |

| Data Rate                                    |        |            |                 |         |                                                                           |

| FSK/GFSK                                     | 0.15   |            | 200             | kbps    |                                                                           |

| OOK/ASK                                      | 0.15   |            | 64 <sup>1</sup> | kbps    |                                                                           |

| OOK/ASK                                      | 0.3    |            | 100             | kbaud   | Using Manchester biphase-L encoding                                       |

| Frequency Shift Keying                       |        |            |                 |         |                                                                           |

| GFSK/FSK Frequency Deviation <sup>2, 3</sup> | 1      |            | 110             | kHz     | PFD = 3.625 MHz                                                           |

|                                              | 4.88   |            | 620             | kHz     | PFD = 20 MHz                                                              |

| Deviation Frequency Resolution               | 100    |            |                 | Hz      | PFD = 3.625 MHz                                                           |

| Gaussian Filter BT                           |        | 0.5        |                 |         |                                                                           |

| Amplitude Shift Keying                       |        |            |                 |         |                                                                           |

| ASK Modulation Depth                         |        |            | 30              | dB      |                                                                           |

| OOK-PA Off Feedthrough                       |        | -50        |                 | dBm     |                                                                           |

| Transmit Power <sup>4</sup>                  | -20    |            | +13             | dBm     | $V_{DD} = 3.0 \text{ V}, T_A = 25^{\circ}\text{C}, FRF > 200 \text{ MHz}$ |

| Transmit Power                               | -20    |            | +11             | dBm     | $V_{DD} = 3.0 \text{ V}, T_A = 25^{\circ}\text{C}, FRF < 200 \text{ MHz}$ |

| Transmit Power Variation vs. Temp.           |        | ±1         |                 | dB      | From -40°C to +85°C                                                       |

| Transmit Power Variation vs. V <sub>DD</sub> |        | ±1         |                 | dB      | From 2.3 V to 3.6 V at 315 MHz, T <sub>A</sub> = 25°C                     |

| Programmable Step Size                       |        |            |                 |         |                                                                           |

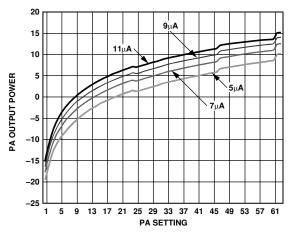

| –20 dBm to +13 dBm                           |        | 0.3125     |                 | dB      | See Figure 13 for how output power varies with PA setting                 |

| Integer Boundary                             |        | -55        |                 | dBc     | 50 kHz loop BW                                                            |

| Reference                                    |        | -65        |                 | dBc     |                                                                           |

| Harmonics                                    |        |            |                 |         |                                                                           |

| Second Harmonic                              |        | -27        |                 | dBc     | Unfiltered conductive                                                     |

| Third Harmonic                               |        | -21        |                 | dBc     |                                                                           |

| All Other Harmonics                          |        | -35        |                 | dBc     |                                                                           |

| VCO Frequency Pulling, OOK Mode              |        | 30         |                 | kHz rms | DR = 9.6 kbps                                                             |

| Optimum PA Load Impedance⁵                   |        | 79.4 + j64 |                 |         | FRF = 140 MHz                                                             |

| ·                                            |        | 109 + j64  |                 |         | FRF = 320 MHz                                                             |

|                                              |        | 40 + j47.5 |                 |         | FRF = 590 MHz                                                             |

| Parameter                                                                        | Min | Тур            | Max | Unit  | Test Conditions                                                                                              |

|----------------------------------------------------------------------------------|-----|----------------|-----|-------|--------------------------------------------------------------------------------------------------------------|

| RECEIVER PARAMETERS                                                              |     |                |     |       |                                                                                                              |

| FSK/GFSK Input Sensitivity                                                       |     |                |     |       | At BER = 1E - 3, FRF = 315 MHz,<br>LNA and PA matched separately <sup>6</sup>                                |

| Sensitivity at 1 kbps                                                            |     | -119.2         |     | dBm   | FDEV= 5 kHz, high sensitivity mode <sup>7</sup>                                                              |

| Sensitivity at 9.6 kbps                                                          |     | -114.2         |     | dBm   | FDEV = 10 kHz, high sensitivity mode                                                                         |

| OOK Input Sensitivity                                                            |     |                |     |       | At BER = 1E - 3, FRF = 315 MHz                                                                               |

| Sensitivity at 1 kbps                                                            |     | -118.2         |     | dBm   | High sensitivity mode                                                                                        |

| Sensitivity at 9.6 kbps                                                          |     | -111.8         |     | dBm   | High sensitivity mode                                                                                        |

| LNA and Mixer, Input IP3 <sup>7</sup>                                            |     |                |     |       | ,                                                                                                            |

| Enhanced Linearity Mode                                                          |     | 6.8            |     | dBm   | Pin = -20 dBm, 2 CW interferers,                                                                             |

| Low Current Mode                                                                 |     | -3.2           |     | dBm   | FRF = 315 MHz, F1 = FRF + 3 MHz,                                                                             |

| High Sensitivity Mode                                                            |     | -35            |     | dBm   | F2 = FRF + 6 MHz, maximum gain                                                                               |

| Rx Spurious Emissions <sup>8</sup>                                               |     |                | -57 | dBm   | <1 GHz at antenna input                                                                                      |

| Tox Sparrous Errissions                                                          |     |                | -47 | dBm   | >1 GHz at antenna input                                                                                      |

| AFC                                                                              |     |                | ''  | dbiii | > 1 GHz at afferma input                                                                                     |

| Pull-In Range                                                                    |     | ±50            |     | kHz   | IF_BW = 200 kHz                                                                                              |

| Response Time                                                                    |     | 48             |     | Bits  | Modulation index = 0.875                                                                                     |

| Accuracy                                                                         |     | 1              |     | kHz   |                                                                                                              |

| CHANNEL FILTERING                                                                |     |                |     |       |                                                                                                              |

| Adjacent Channel Rejection (Offset = $\pm 1 \times IF$ Filter BW                 |     | 27             |     | dB    | IF filter BW settings = 100 kHz, 150 kHz, 200 kHz; desired signal 3 dB above the input                       |

| Setting)  Second Adjacent Channel Rejection (Offset = ±2 × IF Filter BW Setting) |     | 50             |     | dB    | sensitivity level; CW interferer power level increased until BER = 10 <sup>-3</sup> ; image channel excluded |

| Third Adjacent Channel Rejection<br>(Offset = ±3 × IF Filter BW<br>Setting)      |     | 55             |     | dB    |                                                                                                              |

| Image Channel Rejection                                                          |     | 35             |     | dB    | Image at FRF – 400 kHz                                                                                       |

| CO-CHANNEL REJECTION                                                             |     | -2             |     | dB    |                                                                                                              |

| Wideband Interference Rejection                                                  |     | 70             |     | dB    | Swept from 100 MHz to 2 GHz, measured as channel rejection                                                   |

| BLOCKING                                                                         |     |                |     |       | Desired signal 3 dB above the input sensitivity                                                              |

| ±1 MHz                                                                           |     | 60             |     | dB    | level, CW interferer power level increased until BER = 10 <sup>-2</sup>                                      |

| ±5 MHz                                                                           |     | 68             |     | dB    |                                                                                                              |

| ±10 MHz                                                                          |     | 65             |     | dB    |                                                                                                              |

| ±10 MHz (High Linearity Mode)                                                    |     | 72             |     | dB    |                                                                                                              |

| Saturation (Maximum Input Level)                                                 |     | 12             |     | dBm   | FSK mode, BER = $10^{-3}$                                                                                    |

| LNA Input Impedance                                                              |     | 237 – j193     |     | Ω     | FRF = 130 MHz, RFIN to GND                                                                                   |

|                                                                                  |     | 101.4 – j161.6 |     | Ω     | FRF = 310 MHz                                                                                                |

|                                                                                  |     | 49.3 – j104.6  |     | Ω     | FRF = 610 MHz                                                                                                |

| RSSI                                                                             |     | -              |     |       |                                                                                                              |

| Range at Input                                                                   |     | −100 to −36    |     | dBm   |                                                                                                              |

| Linearity                                                                        |     | ±2             |     | dB    |                                                                                                              |

| Absolute Accuracy                                                                |     | ±3             |     | dB    |                                                                                                              |

| Response Time                                                                    |     | 150            |     | μs    | See the RSSI/AGC section                                                                                     |

| Parameter                                            | Min                    | Тур                     | Max                 | Unit           | Test Conditions                                                                                                               |

|------------------------------------------------------|------------------------|-------------------------|---------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------|

| PHASE-LOCKED LOOP                                    |                        |                         |                     |                |                                                                                                                               |

| VCO Gain                                             |                        | 40                      |                     | MHz/V          | 433 MHz, VCO adjust = 0,<br>VCO_BIAS_SETTING = 2                                                                              |

|                                                      |                        | 35                      |                     | MHz/V          | 315 MHz, VCO adjust = 0,<br>VCO_BIAS_SETTING = 2                                                                              |

|                                                      |                        | 16.5                    |                     | MHz/V          | 135 MHz, VCO adjust = 0,<br>VCO_BIAS_SETTING = 1                                                                              |

| Phase Noise (In-Band)                                |                        | -89                     |                     | dBc/Hz         | $PA = 0 \text{ dBm}$ , $V_{DD} = 3.0 \text{ V}$ , $PFD = 10 \text{ MHz}$ , $FRF = 315 \text{ MHz}$ , $VCO\_BIAS\_SETTING = 2$ |

| Normalized In-Band Phase Noise<br>Floor <sup>9</sup> |                        | -198                    |                     | dBc/Hz         |                                                                                                                               |

| Phase Noise (Out-of-Band)                            |                        | -110                    |                     | dBc/Hz         | 1 MHz offset                                                                                                                  |

| Residual FM                                          |                        | 128                     |                     | Hz             | From 200 Hz to 20 kHz, FRF = 315 MHz                                                                                          |

| PLL Settling                                         |                        | 40                      |                     | μs             | Measured for a 10 MHz frequency step to within 5 ppm accuracy, PFD = 20 MHz, LBW = 50 kHz                                     |

| REFERENCE INPUT                                      |                        |                         |                     |                |                                                                                                                               |

| Crystal Reference                                    | 3.625                  |                         | 24                  | MHz            | Must ensure PFD maximum is not exceeded                                                                                       |

| External Oscillator                                  | 3.625                  |                         | 24                  | MHz            |                                                                                                                               |

| Load Capacitance                                     |                        | 33                      |                     | pF             | Refer to the crystal's data sheet                                                                                             |

| Crystal Start-Up Time                                |                        | 2.1                     |                     | ms             | 11.0592 MHz crystal, using 33 pF load capacitors                                                                              |

|                                                      |                        | 1.0                     |                     | ms             | Using 16 pF load capacitors                                                                                                   |

| Input Level                                          |                        |                         |                     | CMOS<br>levels | See the Reference Input section                                                                                               |

| ADC PARAMETERS                                       |                        |                         |                     |                |                                                                                                                               |

| INL                                                  |                        | ±1                      |                     | LSB            | From 2.3 V to 3.6 V, T <sub>A</sub> = 25°C                                                                                    |

| DNL                                                  |                        | ±1                      |                     | LSB            | From 2.3 V to 3.6 V, T <sub>A</sub> = 25°C                                                                                    |

| TIMING INFORMATION                                   |                        |                         |                     |                |                                                                                                                               |

| Chip Enabled to Regulator Ready                      |                        | 10                      |                     | μs             | $C_{REG} = 100 \text{ nF}$                                                                                                    |

| Chip Enabled to RSSI Ready                           |                        | 3.0                     |                     | ms             | See Table 13 for more details                                                                                                 |

| Tx-to-Rx Turnaround Time                             |                        | 150 μs +                |                     |                | Time to synchronized data out, includes                                                                                       |

|                                                      |                        | (5 × T <sub>BIT</sub> ) |                     |                | AGC settling. See AGC Information and Timing section for more details.                                                        |

| LOGIC INPUTS                                         |                        |                         |                     |                | _                                                                                                                             |

| Input High Voltage, V <sub>INH</sub>                 | $0.7 \times V_{DD}$    |                         |                     | V              |                                                                                                                               |

| Input Low Voltage, V <sub>INL</sub>                  |                        |                         | $0.2 \times V_{DD}$ | V              |                                                                                                                               |

| Input Current, I <sub>INH</sub> /I <sub>INL</sub>    |                        |                         | ±1                  | μΑ             |                                                                                                                               |

| Input Capacitance, C <sub>IN</sub>                   |                        |                         | 10                  | pF             |                                                                                                                               |

| Control Clock Input                                  |                        |                         | 50                  | MHz            |                                                                                                                               |

| LOGIC OUTPUTS                                        |                        |                         |                     |                |                                                                                                                               |

| Output High Voltage, Vон                             | DV <sub>DD</sub> - 0.4 |                         |                     | V              | $I_{OH} = 500 \mu A$                                                                                                          |

| Output Low Voltage, Vol                              |                        |                         | 0.4                 | V              | $I_{OL} = 500 \mu\text{A}$                                                                                                    |

| CLKOUT Rise/Fall                                     |                        |                         | 5                   | ns             |                                                                                                                               |

| CLKOUT Load                                          |                        |                         | 10                  | pF             |                                                                                                                               |

| TEMPERATURE RANGE—T <sub>A</sub>                     | -40                    |                         | +85                 | °C             |                                                                                                                               |

| Parameter                    | Min | Тур Мах  |     | Unit | Test Conditions                                               |

|------------------------------|-----|----------|-----|------|---------------------------------------------------------------|

| POWER SUPPLIES               |     |          |     |      |                                                               |

| Voltage Supply               |     |          |     |      |                                                               |

| $V_{DD}$                     | 2.3 |          | 3.6 | V    | All V <sub>DD</sub> pins must be tied together                |

| Transmit Current Consumption |     |          |     |      | FRF = 315 MHz, $V_{DD}$ = 3.0 V, PA is matched to 50 $\Omega$ |

| 433 MHz, 0 dBm/5 dBm/10 dBm  |     | 13/16/21 |     | mA   | VCO_BIAS_SETTING = 2                                          |

| Receive Current Consumption  |     |          |     |      |                                                               |

| Low Current Mode             |     | 17.6     |     | mA   | VCO_BIAS_SETTING = 2                                          |

| High Sensitivity Mode        |     | 20.1     |     | mA   | VCO_BIAS_SETTING = 2                                          |

| Power-Down Mode              |     |          |     |      |                                                               |

| Low Power Sleep Mode         |     | 0.1      | 1   | μΑ   |                                                               |

<sup>&</sup>lt;sup>1</sup> Higher data rates are achievable, depending on local regulations.

<sup>&</sup>lt;sup>2</sup> For definition of frequency deviation, see the Register 2—Transmit Modulation Register (FSK Mode) section.

<sup>&</sup>lt;sup>3</sup> For definition of GFSK frequency deviation, see the Register 2—Transmit Modulation Register (GFSK/GOOK Mode) section. <sup>4</sup> Measured as maximum unmodulated power. Output power varies with both supply and temperature. <sup>5</sup> For matching details, see the LNA/PA Matching section.

<sup>6</sup> Sensitivity for combined matching network case is typically 2 dB less than separate matching networks. See Table 11 for sensitivity values at various data rates and frequencies.

<sup>&</sup>lt;sup>7</sup> See Table 6 for a description of different receiver modes.

<sup>8</sup> Follow the matching and layout guidelines to achieve the relevant FCC/ETSI specifications.

<sup>&</sup>lt;sup>9</sup> This figure can be used to calculate the in-band phase noise for any operating frequency. Use the following equation to calculate the in-band phase noise performance as seen at the PA output:  $-198 + 10 \log(f_{PFD}) + 20 \log N$ .

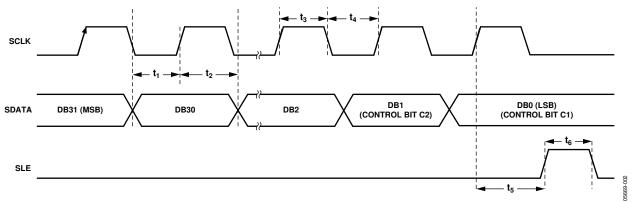

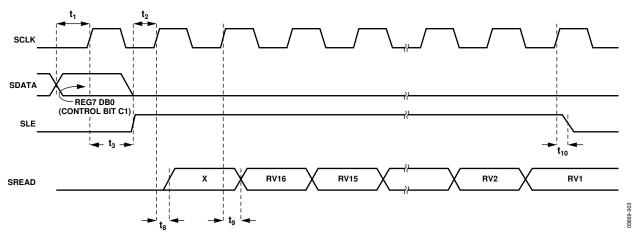

#### **TIMING CHARACTERISTICS**

$V_{DD} = 3 \text{ V} \pm 10\%$ , VGND = 0 V,  $T_A = 25$ °C, unless otherwise noted. Guaranteed by design, but not production tested.

Table 2.

| Parameter             | Limit at T <sub>MIN</sub> to T <sub>MAX</sub> | Unit | Test Conditions/Comments             |

|-----------------------|-----------------------------------------------|------|--------------------------------------|

| t <sub>1</sub>        | <10                                           | ns   | SDATA-to-SCLK set-up time            |

| $t_2$                 | <10                                           | ns   | SDATA-to-SCLK hold time              |

| $t_3$                 | <25                                           | ns   | SCLK high duration                   |

| t <sub>4</sub>        | <25                                           | ns   | SCLK low duration                    |

| <b>t</b> <sub>5</sub> | <10                                           | ns   | SCLK-to-SLE set-up time              |

| t <sub>6</sub>        | <20                                           | ns   | SLE pulse width                      |

| t <sub>8</sub>        | <25                                           | ns   | SCLK-to-SREAD data valid, readback   |

| t <sub>9</sub>        | <25                                           | ns   | SREAD hold time after SCLK, readback |

| t <sub>10</sub>       | <10                                           | ns   | SCLK-to-SLE disable time, readback   |

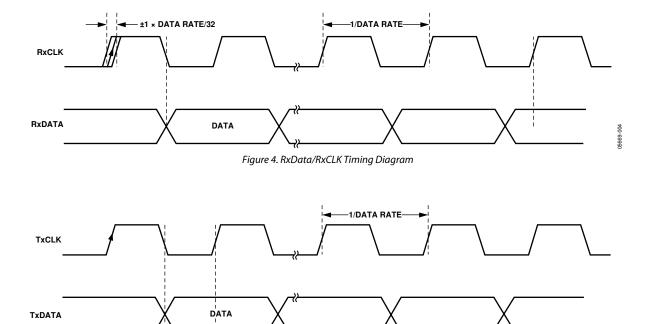

Figure 2. Serial Interface Timing Diagram

Figure 3. Readback Timing Diagram

Figure 5. TxData/TxCLK Timing Diagram

FETCH

NOTES

1. TxCLK ONLY AVAILABLE IN GFSK MODE.

SAMPLE

### **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C, unless otherwise noted.

Table 3.

| Parameter                           | Rating                                      |

|-------------------------------------|---------------------------------------------|

| V <sub>DD</sub> to GND <sup>1</sup> | −0.3 V to +5 V                              |

| Analog I/O Voltage to GND           | $-0.3 \text{ V to AV}_{DD} + 0.3 \text{ V}$ |

| Digital I/O Voltage to GND          | -0.3 V to DV <sub>DD</sub> + 0.3 V          |

| Operating Temperature Range         |                                             |

| Industrial (B Version)              | −40°C to +85°C                              |

| Storage Temperature Range           | −65°C to +125°C                             |

| Maximum Junction Temperature        | 150°C                                       |

| MLF $\theta_{JA}$ Thermal Impedance | 26°C/W                                      |

| Reflow Soldering                    |                                             |

| Peak Temperature                    | 260°C                                       |

| Time at Peak Temperature            | 40 sec                                      |

|                                     |                                             |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

This device is a high performance RF-integrated circuit with an ESD rating of <2 kV. It is ESD sensitive; proper precautions should be taken for handling and assembly.

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

$<sup>^{1}</sup>$  GND = CPGND = RFGND = DGND = AGND = 0 V.

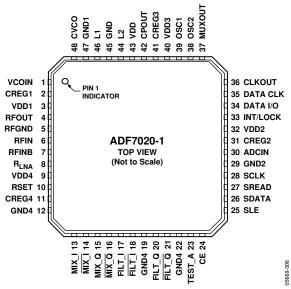

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 6. Pin Configuration

**Table 4. Pin Function Descriptions**

| Pin No.       | Mnemonic         | Description                                                                                                                                                                                                                       |

|---------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | VCOIN            | VCO Input Pin. The tuning voltage on this pin determines the output frequency of the voltage controlled oscillator (VCO). The higher the tuning voltage, the higher the output frequency.                                         |

| 2             | CREG1            | Regulator Voltage for PA Block. A 100 nF in parallel with a 5.1 pF capacitor should be placed between this pin and ground for regulator stability and noise rejection.                                                            |

| 3             | VDD1             | Voltage Supply for PA Block. Decoupling capacitors of 0.1 $\mu$ F and 10 pF should be placed as close as possible to this pin. All $V_{DD}$ pins should be tied together.                                                         |

| 4             | RFOUT            | PA Output Pin. The modulated signal is available at this pin. Output power levels are from –20 dBm to +13 dBm. The output should be impedance matched to the desired load using suitable components. See the Transmitter section. |

| 5             | RFGND            | Ground for Output Stage of Transmitter. All GND pins should be tied together.                                                                                                                                                     |

| 6             | RFIN             | LNA Input for Receiver Section. Input matching is required between the antenna and the differential LNA input to ensure maximum power transfer. See the LNA/PA Matching section.                                                  |

| 7             | RFINB            | Complementary LNA Input. See the LNA/PA Matching section.                                                                                                                                                                         |

| 8             | R <sub>LNA</sub> | External Bias Resistor for LNA. Optimum resistor is 1.1 k $\Omega$ with 5% tolerance.                                                                                                                                             |

| 9             | VDD4             | Voltage Supply for LNA/MIXER Block. This pin should be decoupled to ground with a 10 nF capacitor.                                                                                                                                |

| 10            | RSET             | External Resistor to Set Charge Pump Current and Some Internal Bias Currents. Use 3.6 k $\Omega$ with 5% tolerance.                                                                                                               |

| 11            | CREG4            | Regulator Voltage for LNA/MIXER Block. A 100 nF capacitor should be placed between this pin and GND for regulator stability and noise rejection.                                                                                  |

| 12            | GND4             | Ground for LNA/MIXER Block.                                                                                                                                                                                                       |

| 13 to 18      | MIX/FILT         | Signal Chain Test Pins. These pins are high impedance under normal conditions and should be left unconnected.                                                                                                                     |

| 19, 22        | GND4             | Ground for LNA/MIXER Block.                                                                                                                                                                                                       |

| 20, 21,<br>23 | FILT/TEST_A      | Signal Chain Test Pins. These pins are high impedance under normal conditions and should be left unconnected.                                                                                                                     |

| 24            | CE               | Chip Enable. Bringing CE low puts the ADF7020-1 into complete power-down. Register values are lost when CE is low, and the part must be reprogrammed once CE is brought high.                                                     |

| 25            | SLE              | Load Enable, CMOS Input. When LE goes high, the data stored in the shift registers is loaded into one of the four latches. A latch is selected using the control bits.                                                            |

| 26            | SDATA            | Serial Data Input. The serial data is loaded MSB first, with the 2 LSBs as the control bits. This pin is a high impedance CMOS input.                                                                                             |

| Pin No. | Mnemonic  | Description                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27      | SREAD     | Serial Data Output. This pin is used to feed readback data from the ADF7020-1 to the microcontroller. The SCLK input is used to clock each readback bit (AFC, ADC readback) from the SREAD pin.                                                                                                                                                                                                                             |

| 28      | SCLK      | Serial Clock Input. This serial clock is used to clock in the serial data to the registers. The data is latched into the 24-bit shift register on the CLK rising edge. This pin is a digital CMOS input.                                                                                                                                                                                                                    |

| 29      | GND2      | Ground for Digital Section.                                                                                                                                                                                                                                                                                                                                                                                                 |

| 30      | ADCIN     | Analog-to-Digital Converter Input. The internal 7-bit ADC can be accessed through this pin. Full scale is 0 to 1.9 V. Readback is made using the SREAD pin.                                                                                                                                                                                                                                                                 |

| 31      | CREG2     | Regulator Voltage for Digital Block. A 100 nF in parallel with a 5.1 pF capacitor should be placed between this pin and ground for regulator stability and noise rejection.                                                                                                                                                                                                                                                 |

| 32      | VDD2      | Voltage Supply for Digital Block. A decoupling capacitor of 10 nF should be placed as close as possible to this pin.                                                                                                                                                                                                                                                                                                        |

| 33      | INT/LOCK  | Bidirectional Pin. In output mode (interrupt mode), the ADF7020-1 asserts the INT/LOCK pin when it has found a match for the preamble sequence. In input mode (lock mode), the microcontroller can be used to lock the demodulator threshold when a valid preamble has been detected. Once the threshold is locked, NRZ data can be reliably received. In this mode, a demodulator lock can be asserted with minimum delay. |

| 34      | DATA I/O  | Transmit Data Input/Received Data Output. This is a digital pin and normal CMOS levels apply.                                                                                                                                                                                                                                                                                                                               |

| 35      | DATA CLK  | Transmit/Receive Clock Pin. In receive mode, the pin outputs the synchronized data clock. The positive clock edge is matched to the center of the received data. In GFSK transmit mode, the pin outputs an accurate clock to latch the data from the microcontroller into the transmit section at the exact required data rate. See the Gaussian Frequency Shift Keying (GFSK) section.                                     |

| 36      | CLKOUT    | A Divided-Down Version of the Crystal Reference with Output Driver. The digital clock output can be used to drive several other CMOS inputs such as a microcontroller clock. The output has a 50:50 mark-space ratio.                                                                                                                                                                                                       |

| 37      | MUXOUT    | Multiplexer Output Pin. This pin provides the Lock_Detect signal, which is used to determine if the PLL is locked to the correct frequency. Other signals include Regulator_Ready, which is an indicator of the status of the serial interface regulator.                                                                                                                                                                   |

| 38      | OSC2      | Oscillator Output Pin. The reference crystal should be connected between this pin and OSC1. A TCXO reference can be used by driving this pin with CMOS levels and disabling the crystal oscillator.                                                                                                                                                                                                                         |

| 39      | OSC1      | Oscillator Input Pin. The reference crystal should be connected between this pin and OSC2.                                                                                                                                                                                                                                                                                                                                  |

| 40      | VDD3      | Voltage Supply for the Charge Pump and PLL Dividers. This pin should be decoupled to ground with a 0.01 µF capacitor.                                                                                                                                                                                                                                                                                                       |

| 41      | CREG3     | Regulator Voltage for Charge Pump and PLL Dividers. A 100 nF in parallel with a 5.1 pF capacitor should be placed between this pin and ground for regulator stability and noise rejection.                                                                                                                                                                                                                                  |

| 42      | CPOUT     | Charge Pump Output. This output generates current pulses that are integrated in the loop filter. The integrated current changes the control voltage on the input to the VCO.                                                                                                                                                                                                                                                |

| 43      | VDD       | Voltage Supply for VCO Tank Circuit. This pin should be decoupled to ground with a 0.01 μF capacitor.                                                                                                                                                                                                                                                                                                                       |

| 44, 46  | L2, L1    | External VCO Inductor Pins. A chip inductor should be connected across these pins to set the VCO operating frequency. See the Voltage Controlled Oscillator (VCO) section for details on choosing the appropriate value.                                                                                                                                                                                                    |

| 45, 47  | GND, GND1 | Grounds for VCO Block.                                                                                                                                                                                                                                                                                                                                                                                                      |

| 48      | CVCO      | VCO Noise Compensation Node. A 22 nF capacitor should be placed between this pin and CREG1 to reduce VCO noise.                                                                                                                                                                                                                                                                                                             |

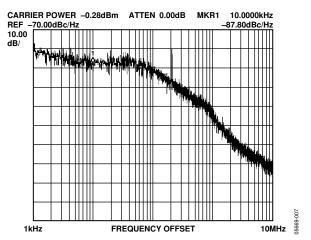

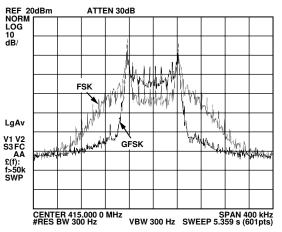

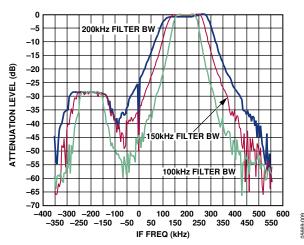

# TYPICAL PERFORMANCE CHARACTERISTICS

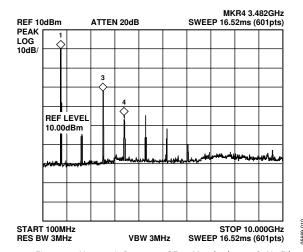

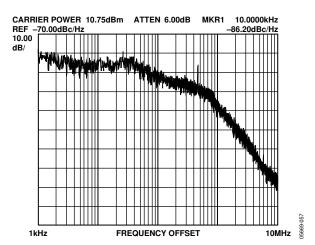

Figure 7. Phase Noise Response at 315 MHz,  $V_{\rm DD}$  = 3.0 V, ICP = 1.5 mA

Figure 8. Output Spectrum in FSK and GFSK Modulation

Figure 9. IF Filter Response

Figure 10. Harmonic Response, RF<sub>OUT</sub> Matched to 50  $\Omega$ , No Filter

Figure 11. Harmonic Response, Murata Dielectric Filter

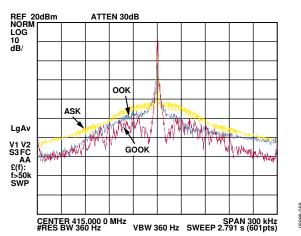

Figure 12. Output Spectrum in ASK, OOK, and GOOK Modes, DR = 10 kbps

Rev. 0 | Page 13 of 48

Figure 13. PA Output Power vs. Setting

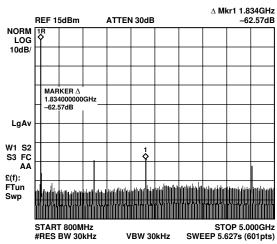

Figure 14. Wideband Interference Rejection. Wanted Signal (880 MHz) at 3 dB above Sensitivity Point Interferer = FM Jammer (9.76 kbps, 10k Deviation)

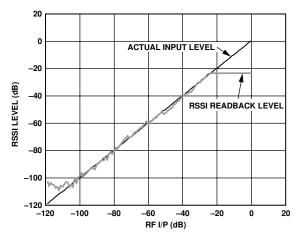

Figure 15. Digital RSSI Readback Linearity

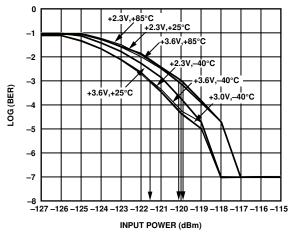

Figure 16. Sensitivity vs.  $V_{DD}$  and Temperature, RF = 315 MHz, DR = 1 kBPS, Correlator Demod

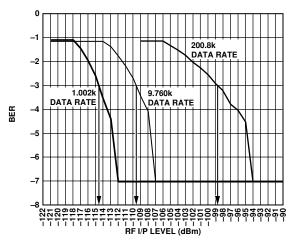

Figure 17. BER vs. Data-Rate (Combined Matching Network) Separate LNA and PA Matching Paths Typically Improve Performance by 2 dB

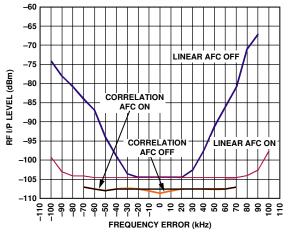

Figure 18. Sensitivity vs. Frequency Error with AFC On/Off

### FREQUENCY SYNTHESIZER

#### REFERENCE INPUT

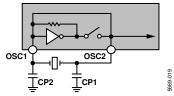

The on-board crystal oscillator circuitry (see Figure 19) can use an inexpensive quartz crystal as the PLL reference. The oscillator circuit is enabled by setting R1\_DB12 high. It is enabled by default on power-up and is disabled by bringing CE low. Errors in the crystal can be corrected using the automatic frequency control (see the AFC Section) feature or by adjusting the fractional-N value (see the N Counter section). A single-ended reference (TCXO, CXO) can also be used. The CMOS levels should be applied to OSC2 with R1\_DB12 set low.

Figure 19. Oscillator Circuit on the ADF7020-1

Two parallel resonant capacitors are required for oscillation at the correct frequency; their values are dependent on the crystal specification. They should be chosen so that the series value of capacitance added to the PCB track capacitance adds up to the load capacitance of the crystal, usually 20 pF. Track capacitance values vary from 2 pF to 5 pF, depending on board layout. Where possible, choose capacitors that have a very low temperature coefficient to ensure stable frequency operation over all conditions.

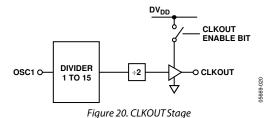

#### **CLKOUT Divider and Buffer**

The CLKOUT circuit takes the reference clock signal from the oscillator section (see Figure 19) and supplies a divided-down 50:50 mark-space signal to the CLKOUT pin. An even divide from 2 to 30 is available. This divide number is set in R1\_DB (8:11). On power-up, the CLKOUT defaults to the divide-by-8 block.

To disable CLKOUT, set the divide number to 0. The output buffer can drive up to a 20 pF load with a 10% rise time at 4.8 MHz. Faster edges can result in some spurious feedthrough to the output. A small series resistor (50  $\Omega$ ) can be used to slow the clock edges to reduce these spurs at F<sub>CLK</sub>.

#### R Counter

The 3-bit R counter divides the reference input frequency by an integer from 1 to 7. The divided-down signal is presented as the reference clock to the phase frequency detector (PFD). The divide ratio is set in Register 1. Maximizing the PFD frequency reduces the N value. This reduces the noise multiplied at a rate of  $20 \log(N)$  to the output, as well as reducing occurrences of spurious components. The R Register defaults to R=1 on power-up:

$$PFD$$

[Hz] =  $XTAL/R$

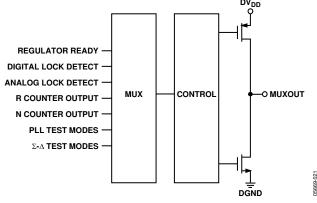

#### **MUXOUT and Lock Detect**

The MUXOUT pin allows the user to access various digital points in the ADF7020-1. The state of MUXOUT is controlled by Bits R0 DB (29:31).

#### **Regulator Ready**

Regulator ready is the default setting on MUXOUT after the transceiver has been powered up. The power-up time of the regulator is typically 50  $\mu s$ . Because the serial interface is powered from the regulator, the regulator must be at its nominal voltage before the ADF7020-1 can be programmed. The status of the regulator can be monitored at MUXOUT. When the regulator ready signal on MUXOUT is high, programming of the ADF7020-1 can begin.

Figure 21. MUXOUT Circuit

#### **Digital Lock Detect**

Digital lock detect is active high. The lock detect circuit is located at the PFD. When the phase error on five consecutive cycles is less than 15 ns, lock detect is set high. Lock detect remains high until 25 ns phase error is detected at the PFD. Because no external components are needed for digital lock detect, it is more widely used than analog lock detect.

#### **Analog Lock Detect**

This N-channel, open-drain lock detect should be operated with an external pull-up resistor of  $10~k\Omega$  nominal. When a lock has been detected, this output is high with narrow low-going pulses.

#### **Voltage Regulators**

The ADF7020-1 contains four regulators to supply stable voltages to the part. The nominal regulator voltage is 2.3 V. Each regulator should have a 100 nF capacitor connected between CREG and GND. When CE is high, the regulators and other associated circuitry are powered on, drawing a total supply current of 2 mA. Bringing the chip-enable pin low disables the regulators, reduces the supply current to less than 1  $\mu A$ , and erases all values held in the registers. The serial interface operates from a regulator supply; therefore, to write to the part, the user must have CE high and the regulator voltage must be stabilized. Regulator status (CREG4) can be monitored using the regulator ready signal from muxout.

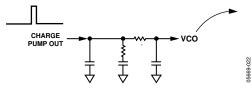

#### Loop Filter

The loop filter integrates the current pulses from the charge pump to form a voltage that tunes the output of the VCO to the desired frequency. It also attenuates spurious levels generated by the PLL. A typical loop-filter design is shown in Figure 22.

Figure 22. Typical Loop-Filter Configuration

In FSK, the loop should be designed so that the loop bandwidth (LBW) is approximately 5 times the data rate. Widening the LBW excessively reduces the time spent jumping between frequencies, but can cause insufficient spurious attenuation.

For ASK systems, a wider LBW is recommended. The sudden large transition between two power levels might result in VCO pulling and can cause a wider output spectrum than is desired. By widening the LBW to more than 10 times the data rate, the amount of VCO pulling is reduced, because the loop settles quickly back to the correct frequency. The wider LBW might restrict the output power and data rate of ASK-based systems more than it would that of FSK-based systems.

Narrow-loop bandwidths can result in the loop taking long periods of time to attain lock. Careful design of the loop filter is critical to obtaining accurate FSK/GFSK modulation.

For GFSK, it is recommended that an LBW of 2.0 to 2.5 times the data rate be used to ensure that sufficient samples are taken of the input data while filtering system noise. The free design tool ADIsimPLL can be used to design loop filters for the ADF7020-1.

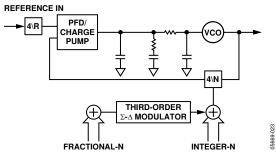

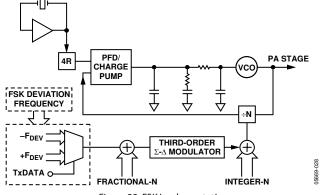

#### N Counter

The feedback divider in the ADF7020-1 PLL consists of an 8-bit integer counter and a 15-bit  $\Sigma$ - $\Delta$  fractional-N divider. The integer counter is the standard pulse-swallow type common in PLLs. This sets the minimum integer divide value to 31. The fractional divide value gives very fine resolution at the output, where the output frequency of the PLL is calculated as

$$Fout = \frac{XTAL}{R} \times (Integer - N + \frac{Fractional - N}{2^{15}})$$

Figure 23. Fractional-N PLL

The combination of the integer-N (maximum = 255) and the fractional-N (maximum = 16,383/16,384) give a maximum N divider of 255 + 1. Therefore, the minimum usable PFD is

$PFD_{MIN}$  [Hz] = Maximum Required Output Frequency/(255 + 1)

For example, when operating at 620 MHz, PFD  $_{\mbox{\scriptsize MIN}}$  equals 2.42 MHz.

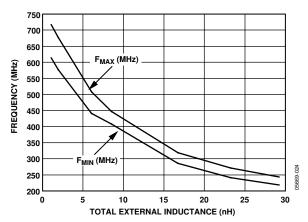

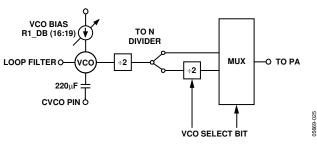

### Voltage Controlled Oscillator (VCO)

The ADF7020-1 features an on-chip VCO with external tank inductor, which is used to set the frequency range. The center frequency of the VCO is set by the internal varactor capacitance and the combined inductance of the external chip inductor, bond wire, and PCB track. A plot of VCO operating range vs. total external inductance (chip inductor + PCB track) is shown in Figure 24. The inductance for a PCB track using FR4 material is approximately 0.57 nH/mm. This should be subtracted from the total value to determine the correct chip inductor value.

An additional frequency divide-by-2 block is included to allow operation from 80 MHz to 325 MHz. To enable the divide-by-2 block, set R1\_DB13 to 1.

The VCO can be recentered, depending on the required frequency of operation, by programming the VCO adjust bits R1 DB (20:21).

The VCO is enabled as part of the PLL by the PLL-enable bit, R0 DB28.

The VCO needs an external 22 nF between the VCO and the regulator to reduce internal noise.

Figure 24. External Inductance vs. Frequency

#### **VCO Bias Current**

VCO bias current can be adjusted using Bits R1\_DB19 to R1\_DB16. To minimize current consumption, the bias current setting should be as indicated in Table 5.

Table 5. Recommended VCO Bias Currents

| Direct Frequency Output (f) | VCO Bias R1_DB(19:16) |

|-----------------------------|-----------------------|

| f < 200 MHz                 | 0001                  |

| 200 MHz < f < 450 MHz       | 0010                  |

| f > 450 MHz                 | 0011                  |

Figure 25. Voltage Controlled Oscillator (VCO)

# CHOOSING CHANNELS FOR BEST SYSTEM PERFORMANCE

The fractional-N PLL allows the selection of any channel within 80 MHz to 650 MHz to a resolution of <300 Hz. This also facilitates frequency-hopping systems.

Careful selection of the RF transmit channels must be made to achieve best spurious performance. The architecture of fractional-N results in some level of the nearest integer channel moving through the loop to the RF output. These beat-note spurs are not attenuated by the loop if the desired RF channel and the nearest integer channel are separated by a frequency of less than the LBW.

The occurrence of beat-note spurs is rare, because the integer frequencies are at multiples of the reference, which is typically >10 MHz.

The amplitude of beat-note spurs can be significantly reduced by using the frequency doubler to avoid very small or very large values in the fractional register. By having a channel 1 MHz away from an integer frequency, a 100 kHz loop filter can reduce the level to < 45 dBc.

### **TRANSMITTER**

#### **RF OUTPUT STAGE**

The PA of the ADF7020-1 is based on a single-ended, controlled current, open-drain amplifier that has been designed to deliver up to 13 dBm into a 50  $\Omega$  load at a maximum frequency of 650 MHz.

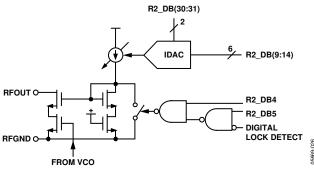

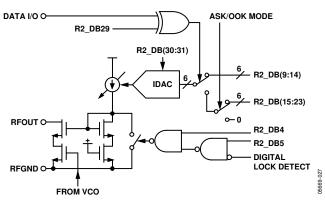

The PA output current and, consequently, the output power are programmable over a wide range. The PA configurations in FSK/GFSK and ASK/OOK modulation modes are shown in Figure 26 and Figure 27, respectively. In FSK/GFSK modulation mode, the output power is independent of the state of the DATA\_IO pin. In ASK/OOK modulation mode, it is dependent on the state of the DATA\_IO pin and Bit R2\_DB29, which selects the polarity of the TxData input. For each transmission mode, the output power can be adjusted as follows:

- FSK/GFSK: The output power is set using bits R2 DB (9:14).

- ASK: The output power for the inactive state of the TxData input is set by Bits R2\_DB (15:20). The output power for the active state of the TxData input is set by Bits R2\_DB (9:14).

- OOK: The output power for the active state of the TxData input is set by Bits R2\_DB (9:14). The PA is muted when the TxData input is inactive.

Figure 26. PA Configuration in FSK/GFSK Mode

Figure 27. PA Configuration in ASK/OOK Mode

The PA is equipped with overvoltage protection, which makes it robust in severely mismatched conditions. Depending on the application, users can design a matching network for the PA to exhibit optimum efficiency at the desired radiated output power level for a wide range of different antennas, such as loop or monopole antennas. See the LNA/PA Matching section for details.

#### **PA Bias Currents**

Control Bits R2\_DB (30:31) facilitate an adjustment of the PA bias current to further extend the output power control range, if necessary. If this feature is not required, the default value of 9  $\mu$ A is recommended. The output stage is powered down by resetting Bit R2\_DB4. To reduce the level of undesired spurious emissions, the PA can be muted during the PLL lock phase by toggling this bit.

#### **MODULATION SCHEMES**

#### Frequency Shift Keying (FSK)

Frequency shift keying is implemented by setting the N value for the center frequency and then toggling this with the TxData line. The deviation from the center frequency is set using Bits R2\_DB (15:23). The deviation from the center frequency in hertz is

$$FSK_{DEVIATION}$$

[Hz] =  $\frac{PFD \times Modulation \ Number}{2^{14}}$

where *Modulation Number* is a number from 1 to 511 (R2\_DB (15:23)).

Select FSK using Bits R2\_DB (6:8).

Figure 28. FSK Implementation

#### Gaussian Frequency Shift Keying (GFSK)

Gaussian frequency shift keying reduces the bandwidth occupied by the transmitted spectrum by digitally prefiltering the TxData. A TxCLK output line is provided from the ADF7020-1 for synchronization of TxData from the microcontroller. The TxCLK line can be connected to the clock input of a shift register that clocks data to the transmitter at the exact data rate.

#### Setting Up the ADF7020-1 for GFSK

To set up the frequency deviation, set the PFD and the modulator control bits according to the following equation:

$$GFSK_{DEVIATION} [Hz] = \frac{PFD \times 2^m}{2^{12}}$$

where *m* is GFSK\_MOD\_CONTROL set using R2\_DB (24:26).

To set up the GFSK data rate, set the PFD and the modulator control bits according to the following equation:

$$DR[bps] = \frac{PFD}{DIVIDER\_FACTOR \times INDEX\_COUNTER}$$

where DIVIDER\_FACTOR and INDEX\_COUNTER are programmed in Bits R2\_DB (15:21) and R2\_DB (27:28), respectively. For further information, see the Using GFSK on the ADF7010 section in the EVAL-ADF7010EB1 data sheet.

#### Amplitude Shift Keying (ASK)

Amplitude shift keying is implemented by switching the output stage between two discrete power levels. This is accomplished by toggling the DAC, which controls the output level between two 6-bit values set up in Register 2. A 0 TxData bit sends Bits R2\_DB (15:20) to the DAC. A high TxData bit sends Bits R2\_DB (9:14) to the DAC. A maximum modulation depth of 30 dB is possible.

#### On-Off Keying (OOK)

On-off keying is implemented by switching the output stage to a certain power level for a high TxData bit and switching the output stage off for a low TxData bit. For OOK, the transmitted power for a high input is programmed using Bits R2\_DB (9:14).

#### Gaussian On-Off Keying (GOOK)

Gaussian on-off keying represents a prefiltered form of OOK modulation. The usually sharp symbol transitions are replaced with smooth Gaussian filtered transitions, the result being a reduction in frequency pulling of the VCO. Frequency pulling of the VCO in OOK mode can lead to a wider than desired BW, especially if it is not possible to increase the loop-filter BW > 300 kHz. The GOOK sampling clock samples data at the data rate. (See the Setting Up the ADF7020-1 for GFSK section.)

### RECEIVER SECTION

#### **RF FRONT END**

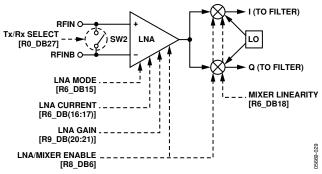

The ADF7020-1 is based on a fully integrated, low IF receiver architecture. The low IF architecture facilitates a very low external component count and does not suffer from power-line-induced interference problems.

Figure 29 shows the structure of the receiver front end. The many programming options allow users to trade off sensitivity, linearity, and current consumption for each other in the most suitable way for their applications. To achieve a high level of resilience against spurious reception, the LNA features a differential input. Switch SW2 shorts the LNA input when transmit mode is selected (R0\_DB27 = 0). This feature facilitates the design of a combined LNA/PA matching network, avoiding the need for an external Rx/Tx switch. See the LNA/PA Matching section for details on the design of the matching network.

Figure 29. ADF7020-1 RF Front End

The LNA is followed by a quadrature down conversion mixer, which converts the RF signal to the IF frequency of 200 kHz. It is important to consider that the output frequency of the synthesizer must be programmed to a value 200 kHz below the center frequency of the received channel.

The LNA has two basic operating modes: high gain/low noise mode and low gain/low power mode. To switch between these two modes, use the LNA\_mode bit, R6\_DB15. The mixer is also configurable between a low current and an enhanced linearity mode using the mixer\_linearity bit, R6\_DB18.

Based on the specific sensitivity and linearity requirements of the application, it is recommended to adjust control bits LNA\_mode (R6\_DB15) and mixer\_linearity (R6\_DB18) as outlined in Table 6.

The gain of the LNA is configured by the LNA\_gain field, R9\_DB (20:21), and can be set by either the user or the automatic gain control (AGC) logic.

#### IF Filter Settings/Calibration