Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# High Performance Narrow-Band Transceiver IC

Data Sheet ADF7021

#### **FEATURES**

Low power, narrow-band transceiver

Frequency bands using dual VCO

80 MHz to 650 MHz

862 MHz to 950 MHz

Modulation schemes

2FSK, 3FSK, 4FSK, MSK

Spectral shaping

Gaussian and raised cosine filtering

Data rates supported

0.05 kbps to 32.8 kbps

2.3 V to 3.6 V power supply

Programmable output power

–16 dBm to +13 dBm in 63 steps

Automatic PA ramp control

Receiver sensitivity

-130 dBm at 100 bps, 2FSK

-122 dBm at 1 kbps, 2FSK

-113 dBm at 25 kbps, raised cosine 2FSK

Patent pending, on-chip image rejection calibration

On-chip VCO and fractional-N PLL

On-chip, 7-bit ADC and temperature sensor

Fully automatic frequency control loop (AFC)

Digital received signal strength indication (RSSI)

Integrated Tx/Rx switch

0.1 µA leakage current in power-down mode

#### **APPLICATIONS**

Narrow-band standards ETSI EN 300 220, FCC Part 15, FCC Part 90, FCC Part 95, ARIB STD-T67

Low cost, wireless data transfer

Remote control/security systems

Wireless metering

Private mobile radio

Wireless medical telemetry service (WMTS)

Keyless entry

Home automation

Process and building control

Pagers

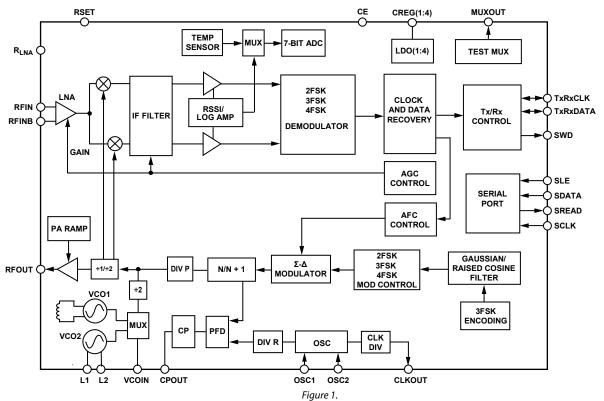

#### **FUNCTIONAL BLOCK DIAGRAM**

Rev. D

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2007–2016 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

## ADF7021\* PRODUCT PAGE QUICK LINKS

Last Content Update: 02/23/2017

## COMPARABLE PARTS 🖵

View a parametric search of comparable parts.

## **EVALUATION KITS**

· ADF7021 Evaluation Boards

#### **DOCUMENTATION**

#### **Application Notes**

- AN-0987: Designing a Wireless Transceiver System to Meet the Wireless M-Bus Standard

- AN-1182: Understanding and Optimizing the AFC Loop on the ADF7021 for Minimum Preamble

- AN-1258: Image Rejection Calibration on the ADF7021, ADF7021-N, and ADF7021-V

- AN-1285: ADF7021-N Radio Performance for Wireless Meter-Bus (WM-Bus), Mode N

- AN-1389: Recommended Rework Procedure for the Lead Frame Chip Scale Package (LFCSP)

- AN-771: ADSP-BF533 EZ-KIT Lite and ADF70xx Interface

- AN-772: A Design and Manufacturing Guide for the Lead Frame Chip Scale Package (LFCSP)

- AN-852: Using the Test DAC on the ADF702x to Implement Functions Such as Analog FM DEMOD, SNR Measurement, FEC Decoding, and PSK/4FSK Demodulation

- AN-859: RF Port Impedance Data, Matching, and External Component Selection for the ADF7020-1, ADF7021, and ADF7021-N

- AN-915: CDR Operation for ADF7020, ADF7020-1, ADF7021, and ADF7025

#### **Data Sheet**

ADF7021: High Performance Narrow-Band Transceiver IC Data Sheet

## SOFTWARE AND SYSTEMS REQUIREMENTS 🖳

- · ADF70xx Evaluation Software

- ADIismLINK Development Platform

#### TOOLS AND SIMULATIONS $\Box$

## REFERENCE MATERIALS 🖵

#### **Product Selection Guide**

RF Source Booklet

#### **Solutions Bulletins & Brochures**

• Emerging Energy Applications Solutions Bulletin, Volume 10. Issue 4

#### **Technical Articles**

- Innovative Line Sensor Design with ADI Energy Harvesting and Low Power Signal Chain

- · Low Power, Low Cost, Wireless ECG Holter Monitor

- RF Meets Power Lines: Designing Intelligent Smart Grid Systems that Promote Energy Efficiency

- Smart Metering Technology Promotes Energy Efficiency for a Greener World

- The Next Generation of Line Sensors: Power Harvested, Connected, and Lower Maintenance

- The Use of Short Range Wireless in a Multi-Metering System

- Understand Wireless Short-Range Devices for Global License-Free Systems

- Wireless Short Range Devices and Narrowband Communications

- Wireless Technologies for Smart Meters: Focus on Water Metering

## DESIGN RESOURCES 🖵

- · ADF7021 Material Declaration

- PCN-PDN Information

- · Quality And Reliability

- Symbols and Footprints

## **DISCUSSIONS**

View all ADF7021 EngineerZone Discussions.

## SAMPLE AND BUY 🖳

Visit the product page to see pricing options.

## TECHNICAL SUPPORT 🖵

Submit a technical question or find your regional support number.

Submit feedback for this data sheet.

This page is dynamically generated by Analog Devices, Inc., and inserted into this data sheet. A dynamic change to the content on this page will not trigger a change to either the revision number or the content of the product data sheet. This dynamic page may be frequently modified.

## **ADF7021**

## **TABLE OF CONTENTS**

| Features                                      | 1  |

|-----------------------------------------------|----|

| Applications                                  | 1  |

| Functional Block Diagram                      | 1  |

| Revision History                              | 3  |

| General Description                           | 4  |

| Specifications                                | 5  |

| RF and PLL Specifications                     | 5  |

| Transmission Specifications                   | 6  |

| Receiver Specifications                       | 8  |

| Digital Specifications                        | 10 |

| General Specifications                        | 11 |

| Timing Characteristics                        | 11 |

| Absolute Maximum Ratings                      | 15 |

| ESD Caution                                   | 15 |

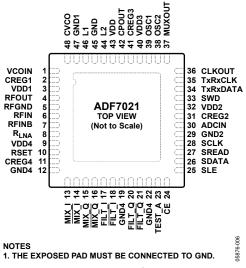

| Pin Configuration and Function Descriptions   | 16 |

| Typical Performance Characteristics           | 18 |

| Frequency Synthesizer                         | 22 |

| Reference Input                               | 22 |

| MUXOUT                                        | 23 |

| Voltage Controlled Oscillator (VCO)           | 24 |

| Choosing Channels for Best System Performance | 25 |

| Transmitter                                   | 26 |

| RF Output Stage                               | 26 |

| Modulation Schemes                            | 26 |

| Spectral Shaping                              | 28 |

| Modulation and Filtering Options              | 29 |

| Transmit Latency                              | 29 |

| Test Pattern Generator                        | 29 |

| Receiver Section                              | 30 |

| RF Front End                                  | 30 |

| IF Filter                                     | 30 |

| RSSI/AGC                                      | 31 |

| Demodulation, Detection, and CDR              | 32 |

| <del>-</del>                               |      |

|--------------------------------------------|------|

| Demodulator Considerations                 | . 36 |

| AFC Operation                              | . 36 |

| Automatic Sync Word Detection (SWD)        | . 37 |

| Applications Information                   | . 38 |

| IF Filter Bandwidth Calibration            | . 38 |

| LNA/PA Matching                            | . 38 |

| Image Rejection Calibration                | . 39 |

| Packet Structure and Coding                | . 41 |

| Applications Circuit                       | . 44 |

| Serial Interface                           | . 45 |

| Readback Format                            | . 45 |

| Interfacing to Microcontroller/DSP         | . 46 |

| Register 0—N Register                      | . 47 |

| Register 1—VCO/Oscillator Register         | . 47 |

| Register 2—Transmit Modulation Register    | . 49 |

| Register 3—Transmit/Receive Clock Register | . 50 |

| Register 4—Demodulator Setup Register      | . 51 |

| Register 5—IF Filter Setup Register        | . 52 |

| Register 6—IF Fine Cal Setup Register      | . 53 |

| Register 7—Readback Setup Register         | . 54 |

| Register 8—Power-Down Test Register        | . 55 |

| Register 9—AGC Register                    | . 56 |

| Register 10—AFC Register                   | . 57 |

| Register 11—Sync Word Detect Register      | . 58 |

| Register 12—SWD/Threshold Setup Register   | . 58 |

| Register 13—3FSK/4FSK Demod Register       | . 59 |

| Register 14—Test DAC Register              | . 60 |

| Register 15—Test Mode Register             | . 61 |

| Outline Dimensions                         |      |

| Ordering Guide                             | . 62 |

#### **REVISION HISTORY**

| 9/2016—Rev. C to Rev. D                                    |

|------------------------------------------------------------|

| Changes to General Description Section4                    |

| Changes to Interfacing to Microcontroller/DSP Section and  |

| Figure 58                                                  |

| 10 lead of D. D. D. G.                                     |

| 10/2014—Rev. B to Rev. C                                   |

| Changes to Table 816                                       |

| Change to Figure 3624                                      |

| Change to IF Filter Fine Calibration Overview Section30 $$ |

| Change to Post Demodulator Filter Setup Section34          |

| Change to Battery Voltage/ADCIN/Temperature Sensor         |

| Readback Section45                                         |

| Change to Register 4—Demodulator Setup Register Section51  |

| Change to Register 7—Readback Setup Register Section54     |

| Change to Register 10—AFC Register Section57               |

|                                                            |

| 4/2013—Rev. A to Rev. B                                    |

| Changes to Figure 1016                                     |

| Updated Outline Dimensions62                               |

| Changes to Ordering Guide62                                |

#### 9/2007—Rev. 0 to Rev. A

| Change to UART/SPI Mode Section                         | 14 |

|---------------------------------------------------------|----|

| Changes to Figure 10                                    | 16 |

| Change to Table 8                                       |    |

| Changes to Figure 12                                    | 18 |

| Change to Internal Inductor VCO Section                 | 24 |

| Changes to Figure 40                                    | 26 |

| Changes to Figure 47                                    |    |

| Change to Table 19                                      |    |

| Changes to Figure 56                                    |    |

| Change to SPI Mode Section                              | 46 |

| Changes to Figure 59                                    |    |

| Changes to Figure 60                                    |    |

| Change to Register 3—Transmit/Receive Clock             |    |

| Register Section                                        | 50 |

| Change to Register 4—Demodulator Setup Register Section |    |

| Change to Register 7—Readback Setup Register            |    |

| Change to Register 13—3FSK/4FSK Demod Register Heading  |    |

3/2007—Revision 0: Initial Version

#### **GENERAL DESCRIPTION**

The ADF7021 is a high performance, low power, highly integrated 2FSK/3FSK/4FSK transceiver. It is designed to operate in the narrowband, license-free ISM bands, and in the licensed bands with frequency ranges of 80 MHz to 650 MHz and 862 MHz to 950 MHz. The device has both Gaussian and raised cosine transmit data filtering options to improve spectral efficiency for narrowband applications. It is suitable for circuit applications targeted at European ETSI EN 300 220, the Japanese ARIB STD-T67, the Chinese short range device regulations, and the North American FCC Part 15, Part 90, and Part 95 regulatory standards. A complete transceiver can be built using a small number of external discrete components, making the ADF7021 very suitable for price sensitive and area sensitive applications.

The range of on-chip FSK modulation and data filtering options allows users greater flexibility in their choice of modulation schemes while meeting tight spectral efficiency requirements. The ADF7021 also supports protocols that dynamically switch between 2FSK/3FSK/4FSK to maximize communication range and data throughput.

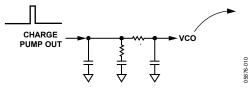

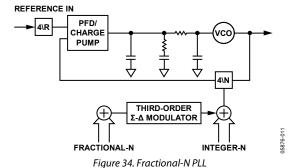

The transmit section contains dual voltage controlled oscillators (VCOs) and a low noise fractional-N PLL with an output resolution of <1 ppm. The ADF7021 has a VCO using an internal LC tank (431 MHz to 475 MHz, 862 MHz to 950 MHz) and a VCO using an external inductor as part of its tank circuit (80 MHz to 650 MHz). The dual VCO design allows dual-band operation where the user can transmit and/or receive at any frequency supported by the internal inductor VCO and can also transmit and/or receive at a particular frequency band supported by the external inductor VCO.

The frequency agile PLL allows the ADF7021 to be used in frequency hopping spread spectrum (FHSS) systems. Both VCOs operate at twice the fundamental frequency to reduce spurious emissions and frequency pulling problems.

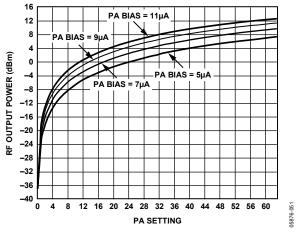

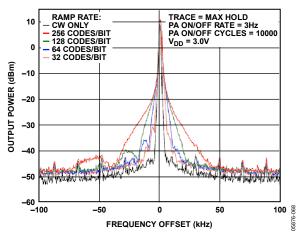

The transmitter output power is programmable in 63 steps from  $-16~\mathrm{dBm}$  to  $+13~\mathrm{dBm}$ , and has an automatic power ramp control to prevent spectral splatter and help meet regulatory standards. The transceiver RF frequency and modulation are programmable using a simple 3-wire interface. The device operates with a power supply range of 2.3 V to 3.6 V and can be powered down when not in use.

A low IF architecture is used in the receiver (100 kHz), which minimizes power consumption and the external component count, yet avoids dc offset and flicker noise at low frequencies. The IF filter has programmable bandwidths of 12.5 kHz, 18.75 kHz, and 25 kHz. The ADF7021 supports a wide variety of programmable features including Rx linearity, sensitivity, and IF bandwidth, allowing the user to trade off receiver sensitivity and selectivity against current consumption, depending on the application. The receiver also features a patent-pending automatic frequency control (AFC) loop with programmable pull-in range that allows the PLL to track out the frequency error in the incoming signal.

The receiver achieves an image rejection performance of 56 dB using a patent-pending IR calibration scheme that does not require the use of an external RF source.

An on-chip ADC provides readback of the integrated temperature sensor, external analog input, battery voltage, and RSSI signal, which provides savings on an ADC in some applications. The temperature sensor is accurate to  $\pm 10^{\circ}\text{C}$  over the full operating temperature range of  $-40^{\circ}\text{C}$  to +85°C. This accuracy can be improved by performing a 1-point calibration at room temperature and storing the result in memory.

## **SPECIFICATIONS**

$V_{DD} = 2.3 \text{ V}$  to 3.6 V, GND = 0 V,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical specifications are at  $V_{DD} = 3$  V,  $T_A = 25$ °C. All measurements are performed with the EVAL-ADF7021DB evaluation boards using the PN9 data sequence, unless otherwise noted.

#### **RF AND PLL SPECIFICATIONS**

Table 1.

| Parameter                                             | Min    | Тур         | Max   | Unit   | Test Conditions/Comments                                                                                       |

|-------------------------------------------------------|--------|-------------|-------|--------|----------------------------------------------------------------------------------------------------------------|

| RF CHARACTERISTICS                                    |        |             |       |        | See Table 9 for required VCO_BIAS and VCO_ADJUST settings                                                      |

| Frequency Ranges (Direct Output)                      | 160    |             | 650   | MHz    | External inductor VCO                                                                                          |

|                                                       | 862    |             | 950   | MHz    | Internal inductor VCO                                                                                          |

| Frequency Ranges (RF Divide-by-2 Mode)                | 80     |             | 325   | MHz    | External inductor VCO, RF divide-by-2 enabled                                                                  |

|                                                       | 431    |             | 475   | MHz    | Internal inductor VCO, RF divide-by-2 enabled                                                                  |

| Phase Frequency Detector (PFD) Frequency <sup>1</sup> | RF/256 |             | 26/30 | MHz    | Crystal reference/external reference                                                                           |

| PHASE-LOCKED LOOP (PLL)                               |        |             |       |        |                                                                                                                |

| VCO Gain <sup>2</sup>                                 |        |             |       |        |                                                                                                                |

| 868 MHz, Internal Inductor VCO                        |        | 58          |       | MHz/V  | VCO_ADJUST = 0, VCO_BIAS = 8                                                                                   |

| 434 MHz, Internal Inductor VCO                        |        | 29          |       | MHz/V  | VCO_ADJUST = 0, VCO_BIAS = 8                                                                                   |

| 426 MHz, External Inductor VCO                        |        | 27          |       | MHz/V  | VCO_ADJUST = 0, VCO_BIAS = 3                                                                                   |

| 160 MHz, External Inductor VCO                        |        | 6           |       | MHz/V  | VCO_ADJUST = 0, VCO_BIAS = 2                                                                                   |

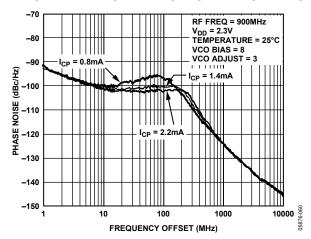

| Phase Noise (In-Band)                                 |        |             |       |        |                                                                                                                |

| 868 MHz, Internal Inductor VCO                        |        | <b>-97</b>  |       | dBc/Hz | 10 kHz offset, PA = 10 dBm, V <sub>DD</sub> = 3.0 V,<br>PFD = 19.68 MHz, VCO_BIAS = 8                          |

| 433 MHz, Internal Inductor VCO                        |        | -103        |       | dBc/Hz | 10 kHz offset, PA = 10 dBm, V <sub>DD</sub> = 3.0 V,<br>PFD = 19.68 MHz, VCO_BIAS = 8                          |

| 426 MHz, External Inductor VCO                        |        | -95         |       | dBc/Hz | 10 kHz offset, PA = 10 dBm, V <sub>DD</sub> = 3.0 V,<br>PFD = 9.84 MHz, VCO_BIAS = 3                           |

| Phase Noise (Out-of-Band)                             |        | -124        |       | dBc/Hz | 1 MHz offset, $f_{RF}$ = 433 MHz, PA = 10 dBm,<br>$V_{DD}$ = 3.0 V, PFD = 19.68 MHz, VCO_BIAS = 8              |

| Normalized In-Band Phase Noise Floor <sup>3</sup>     |        | -203        |       | dBc/Hz |                                                                                                                |

| PLL Settling                                          |        | 40          |       | μs     | Measured for a 10 MHz frequency step to within 5 ppm accuracy, PFD = 19.68 MHz, loop bandwidth (LBW) = 100 kHz |

| REFERENCE INPUT                                       |        |             |       |        |                                                                                                                |

| Crystal Reference⁴                                    | 3.625  |             | 26    | MHz    |                                                                                                                |

| External Oscillator <sup>4, 5</sup>                   | 3.625  |             | 30    | MHz    |                                                                                                                |

| Crystal Start-Up Time <sup>6</sup>                    |        |             |       |        |                                                                                                                |

| XTAL Bias = 20 μA                                     |        | 0.930       |       | ms     | 10 MHz XTAL, 33 pF load capacitors, $V_{DD} = 3.0 \text{ V}$                                                   |

| XTAL Bias = $35 \mu A$                                |        | 0.438       |       | ms     | 10 MHz XTAL, 33 pF load capacitors, $V_{DD} = 3.0 \text{ V}$                                                   |

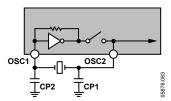

| Input Level for External Oscillator <sup>7</sup>      |        |             |       |        |                                                                                                                |

| OSC1                                                  |        | 0.8         |       | V p-p  | Clipped sine wave                                                                                              |

| OSC2                                                  |        | CMOS levels |       | V      |                                                                                                                |

| ADC PARAMETERS                                        |        |             |       |        |                                                                                                                |

| INL                                                   |        | ±0.4        |       | LSB    | $V_{DD} = 2.3 \text{ V to } 3.6 \text{ V}, T_A = 25^{\circ}\text{C}$                                           |

| DNL                                                   |        | ±0.4        |       | LSB    | $V_{DD} = 2.3 \text{ V to } 3.6 \text{ V}, T_A = 25^{\circ}\text{C}$                                           |

<sup>&</sup>lt;sup>1</sup> The maximum usable PFD at a particular RF frequency is limited by the minimum N divide value.

<sup>&</sup>lt;sup>2</sup> VCO gain measured at a VCO tuning voltage of 1 V. The VCO gain varies across the tuning range of the VCO. The software package ADIsimPLL™ can be used to model this variation.

<sup>&</sup>lt;sup>3</sup> This value can be used to calculate the in-band phase noise for any operating frequency. Use the following equation to calculate the in-band phase noise performance as seen at the PA output: –203 + 10 log(f<sub>PFD</sub>) + 20 logN.

<sup>&</sup>lt;sup>4</sup> Guaranteed by design. Sample tested to ensure compliance.

<sup>&</sup>lt;sup>5</sup> A TCXO, VCXO, or OCXO can be used as an external oscillator.

<sup>&</sup>lt;sup>6</sup> Crystal start-up time is the time from chip enable (CE) being asserted to correct clock frequency on the CLKOUT pin.

<sup>&</sup>lt;sup>7</sup> Refer to the Reference Input section for details on using an external oscillator.

### TRANSMISSION SPECIFICATIONS

Table 2.

| Parameter                                            | Min   | Тур        | Max               | Unit | Test Conditions/Comments                                                                                                                                                                       |  |

|------------------------------------------------------|-------|------------|-------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| DATA RATE                                            |       |            |                   |      |                                                                                                                                                                                                |  |

| 2FSK, 3FSK                                           | 0.05  |            | 25 <sup>1</sup>   | kbps | IF_BW = 25 kHz                                                                                                                                                                                 |  |

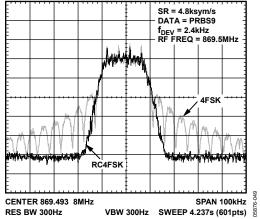

| 4FSK                                                 | 0.05  |            | 32.8 <sup>2</sup> | kbps | IF_BW = 25 kHz                                                                                                                                                                                 |  |

| MODULATION                                           |       |            |                   |      |                                                                                                                                                                                                |  |

| Frequency Deviation (f <sub>DEV</sub> ) <sup>3</sup> | 0.056 |            | 28.26             | kHz  | PFD = 3.625 MHz                                                                                                                                                                                |  |

|                                                      | 0.306 |            | 156               | kHz  | PFD = 20 MHz                                                                                                                                                                                   |  |

| <b>Deviation Frequency Resolution</b>                | 56    |            |                   | Hz   | PFD = 3.625 MHz                                                                                                                                                                                |  |

| Gaussian Filter BT                                   |       | 0.5        |                   |      |                                                                                                                                                                                                |  |

| Raised Cosine Filter Alpha                           |       | 0.5/0.7    |                   |      | Programmable                                                                                                                                                                                   |  |

| TRANSMIT POWER                                       |       |            |                   |      |                                                                                                                                                                                                |  |

| Maximum Transmit Power <sup>4</sup>                  |       | +13        |                   | dBm  | $V_{DD} = 3.0 \text{ V}, T_A = 25^{\circ}\text{C}$                                                                                                                                             |  |

| Transmit Power Variation vs.<br>Temperature          |       | ±1         |                   | dB   | _40°C to +85°C                                                                                                                                                                                 |  |

| Transmit Power Variation vs. VDD                     |       | ±1         |                   | dB   | 2.3 V to 3.6 V at 915 MHz, T <sub>A</sub> = 25°C                                                                                                                                               |  |

| Transmit Power Flatness                              |       | ±1         |                   | dB   | 902 MHz to 928 MHz, 3 V, T <sub>A</sub> = 25°C                                                                                                                                                 |  |

| Programmable Step Size                               |       | 0.3125     |                   | dB   | −20 dBm to +13 dBm                                                                                                                                                                             |  |

| ADJACENT CHANNEL POWER (ACP)                         |       |            |                   |      |                                                                                                                                                                                                |  |

| 426 MHz, External Inductor VCO                       |       |            |                   |      | PFD = 9.84 MHz                                                                                                                                                                                 |  |

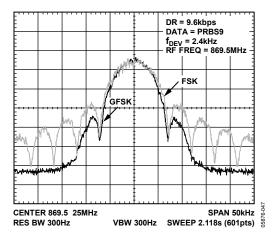

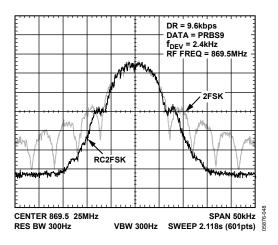

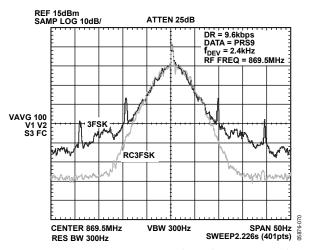

| 12.5 kHz Channel Spacing                             |       | -50        |                   | dBc  | Gaussian 2FSK modulation, measured in a ±4.25 kHz bandwidth at ±12.5 kHz offset, 2.4 kbps PN9 data, 1.2 kHz frequency deviation, compliant with ARIB STD-T67                                   |  |

| 25 kHz Channel Spacing                               |       | -50        |                   | dBc  | Gaussian 2FSK modulation, measured in a ±8 kHz bandwidth at ±25 kHz offset, 9.6 kbps PN9 data, 2.4 kHz frequency deviation, compliant with ARIB STD-T67                                        |  |

| 868 MHz, Internal Inductor VCO                       |       |            |                   |      | PFD = 19.68 MHz                                                                                                                                                                                |  |

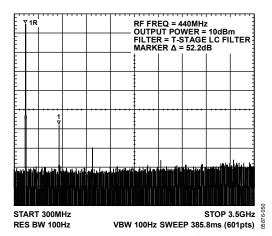

| 12.5 kHz Channel Spacing                             |       | -46        |                   | dBm  | Gaussian 2FSK modulation, 10 dBm output power, measured in a $\pm 6.25$ kHz bandwidth at $\pm 12.5$ kHz offset, 2.4 kbps PN9 data, 1.2 kHz frequency deviation, compliant with ETSI EN 300-220 |  |

| 25 kHz Channel Spacing                               |       | -43        |                   | dBm  | Gaussian 2FSK modulation, 10 dBm output power, measured in a $\pm 12.5$ kHz bandwidth at $\pm 25$ kHz offset, 9.6 kbps PN9 data, 2.4 kHz frequency deviation, compliant with ETSI EN 300-220   |  |

| 433 MHz, Internal Inductor VCO                       |       |            |                   |      | PFD = 19.68 MHz                                                                                                                                                                                |  |

| 12.5 kHz Channel Spacing                             |       | -50        |                   | dBm  | Gaussian 2FSK modulation, 10 dBm output power, measured in a $\pm 6.25$ kHz bandwidth at $\pm 12.5$ kHz offset, 2.4 kbps PN9 data, 1.2 kHz frequency deviation, compliant with ETSI EN 300-220 |  |

| 25 kHz Channel Spacing                               |       | <b>-47</b> |                   | dBm  | Gaussian 2FSK modulation, 10 dBm output power, measured in a $\pm 12.5$ kHz bandwidth at $\pm 25$ kHz offset, 9.6 kbps PN9 data, 2.4 kHz frequency deviation, compliant with ETSI EN 300-220   |  |

| OCCUPIED BANDWIDTH                                   |       |            |                   |      | 99.0% of total mean power; 12.5 kHz channel spacing (2.4 kbps PN9 data, 1.2 kHz frequency deviation); 25 kHz channel spacing (9.6 kbps PN9 data, 2.4 kHz frequency deviation)                  |  |

| 2FSK Gaussian Data Filtering                         |       |            |                   |      |                                                                                                                                                                                                |  |

| 12.5 kHz Channel Spacing                             |       | 3.9        |                   | kHz  |                                                                                                                                                                                                |  |

| 25 kHz Channel Spacing                               |       | 9.9        |                   | kHz  |                                                                                                                                                                                                |  |

| 2FSK Raised Cosine Data Filtering                    |       |            |                   |      |                                                                                                                                                                                                |  |

| 12.5 kHz Channel Spacing                             |       | 4.4        |                   | kHz  |                                                                                                                                                                                                |  |

| 25 kHz Channel Spacing                               |       | 10.2       |                   | kHz  |                                                                                                                                                                                                |  |

| 3FSK Raised Cosine Filtering                         |       |            |                   |      |                                                                                                                                                                                                |  |

| 12.5 kHz Channel Spacing                             |       | 3.9        |                   | kHz  |                                                                                                                                                                                                |  |

| 25 kHz Channel Spacing                               |       | 9.5        |                   | kHz  |                                                                                                                                                                                                |  |

| 4FSK Raised Cosine Filtering                         |       |            |                   |      | 19.2 kbps PN9 data, 1.2 kHz frequency deviation                                                                                                                                                |  |

| 25 kHz Channel Spacing                               |       | 13.2       |                   | kHz  |                                                                                                                                                                                                |  |

| Parameter                              | Min | Тур       | Max | Unit | Test Conditions/Comments                                       |

|----------------------------------------|-----|-----------|-----|------|----------------------------------------------------------------|

| SPURIOUS EMISSIONS                     |     |           |     |      |                                                                |

| Reference Spurs                        |     | -65       |     | dBc  | 100 kHz loop bandwidth                                         |

| HARMONICS <sup>5</sup>                 |     |           |     |      | 13 dBm output power, unfiltered conductive/filtered conductive |

| Second Harmonic                        |     | -35/-52   |     | dBc  |                                                                |

| Third Harmonic                         |     | -43/-60   |     | dBc  |                                                                |

| All Other Harmonics                    |     | -36/-65   |     | dBc  |                                                                |

| OPTIMUM PA LOAD IMPEDANCE <sup>6</sup> |     |           |     |      |                                                                |

| $f_{RF} = 915 \text{ MHz}$             |     | 39 + j61  |     | Ω    |                                                                |

| $f_{RF} = 868 \text{ MHz}$             |     | 48 + j54  |     | Ω    |                                                                |

| $f_{RF} = 450 \text{ MHz}$             |     | 98 + j65  |     | Ω    |                                                                |

| $f_{RF} = 426 \text{ MHz}$             |     | 100 + j65 |     | Ω    |                                                                |

| $f_{RF} = 315 \text{ MHz}$             |     | 129 + j63 |     | Ω    |                                                                |

| $f_{RF} = 175 \text{ MHz}$             |     | 173 + j49 |     | Ω    |                                                                |

<sup>&</sup>lt;sup>1</sup> Using Gaussian or raised cosine filtering. Choose the frequency deviation to ensure that the transmit occupied signal bandwidth is within the receiver IF filter bandwidth.

<sup>2</sup> Using raised cosine filtering with an alpha = 0.7. The inner frequency deviation = 1.78 kHz, and the POST\_DEMOD\_BW = 24.6 kHz.

<sup>3</sup> For the definition of frequency deviation, refer to the Register 2—Transmit Modulation Register section.

<sup>&</sup>lt;sup>4</sup> Measured as maximum unmodulated power.

<sup>&</sup>lt;sup>5</sup> Conductive filtered harmonic emissions measured on the EVAL-ADF7021DB models, which includes a T-stage harmonic filter (two inductors and one capacitor). <sup>6</sup> For matching details, refer to the LNA/PA Matching section.

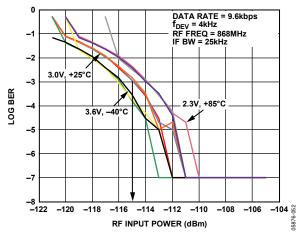

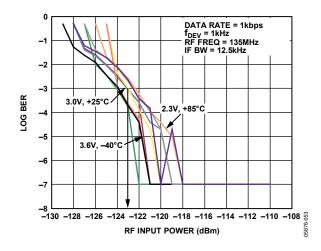

### **RECEIVER SPECIFICATIONS**

Table 3.

| Parameter                   | Min Typ | Max | Unit  | Test Conditions/Comments                                                                                      |

|-----------------------------|---------|-----|-------|---------------------------------------------------------------------------------------------------------------|

| SENSITIVITY                 |         |     |       | Bit error rate (BER) = $10^{-3}$ , low noise amplifier (LNA) and                                              |

|                             |         |     |       | power amplifier (PA) matched separately                                                                       |

| 2FSK                        | 120     |     | 10    | 6 4111 1:1 :::: 1 IE DW 42 E111                                                                               |

| Sensitivity at 0.1 kbps     | -130    |     | dBm   | f <sub>DEV</sub> = 1 kHz, high sensitivity mode, IF_BW = 12.5 kHz                                             |

| Sensitivity at 0.25 kbps    | -127    |     | dBm   | $f_{DEV} = 1 \text{ kHz}$ , high sensitivity mode, IF_BW = 12.5 kHz                                           |

| Sensitivity at 1 kbps       | -122    |     | dBm   | $f_{DEV} = 1 \text{ kHz}$ , high sensitivity mode, IF_BW = 12.5 kHz                                           |

| Sensitivity at 9.6 kbps     | -115    |     | dBm   | $f_{DEV} = 4 \text{ kHz}$ , high sensitivity mode, $IF_BW = 18.75 \text{ kHz}$                                |

| Sensitivity at 25 kbps      | -110    |     | dBm   | $f_{DEV} = 10 \text{ kHz}$ , high sensitivity mode, $IF\_BW = 25 \text{ kHz}$                                 |

| Gaussian 2FSK               |         |     |       |                                                                                                               |

| Sensitivity at 0.1 kbps     | -129    |     | dBm   | $f_{DEV} = 1 \text{ kHz}$ , high sensitivity mode, IF_BW = 12.5 kHz                                           |

| Sensitivity at 0.25 kbps    | -127    |     | dBm   | $f_{DEV} = 1 \text{ kHz}$ , high sensitivity mode, IF_BW = 12.5 kHz                                           |

| Sensitivity at 1 kbps       | -121    |     | dBm   | $f_{DEV} = 1 \text{ kHz}$ , high sensitivity mode, IF_BW = 12.5 kHz                                           |

| Sensitivity at 9.6 kbps     | -114    |     | dBm   | $f_{DEV} = 4 \text{ kHz}$ , high sensitivity mode, IF_BW = 18.75 kHz                                          |

| Sensitivity at 25 kbps      | -111    |     | dBm   | $f_{DEV} = 10 \text{ kHz}$ , high sensitivity mode, IF_BW = 25 kHz                                            |

| GMSK                        |         |     |       | ,                                                                                                             |

| Sensitivity at 9.6 kbps     | -113    |     | dBm   | $f_{DEV} = 2.4 \text{ kHz}$ , high sensitivity mode, IF_BW = 18.75 kHz                                        |

| Raised Cosine 2FSK          |         |     |       | , , , =                                                                                                       |

| Sensitivity at 0.25 kbps    | -127    |     | dBm   | f <sub>DEV</sub> = 1 kHz, high sensitivity mode, IF_BW = 12.5 kHz                                             |

| Sensitivity at 1 kbps       | -121    |     | dBm   | $f_{DEV} = 1 \text{ kHz}$ , high sensitivity mode, IF_BW = 12.5 kHz                                           |

| Sensitivity at 9.6 kbps     | -114    |     | dBm   | $f_{DEV} = 4 \text{ kHz}$ , high sensitivity mode, IF_BW = 18.75 kHz                                          |

| Sensitivity at 25 kbps      | -113    |     | dBm   | $f_{DEV} = 10 \text{ kHz}$ , high sensitivity mode, IF_BW = 25 kHz                                            |

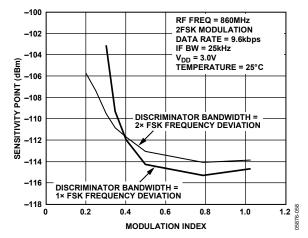

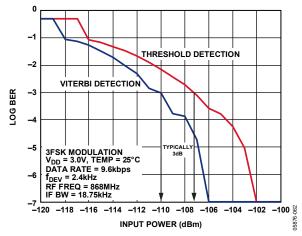

| 3FSK                        | 113     |     | abiii | To kitz, high sensitivity mode, it _bw = 25 kitz                                                              |

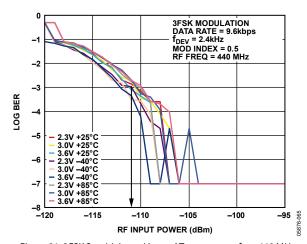

| Sensitivity at 9.6 kbps     | -110    |     | dBm   | $f_{DEV} = 2.4 \text{ kHz}$ , high sensitivity mode, IF_BW = 18.75 kHz,                                       |

| Sensitivity at 9.0 kbps     | -110    |     | ubili | Viterbi detection on                                                                                          |

| Raised Cosine 3FSK          |         |     |       |                                                                                                               |

| Sensitivity at 9.6 kbps     | -110    |     | dBm   | f <sub>DEV</sub> = 2.4 kHz, high sensitivity mode, IF_BW = 12.5 kHz,                                          |

| Schistivity at 5.0 kbps     | 110     |     | abiii | alpha = 0.5, Viterbi detection on                                                                             |

| Sensitivity at 19.6 kbps    | -106    |     | dBm   | $f_{DEV} = 4.8 \text{ kHz}$ , high sensitivity mode, IF_BW = 18.75 kHz,                                       |

| Sensitivity at 1910 hops    |         |     |       | alpha = 0.5, Viterbi detection on                                                                             |

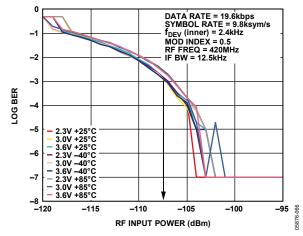

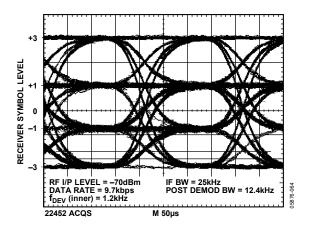

| 4FSK                        |         |     |       |                                                                                                               |

| Sensitivity at 9.6 kbps     | -112    |     | dBm   | f <sub>DEV</sub> (inner) = 1.2 kHz, high sensitivity mode, IF_BW = 12.5 kHz                                   |

| Sensitivity at 19.6 kbps    | -107    |     | dBm   | $f_{DEV}$ (inner) = 2.4 kHz, high sensitivity mode, IF_BW = 25 kHz                                            |

| Raised Cosine 4FSK          |         |     |       | 555 ()                                                                                                        |

| Sensitivity at 9.6 kbps     | -109    |     | dBm   | f <sub>DEV</sub> (inner) = 1.2 kHz, high sensitivity mode,                                                    |

| Schistavity at 3.0 RSp3     | 105     |     | abiii | IF_BW = 12.5 kHz, alpha = 0.5                                                                                 |

| Sensitivity at 19.2 kbps    | -103    |     | dBm   | f <sub>DEV</sub> (inner) = 1.2 kHz, high sensitivity mode,                                                    |

| 50.15ta.1tt, at 1512 115ps  |         |     |       | IF_BW = 18.75 kHz, alpha = 0.5                                                                                |

| Sensitivity at 32.8 kbps    | -100    |     | dBm   | f <sub>DEV</sub> (inner) = 1.8 kHz, high sensitivity mode, IF_BW = 25 kHz,                                    |

| ,                           |         |     |       | alpha = 0.7                                                                                                   |

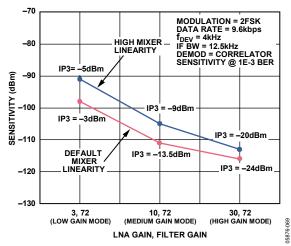

| INPUT IP3                   |         |     |       | Two-tone test, $f_{LO} = 860 \text{ MHz}$ , $F1 = f_{LO} + 100 \text{ kHz}$ , $F2 = f_{LO} - 800 \text{ kHz}$ |

| Low Gain Enhanced Linearity | -3      |     | dBm   | LNA_GAIN = 3, MIXER_LINEARITY = 1                                                                             |

| Mode                        |         |     |       | · -                                                                                                           |

| Medium Gain Mode            | -13.5   |     | dBm   | LNA_GAIN = 10, MIXER_LINEARITY = 0                                                                            |

| High Sensitivity Mode       | -24     |     | dBm   | LNA_GAIN = 30, MIXER_LINEARITY = 0                                                                            |

| Parameter                           | Min Typ        | Max         | Unit     | Test Conditions/Comments                                                                                                                                                                                                                                                                |

|-------------------------------------|----------------|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADJACENT CHANNEL REJECTION          |                |             |          |                                                                                                                                                                                                                                                                                         |

| 868 MHz                             |                |             |          | Wanted signal is 3 dB above the sensitivity point (BER = $10^{-3}$ ); unmodulated interferer is at the center of the adjacent channel; rejection measured as the difference between interferer level and wanted signal level in dB                                                      |

| 12.5 kHz Channel Spacing            | 25             |             | dB       | 12.5 kHz IF_BW                                                                                                                                                                                                                                                                          |

| 25 kHz Channel Spacing              | 27             |             | dB       | 25 kHz IF_BW                                                                                                                                                                                                                                                                            |

| 25 kHz Channel Spacing              | 39             |             | dB       | 18 kHz IF_BW                                                                                                                                                                                                                                                                            |

| 426 MHz, External Inductor VCO      |                |             |          | Wanted signal 3 dB above reference sensitivity point (BER = $10^{-2}$ ); modulated interferer (1 kHz sine, $\pm 2$ kHz deviation) at the center of the adjacent channel; rejection measured as the difference between interferer level and reference sensitivity level in dB            |

| 12.5 kHz Channel Spacing            | 25             |             | dB       | 12.5 kHz IF_BW                                                                                                                                                                                                                                                                          |

| 25 kHz Channel Spacing              | 30             |             | dB       | 25 kHz IF_BW                                                                                                                                                                                                                                                                            |

| 25 kHz Channel Spacing              | 41             |             | dB       | 18 kHz IF_BW, compliant with ARIB STD-T67                                                                                                                                                                                                                                               |

| CO-CHANNEL REJECTION                |                |             |          | Wanted signal (2FSK, 9.6 kbps, $\pm 4$ kHz deviation) is 10 dB above the sensitivity point (BER = $10^{-3}$ ), modulated interferer                                                                                                                                                     |

| 868 MHz                             | -3             |             | dB       |                                                                                                                                                                                                                                                                                         |

| IMAGE CHANNEL REJECTION             |                |             |          | Wanted signal (2FSK, 9.6 kbps, $\pm 4$ kHz deviation) is 10 dB above the sensitivity point (BER = $10^{-3}$ ); modulated interferer (2FSK, 9.6 kbps, $\pm 4$ kHz deviation) is placed at the image frequency of $f_{RF} - 200$ kHz; interferer level is increased until BER = $10^{-3}$ |

| 900 MHz                             | 23/39          |             | dB       | Uncalibrated/calibrated <sup>1</sup> , $V_{DD} = 3.0 \text{ V}$ , $T_A = 25^{\circ}\text{C}$                                                                                                                                                                                            |

| 450 MHz                             | 29/50          |             | dB       | Uncalibrated/calibrated $^{1}$ , $V_{DD} = 3.0 \text{ V}$ , $T_{A} = 25^{\circ}\text{C}$                                                                                                                                                                                                |

| 450 MHz, External Inductor VCO      | 38/53          |             | dB       | Uncalibrated/calibrated <sup>1</sup> , $V_{DD} = 3.0 \text{ V}$ , $T_A = 25^{\circ}\text{C}$                                                                                                                                                                                            |

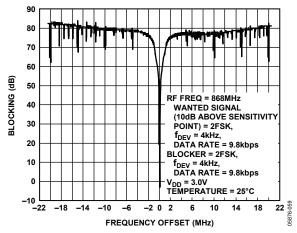

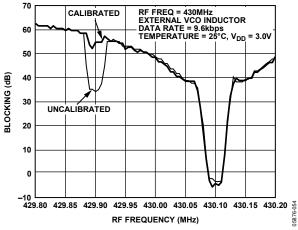

| BLOCKING                            |                |             |          | Wanted signal is 10 dB above the input sensitivity level;<br>CW interferer level is increased until BER = $10^{-3}$                                                                                                                                                                     |

| ±1 MHz                              | 69             |             | dB       |                                                                                                                                                                                                                                                                                         |

| ±2 MHz                              | 75             |             | dB       |                                                                                                                                                                                                                                                                                         |

| ±5 MHz                              | 78             |             | dB       |                                                                                                                                                                                                                                                                                         |

| ±10 MHz                             | 78.5           |             | dB       |                                                                                                                                                                                                                                                                                         |

| SATURATION<br>(MAXIMUM INPUT LEVEL) | 12             |             | dBm      | 2FSK mode, BER = 10 <sup>-3</sup>                                                                                                                                                                                                                                                       |

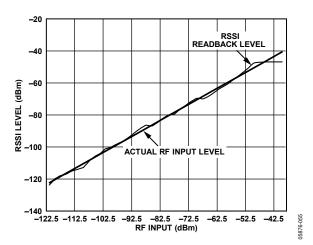

| RSSI                                |                |             |          |                                                                                                                                                                                                                                                                                         |

| Range at Input <sup>2</sup>         | −120 to<br>−47 |             | dBm      |                                                                                                                                                                                                                                                                                         |

| Linearity                           | ±2             |             | dB       | Input power range = -100 dBm to -47 dBm                                                                                                                                                                                                                                                 |

| Absolute Accuracy                   | ±3             |             | dB       | Input power range = $-100 \text{ dBm to } -47 \text{ dBm}$                                                                                                                                                                                                                              |

| Response Time                       | 300            |             | μs       | See the RSSI/AGC section                                                                                                                                                                                                                                                                |

| AFC                                 |                |             | <u> </u> |                                                                                                                                                                                                                                                                                         |

| Pull-In Range                       | 0.5            | 1.5 × IF_BW | kHz      | The range is programmable, R10_DB[24:31]                                                                                                                                                                                                                                                |

| Response Time                       | 48             |             | Bits     | 2 - 2 - 1 - 1 - 2 - 1 - 1 - 1 - 1 - 1 -                                                                                                                                                                                                                                                 |

| Accuracy                            | 0.5            |             | kHz      | Input power range = -100 dBm to +12 dBm                                                                                                                                                                                                                                                 |

| Rx SPURIOUS EMISSIONS <sup>3</sup>  |                |             |          | , , , , , , , , , , , , , , , , , , , ,                                                                                                                                                                                                                                                 |

| Internal Inductor VCO               | -91/-91        |             | dBm      | <1 GHz at antenna input, unfiltered conductive/filtered conductive                                                                                                                                                                                                                      |

|                                     | -52/-70        |             | dBm      | >1 GHz at antenna input, unfiltered conductive/filtered conductive                                                                                                                                                                                                                      |

| External Inductor VCO               | -62/-72        |             | dBm      | <1 GHz at antenna input, unfiltered conductive/filtered conductive                                                                                                                                                                                                                      |

|                                     | -64/-85        |             | dBm      | >1 GHz at antenna input, unfiltered conductive/filtered conductive                                                                                                                                                                                                                      |

| Parameter                  | Min | Тур        | Max | Unit | Test Conditions/Comments |

|----------------------------|-----|------------|-----|------|--------------------------|

| LNA INPUT IMPEDANCE        |     |            |     |      | RFIN to RFGND            |

| $f_{RF} = 915 \text{ MHz}$ |     | 24 – j60   |     | Ω    |                          |

| $f_{RF} = 868 \text{ MHz}$ |     | 26 – j63   |     | Ω    |                          |

| $f_{RF} = 450 \text{ MHz}$ |     | 63 – j129  |     | Ω    |                          |

| $f_{RF} = 426 \text{ MHz}$ |     | 68 – j134  |     | Ω    |                          |

| $f_{RF} = 315 \text{ MHz}$ |     | 96 – j160  |     | Ω    |                          |

| $f_{RF} = 175 \text{ MHz}$ |     | 178 – j190 |     | Ω    |                          |

#### **DIGITAL SPECIFICATIONS**

Table 4.

| Parameter                                         | Min                    | Тур                                          | Max                       | Unit | Test Conditions/Comments                                                                                                                                                  |

|---------------------------------------------------|------------------------|----------------------------------------------|---------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TIMING INFORMATION                                |                        |                                              |                           |      |                                                                                                                                                                           |

| Chip Enabled to Regulator Ready                   |                        | 10                                           |                           | μs   | $C_{REG} = 100 \text{ nF}$                                                                                                                                                |

| Chip Enabled to Tx Mode                           |                        |                                              |                           |      | 32-bit register write time = 50 μs                                                                                                                                        |

| TCXO Reference                                    |                        | 1                                            |                           | ms   |                                                                                                                                                                           |

| XTAL                                              |                        | 2                                            |                           | ms   |                                                                                                                                                                           |

| Chip Enabled to Rx Mode                           |                        |                                              |                           |      | 32-bit register write time = 50 μs, IF filter coarse calibration only                                                                                                     |

| TCXO Reference                                    |                        | 1.2                                          |                           | ms   |                                                                                                                                                                           |

| XTAL                                              |                        | 2.2                                          |                           | ms   |                                                                                                                                                                           |

| Tx to Rx Turnaround Time                          |                        | 300 $\mu$ s + (5 $\times$ t <sub>BIT</sub> ) |                           |      | Time to synchronized data out, includes AGC settling and CDR synchronization; see AGC Information and Timing section for more details; t <sub>BIT</sub> = data bit period |

| LOGIC INPUTS                                      |                        |                                              |                           |      |                                                                                                                                                                           |

| Input High Voltage, V <sub>INH</sub>              | $0.7 \times V_{DD}$    |                                              |                           | V    |                                                                                                                                                                           |

| Input Low Voltage, V <sub>INL</sub>               |                        |                                              | $0.2\times V_{\text{DD}}$ | V    |                                                                                                                                                                           |

| Input Current, I <sub>INH</sub> /I <sub>INL</sub> |                        |                                              | ±1                        | μΑ   |                                                                                                                                                                           |

| Input Capacitance, C <sub>IN</sub>                |                        |                                              | 10                        | рF   |                                                                                                                                                                           |

| Control Clock Input                               |                        |                                              | 50                        | MHz  |                                                                                                                                                                           |

| LOGIC OUTPUTS                                     |                        |                                              |                           |      |                                                                                                                                                                           |

| Output High Voltage, V <sub>OH</sub>              | DV <sub>DD</sub> - 0.4 |                                              |                           | ٧    | $I_{OH} = 500  \mu A$                                                                                                                                                     |

| Output Low Voltage, Vol                           |                        |                                              | 0.4                       | ٧    | $I_{OL} = 500  \mu A$                                                                                                                                                     |

| CLKOUT Rise/Fall                                  |                        |                                              | 5                         | ns   |                                                                                                                                                                           |

| CLKOUT Load                                       |                        |                                              | 10                        | рF   |                                                                                                                                                                           |

<sup>&</sup>lt;sup>1</sup> Calibration of the image rejection used an external RF source. <sup>2</sup> For received signal levels < –100 dBm, it is recommended to average the RSSI readback value over a number of samples to improve the RSSI accuracy at low input powers. <sup>3</sup> Filtered conductive receive spurious emissions measured on the EVAL-ADF7021DB evaluation boards, which includes a T-stage harmonic filter (two inductors and one capacitor).

#### **GENERAL SPECIFICATIONS**

Table 5.

| Parameter                                 | Min | Тур  | Max | Unit | Test Conditions/Comments                                  |

|-------------------------------------------|-----|------|-----|------|-----------------------------------------------------------|

| TEMPERATURE RANGE (T <sub>A</sub> )       | -40 |      | +85 | °C   |                                                           |

| POWER SUPPLIES                            |     |      |     |      |                                                           |

| Voltage Supply, V <sub>DD</sub>           | 2.3 |      | 3.6 | V    | All VDD pins must be tied together                        |

| TRANSMIT CURRENT CONSUMPTION <sup>1</sup> |     |      |     |      | $V_{DD} = 3.0 \text{ V}$ , PA is matched into $50 \Omega$ |

| 868 MHz                                   |     |      |     |      | VCO_BIAS = 8                                              |

| 0 dBm                                     |     | 20.2 |     | mA   |                                                           |

| 5 dBm                                     |     | 24.7 |     | mA   |                                                           |

| 10 dBm                                    |     | 32.3 |     | mA   |                                                           |

| 450 MHz, Internal Inductor VCO            |     |      |     |      | VCO_BIAS = 8                                              |

| 0 dBm                                     |     | 19.9 |     | mA   |                                                           |

| 5 dBm                                     |     | 23.2 |     | mA   |                                                           |

| 10 dBm                                    |     | 29.2 |     | mA   |                                                           |

| 426 MHz, External Inductor VCO            |     |      |     |      | VCO_BIAS = 2                                              |

| 0 dBm                                     |     | 13.5 |     | mA   |                                                           |

| 5 dBm                                     |     | 17   |     | mA   |                                                           |

| 10 dBm                                    |     | 23.3 |     | mA   |                                                           |

| RECEIVE CURRENT CONSUMPTION               |     |      |     |      | $V_{DD} = 3.0 \text{ V}$                                  |

| 868 MHz                                   |     |      |     |      | VCO_BIAS = 8                                              |

| Low Current Mode                          |     | 22.7 |     | mA   |                                                           |

| High Sensitivity Mode                     |     | 24.6 |     | mA   |                                                           |

| 433MHz, Internal Inductor VCO             |     |      |     |      | VCO_BIAS = 8                                              |

| Low Current Mode                          |     | 24.5 |     | mA   |                                                           |

| High Sensitivity Mode                     |     | 26.4 |     | mA   |                                                           |

| 426 MHz, External Inductor VCO            |     |      |     |      | VCO_BIAS = 2                                              |

| Low Current Mode                          |     | 17.5 |     | mA   |                                                           |

| High Sensitivity Mode                     |     | 19.5 |     | mA   |                                                           |

| POWER-DOWN CURRENT CONSUMPTION            |     |      |     |      |                                                           |

| Low Power Sleep Mode                      |     | 0.1  | 1   | μΑ   | CE low                                                    |

<sup>&</sup>lt;sup>1</sup> The transmit current consumption tests used the same combined PA and LNA matching network as that used on the EVAL-ADF7021DB evaluation boards. Improved PA efficiency is achieved by using a separate PA matching network.

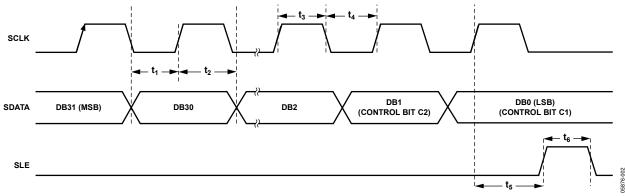

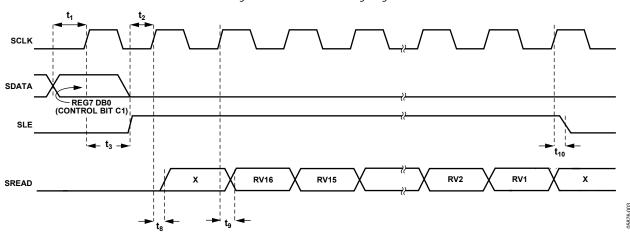

#### **TIMING CHARACTERISTICS**

$V_{DD} = 3~V \pm 10\%$ , DGND = AGND = 0 V,  $T_A = 25$ °C, unless otherwise noted. Guaranteed by design but not production tested.

Table 6.

| Parameter             | Limit at T <sub>MIN</sub> to T <sub>MAX</sub> | Unit | Test Conditions/Comments                      |

|-----------------------|-----------------------------------------------|------|-----------------------------------------------|

| t <sub>1</sub>        | >10                                           | ns   | SDATA to SCLK setup time                      |

| $t_2$                 | >10                                           | ns   | SDATA to SCLK hold time                       |

| t <sub>3</sub>        | >25                                           | ns   | SCLK high duration                            |

| $t_4$                 | >25                                           | ns   | SCLK low duration                             |

| <b>t</b> <sub>5</sub> | >10                                           | ns   | SCLK to SLE setup time                        |

| $t_6$                 | >20                                           | ns   | SLE pulse width                               |

| t <sub>8</sub>        | <25                                           | ns   | SCLK to SREAD data valid, readback            |

| t <sub>9</sub>        | <25                                           | ns   | SREAD hold time after SCLK, readback          |

| t <sub>10</sub>       | >10                                           | ns   | SCLK to SLE disable time, readback            |

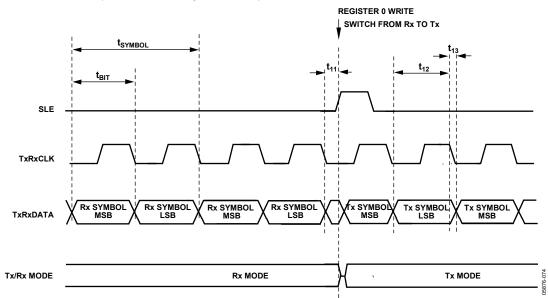

| t <sub>11</sub>       | $5 < t_{11} < (1/4 \times t_{BIT})$           | ns   | TxRxCLK negative edge to SLE                  |

| t <sub>12</sub>       | >5                                            | ns   | TxRxDATA to TxRxCLK setup time (Tx mode)      |

| t <sub>13</sub>       | >5                                            | ns   | TxRxCLK to TxRxDATA hold time (Tx mode)       |

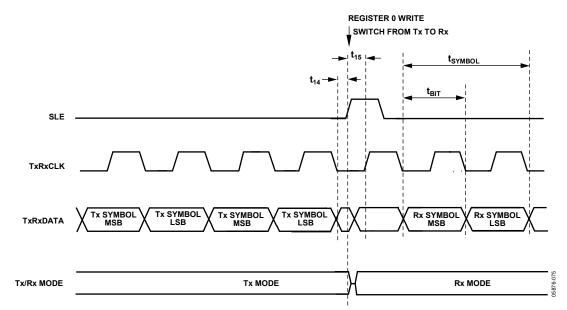

| t <sub>14</sub>       | $>$ 1/4 $\times$ t <sub>BIT</sub>             | μs   | TxRxCLK negative edge to SLE                  |

| t <sub>15</sub>       | $>$ 1/4 $\times$ t <sub>BIT</sub>             | μs   | SLE positive edge to positive edge of TxRxCLK |

Rev. D | Page 11 of 62

#### **Timing Diagrams**

#### **Serial Interface**

Figure 2. Serial Interface Timing Diagram

Figure 3. Serial Interface Readback Timing Diagram

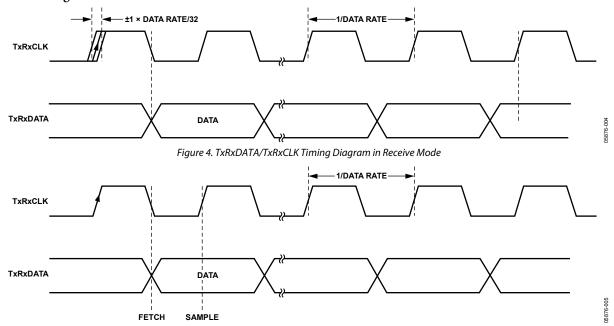

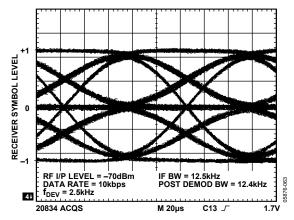

#### 2FSK/3FSK Timing

Figure 5. TxRxDATA/TxRxCLK Timing Diagram in Transmit Mode

#### **4FSK Timing**

In 4FSK receive mode, MSB/LSB synchronization is guaranteed by SWD in the receive bit stream.

Figure 6. Receive-to-Transmit Timing Diagram in 4FSK Mode

Figure 7. Transmit-to-Receive Timing Diagram in 4FSK Mode

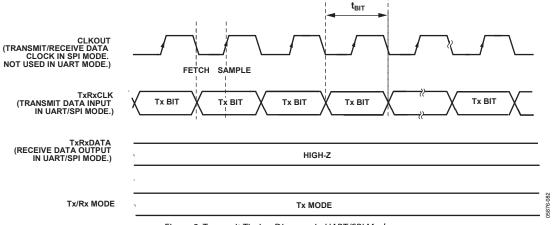

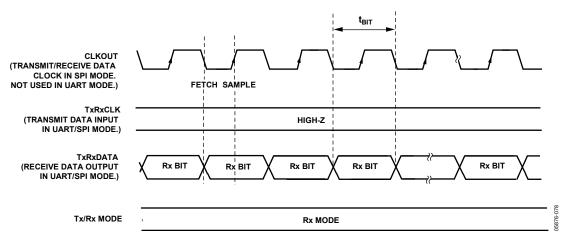

#### **UART/SPI Mode**

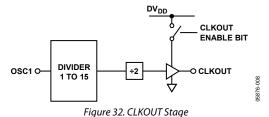

UART mode is enabled by setting R0\_DB28 to 1. SPI mode is enabled by setting R0\_DB28 to 1 and setting R15\_DB[17:19] to 0x7. The transmit/receive data clock is available on the CLKOUT pin.

Figure 8. Transmit Timing Diagram in UART/SPI Mode

Figure 9. Receive Timing Diagram in UART/SPI Mode

## **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C, unless otherwise noted.

Table 7.

| Parameter                           | Rating                                      |  |  |  |

|-------------------------------------|---------------------------------------------|--|--|--|

| V <sub>DD</sub> to GND <sup>1</sup> | −0.3 V to +5 V                              |  |  |  |

| Analog I/O Voltage to GND           | $-0.3 \text{ V to AV}_{DD} + 0.3 \text{ V}$ |  |  |  |

| Digital I/O Voltage to GND          | $-0.3 \text{ V to DV}_{DD} + 0.3 \text{ V}$ |  |  |  |

| Operating Temperature Range         |                                             |  |  |  |

| Industrial (B Version)              | -40°C to +85°C                              |  |  |  |

| Storage Temperature Range           | −65°C to +125°C                             |  |  |  |

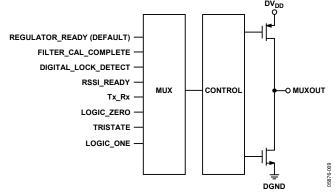

| Maximum Junction Temperature        | 150°C                                       |  |  |  |