Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 8-Channel CMOS Logic to High Voltage Level Translator

Data Sheet ADG3123

#### **FEATURES**

2.3 V to 5.5 V input voltage range

Output voltage levels (V<sub>DDA</sub> and V<sub>DDB</sub> to V<sub>SS</sub> ≤ 35 V)

Low output voltage levels: down to −24.2 V

High output voltage levels: up to +35 V

Rise/fall time: 12 ns/19.5 ns typical

Propagation delay: 80 ns typical

Operating frequency: 100 kHz typical

Ultralow quiescent current: 65 µA typical

20-lead, Pb-free, TSSOP package

#### **APPLICATIONS**

Low voltage to high voltage translation TFT-LCD panels Piezoelectric motor drivers

#### **GENERAL DESCRIPTION**

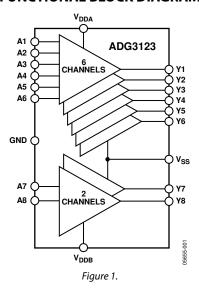

The ADG3123 is an 8-channel, noninverting CMOS to high voltage level translator. Fabricated on an enhanced LC<sup>2</sup>MOS process, the device is capable of operating at high supply voltages while maintaining ultralow power consumption.

The internal architecture of the device ensures compatibility with logic circuits running from supply voltages within the 2.3 V to 5.5 V range. The voltages applied to Pin  $V_{\rm DDA}$ , Pin  $V_{\rm DDB}$ , and Pin  $V_{\rm SS}$  set the logic levels available at the outputs on the Y side of the device. Pin  $V_{\rm DDA}$  and Pin  $V_{\rm DDB}$  set the high output level for Pin Y1 to Pin Y6 and for Pin Y7 to Pin Y8, respectively. The  $V_{\rm SS}$  pin sets the low output level for all channels. The ADG3123 can provide output voltages levels down to  $-24.2~\rm V$  for a low input level and up to  $+35~\rm V$  for a high input logic level. For proper operation,  $V_{\rm DDB}$  must always be greater than or equal to  $V_{\rm DDA}$  and the voltage between the Pin  $V_{\rm DDB}$  and Pin  $V_{\rm SS}$  should not exceed 35 V.

The low output impedance of the channels guarantees fast rise and fall times even for significant capacitive loads. This feature, combined with low propagation delay and low power consumption, makes the ADG3123 an ideal driver for TFT-LCD panel applications.

#### **FUNCTIONAL BLOCK DIAGRAM**

The ADG3123 is guaranteed to operate over the  $-40^{\circ}$ C to  $+85^{\circ}$ C temperature range and is available in a compact, 20-lead TSSOP, Pb-free package.

#### **PRODUCT HIGHLIGHTS**

- 1. Compatible with a wide range of CMOS logic levels.

- 2. High output voltage levels.

- 3. Fast rise and fall times coupled with low propagation delay.

- 4. Ultralow power consumption.

- 5. Compact, 20-lead TSSOP, RoHS-compliant package.

# **ADG3123\* PRODUCT PAGE QUICK LINKS**

Last Content Update: 02/23/2017

# COMPARABLE PARTS 🖵

View a parametric search of comparable parts.

# **EVALUATION KITS**

Evaluation Board for 24-Lead TSSOP Devices in the Switches and Multiplexers Portfolio

# **DOCUMENTATION**

#### **Data Sheet**

ADG3123: 8-Channel CMOS Logic to High Voltage Level Translator Data Sheet

#### **User Guides**

UG-1036: Evaluation Board for 24-Lead TSSOP Devices in the Switches and Multiplexers Portfolio

# REFERENCE MATERIALS -

#### **Product Selection Guide**

• Switches and Multiplexers Product Selection Guide

# **DESIGN RESOURCES**

- ADG3123 Material Declaration

- PCN-PDN Information

- · Quality And Reliability

- Symbols and Footprints

## **DISCUSSIONS**

View all ADG3123 EngineerZone Discussions.

## SAMPLE AND BUY 🖳

Visit the product page to see pricing options.

# TECHNICAL SUPPORT

Submit a technical question or find your regional support number.

## DOCUMENT FEEDBACK 🖳

Submit feedback for this data sheet.

# **TABLE OF CONTENTS**

| Applications1                                                 |

|---------------------------------------------------------------|

| Functional Block Diagram1                                     |

| General Description1                                          |

| Product Highlights1                                           |

| Revision History2                                             |

| Specifications3                                               |

| Absolute Maximum Ratings4                                     |

| ESD Caution                                                   |

| Pin Configuration and Function Descriptions5                  |

|                                                               |

| REVISION HISTORY                                              |

| 1/13—Rev. A to Rev. B                                         |

| Changes to Features Section and General Description Section 1 |

| Changes to Ordering Guide12                                   |

| 5/06—Rev. 0 to Rev. A                                         |

| Changes to Features Section, General Description Section, and |

| Product Highlights Section1                                   |

| Changes to Specifications                                     |

| Changes to Figure 4 through Figure 96                         |

| Changes to Figure 14 and Figure 157                           |

| Changes to Theory of Operations Section and Power Supplies    |

|                                                               |

Section.....

9/05—Revision 0: Initial Version

| Typical Performance Characteristics | 6  |

|-------------------------------------|----|

| Terminology                         | 9  |

| Theory of Operation                 | 10 |

| Input Driving Requirements          | 10 |

| Output Load Requirements            | 10 |

| Power Supplies                      | 10 |

| Applications Information            | 11 |

| Outline Dimensions                  | 12 |

| Ordering Guide                      | 12 |

# **SPECIFICATIONS**

$V_{DDA} = V_{DDB} = 27 \text{ V}, V_{SS} = -7 \text{ V}, GND = 0 \text{ V}, unless otherwise noted.}$  Temperature range for B version is  $-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ .

Table 1.

| Parameter                              | Symbol           | Min         | Typ <sup>1</sup> | Max          | Unit | Test Conditions/Comments                                                                                                                                         |

|----------------------------------------|------------------|-------------|------------------|--------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIGITAL INPUTS (Pin A1 to Pin A8)      |                  |             |                  |              |      | $V_{AX} = 0 \text{ V to } 5.5 \text{ V}$                                                                                                                         |

| Input High Voltage                     | V <sub>IH</sub>  | 1.7         |                  |              | V    |                                                                                                                                                                  |

| Input Low Voltage                      | $V_{IL}$         |             |                  | 8.0          | V    |                                                                                                                                                                  |

| Leakage Current                        | I <sub>IL</sub>  |             | ±0.03            | ±1           | μΑ   |                                                                                                                                                                  |

| Capacitance <sup>2</sup>               | Cı               |             | 1                |              | рF   |                                                                                                                                                                  |

| ANALOG INPUTS (Pin V <sub>DDA</sub> )  |                  |             |                  |              |      |                                                                                                                                                                  |

| Input Voltage Range                    | $V_{DDA}$        | 0           |                  | $V_{DDB}$    | V    |                                                                                                                                                                  |

| DIGITAL OUTPUTS (Pin Y1 to Pin Y8)     |                  |             |                  |              |      | $V_{DDA} = V_{DDB} = 25 \text{ V to } 30 \text{ V, } V_{SS} = -5 \text{ V to } -7 \text{ V,}$ $V_{DDA} \text{ and } V_{DDB} \text{ to } V_{SS} \le 35 \text{ V}$ |

| Output High Voltage (Pin Y1 to Pin Y6) | $V_{OH}$         | $V_{DDA}-1$ |                  |              | V    | $I_{OH} = -10 \text{ mA}$                                                                                                                                        |

| Output High Voltage (Pin Y7 to Pin Y8) | V <sub>OH</sub>  | $V_{DDB}-1$ |                  |              | V    | $I_{OH} = -10 \text{ mA}$                                                                                                                                        |

| Output Low Voltage                     | $V_{OL}$         |             |                  | $V_{SS} + 1$ | V    | $I_{OL} = +10 \text{ mA}$                                                                                                                                        |

| Output Impedance                       | R <sub>0</sub>   |             | 30               |              | Ω    | $V_{DDA} = V_{DDB} = +27 \text{ V}, V_{SS} = -7 \text{ V}$                                                                                                       |

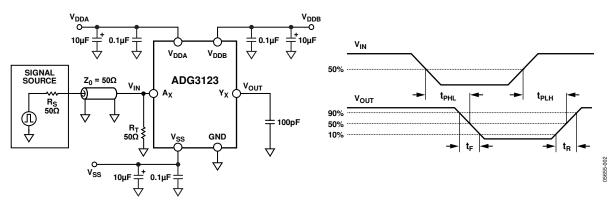

| SWITCHING CHARACTERISTICS <sup>2</sup> |                  |             |                  |              |      | See Figure 2                                                                                                                                                     |

| Propagation Delay                      |                  |             |                  |              |      |                                                                                                                                                                  |

| Low to High Transition                 | t <sub>PLH</sub> |             | 76               | 125          | ns   |                                                                                                                                                                  |

| High to Low Transition                 | t <sub>PHL</sub> |             | 80               | 125          | ns   |                                                                                                                                                                  |

| Rise Time                              | $t_{R}$          |             | 12               | 20           | ns   |                                                                                                                                                                  |

| Fall Time                              | t <sub>F</sub>   |             | 19.5             | 32           | ns   |                                                                                                                                                                  |

| Maximum Operating Frequency            | F <sub>0</sub>   | 50          | 100              |              | kHz  | 100 pF load, all channels, see Figure 2                                                                                                                          |

| POWER REQUIREMENTS                     |                  |             |                  |              |      |                                                                                                                                                                  |

| Quiescent Power Supply Current         | I <sub>DDA</sub> |             | 0.03             | 1            | μΑ   | $V_{AX} = 0 \text{ V or } 5.5 \text{ V, no load, } V_{DDA} \leq V_{DDB}$                                                                                         |

|                                        | I <sub>DDB</sub> |             | 65               | 150          | μΑ   |                                                                                                                                                                  |

|                                        | Iss              |             | 0.03             | 1            | μΑ   |                                                                                                                                                                  |

| Power Supply Voltages                  |                  |             |                  |              |      |                                                                                                                                                                  |

| $V_{DDB}$ to $V_{SS}$                  |                  | 10.8        |                  | 35           | V    |                                                                                                                                                                  |

| V <sub>DDB</sub> to GND                | $V_{DDB}$        | 10.8        |                  | 35           | V    | $V_{DDB}$ to $V_{SS} \le 35 \text{ V}$                                                                                                                           |

| V <sub>ss</sub> to GND                 | Vss              | -24.2       |                  | 0            | V    | $V_{DDB}$ to $V_{SS} \le 35 \text{ V}$                                                                                                                           |

<sup>&</sup>lt;sup>1</sup> Typical values are specified at 25°C. <sup>2</sup> Guaranteed by design; not subject to production testing.

Figure 2. Switching Characteristics Test Circuit

# **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C, unless otherwise noted.

Table 2.

| 1 4014 21                                       |  |  |  |  |  |  |

|-------------------------------------------------|--|--|--|--|--|--|

| Rating                                          |  |  |  |  |  |  |

| 44 V                                            |  |  |  |  |  |  |

| −0.3 V to +32 V                                 |  |  |  |  |  |  |

| $-0.3\mathrm{V}$ to $\mathrm{V}_{\mathrm{DDB}}$ |  |  |  |  |  |  |

| +0.3 V to −32 V                                 |  |  |  |  |  |  |

| $V_{SS} - 0.3 V$ to $V_{DDB} + 0.3 V$ or        |  |  |  |  |  |  |

| 20 mA, whichever occurs first                   |  |  |  |  |  |  |

|                                                 |  |  |  |  |  |  |

| 15 mA at 25°C                                   |  |  |  |  |  |  |

| 8 mA at 85°C                                    |  |  |  |  |  |  |

| 150 mA at 25°C                                  |  |  |  |  |  |  |

| 80 mA at 85°C                                   |  |  |  |  |  |  |

|                                                 |  |  |  |  |  |  |

| –40°C to +85°C                                  |  |  |  |  |  |  |

| −65°C to +125°C                                 |  |  |  |  |  |  |

| 150°C                                           |  |  |  |  |  |  |

| 78°C/W <sup>3</sup>                             |  |  |  |  |  |  |

|                                                 |  |  |  |  |  |  |

| 260 (+0/-5)°C                                   |  |  |  |  |  |  |

| 10 seconds to 40 seconds                        |  |  |  |  |  |  |

|                                                 |  |  |  |  |  |  |

<sup>&</sup>lt;sup>1</sup> Overvoltage at Pin A1 to Pin A8 is clamped by internal diodes. Limit the current to the maximum ratings given.

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Only one absolute maximum rating can be applied at any one time.

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

<sup>&</sup>lt;sup>2</sup> Pulsed at 100 kHz; 10% duty cycle maximum with the load shown in Figure 2.

<sup>&</sup>lt;sup>3</sup> Guaranteed when the device is soldered on a 4-layer board.

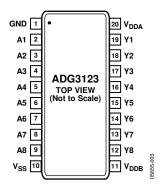

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 3. Pin Configuration

**Table 3. Pin Function Descriptions**

| 1 W 1 W 1 W 1 W 1 W 1 W 1 W 1 W 1 W 1 W |                 |                                                                                                                             |  |  |  |

|-----------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin No.                                 | Mnemonic        | Description                                                                                                                 |  |  |  |

| 1                                       | GND             | Ground Reference (0 V).                                                                                                     |  |  |  |

| 2 to 9                                  | A1 to A8        | Level Translator CMOS Inputs.                                                                                               |  |  |  |

| 10                                      | V <sub>SS</sub> | Most Negative Power Supply. Use the V <sub>SS</sub> pin to generate the output low level for Output Y1 to Output Y8.        |  |  |  |

| 11                                      | $V_{DDB}$       | Positive Power Supply. Use the V <sub>DDB</sub> pin to generate the output high level for Output Y7 and Output Y8.          |  |  |  |

| 12 to 19                                | Y8 to Y1        | Level Translator High Voltage Outputs.                                                                                      |  |  |  |

| 20                                      | $V_{DDA}$       | Analog Input. Use the $V_{DDA}$ pin to generate the output high level for Output Y1 to Output Y6 ( $V_{DDA} \le V_{DDB}$ ). |  |  |  |

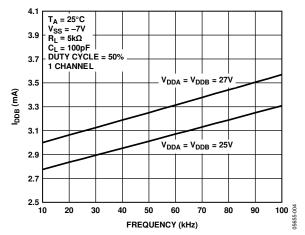

# TYPICAL PERFORMANCE CHARACTERISTICS

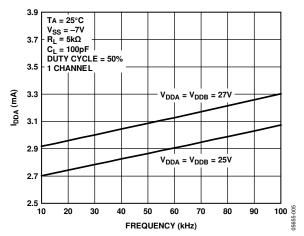

Figure 4. Supply Current (IDDB) vs. Frequency

Figure 5. Supply Current (IDDA) vs. Frequency

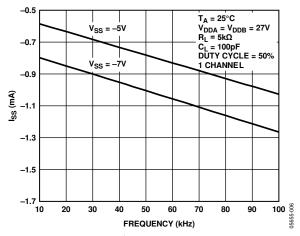

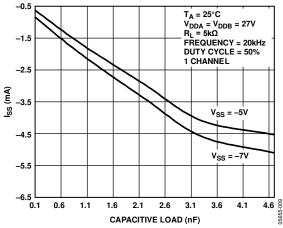

Figure 6. Supply Current (Iss) vs. Frequency

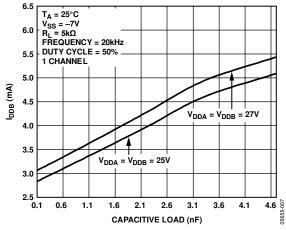

Figure 7. Supply Current (IDDB) vs. Capacitive Load

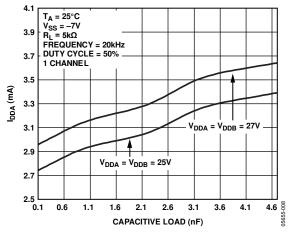

Figure 8. Supply Current (IDDA) vs. Capacitive Load

Figure 9. Supply Current (Iss) vs. Capacitive Load

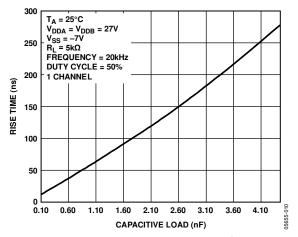

Figure 10. Rise Time vs. Capacitive Load

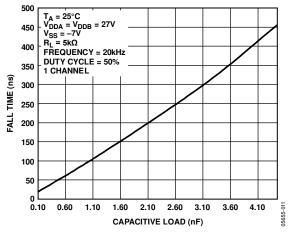

Figure 11. Fall Time vs. Capacitive Load

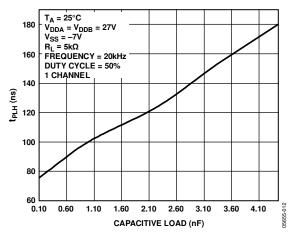

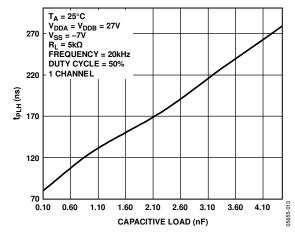

Figure 12. Propagation Delay (tplh) vs. Capacitive Load

Figure 13. Propagation Delay ( $t_{PHL}$ ) vs. Capacitive Load

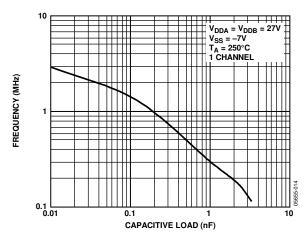

Figure 14. Maximum Operating Frequency vs. Capacitive Load (One Channel)

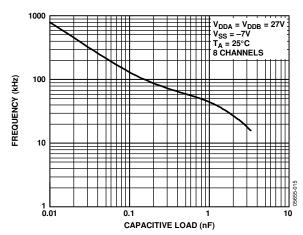

Figure 15. Maximum Operating Frequency vs. Capacitive Load (Eight Channels)

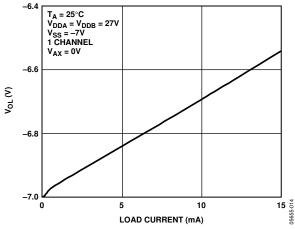

Figure 16. Output Voltage ( $V_{OL}$ ) vs. Load Current

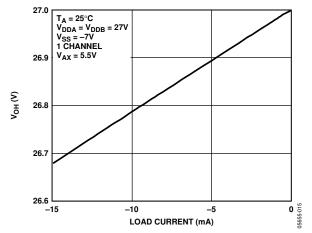

Figure 17. Output Voltage (V<sub>OH</sub>) vs. Load Current

# **TERMINOLOGY**

$\mathbf{V}_{\mathrm{IH}}$

Logic input high voltage at Pin A1 to Pin A8.

$V_{II}$

Logic input low voltage at Pin A1 to Pin A8.

III.

Leakage current at Pin A1 to Pin A8.

Cı

Capacitance measured at Pin A1 to Pin A8.

$V_{\text{OH}}$

Logic output high voltage at Pin Y1 to Pin Y8.

$\mathbf{V}_{\text{OL}}$

Logic output low voltage at Pin Y1 to Pin Y8.

Ro

Output impedance.

$t_{PLH}$

Propagation delay through the part measured between the input signal applied to any one channel and its corresponding output for a low-to-high transition (see Figure 2).

$t_{PHL}$

Propagation delay through the part measured between the input signal applied to any one channel and its corresponding output for a high-to-low transition (see Figure 2).

$t_{\text{R}}$

Rise time of the output signal at Pin Y1 to Pin Y8 (see Figure 2).

tf

Fall time of the output signal at the Pin Y1 to Pin Y8 (see Figure 2).

Fo

Frequency of the signal applied to the A1 to A8 input pins.

$V_{DD4}$

Input voltage used to generate the high logic levels for Y1 to Y6 outputs.

$\mathbf{V}_{\text{DDB}}$

Positive power supply voltage. Also used to generate the high logic levels for Y7 to Y8 outputs.

Vss

Negative power supply voltage. It is used to generate the low logic level for Y1 to Y8 outputs.

**GND**

Ground (0 V) reference.

$I_{DDA}$

Supply current at the  $V_{\rm DDA}$  pin.

$I_{\text{DDB}}$

Supply current at the  $V_{\text{DDB}}$  pin.

Iss

Supply current at the V<sub>SS</sub> pin.

## THEORY OF OPERATION

The ADG3123 is an 8-channel, noninverting CMOS to high voltage level translator. Fabricated on an enhanced LC<sup>2</sup>MOS process, the device is capable of operating at high supply voltages while maintaining ultralow power consumption.

The device requires a dual-supply voltage,  $V_{\rm DDB}$  and  $V_{\rm SS}$ , which sets the low logic levels for all outputs and the high logic levels for the Y7 and Y8 outputs. The  $V_{\rm DDA}$  pin acts as an analog input. The voltage applied to the  $V_{\rm DDA}$  pin sets the output high logic level for the Y1 to Y6 outputs.

The device translates the CMOS logic levels applied to the A1 to A8 inputs into high voltage bipolar levels available on the Y side of the device at Pin Y1 to Pin Y8.

To ensure proper operation,  $V_{\rm DDB}$  must always be greater than or equal to  $V_{\rm DDA}$  and the voltage between the Pin  $V_{\rm DDB}$  and Pin  $V_{SS}$  should not exceed 35 V.

#### INPUT DRIVING REQUIREMENTS

The ADG3123 design ensures low input capacitance and leakage current thereby reducing the loading of the circuit that drives the input pins (Pin A1 to Pin A8) to a minimum. Its input threshold levels are compliant with JEDEC standards for drivers operated from supply voltages between 2.3 V and 5.5 V. It is recommended that the inputs of any unused channel be tied to a stable logic level (low or high).

#### **OUTPUT LOAD REQUIREMENTS**

The low output impedance of the ADG3123 allows each channel to drive both resistive and capacitive loads. The maximum load current is limited by the current carrying capability of any given channel. If more channels are used, the maximum load current per channel is reduced accordingly. Note that the sum of the load currents on all channels should never exceed the absolute maximum ratings specifications.

The average load current on each channel, I<sub>CHANNEL</sub>, can be determined using the formulas shown in the Capacitive Loads and the Resistive Loads sections.

#### **Capacitive Loads**

$$I_{CHANNEL}(A) = F_O \times C_L \times (V_{DDX} + |V_{SS}|)$$

where:

$F_O$  is the frequency of the signal applied to the channel in Hz.  $C_L$  is the load capacitance in farads.

$V_{SS}$  is the voltage applied to the  $V_{SS}$  pin.

$V_{DDX}$  is  $V_{DDA}$  for Y1 to Y6 outputs, and  $V_{DDB}$  for Y7 to Y8 outputs.

#### **Resistive Loads**

$$I_{CHANNEL}(A) = \frac{D \times V_{DDX} + (1 - D) \times |V_{SS}|}{R_{I}}$$

where:

D is the duty cycle of the input signal. D is defined as the ratio between the high state duration of the signal and its period.  $R_L$  is the load resistor in  $\Omega$ .

$V_{SS}$  is the voltage applied to the  $V_{SS}$  pin.

$V_{DDX}$  is  $V_{DDA}$  for Y1 to Y6 outputs, and  $V_{DDB}$  for Y7 to Y8 outputs.

#### **POWER SUPPLIES**

The ADG3123 operates from a dual-supply voltage. As good design practice for all CMOS devices dictates, power up the ADG3123 first ( $V_{\rm DDB}$  and  $V_{\rm SS}$ ) before applying the signals to its inputs (A1 to A8 and  $V_{\rm DDA}$ ). To ensure correct operation of the ADG3123, the voltage applied to the  $V_{\rm DDB}$  pin must always be greater than or equal to  $V_{\rm DDA}$  and the voltage between the Pin  $V_{\rm DDB}$  and Pin  $V_{\rm SS}$  should not exceed 35 V.

To ensure optimum performance, use decoupling capacitors on all power supply pins. Furthermore, good engineering and layout practice suggests placing these capacitors as close as possible to the package supply pins.

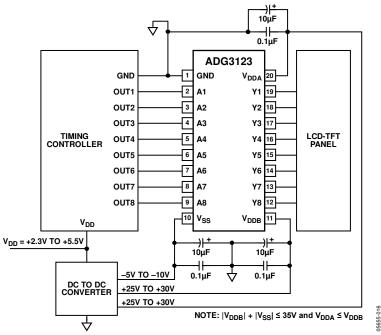

## APPLICATIONS INFORMATION

The high voltage operation coupled with high current driving capability and the wide range of CMOS levels accepted by the ADG3123, make the device ideal for LCD-TFT panel applications. In this type of application, the controllers that generate the timing signals required to control the pixel scanning process inside the panel are usually low voltage CMOS devices.

Most LCD-TFT panels operate at high supply voltages; therefore, the timing signals generated by the controller require level translation to drive the panel. Figure 18 shows a typical application circuit where the ADG3123 translates eight timing signals provided by the timing controller into high voltage logic levels required to drive the panel.

Figure 18. Typical Application Circuit

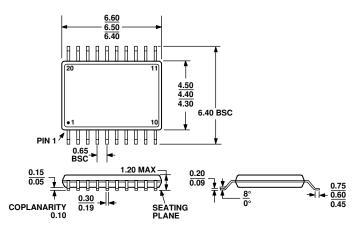

# **OUTLINE DIMENSIONS**

COMPLIANT TO JEDEC STANDARDS MO-153-AC

Figure 19. 20-Lead Thin Shrink Small Outline Package [TSSOP] (RU-20) Dimensions shown in millimeters

## **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                               | Package Option |

|--------------------|-------------------|---------------------------------------------------|----------------|

| ADG3123BRUZ        | −40°C to +85°C    | 20-Lead Thin Shrink Small Outline Package [TSSOP] | RU-20          |

| ADG3123BRUZ-REEL7  | −40°C to +85°C    | 20-Lead Thin Shrink Small Outline Package [TSSOP] | RU-20          |

$<sup>^{1}</sup>$  Z = RoHS Compliant Part.