# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Dual, 35 dB Range, 1 dB Step Size DGA

### **Data Sheet**

# ADL5205

#### FEATURES

- Dual, independent, digitally controlled gain amplifier (DGA)

- –9 dB to +26 dB gain range

- 1 dB step size, ±0.2 dB accuracy at 200 MHz

- 100  $\Omega$  differential input resistance

- $10\,\Omega$  differential output resistance

- 1.2 dB change in noise figure for first 12 dB of gain reduction

- Output third-order intercept (OIP3): 48.5 dBm at 200 MHz, 5 V, high performance mode

- –3 dB bandwidth: 1700 MHz typical in high performance mode

- **Multiple control interface options**

- Parallel 6-bit control interface with latch

- Serial peripheral interface (SPI) with fast attack Gain step up/down interface

- Wide input dynamic range

- Low power mode

- Power-down control

- Single 3.3 V or 5 V supply operation

- 40-lead, 6 mm × 6 mm LFCSP package

#### APPLICATIONS

Differential analog-to-digital converter (ADC) drivers High intermediate frequency (IF) sampling receivers High output power IF amplification Instrumentation

#### **GENERAL DESCRIPTION**

The ADL5205 is a digitally controlled, wide bandwidth, variable gain dual amplifier (DGA) that provides precise gain control, high output third-order intercept (OIP3) and a near constant noise figure for the first 12 dB of attenuation. The excellent OIP3 performance of 48.5 dBm (at 200 MHz, 5 V, high performance mode, and maximum gain) makes the ADL5205 an excellent gain control device for a variety of receiver applications.

For wide input dynamic range applications, the ADL5205 provides a broad 35 dB gain range with a 1 dB step size. The gain is adjustable through multiple gain control and interface options: parallel, SPI, or gain step up/down control.

The two channels of the ADL5205 can be powered up independently by applying the appropriate logic level to the PWUPA and PWUPB pins. The quiescent current of the ADL5205 is typically 175 mA for high performance mode and 135 mA for

Rev. 0 Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

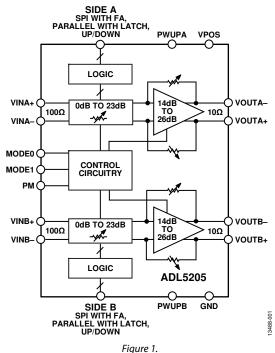

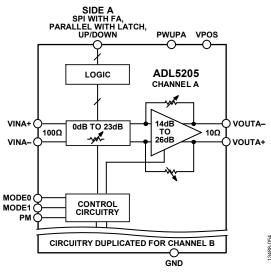

#### FUNCTIONAL BLOCK DIAGRAM

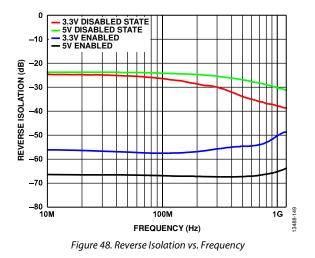

low power mode. When disabled, the ADL5205 consumes only 14 mA and offers excellent input to output isolation. The gain setting is preserved when the device is disabled.

Fabricated on the Analog Devices, Inc., high speed, silicon germanium (SiGe) complementary BiCMOS process, the ADL5205 provides precise gain adjustment capabilities with good distortion performance. The ADL5205 amplifier comes in a compact, thermally enhanced, 6 mm  $\times$  6 mm, 40-lead LFCSP package and operates over the temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C.

Note that throughout this data sheet, multifunction pins, such as  $\overline{CSA}/A3$ , are referred to by the entire pin name or by a single function of the pin, for example,  $\overline{CSA}$ , when only that function is relevant.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2016 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

# ADL5205\* PRODUCT PAGE QUICK LINKS

Last Content Update: 02/23/2017

### COMPARABLE PARTS

View a parametric search of comparable parts.

### EVALUATION KITS

ADL5205 Evaluation Board

### **DOCUMENTATION**

#### **Application Notes**

AN-1363: Meeting Biasing Requirements of Externally Biased RF/Microwave Amplifiers with Active Bias Controllers

#### **Data Sheet**

ADL5205: Dual, 35 dB Range, 1 dB Step Size DGA Data Sheet

### TOOLS AND SIMULATIONS $\square$

ADL5205 S-Parameters

### DESIGN RESOURCES

- ADL5205 Material Declaration

- PCN-PDN Information

- Quality And Reliability

- Symbols and Footprints

### DISCUSSIONS

View all ADL5205 EngineerZone Discussions.

### SAMPLE AND BUY

Visit the product page to see pricing options.

### **TECHNICAL SUPPORT**

Submit a technical question or find your regional support number.

### DOCUMENT FEEDBACK

Submit feedback for this data sheet.

# **TABLE OF CONTENTS**

| Features                                     |

|----------------------------------------------|

| Applications1                                |

| Functional Block Diagram 1                   |

| General Description                          |

| Revision History 2                           |

| Specifications                               |

| Timing Specifications 5                      |

| Absolute Maximum Ratings                     |

| Thermal Resistance                           |

| Junction to Board Thermal Impedance6         |

| ESD Caution                                  |

| Pin Configuration and Function Descriptions7 |

| Typical Performance Characteristics          |

| Theory of Operation17                        |

| Basic Structure                              |

| Control/Logic Circuitry17                    |

| Common-Mode Voltage17                        |

| Applications Information                     |

| Basic Connections                            |

| Digital Interface Overview19                 |

| SPI Read20                                    |

|-----------------------------------------------|

| ADC Interfacing                               |

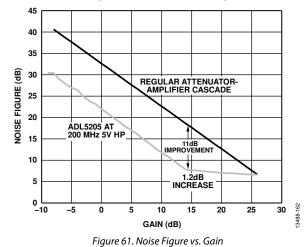

| Noise Figure vs. Gain Setting21               |

| Evaluation Board 22                           |

| Overview                                      |

| Power Supply Interface                        |

| Signal Inputs and Outputs23                   |

| Manual Controls                               |

| Parallel Interface24                          |

| Serial Interface                              |

| Standard Development Platform (SDP) Interface |

| Evaluation Board Control Software             |

| Command Line Control Program                  |

| Graphical User Interface (GUI) Program        |

| Evaluation Board Schematics and Layout        |

| Bill of Materials                             |

| Outline Dimensions                            |

#### **REVISION HISTORY**

4/16—Revision 0: Initial Version

# **SPECIFICATIONS**

Supply voltage ( $V_{POS}$ ) = 3.3 V or 5 V,  $T_A$  = 25°C,  $Z_{LOAD}$  = 200  $\Omega$ , maximum gain (Gain code = 000000), frequency = 200 MHz, PM = 0 V, 2 V p-p differential output, unless otherwise noted.

#### Table 1.

|                                         |                                                                                | 3   | .3 V Sup | ply | 5   | i V Supp | ly  |        |

|-----------------------------------------|--------------------------------------------------------------------------------|-----|----------|-----|-----|----------|-----|--------|

| Parameter <sup>1</sup>                  | <b>Test Conditions/Comments</b>                                                | Min | Тур      | Max | Min | Тур      | Мах | Unit   |

| DYNAMIC PERFORMANCE                     |                                                                                |     |          |     |     |          |     |        |

| –3 dB Bandwidth                         | High performance mode                                                          |     | 1700     |     |     | 1700     |     | MHz    |

|                                         | Low power mode                                                                 |     | 1500     |     |     | 1500     |     | MHz    |

| Slew Rate                               |                                                                                |     | 5        |     |     | 5        |     | V/ns   |

| INPUT STAGE                             | VINx+ and VINx- pins                                                           |     |          |     |     |          |     |        |

| Maximum Input Swing                     | Gain code = 111111                                                             |     | 8        |     |     | 8        |     | V р-р  |

| Differential Input Resistance           | Differential                                                                   |     | 100      |     |     | 100      |     | Ω      |

| Input Common-Mode Voltage               |                                                                                |     | 1.65     |     |     | 2.5      |     | V      |

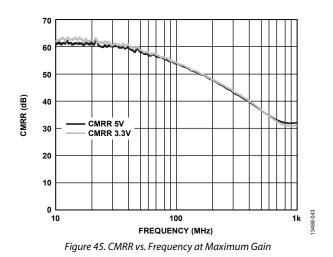

| Common-Mode Rejection Ratio (CMRR)      | Gain code = 000000                                                             |     | 48       |     |     | 48       |     | dB     |

| GAIN                                    |                                                                                |     |          |     |     |          |     |        |

| Voltage Gain Range                      |                                                                                |     | 35       |     |     | 35       |     | dB     |

| Maximum Gain                            | Gain code = 000000                                                             |     | 26       |     |     | 26       |     | dB     |

| Minimum Gain                            | Gain code = 100011 to 111111                                                   |     | -9       |     |     | -9       |     | dB     |

| Gain Step Size                          |                                                                                |     | 1        |     |     | 1        |     | dB     |

| Gain Step Accuracy                      |                                                                                |     | ±0.2     |     |     | ±0.2     |     | dB     |

| Gain Flatness                           | From 30 MHz to 200 MHz                                                         |     | 0.2      |     |     | 0.2      |     | dB p-p |

| Gain Temperature Sensitivity            | Gain code = 000000                                                             |     | 2.4      |     |     | 4        |     | mdB/°C |

| Fast Attack Step Response Delay         | For $V_{IN} = 0.1 V$ , FA_A or FA_B 15<br>changing from 0 to 1 with 16 dB step |     |          | 80  |     | ns       |     |        |

| COMMON-MODE INPUTS                      |                                                                                |     |          |     |     |          |     |        |

| VCMA and VCMB Input Resistance          |                                                                                |     | 2.6      |     |     | 2.6      |     | kΩ     |

| OUTPUT STAGE                            | VOUTx+ and VOUTx- pins                                                         |     |          |     |     |          |     |        |

| Output Voltage Swing                    | At P1dB, gain code = 000000                                                    |     | 4.5      |     |     | 5.4      |     | V р-р  |

| Common-Mode Voltage Reference           | VCMA, VCMB                                                                     | 1.2 | 1.65     | 1.8 | 1.4 | 2.5      | 2.7 | V      |

| Output Common-Mode Offset               | ((VOUTx+) + (VOUTx-))/2 - VCMx/2                                               | -10 |          | +10 | -10 |          | +10 | mV     |

| Differential Output Resistance          | Differential                                                                   |     | 10       |     |     | 10       |     | Ω      |

| Short-Circuit Current                   | High performance mode                                                          |     | 22       |     | 22  |          | mA  |        |

|                                         | Low power mode                                                                 |     | 17       |     |     | 17       |     | mA     |

| NOISE/HARMONIC PERFORMANCE              | Gain code = 000000, high<br>performance mode                                   |     |          |     |     |          |     |        |

| 10 MHz                                  |                                                                                |     |          |     |     |          |     |        |

| Noise Figure                            |                                                                                |     | 6.3      |     |     | 6.5      |     | dB     |

| Second Harmonic                         | V <sub>оит</sub> = 2 V р-р                                                     |     | -103     |     |     | -103     |     | dBc    |

| Third Harmonic                          | V <sub>OUT</sub> = 2 V p-p                                                     |     | -101     |     |     | -100     |     | dBc    |

| Output Third-Order Intercept (OIP3)     | $V_{OUT} = 2 V p - p composite$                                                |     | 48.5     |     |     | 47       |     | dBm    |

| Output 1 dB Compression Point<br>(P1dB) |                                                                                |     | 13.7     |     |     | 17.5     |     | dBm    |

| 100 MHz                                 |                                                                                |     |          |     |     |          |     |        |

| Noise Figure                            |                                                                                |     | 6.3      |     |     | 6.6      |     | dB     |

| Second Harmonic                         | $V_{OUT} = 2 V p - p$                                                          |     | -86      |     |     | -90      |     | dBc    |

| Third Harmonic                          | $V_{OUT} = 2 V p - p$                                                          |     | -87      |     |     | -94      |     | dBc    |

| OIP3                                    | $V_{OUT} = 2 V p - p composite$                                                |     | 45       |     |     | 46       |     | dBm    |

| Output P1dB                             |                                                                                |     | 13.2     |     |     | 17.4     |     | dBm    |

|                                                            |                                                                                | 3    | .3 V Sup | ply  | 5 V Supply |       |      |      |

|------------------------------------------------------------|--------------------------------------------------------------------------------|------|----------|------|------------|-------|------|------|

| Parameter                                                  | Test Conditions/Comments                                                       | Min  | Тур      | Max  | Min        | Тур   | Max  | Unit |

| 200 MHz                                                    |                                                                                |      |          |      |            |       |      |      |

| Noise Figure Increase for First 12 dB of<br>Gain Reduction | Gain code = 000000 to 001100                                                   |      | 1.2      |      |            | 1.2   |      | dB   |

| Noise Figure                                               |                                                                                |      | 6.6      |      |            | 6.6   |      | dB   |

| Second Harmonic                                            | $V_{OUT} = 2 V p - p$                                                          |      | -75.5    |      |            | -75   |      | dBc  |

| Third Harmonic                                             | $V_{OUT} = 2 V p - p$                                                          |      | -77      |      |            | -87.5 |      | dBc  |

| OIP3                                                       | $V_{OUT} = 2 V p - p composite$                                                |      | 44       |      |            | 48.5  |      | dBm  |

| Output P1dB                                                |                                                                                |      | 13       |      |            | 17    |      | dBm  |

| 300 MHz                                                    |                                                                                |      |          |      |            |       |      |      |

| Noise Figure                                               |                                                                                |      | 6.6      |      |            | 6.9   |      | dB   |

| Second Harmonic                                            | $V_{OUT} = 2 V p - p$                                                          |      | -63      |      |            | -64   |      | dBc  |

| Third Harmonic                                             | $V_{OUT} = 2 V p - p$                                                          |      | -68      |      |            | -78   |      | dBc  |

| OIP3                                                       | $V_{OUT} = 2 V p - p composite$                                                |      | 43       |      |            | 43.5  |      | dBm  |

| Output P1dB                                                |                                                                                |      | 12.8     |      |            | 17.3  |      | dBm  |

| 500 MHz                                                    |                                                                                |      |          |      |            |       |      |      |

| Noise Figure                                               |                                                                                |      | 7.8      |      |            | 8.2   |      | dB   |

| Second Harmonic                                            | $V_{OUT} = 2 V p - p$                                                          |      | -58      |      |            | -61.5 |      | dBc  |

| Third Harmonic                                             | $V_{OUT} = 2 V p - p$                                                          |      | -57.5    |      |            | -67.5 |      | dBc  |

| OIP3                                                       | $V_{OUT} = 2 V p - p$ composite                                                |      | 37       |      |            | 36    |      | dBm  |

| Output P1dB                                                | 15                                                                             |      | 13.1     |      |            | 17.7  |      | dBm  |

| DIGITAL INTERFACE                                          |                                                                                |      |          |      |            |       |      |      |

| Input Pins                                                 | A0 to A5, B0 to B5, MODE1,<br>MODE0, PWUPA, PWUPB, PM,<br>LATCHA, LATCHB, SDIO |      |          |      |            |       |      |      |

| VIH                                                        | Logic high                                                                     | 2    |          | VPOS | 2          |       | 3.3  | V    |

| VIL                                                        | Logic low                                                                      | 0    |          | 1.0  | 0          |       | 1.0  | V    |

| Input Leakage Current                                      | Digital input voltage = 0 V to 3.3 V                                           |      | ±3       |      |            | ±3    |      | μA   |

| Output Pins                                                | SDIO                                                                           |      |          |      |            |       |      |      |

| Logic High (V <sub>он</sub> )                              | $I_{OH} = -2 \text{ mA} $ 2.                                                   |      |          |      | 2.4        |       |      | V    |

| Logic Low (V <sub>OL</sub> )                               | $I_{OL} = 2 \text{ mA}$                                                        |      |          | 0.5  |            |       | 0.5  | V    |

| POWER-INTERFACE                                            |                                                                                | 1    |          |      |            |       |      |      |

| Supply Voltage (V <sub>POS</sub> )                         | VPOS                                                                           | 3.15 | 3.3      | 3.45 | 4.75       | 5     | 5.25 | V    |

| Quiescent Current                                          |                                                                                |      |          |      |            |       |      |      |

| High Performance Mode                                      | PM = low                                                                       |      | 175      |      |            | 175   |      | mA   |

| Low Power Mode                                             | PM = high                                                                      |      | 135      |      |            | 135   |      | mA   |

| Power-Down Current                                         | PWUPA and PWUPB = low                                                          | 1    | 14       |      |            | 14    |      | mA   |

<sup>1</sup> When referring to a single function of a multifunction pin in the parameters, only the portion of the pin name that is relevant to the specification is listed. For full pin names of multifunction pins, refer to the Pin Configuration and Function Descriptions section.

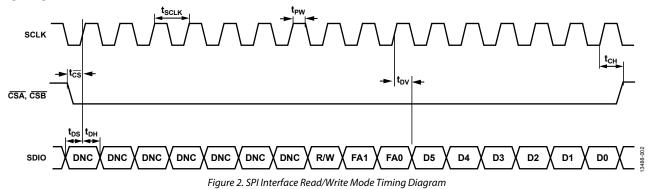

#### TIMING SPECIFICATIONS

#### **Table 2. SPI Timing Parameters**

| Parameter                       | Symbol            | Min | Тур | Max | Unit | Test Conditions/Comments |

|---------------------------------|-------------------|-----|-----|-----|------|--------------------------|

| CSA or CSB to SCLK Setup Time   | t <sub>cs</sub>   | 20  |     |     | ns   |                          |

| SDIO to SCLK Setup Time         | t <sub>DS</sub>   | 10  |     |     | ns   |                          |

| SCLK to SDIO Hold Time          | t <sub>DH</sub>   | 10  |     |     | ns   |                          |

| SCLK Pulse Width                | t <sub>PW</sub>   | 25  |     |     | ns   |                          |

| SCLK Cycle Time                 | t <sub>SCLK</sub> | 50  |     |     | ns   |                          |

| SCLK to CSA or CSB Setup Time   | t <sub>сн</sub>   | 10  |     |     | ns   |                          |

| SCLK to SDIO Output Valid Delay | t <sub>DV</sub>   |     |     | 20  | ns   | During readback          |

#### **Timing Diagrams**

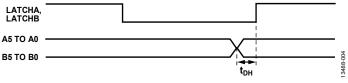

Figure 4. Parallel Mode Timing Diagram

## **ABSOLUTE MAXIMUM RATINGS**

#### Table 3.

| Parameter                                                               | Rating           |

|-------------------------------------------------------------------------|------------------|

| Differential Output Voltage Swing ×<br>Bandwidth Product                | 3 V-GHz          |

| Supply Voltage, V <sub>POS</sub>                                        | 5.4 V            |

| PWUPA, PWUPB, A0 to A5, B0 to B5, MODE0,<br>MODE1, PM, LATCH A, LATCH B | –0.5 V to +3.6 V |

| Input Voltage (VINx+ ,VINx–)                                            | –0.5 V to +3.1 V |

| Differential Input Voltage ((VINx+) – (VINx–))                          | ±1 V             |

| Internal Power Dissipation                                              | 1000 mW          |

| Maximum Junction Temperature                                            | 135°C            |

| Operating Temperature Range                                             | –40°C to +85°C   |

| Storage Temperature Range                                               | –65°C to +150°C  |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

Table 4 shows the thermal resistance from the die to ambient  $(\theta_{JA})$ , die to board  $(\theta_{JB})$ , and die to lead  $(\theta_{JC})$ , respectively.

#### Table 4. Thermal Resistance

| Package Type  | θιΑ  | θյβ  | οıc  | Unit |

|---------------|------|------|------|------|

| 40-Lead LFCSP | 47.7 | 24.4 | 15.4 | °C/W |

#### JUNCTION TO BOARD THERMAL IMPEDANCE

The junction to board thermal impedance ( $\theta_{JB}$ ) is the thermal impedance from the die to the leads of the ADL5205. The value given in Table 4 is based on the standard printed circuit board (PCB) described in the JESD51-7 standard for thermal testing of surface-mount components. PCB size and complexity (number of layers) affect  $\theta_{JB}$ ; more layers tend to reduce thermal impedance slightly.

If the PCB temperature is known, use the junction to board thermal impedance to calculate the die temperature (also known as the junction temperature) to ensure that the die temperature does not exceed the specified limit of 135°C. For example, if the PCB temperature is 85°C, the die temperature is given by

$$T_{I} = T_{B} + (P_{DISS} \times \theta_{IB})$$

The worst case power dissipation for the ADL5205 is 919 mW (5.25 V  $\times$  175 mA, see Table 1). Therefore, T<sub>1</sub> is

$T_J = 85^{\circ}\text{C} + (0.919 \text{ W} \times 24.4^{\circ}\text{C/W}) = 107.4^{\circ}\text{C}$

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

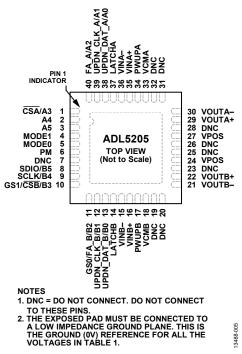

# **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

Figure 5. Pin Configuration

| Pin No.                              | Mnemonic      | Description                                                                                                                                             |  |  |  |  |

|--------------------------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1                                    | CSA/A3        | Channel A Select in Serial Mode (CSA). When serial mode is enabled, a logic low selects Channel A.                                                      |  |  |  |  |

|                                      |               | Bit 3 for Channel A in Parallel Gain Control Interface Mode (A3).                                                                                       |  |  |  |  |

| 2                                    | A4            | Bit 4 for Channel A in Parallel Gain Control Interface Mode (A4).                                                                                       |  |  |  |  |

| 3                                    | A5            | Bit 5 for Channel A in Parallel Gain Control Interface Mode (A5).                                                                                       |  |  |  |  |

| 4                                    | MODE1         | MSB for Mode Control. Use both the MODE0 and MODE1 pins to select parallel, SPI, or up/o interface mode.                                                |  |  |  |  |

| 5                                    | MODE0         | LSB for Mode Control. Use both the MODE1 and MODE0 pins to select parallel, SPI, or up/down interface mode.                                             |  |  |  |  |

| 6                                    | PM            | Power Mode. Set this pin to logic low to enable high performance mode, or logic high to enable low power mode.                                          |  |  |  |  |

| 7, 19, 20, 23, 25, 26,<br>28, 31, 32 | DNC           | Do Not Connect. Do not connect to these pins.                                                                                                           |  |  |  |  |

| 8                                    | SDIO/B5       | Serial Data Input and Output in SPI Mode (SDIO).                                                                                                        |  |  |  |  |

|                                      |               | Bit 5 for Channel B in Parallel Gain Control Interface Mode (B5).                                                                                       |  |  |  |  |

| 9                                    | SCLK/B4       | Serial Clock Input in SPI Mode (SCLK).                                                                                                                  |  |  |  |  |

|                                      |               | Bit 4 for Channel B in Parallel Gain Control Interface (B4).                                                                                            |  |  |  |  |

| 10                                   | GS1/CSB/B3    | MSB for the Gain Step Size Control in Up/Down Mode (GS1).                                                                                               |  |  |  |  |

|                                      |               | Channel B Select in Serial Mode (CSB). When serial mode is enabled, a logic low selects Channel B.                                                      |  |  |  |  |

|                                      |               | Bit 3 for Channel B in Parallel Gain Control Mode (B3).                                                                                                 |  |  |  |  |

| 11                                   | GS0/FA_B/B2   | LSB for the Gain Step Size Control in Up/Down Mode (GS0).                                                                                               |  |  |  |  |

|                                      |               | Fast Attack for Channel B (FA_B). In serial mode, a logic high on this pin attenuates Channel B according to the FA bit values in the control register. |  |  |  |  |

|                                      |               | Bit 2 for Channel B in Parallel Gain Control Interface (B2).                                                                                            |  |  |  |  |

| 12                                   | UPDN_CLK_B/B1 | Clock Interface for the Channel B Up/Down Function (UPDN_CLK_B).                                                                                        |  |  |  |  |

|                                      |               | Bit 1 for Channel B in Parallel Gain Control Interface Mode (B1).                                                                                       |  |  |  |  |

| 13                                   | UPDN_DAT_B/B0 | Data Pin for the Channel B Up/Down Function (UPDN_DAT_B).                                                                                               |  |  |  |  |

|                                      |               | Bit 0 for Channel B in Parallel Gain Control Interface Mode (B0).                                                                                       |  |  |  |  |

| Pin No. | Mnemonic      | Description                                                                                                                                                          |  |  |  |

|---------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 14      | LATCHB        | Latch B. A logic low on this pin allows the gain to change on Channel B in parallel gain contro<br>interface mode. A logic high on this pin prevents gain changes.   |  |  |  |

| 15      | VINB-         | Channel B Negative Analog Input.                                                                                                                                     |  |  |  |

| 16      | VINB+         | Channel B Positive Analog Input.                                                                                                                                     |  |  |  |

| 17      | PWUPB         | Channel B Power-Up. A logic high on this pin powers up Channel B, and a logic low on this pin disables it.                                                           |  |  |  |

| 18      | VCMB          | Channel B Common-Mode Output.                                                                                                                                        |  |  |  |

| 21      | VOUTB-        | Channel B Negative Analog Output.                                                                                                                                    |  |  |  |

| 22      | VOUTB+        | Channel B Positive Analog Output.                                                                                                                                    |  |  |  |

| 24, 27  | VPOS          | Positive Power Supply.                                                                                                                                               |  |  |  |

| 29      | VOUTA+        | Channel A Negative Analog Output.                                                                                                                                    |  |  |  |

| 30      | VOUTA-        | Channel A Positive Output.                                                                                                                                           |  |  |  |

| 33      | VCMA          | Channel A Common-Mode Output.                                                                                                                                        |  |  |  |

| 34      | PWUPA         | Channel A Power-Up. A logic high on this pin powers up Channel A, and a logic low on this pin disables it.                                                           |  |  |  |

| 35      | VINA+         | Channel A Positive Analog Input.                                                                                                                                     |  |  |  |

| 36      | VINA-         | Channel A Negative Analog Input.                                                                                                                                     |  |  |  |

| 37      | LATCHA        | Latch A. A logic low on this pin allows the gain to change on Channel A in the parallel gain control interface mode. A logic high on this pin prevents gain changes. |  |  |  |

| 38      | UPDN_DAT_A/A0 | Data Pin for the Channel A Up/Down Function (UPDN_DAT_A).                                                                                                            |  |  |  |

|         |               | Bit 0 for Channel A in Parallel Gain Control Interface Mode (A0).                                                                                                    |  |  |  |

| 39      | UPDN_CLK_A/A1 | Clock Interface for the Channel A Up/Down Function (UPD_CLK_A).                                                                                                      |  |  |  |

|         |               | Bit 1 for Channel A in Parallel Gain Control Interface Mode (A1).                                                                                                    |  |  |  |

| 40      | FA_A/A2       | Fast Attack for Channel A (FA_A). In serial mode, a logic high on this pin attenuates Channel A according to an FA SPI word.                                         |  |  |  |

|         |               | Bit 2 for Channel A in Parallel Gain Control Interface (A2).                                                                                                         |  |  |  |

| EP      | GND           | Exposed Pad Ground. The exposed pad must be connected to a low impedance ground plane.<br>This is the ground (0 V) reference for all the voltages in Table 1.        |  |  |  |

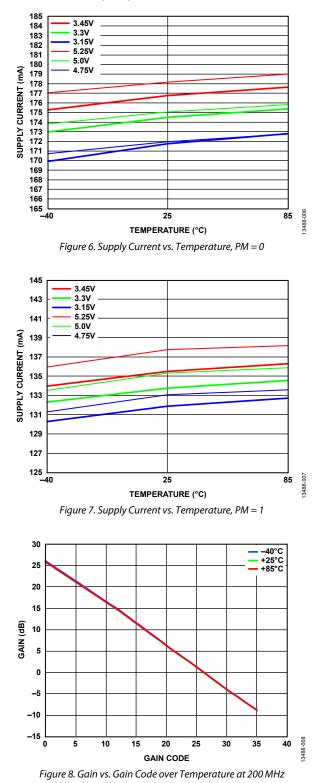

# **TYPICAL PERFORMANCE CHARACTERISTICS**

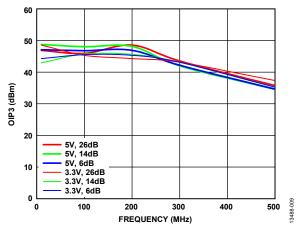

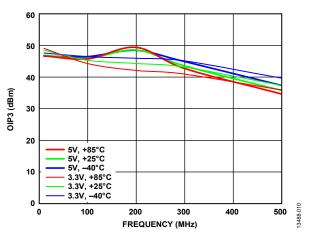

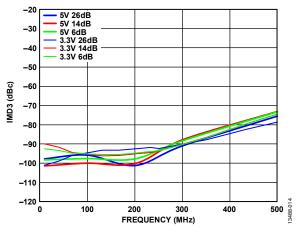

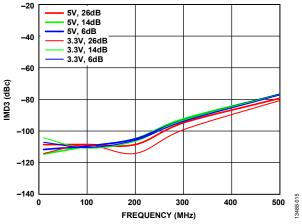

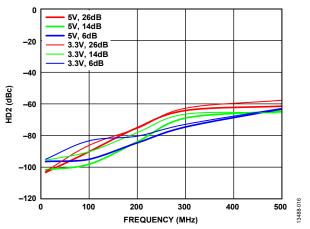

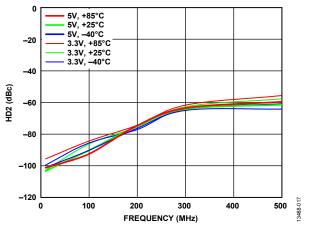

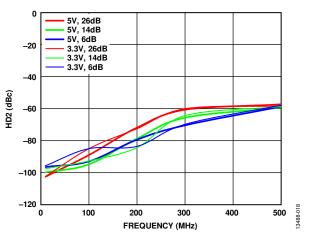

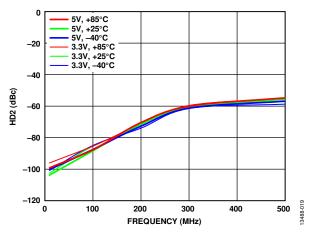

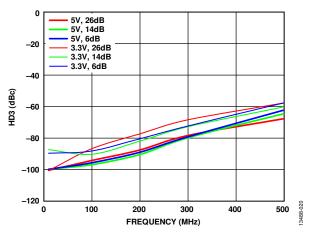

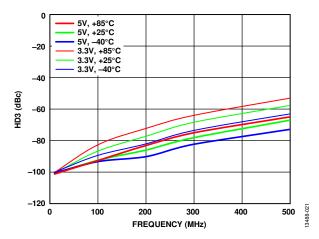

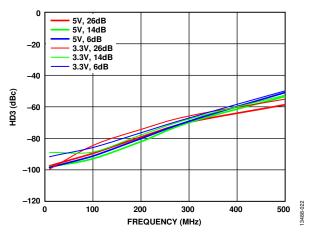

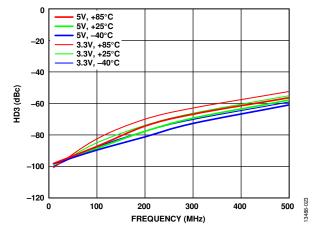

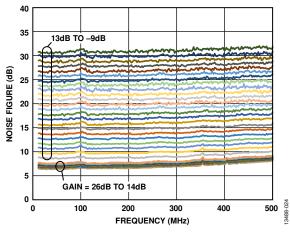

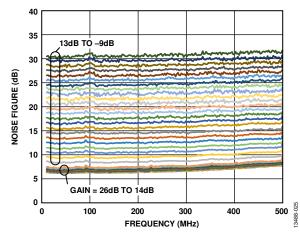

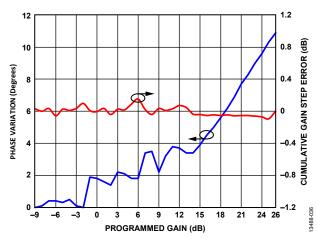

Supply voltage ( $V_{POS}$ ) = 3.3 V or 5 V,  $T_A$  = 25°C,  $Z_{LOAD}$  = 200  $\Omega$ , maximum gain (gain code = 000000), 2 V p-p composite differential output for intermodulation distortion (IMD) and OIP3, 2 V p-p differential output for second harmonic distortion (HD2) and third harmonic distortion (HD3), VCMA = VCMB =  $V_{POS}/2$ , unless otherwise noted.

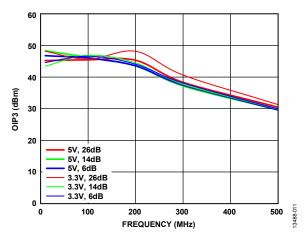

Figure 9. Output Third-Order Intercept (OIP3) vs. Frequency over V<sub>POS</sub> at Three Gain Codes, High Performance Mode

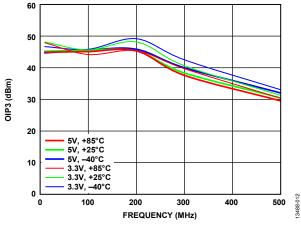

Figure 10. Output Third-Order Intercept (OIP3) vs. Frequency over V<sub>POS</sub> for Three Temperatures at Maximum Gain, High Performance Mode

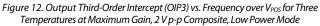

Figure 11. Output Third-Order Intercept (OIP3) vs. Frequency over V<sub>POS</sub> at Three Gain Codes, Low Power Mode

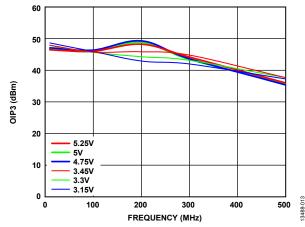

Figure 13. Output Third-Order Intercept (OIP3) vs. Frequency and V<sub>POS</sub> Variance (±5%), Maximum Gain, High Performance Mode

Figure 14. Two-Tone Output IMD3 vs. Frequency over V<sub>POS</sub> for Three Gain Codes at 2 V p-p Composite, Low Power Mode

Figure 15. Two-Tone Output IMD3 vs. Frequency over V<sub>POS</sub> for Three Gain Codes at 2 V p-p, High Performance Mode

Figure 16. Second Harmonic Distortion (HD2) vs. Frequency over V<sub>POS</sub> for Three Gain Codes, High Performance Mode

Figure 17. Second Harmonic Distortion (HD2) vs. Frequency over V<sub>POS</sub> for Three Temperatures at Maximum Gain, 2 V p-p, High Performance Mode

Figure 18. Second Harmonic Distortion (HD2) vs. Frequency over V<sub>POS</sub> for Three Gain Codes at 2 V p-p Composite, Low Power Mode

Figure 19. Second Harmonic Distortion (HD2) vs. Frequency over V<sub>POS</sub> for Three Temperatures at Maximum Gain, 2 V p-p Composite, Low Power Mode

Figure 20. Third Harmonic Distortion (HD3) vs. Frequency over V<sub>POS</sub> for Three Gain Codes at 2 V p-p Composite, High Performance Mode

Figure 21. Third Harmonic Distortion (HD3) vs. Frequency vs. V<sub>POS</sub> for Three Temperatures at Maximum Gain, 2 V p-p Composite, High Performance Mode

Figure 22. Third Harmonic Distortion (HD3) vs. Frequency over V<sub>POS</sub> for Three Gain Codes at 2 V p-p Composite, Low Power Mode

Figure 23. Third Harmonic Distortion (HD3) vs. Frequency over V<sub>POS</sub> for Three Temperatures at Maximum Gain, 2 V p-p Composite, Low Power Mode

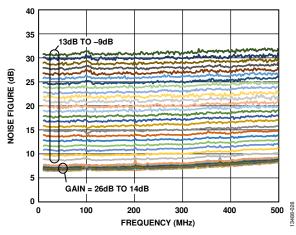

Figure 24. Noise Figure vs. Frequency for 35 dB Gain Range at  $V_{POS} = 5 V$ , High Performance Mode

Figure 25. Noise Figure vs. Frequency for 35 dB Gain Range at  $V_{POS} = 3.3 V$ , High Performance Mode

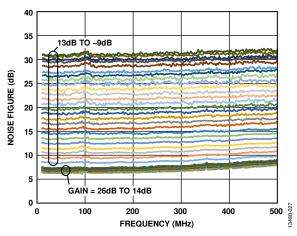

Figure 26. Noise Figure vs. Frequency for 35 dB Gain Range at  $V_{POS} = 5 V$ , Low Power Mode

Figure 27. Noise Figure vs. Frequency for 35 dB Gain Range at  $V_{POS} = 3.3 V$ , Low Power Mode

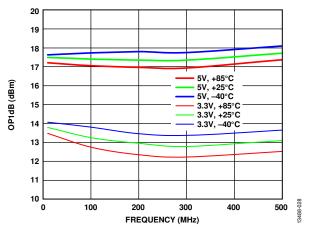

Figure 28. Output 1 dB Compression Point (OP1dB) vs. Frequency at Maximum Gain, High Performance Mode

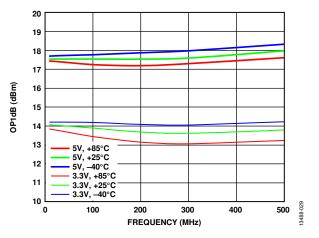

Figure 29. Output 1 dB Compression Point (OP1dB) vs. Frequency at Maximum Gain, Low Power Mode

### **Data Sheet**

####

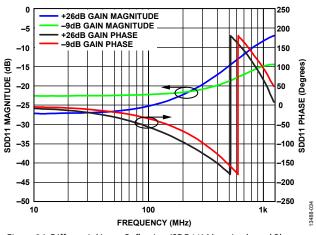

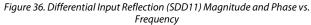

Figure 30. Differential S-Parameters (SDD21, SDD12, SDD11, SDD22) vs. Frequency

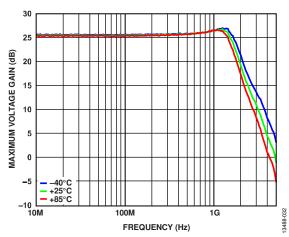

Figure 31. Maximum Voltage Gain vs. Frequency over Temperature at  $V_{\text{POS}}$  = 3.3 V

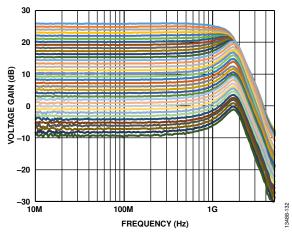

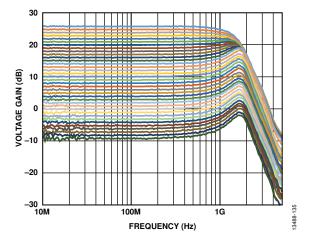

Figure 32. Voltage Gain vs. Frequency for Various Gain Steps at  $V_{POS}$  = 3.3 V, Low Power Mode

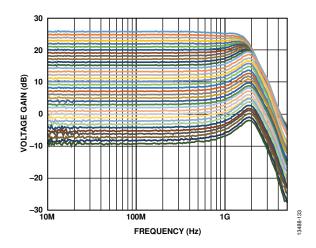

Figure 33. Voltage Gain vs. Frequency for Various Gain Steps at  $V_{POS} = 5 V$ , High Performance Mode

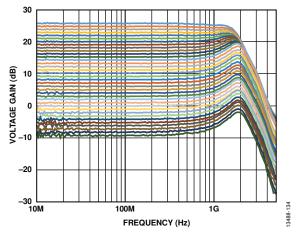

Figure 34. Voltage Gain vs. Frequency for Various Gain Steps at  $V_{POS} = 3.3 V$ , High Performance Mode

Figure 35. Voltage Gain vs. Frequency for Various Gain Steps at  $V_{POS} = 5 V$ , Low Power Mode

Rev. 0 | Page 13 of 31

Figure 37. Differential Output Reflection (SDD22) Magnitude and Phase vs. Frequency

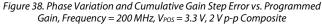

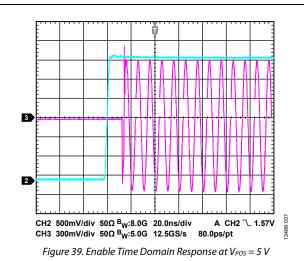

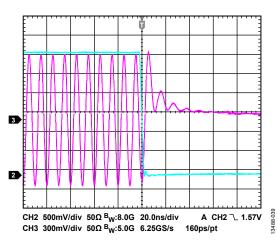

Figure 41. Disable Time Domain Response at  $V_{POS} = 5 V$

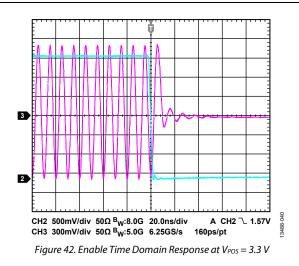

## Data Sheet

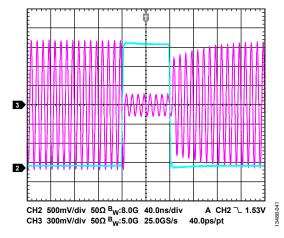

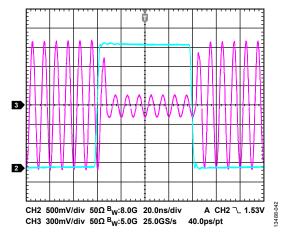

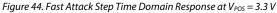

Figure 43. Fast Attack Step Time Domain Response at V<sub>POS</sub> = 5 V

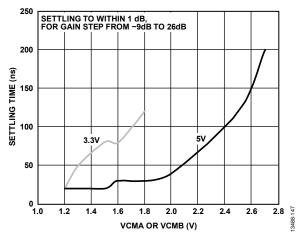

Figure 46. Maximum Gain Transition Settling Time vs. Output Common-Mode Voltage (VCMA or VCMB)

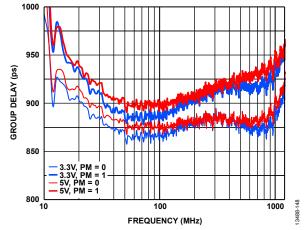

Figure 47. Group Delay at Maximum Gain vs. Frequency over V<sub>POS</sub> and Power Modes

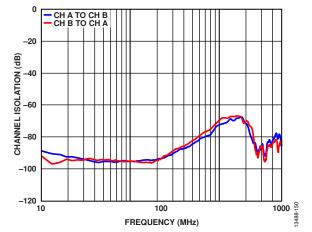

Figure 49. Channel Isolation vs. Frequency for Channel A and Channel B

### THEORY OF OPERATION BASIC STRUCTURE

The ADL5205 is a dual differential, digitally controlled variable gain amplifier (DGA). Each DGA consists of a 100  $\Omega$  differential input, digitally controlled passive attenuator followed by a digitally controlled gain amplifier. The input, digitally controlled, binary weighted attenuator has a range of 0 dB to 23 dB with 1 dB steps, and the amplifier has a range of 14 dB to 26 dB, also with 1 dB steps. On-chip logic circuitry maps the gain codes such that the first 12 dB of gain reduction from the maximum gain are accomplished using the digitally controlled gain amplifier, only. This topology allows the first 12 dB of gain reduction to be accompanied by typically 1.2 dB of total noise figure degradation (at 200 MHz). The OIP3 also remains nearly constant over the first 12 dB of gain range. The noise figure for the DGA increases by 1 dB for each decibel of attenuation within the remaining 23 dB attenuation range. The differential output impedance of the amplifier is  $10 \Omega$ .

#### **CONTROL/LOGIC CIRCUITRY**

The ADL5205 features three different gain control interfaces: serial, parallel, or up/down control, determined by the combination of the MODE1 and MODE0 pins. For details on controlling the gain in each of these modes, see the Digital Interface Overview section. In general, the gain step size is 1 dB; however, larger step sizes can be programmed as described in the Digital Interface Overview section. Each amplifier has a maximum gain of +26 dB (Gain Code 000000) to -9 dB (Gain Code 100011 to Gain Code 111111). Using the performance mode (PM) pin, users can lower the power consumption of the device with a slight degradation in linearity performance.

#### **COMMON-MODE VOLTAGE**

The ADL5205 is flexible in terms of input/output coupling. It can be ac-coupled or dc-coupled at the inputs and/or outputs within the specified output common-mode levels of 1.2 V to 2.7 V, depending on the supply voltage. If no external output common-mode voltage is applied, the input and output common-mode voltages are set internally to half of the supply voltage.

The output common-mode voltages of the ADL5205 are controlled by the voltages on the VCMA and VCMB pins. Each of these pins is connected internally through 5 k $\Omega$  resistors to the VPOS pin as well as to the exposed pad (EP). As a result, the commonmode output voltage at each channel is preset internally to half of the supply voltage at VPOS. Alternatively, the VCMA and VCMB pins can be connected to the common-mode voltage reference output from an ADC, and thus the common-mode levels between the two devices can be matched without requiring any external components.

Figure 50. Basic Structure

### APPLICATIONS INFORMATION BASIC CONNECTIONS

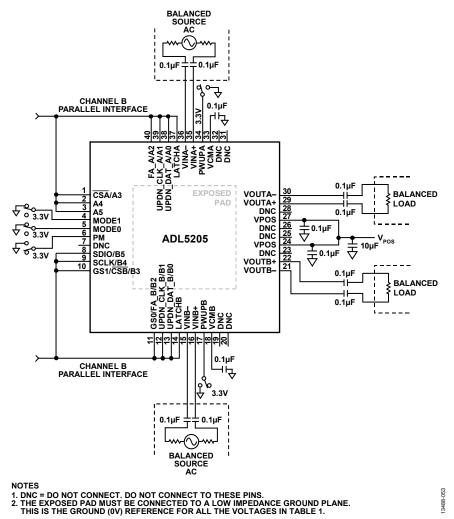

Figure 51 shows the basic connections for operating the ADL5205. Apply a voltage of 3.3 V or 5 V to the VPOS pins. Decouple each supply pin with at least one low inductance, surface-mount ceramic capacitor of 0.1  $\mu$ F placed as close to the device as possible. The differential outputs have a dc common-mode voltage that is approximately half of the supply; therefore, decouple these outputs using 0.1  $\mu$ F capacitors to the balanced load. The balanced differential inputs have the same dc common-mode voltage as the outputs; the inputs are decoupled using 0.1  $\mu$ F capacitors as well. The digital pins, mode control pins, associated SPI pins, and parallel gain control pins, (PM, PWUPA, and PWUPB) operatefrom a 3.3 V voltage.

To enable each channel of the ADL5205, pull the PWUPA pin or the PWUPB pin high (2.0 V  $\leq$  PWUPA/PWUPB  $\leq$  3.3 V). A logic low on the PWUPA pin or the PWUPB pin sets the channel to sleep mode, reducing the current consumption to approximately 7 mA per channel. The VCMA and the VCMB pins are the reference inputs for the output common-mode voltage of each channel, and they must be decoupled with 0.1 µF capacitors.

Figure 51. Basic Connections

#### DIGITAL INTERFACE OVERVIEW

The three digital control interface options of the ADL5205 DGA are, respectively,

- Parallel control interface

- Serial peripheral interface

- Gain step up/down interface

The digital control interface selection is made via two digital pins, MODE1 and MODE0, as shown in Table 6. Additionally, there are three power mode control pins, PM, PWUPA, and PWUPB. PM selects between the high performance and low power modes, whereas PWUPA and PWUPB enable (powerup) the corresponding channel. The gain in each channel is controlled by a 6-bit binary code (A5 to A0 and B5 to B0).

The same physical pins are shared between three interfaces, resulting in as many as three different functions per digital pin (see Table 5).

#### Table 6. Digital Control Interface Selection Truth Table

| MODE1 | MODE0 | Interface    |

|-------|-------|--------------|

| 0     | 0     | Parallel     |

| 0     | 1     | Serial (SPI) |

| 1     | 0     | Up/down      |

| 1     | 1     | Up/down      |

#### Parallel Digital Interface

The parallel digital interface uses six gain control bits and a latch pin per amplifier. The latch pin controls whether the input data latch is transparent (logic low) or latched (logic high). In transparent mode, the gain changes as the input gain control bits change. In latched mode, the gain is determined by the latched gain setting and is not changed by changing the input gain control bits.

#### Serial Peripheral Interface (SPI)

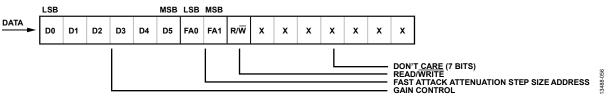

The SPI uses three pins (SDIO, SCLK, and  $\overline{\text{CSA}}$  or  $\overline{\text{CSB}}$ ). The SPI data register consists of two bytes: six gain control bits (D0 to D5), two attenuation step size address bits (FA0 and FA1), one read/write bit (R/W), and seven don't care bits (X), as shown in Figure 53.

The SPI uses a bidirectional pin (SDIO) for writing to the SPI register and for reading from the SPI register. To write to the SPI register, pull the  $\overline{\text{CSA}}$  or the  $\overline{\text{CSB}}$  pin low and apply 16 clock pulses to shift the 16 bits into the corresponding SPI register, MSB first. Individual channel SPI registers can be selected by pulling  $\overline{\text{CSA}}$

or  $\overline{\text{CSB}}$  low. By simultaneously pulling the  $\overline{\text{CSA}}$  and  $\overline{\text{CSB}}$  pins low, the same data can be written to both SPI registers.

SPI register read back operation is described in the SPI Read section. Because there is only one SDIO line, the control register of each channel must be read back individually.

SPI fast attack mode is controlled by the FA\_A or FA\_B pins. A logic high on the FA\_A pin or FA\_B pin results in an attenuation selected by the FA1 and the FA0 bits in the SPI register.

| FA1 | FA0 | Step Size (dB) |

|-----|-----|----------------|

| 0   | 0   | 2              |

| 0   | 1   | 4              |

| 1   | 0   | 8              |

| 1   | 1   | 16             |

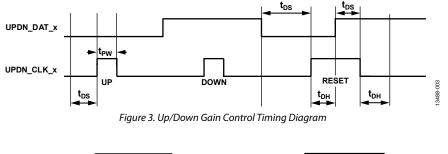

#### **Up/Down Interface**

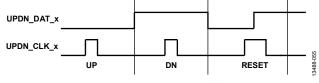

The up/down interface uses two digital pins to control the gain. When the UPDN\_DAT\_x pin is low, the gain for the corresponding channel is increased by a clock pulse on the UPDN\_CLK\_x pin (rising and falling edges). When the UPDN\_DAT\_x pin is high, the corresponding gain is decreased by a clock pulse on the UPDN\_CLK\_x pin. Reset is detected when the rising edge of UPDN\_CLK\_x latches one polarity on UPDN\_DAT\_x, and the falling edge latches the opposite polarity. Reset results in the minimum gain code of 111111.

Figure 52. Up/Down Gain Control Timing

The step size is selectable by the GS1 and GS0 pins. The default step size is 1 dB. The gain code count rails at the top and bottom of the control range.

#### Table 8. Step Size Control Truth Table

| GS1 | GS0 | Step Size (dB) |

|-----|-----|----------------|

| 0   | 0   | 1              |

| 0   | 1   | 2              |

| 1   | 0   | 4              |

| 1   | 1   | 8              |

Figure 53. 16-Bit SPI Register

### **Data Sheet**

| Table 9. Gain Code vs. Voltage Gain |                   |  |  |

|-------------------------------------|-------------------|--|--|

| 6-Bit Binary Gain Code, D5 to D0    | Voltage Gain (dB) |  |  |

| 000000                              | +26               |  |  |

| 000001                              | +25               |  |  |

| 000010                              | +24               |  |  |

| 000011                              | +23               |  |  |

| 000100                              | +22               |  |  |

| 000101                              | +21               |  |  |

| 000110                              | +20               |  |  |

| 000111                              | +19               |  |  |

| 001000                              | +18               |  |  |

| 001001                              | +17               |  |  |

| 001010                              | +16               |  |  |

| 001011                              | +15               |  |  |

| 001100                              | +14               |  |  |

| 001101                              | +13               |  |  |

| 001110                              | +12               |  |  |

| 001111                              | +11               |  |  |

| 010000                              | +10               |  |  |

| 010001                              | +9                |  |  |

| 010010                              | +8                |  |  |

| 010011                              | +7                |  |  |

| 010100                              | +6                |  |  |

| 010101                              | +5                |  |  |

| 010110                              | +4                |  |  |

| 010111                              | +3                |  |  |

| 011000                              | +2                |  |  |

| 011001                              | +1                |  |  |

| 011010                              | 0                 |  |  |

| 011011                              | -1                |  |  |

| 011100                              | -2                |  |  |

| 011101                              | -3                |  |  |

| 011110                              | -4                |  |  |

| 011111                              | -5                |  |  |

| 100000                              | -6                |  |  |

| 100001                              | -7                |  |  |

| 100010                              | -8                |  |  |

| 100011 to 111111                    | -9                |  |  |

#### **SPI READ**

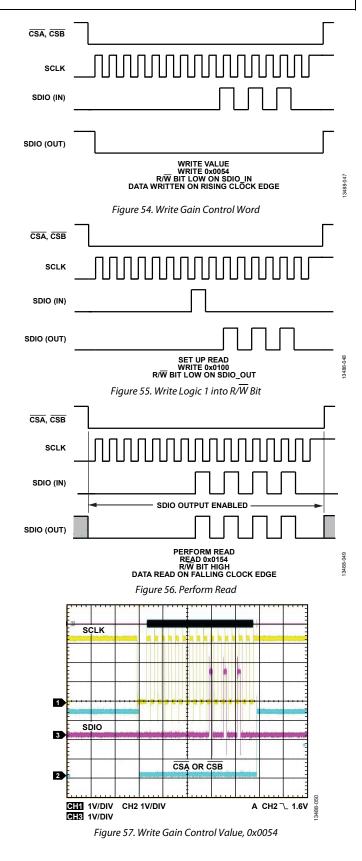

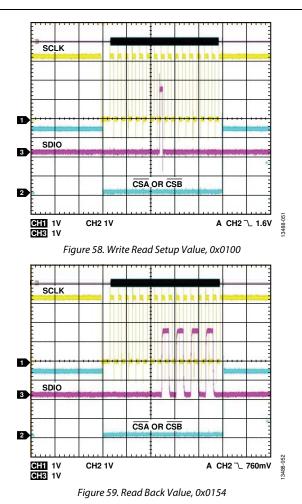

The ADL5205 can be read back only in the serial mode, during a read cycle (from  $\overline{CSA}/\overline{CSB}$  low to  $\overline{CSA}/\overline{CSB}$  high) after the  $R/\overline{W}$  bit is set high in the previous cycle. During the read cycle, data changes at each rising edge of SCLK, and can be latched using the falling edge of SCLK. There is no continual read operation. A logic high (1) must be written into the  $R/\overline{W}$  bit to enable the subsequent read cycle. The sequence for reading back is shown in Figure 54 to Figure 57, showing the operation of the input and output functions of the SDIO pin. The actual waveforms during the readback process are shown in Figure 57 to Figure 59. SDIO is enabled as an output only during the read cycle in Figure 57.

#### **ADC INTERFACING**

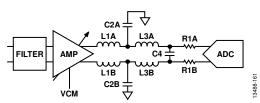

A typical data acquisition system using the ADL5205 together with an antialiasing filter and an ADC is shown in Figure 60. The main role of the filter after the amplifier is for attenuating the broadband noise and out-of-band harmonics generated by the amplifier. Component values for a 500 MHz acquisition bandwidth are listed in Table 10. Without this filter, the out-ofband noise and distortion components alias back into the Nyquist band, resulting in a reduction of signal-to-noise ratio. The design of the filter preceding the ADL5205 amplifier is more specific to the system rejection requirements for the acquisition system,

*Figure 60. ADC Interface (One of Two Channels Shown)*

#### Table 10. Component Values for a 500 MHz Acquisition System

| Table 10. Component Values for a 500 Mill2 Acquisition System |             |                                                  |

|---------------------------------------------------------------|-------------|--------------------------------------------------|

| Component                                                     | Value       | Description/Comments                             |

| Amplifier                                                     | 1/2 ADL5205 | One channel                                      |

| L1A, L1B                                                      | 22 nH       | Q ≥ 50 at 500 MHz                                |

| C2A, C2B                                                      | 6.8 pF      | Final value depends on PCB<br>parasitics         |

| L3A, L3B                                                      | 22 nH       | Q ≥ 50 at 500 MHz                                |

| C4                                                            | 1.5 pF      | Final value depends on PCB<br>parasitics         |

| R1A, R1B                                                      | 10 Ω        | Not applicable                                   |

| ADC                                                           | 1⁄2 AD9680  | One channel, input impedance set to 100 $\Omega$ |

#### **NOISE FIGURE vs. GAIN SETTING**

Because of the architecture of the ADL5205, the noise figure does not degrade significantly for the first 12 dB of gain reduction from the maximum gain setting. The noise figure increases by 2 dB only during the first 12 dB of gain reduction, after which it resumes the 1 dB degradation for each dB of gain reduction.

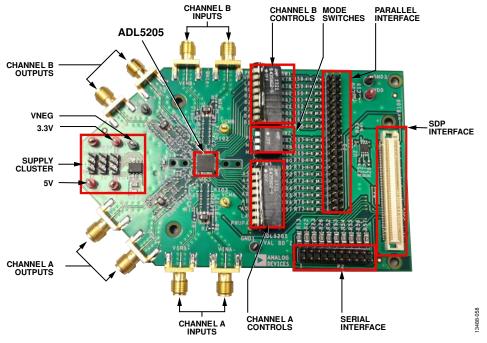

### EVALUATION BOARD overview

The ADL5205-EVALZ evaluation board allows the manual control of the ADL5205 device through the serial and the parallel interface ports, as well as the control of the device through the USB port on a Microsoft<sup>®</sup> Windows<sup>®</sup> PC via the system demonstration platform (SDP) interface board. A 3.3 V low dropout (LDO) voltage regulator supplies the logic circuits when the device is running on a 5 V supply.

On-board baluns convert single-ended input signals to differential form for input to the device and convert the differential output signals of the device to single-ended form for output. To bypass these baluns, rearrange the 0  $\Omega$  resistors on the board as described in the Signal Inputs and Outputs section.

The ADL5205-EVALZ provides all of the support circuitry required to operate the ADL5205 in its various modes and configurations. Figure 62 shows the typical bench setup used to evaluate the performance of the ADL5205.

#### POWER SUPPLY INTERFACE

The ADL5205-EVALZ evaluation board requires either a 3.3 V or 5 V power supply, and an optional negative supply to pull down the output common-mode dc level to match the ADCs that require a lower common-mode level. If an external 3.3 V supply is used, connect it to the test point labeled 3P3V. If a 5 V supply is used, connect it to the test point labeled 5V. Similarly, if an external negative supply is used, connect it to the VNEG test point shown in Figure 62.

Figure 62. ADL5205-EVALZ Evaluation Board

The power supply jumper configurations (S1 to S3) required for selecting the evaluation board analog supply (V<sub>CC</sub>) and digital supply (V<sub>DD</sub>) from the external 3.3 V or 5 V power supply are shown in Table 11. When using a 5 V supply, enable the on-board 3.3 V voltage regulator and select it using the S3 and S2 jumpers, respectively, to provide digital supply (V<sub>DD</sub>) to the pull-up resistors for logic signals.

#### Table 11. Power Supply Selection Jumpers

|        |                            | Supply Selection |                |

|--------|----------------------------|------------------|----------------|

| Jumper | Function                   | $V_{cc} = 3.3 V$ | $V_{cc} = 5 V$ |

| S1     | V <sub>CC</sub> selection  | 3P3V             | 5V             |

| S2     | V <sub>DD</sub> selection  | 3P3V             | VREG           |

| S3     | V <sub>DD</sub> LDO enable | AGND             | 5V             |

#### SIGNAL INPUTS AND OUTPUTS

Signal inputs and outputs for each channel come through a pair of SMA connectors. In the default configuration, on-board baluns convert single-ended signals from VINA- and VINBinto differential signals to the device. Similarly, differential output signals from the device are converted through the on-board baluns into single-ended form to the VOUTA+ and VOUTB+ connectors.

#### **MANUAL CONTROLS**

Three sets of switches provide the manual control of the states of the device. Their functions are listed in Table 12. When the individual switch is in the up position, the signal controlled by the switch is set to logic high.

#### **Table 12. Switch Block Functions**

| Switch Block | Function                            | Device<br>Pin No. |

|--------------|-------------------------------------|-------------------|

| SW1          | Channel B control (eight positions) |                   |

| Position 1   | PWUPB                               | 17                |

| Position 2   | LATCHB                              | 14                |

| Position 3   | во                                  | 13                |

| Position 4   | B1                                  | 12                |

| Position 5   | B2                                  | 11                |

| Position 6   | B3                                  | 10                |

| Position 7   | B4                                  | 9                 |

| Position 8   | B5                                  | 8                 |

| SW2          | Mode control (three positions)      |                   |

| Position 1   | Power mode (PM)                     | 6                 |

| Position 2   | MODE0 (M0)                          | 5                 |

| Position 3   | MODE1 (M1)                          | 4                 |

| SW3          | Channel A control (eight positions) |                   |

| Position 1   | A5                                  | 3                 |

| Position 2   | A4                                  | 2                 |

| Position 3   | A3                                  | 1                 |

| Position 4   | A2                                  | 40                |

| Position 5   | A1                                  | 39                |

| Position 6   | A0                                  | 38                |

| Position 7   | LATCHA                              | 37                |

| Position 8   | PWUPA                               | 34                |

#### **Mode Switches**

When the power mode (PM) switch is up (logic high or Logic 1), the device is in low power mode. When the switch is down (logic low or Logic 0), the device is in high performance mode.

MODE1 and MODE0 (labeled M1 and M0 on the PCB) select one of three interface modes for the device (parallel, serial/SPI, or up/down mode), as shown in Table 13. There is no functional difference between the mode switch settings of 10 and 11.

#### Table 13. Mode Switch Settings

| MODE1, MODE0 | Interface    |

|--------------|--------------|

| 00           | Parallel     |

| 01           | Serial (SPI) |

| 10           | Up/down      |

| 11           | Up/down      |

#### **Channel Control Switches**

The channel control switches include PWUPA, LATCHA, and A5 to A0 for Channel A and PWUPB, LATCHB, and B5 to B0 for Channel B.

PWUPA and PWUPB are the up positions (logic high) that turn on their respective channels. When PM is set to logic low (high performance mode), the total current consumption increases by approximately 81 mA (that is, one half of the difference between the enabled current of 175 mA and the disabled current of 14 mA) when each channel is enabled. When the PM is set to logic high (low power mode), the total current consumption increases by approximately 61 mA (that is, one half of the difference between the enabled current of 135 mA and the disabled current of 14 mA) when each channel is enabled.

The LATCHA and LATCHB switches are used with the gain control input bits (A5 to A0 and B5 to B0) to control the corresponding channel voltage gain. When these switches are in the down (logic low) position, the gain changes with the position of the gain control switches. When these switches are in the up position, the last gain setting is latched into the corresponding channel of the ADL5205, and the gain stops changing.

For Bits[A5:A0] and Bits[B5:B0], the following equation determines the voltage gain of each channel of the ADL5205:

Gain = 26 - [A5:A0] dB

where [*A5*:*A0*] is the value representing the binary string formed by Bits[*A5*:*A0*] from 0 to 35. When this value exceeds 35, the gain is set to minimum (–9 dB). The voltage gain for Channel B is changed by Bits[B5:B0] in the same manner.

#### PARALLEL INTERFACE

The functions of Parallel Interface Connector P3 are identical to those of the switches in the switch block. The pinout of the Parallel Interface Connector P3 is listed in Table 14. Logic levels on the P3 pins override the corresponding switch setting. As a result, the switches for PWUPA and PWUPB must be in the up position when using the parallel interface to control the device.

#### Table 14. Parallel Interface Pinout (P3)

| Pin Number | Function        |

|------------|-----------------|

| 1          | PWUPB           |

| 2          | AGND            |

| 3          | LATCHB          |

| 4          | AGND            |

| 5          | ВО              |

| 6          | AGND            |

| 7          | B1              |

| 8          | AGND            |

| 9          | B2              |

| 10         | AGND            |

| 11         | B3              |

| 12         | AGND            |

| 13         | B4              |

| 14         | AGND            |

| 15         | B5              |

| 16         | AGND            |

| 17         | V <sub>DD</sub> |

| 18         | AGND            |

| 19         | Power mode (PM) |

| 20         | AGND            |

| 21         | MODE0           |

| 22         | AGND            |

| 23         | MODE1           |

| 24         | AGND            |

| 25         | A5              |

| 26         | AGND            |

| 27         | A4              |

| 28         | AGND            |

| 29         | A3              |

| 30         | AGND            |

| 31         | A2              |

| 32         | AGND            |

| 33         | A1              |

| 34         | AGND            |

| 35         | A0              |

| 36         | AGND            |

| 37         | LATCHA          |

| 38         | AGND            |

| 39         | PWUPA           |

| 40         | AGND            |

#### SERIAL INTERFACE

When the mode switches are in the 01 position, the ADL5205 operates in the serial/SPI mode. The pins that are relevant in the serial/SPI mode are brought out to Serial Interface Connector P2. The pinout for Serial Interface Connector P2 is listed in Table 15. Note that only four pins (plus AGND) are used for the SPI, and they include the following:

- CSA and CSB are the active low serial port enable pins for Channel A and Channel B, respectively.

- SDIO is the serial data input and output line. SDIO is a bidirectional pin.

- SCLK is the serial clock pin.

For detailed operations and timing diagrams of the serial port interface, see the Serial Peripheral Interface (SPI) section. These signals operate at 3.3 V logic levels.

The  $\overline{\text{CSA}}$  and  $\overline{\text{CSB}}$  lines can be tied together to program both channels at the same time.

| Table 15. Serial Interface Connector (P2) Pinout |                |  |

|--------------------------------------------------|----------------|--|

| Pin Number                                       | Function       |  |

| 1                                                | PWUPA          |  |

| 2                                                | Not applicable |  |

| 3                                                | FA_A           |  |

| 4                                                | Not applicable |  |

| 5                                                | CSA            |  |

| 6                                                | Not applicable |  |

| 7                                                | PM             |  |

| 8                                                | Not applicable |  |

| 9                                                | SDIO           |  |

| 10                                               | Not applicable |  |

| 11                                               | SCLK           |  |

| 12                                               | Not applicable |  |

| 13                                               | CSB            |  |

| 14                                               | Not applicable |  |

| 15                                               | FA_B           |  |

| 16                                               | Not applicable |  |

| 17                                               | PWUPB          |  |

| 18                                               | Not applicable |  |

| 19                                               | AGND           |  |

| 20                                               | Not applicable |  |

#### Table 15. Serial Interface Connector (P2) Pinout