# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **Thermal Monitor and Fan Speed (RPM) Controller**

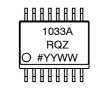

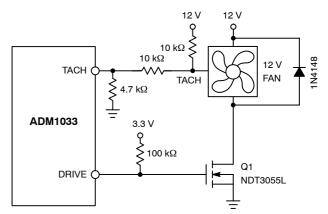

The ADM1033 is a one channel remote- and local-temperature sensor and fan controller. The remote channel monitors the temperature of the remote thermal diode, which may be discrete 2N3904/6s or may be located on a microprocessor die. The device also monitors its own ambient temperature.

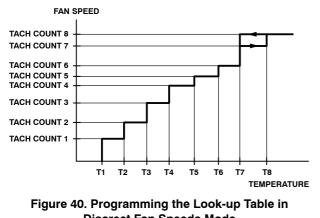

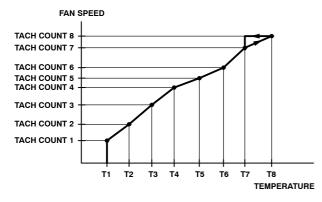

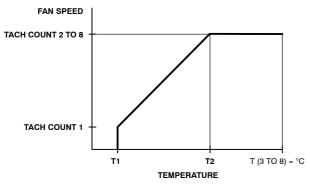

The ADM1033 can monitor and control the speed of cooling fan. The user can program a target fan speed, or else use the look-up table to input a temperature-to-fan speed profile. The look-up table can be configured to run the fans at discrete speeds (discrete mode) or to ramp the fan speed with temperature (linear mode).

The ADM1033 communicates over a 2-wire SMBus 2.0 interface. An 8-level LOCATION input allows the user to choose between SMBus 1.1 and SMBus 2.0. An ALERT output indicates error conditions. The THERM I/O signals overtemperature as an output and times THERM assertions as an input. Pin 8 can be configured as a reference for the THERM (PROCHOT) input.

#### **Features**

- 1 Local and Remote Temperature Channels

- ±1°C Accuracy on Local and Remote Channels

- Automatic Remote Temperature Channel, Up to 1 k $\Omega$

- Fast (Up to 64 Measurements per Second)

- SMBus 2.0, 1.1, and 1.0 Compliant

- SMBus Address Input/LOCATION Input to UDID

- Programmable Over/Undertemperature Limits

- Programmable Fault Queue

- **SMBusALERT** Output

- Fail-Safe Overtemperature Comparator Output

- Fan Speed (RPM) Controller

- Look-up Table for Temperature-to-Fan Speed Control

- Linear and Discrete Options for Look-up Table

- FAN FAULT Output

- THERM Input, Used to Time PROCHOT Assertions

- REF Input, Used as Reference for THERM (PROCHOT)

- 3.0 V to 5.5 V Supply

- Small 16-lead QSOP Package

- This is a Pb-Free Device\*

#### Applications

- Desktop and Notebook PCs

- Embedded Systems

- Telecommunications Equipment

- LCD Projectors

### **ON Semiconductor®**

http://onsemi.com

**CASE 492**

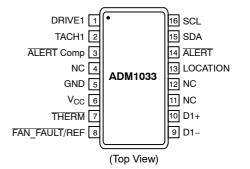

#### **PIN ASSIGNMENT**

1033ARQZ = Specific Device Code #

= Pb-Free Package

YY

ww

= Date Code = Work Week

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 34 of this data sheet.

\* For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

Figure 1. Functional Block Diagram

| Table 1. ABSOLUTE M | AXIMUM RATINGS |

|---------------------|----------------|

|---------------------|----------------|

| Parameter                                                        | Rating                        | Unit |

|------------------------------------------------------------------|-------------------------------|------|

| Positive Supply Voltage (V <sub>CC</sub> )                       | -0.3, +6.5                    | V    |

| Voltage on Any Input or Output Pin except FAN_FAULT and LOCATION | –0.3 to V <sub>DD</sub> + 6.5 | V    |

| Voltage on FAN_FAULT (Note 1)                                    | V <sub>CC</sub>               |      |

| Voltage on LOCATION                                              | V <sub>CC</sub> + 0.3         | V    |

| Input Current at Any Pin                                         | ±20                           | mA   |

| Maximum Junction Temperature (T <sub>J MAX</sub> )               | 150                           | °C   |

| Storage Temperature Range                                        | -65 to +150                   | °C   |

| Lead Temperature, Soldering (10 s)                               | 300                           | °C   |

| IR Reflow Peak Temperature                                       | 220                           | ٥°C  |

| ESD Rating – All Pins                                            | 1500                          | V    |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

1. During powerup the voltage on  $\overline{FAN}_{FAULT}$  should not be higher than  $V_{CC}$ .

NOTE: This device is ESD sensitive. Use standard ESD precautions when handling.

#### Table 2. THERMAL CHARACTERISTICS

| Package Type         | θ <sub>JA</sub> | θ <sub>JC</sub> | Unit |

|----------------------|-----------------|-----------------|------|

| 16-lead QSOP Package | 150             | 39              | °C/W |

#### Table 3. PIN ASSIGNMENT

| Mnemonic          | Description                                                                                                                                                                                               |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DRIVE1            | DRIVE1 Pin Drives Fan 1. Open-drain output. Requires a pullup resistor.                                                                                                                                   |

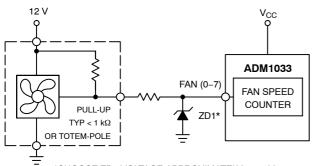

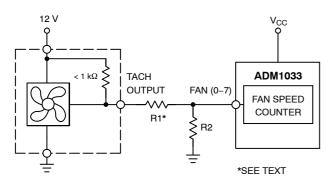

| TACH1             | Fan 1 Fan Speed Measurement Input. Connects to the fan's TACH output to measure the fan speed.                                                                                                            |

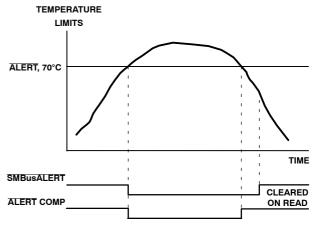

| ALERT Comp        | Open-Drain Active Low Output. Assets low whenever a measurement goes outside its programmed limits if not masked. Automatically goes high again when the measured parameter falls back within its limits. |

| NC                | No Connect.                                                                                                                                                                                               |

| GND               | Ground for Analog and Digital Circuitry.                                                                                                                                                                  |

| VCC               | Power. Can be powered by 3.3 V standby power if monitoring in low power states is required.                                                                                                               |

| THERM             | Can be configured as an overtemperature interrupt output, or as an input (to monitor PROCHOT output of an INTEL CPU). A timer measures assertion times on the THERM pin (either input or output).         |

| FAN_FAULT/R<br>EF | FAN_FAULT: Open-Drain Output. Asserted low when one or both fans stall. Requires a pullup resistor to V <sub>CC</sub> . REF: Analog Input Reference for the THERM Input.                                  |

| D1-               | Cathode Connection for the First Thermal Diode or Diode-Connected Transistor.                                                                                                                             |

| D1+               | Anode Connection for the First Thermal Diode or Diode-Connected Transistor.                                                                                                                               |

| NC                | No Connect.                                                                                                                                                                                               |

| NC                | No Connect.                                                                                                                                                                                               |

| LOCATION          | 8-level Analog Input. Used to determine the correct SMBus version and the SMBus address (in fixed and discoverable mode) and to set the LLL bits in the UDID (in ARP-capable mode).                       |

| ALERT             | Open-Drain Output. SMBusALERT pin. Alerts the system in the case of out-of-limit events, such as over temperature. Can be configured as sticky SMBus mode or comparator mode.                             |

| SDA               | Serial Bus Bidirectional Data. Connects to the SMBus master's data line. Requires pullup resistor if not provided elsewhere in the system.                                                                |

| SCL               | Serial SMBus Clock Input. Connects to the SMBus master's clock line. Requires pullup resistor if not<br>already provided in the system.                                                                   |

|                   | DRIVE1<br>TACH1<br>ALERT Comp<br>NC<br>GND<br>VCC<br>THERM<br>FAN_FAULT/R<br>EF<br>D1-<br>D1+<br>NC<br>NC<br>LOCATION<br>ALERT<br>SDA                                                                     |

| Table 4. ELECTRICAL CHARACTERISTICS ( | = $T_{MIN}$ to $T_{MAX}$ , $V_{CC}$ = $V_{MIN}$ to $V_{MAX}$ , unle | ess otherwise noted.) (Note 1) |

|---------------------------------------|---------------------------------------------------------------------|--------------------------------|

|---------------------------------------|---------------------------------------------------------------------|--------------------------------|

| Parameter                                          | Test Conditions/Comments                                                                                                                                                                                                                                                                 | Min            | Тур               | Max                   | Unit   |

|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-------------------|-----------------------|--------|

| Power Supply                                       |                                                                                                                                                                                                                                                                                          |                |                   |                       |        |

| Supply Voltage, V <sub>CC</sub> (Note 2)           |                                                                                                                                                                                                                                                                                          | 3.0            | 3.30              | 3.6                   | V      |

| Supply Current, I <sub>CC</sub>                    | Interface inactive, ADC Active                                                                                                                                                                                                                                                           | -              | -                 | 3.0                   | mA     |

|                                                    | Standby Mode                                                                                                                                                                                                                                                                             | -              | -                 | 900                   | μA     |

| Undervoltage Lockout Threshold                     |                                                                                                                                                                                                                                                                                          | -              | 2.5               | -                     | V      |

| Power-On Reset Threshold                           |                                                                                                                                                                                                                                                                                          | 1.0            | -                 | 2.4                   | V      |

| Temperature-to-Digital Converter                   |                                                                                                                                                                                                                                                                                          |                |                   |                       |        |

| Internal Sensor Accuracy                           | $20^{\circ}C \le T_A \le 60^{\circ}C$<br>- $40^{\circ}C \le T_A \le +100^{\circ}C$                                                                                                                                                                                                       | _<br>_4.0      | ±1.0<br>-         | ±2.0<br>+2.0          | °C     |

| Resolution                                         |                                                                                                                                                                                                                                                                                          | -              | 0.03125           | -                     | °C     |

| External Diode Sensor Accuracy                     | $\begin{array}{l} -40^{\circ}C \leq T_{D} \leq +100^{\circ}C; \ T_{A} = +40^{\circ}C \\ -40^{\circ}C \leq T_{D} \leq +100^{\circ}C; \ +20^{\circ}C \leq T_{A} \leq +60^{\circ}C \\ -40^{\circ}C \leq T_{D} \leq +100^{\circ}C; \ -40^{\circ}C \leq T_{A} \leq +100^{\circ}C \end{array}$ | -<br>-<br>-3.0 | ±0.5<br>±1.0<br>- | ±1.0<br>±1.25<br>+2.0 | °C     |

| Resolution                                         |                                                                                                                                                                                                                                                                                          | -              | 0.03125           | -                     | °C     |

| Remote Sensor Source Current                       | High Level<br>Mid Level<br>Low Level                                                                                                                                                                                                                                                     | -<br>-<br>-    | 85<br>34<br>5.0   | -<br>-<br>-           | μΑ     |

| Series Resistance Cancellation                     |                                                                                                                                                                                                                                                                                          | _              | -                 | 1000                  | Ω      |

| Power Supply Sensitivity                           |                                                                                                                                                                                                                                                                                          | _              | ±1.0              | _                     | %/V    |

| Conversion Time (Local Temperature)                | Averaging Enabled                                                                                                                                                                                                                                                                        | -              | 11                | -                     | ms     |

| Conversion Time (Remote Temperature)               | Averaging Enabled                                                                                                                                                                                                                                                                        | _              | 32                | _                     | ms     |

| Total Conversion Time                              | Averaging Enabled                                                                                                                                                                                                                                                                        | _              | 43                | _                     | ms     |

| Open-Drain Digital Outputs (ALERT, TH              | IERM, FAN_FAULT, DRIVE1, DRIVE2) (Note 3)                                                                                                                                                                                                                                                | •              |                   | •                     |        |

| Output Low Voltage, V <sub>OL</sub>                | I <sub>OUT</sub> = -6.0 mA; V <sub>CC</sub> = +3.0 V                                                                                                                                                                                                                                     | _              | _                 | 0.4                   | V      |

| High Level Output Leakage Current, I <sub>OH</sub> | V <sub>OUT</sub> = V <sub>CC</sub> ; V <sub>CC</sub> = 3.0 V                                                                                                                                                                                                                             | -              | 0.1               | 1.0                   | μA     |

| Digital Input Leakage Current (TACH1,              | TACH2)                                                                                                                                                                                                                                                                                   | •              |                   | •                     |        |

| Input High Current, I <sub>IH</sub>                | $-V_{IN} = V_{CC}$                                                                                                                                                                                                                                                                       | -1.0           | -                 | -                     | μA     |

| Input Low Current, I <sub>IL</sub>                 | V <sub>IN</sub> = 0                                                                                                                                                                                                                                                                      | -              | -                 | 1.0                   | μA     |

| Input Capacitance, C <sub>IN</sub>                 |                                                                                                                                                                                                                                                                                          | -              | 7.0               | -                     | pF     |

| Digital Input Logic Levels (TACH1, TAC             | H2)                                                                                                                                                                                                                                                                                      | •              |                   |                       |        |

| Input High Voltage, V <sub>IH</sub>                |                                                                                                                                                                                                                                                                                          | 2.0            | -                 | 5.5                   | V      |

| Input Low Voltage, V <sub>IL</sub>                 |                                                                                                                                                                                                                                                                                          | -0.3           | -                 | +0.8                  | V      |

| Hysteresis                                         |                                                                                                                                                                                                                                                                                          | _              | 500               | _                     | mV p-p |

| Open-Drain Serial Data Bus Output (SD              | )A)                                                                                                                                                                                                                                                                                      |                |                   |                       |        |

| Output Low Voltage, V <sub>OL</sub>                | I <sub>OUT</sub> = -6.0 mA; V <sub>CC</sub>                                                                                                                                                                                                                                              | -              | -                 | 0.4                   | V      |

| High Level Output Leakage Current, I <sub>OH</sub> | V <sub>OUT</sub> = V <sub>CC</sub>                                                                                                                                                                                                                                                       | -              | 0.1               | 1.0                   | μA     |

| Serial Bus Digital Inputs (SCL, SDA)               |                                                                                                                                                                                                                                                                                          |                |                   |                       |        |

| Input High Voltage, V <sub>IH</sub>                |                                                                                                                                                                                                                                                                                          | 2.1            | -                 | -                     | V      |

| Input Low Voltage, V <sub>IL</sub>                 |                                                                                                                                                                                                                                                                                          | -              | -                 | 0.8                   | V      |

| Hysteresis                                         |                                                                                                                                                                                                                                                                                          | -              | 500               | _                     | mV     |

| Analog Inputs (Location, REF)                      |                                                                                                                                                                                                                                                                                          |                |                   |                       |        |

| Input Resistance                                   |                                                                                                                                                                                                                                                                                          | 80             | 125               | 160                   | kΩ     |

| Tachometer Accuracy                                | ·                                                                                                                                                                                                                                                                                        | -              |                   | -                     |        |

| Fan Speed Measurement Accuracy                     |                                                                                                                                                                                                                                                                                          | -              | -                 | ±4.0                  | %      |

| Table 4. ELECTRICAL CHARACTERISTICS | $A = T_{MIN}$ to $T_{MAX}$ , $V_{CC} = V_{MIN}$ to $V_{MAX}$ , unless otherwise noted | .) (Note 1) |

|-------------------------------------|---------------------------------------------------------------------------------------|-------------|

|-------------------------------------|---------------------------------------------------------------------------------------|-------------|

| Parameter                                      | <b>Test Conditions/Comments</b> | Min | Тур           | Max  | Unit |

|------------------------------------------------|---------------------------------|-----|---------------|------|------|

| AGTL + INPUT (THERM)                           |                                 |     |               |      |      |

| Input High Level                               |                                 | -   | 0.75 x<br>REF | -    | V    |

| Input Low Level                                |                                 | -   | -             | 0.4  | V    |

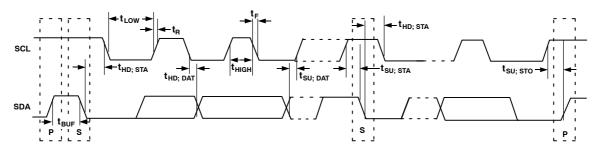

| SERIAL BUS TIMING (Note 4)                     |                                 |     |               |      |      |

| Clock Frequency, f <sub>SCLK</sub>             | See Figure 2 for All Parameters | -   | _             | 400  | kHz  |

| Glitch Immunity, t <sub>SW</sub>               |                                 | -   | 50            | -    | ns   |

| Bus Free Time, t <sub>BUF</sub>                |                                 | 1.3 | -             | -    | μs   |

| Start Setup Time, t <sub>SU:STA</sub>          |                                 | 0.6 | -             | -    | μs   |

| Start Hold Time, t <sub>HD:STA</sub>           |                                 | 0.6 | -             | -    | μs   |

| Stop Condition Setup Time t <sub>SU:STO</sub>  |                                 | 0.6 | -             | -    | μs   |

| SCL Low Time, t <sub>LOW</sub>                 |                                 | 1.3 | -             | -    | μs   |

| SCL High Time, t <sub>HIGH</sub>               |                                 | 0.6 | -             | -    | μs   |

| SCL, SDA Rise Time, t <sub>r</sub>             |                                 | _   | _             | 1000 | ns   |

| SCL, SDA Fall Time, t <sub>f</sub>             |                                 | -   | -             | 300  | ns   |

| Data Setup Time, t <sub>SU:DAT</sub>           |                                 | 100 | -             | -    | ns   |

| Detect Clock Low Timeout, t <sub>TIMEOUT</sub> | (Note 5)                        | 25  | -             | 35   | ms   |

Typicals are at T<sub>A</sub> = 25°C and represent most likely parametric norm. Standby current typ. is measured with V<sub>CC</sub> = 3.3 V. Timing specifications are tested at logic levels of V<sub>IL</sub> = 0.8 V for a falling edge and V<sub>IH</sub> = 2.1 V for a rising edge.

Operation at 5.5 V is guaranteed by design, not production tested.

Recommend use of 100 kΩ pullup resistors for all open-drain outputs from the ADM1033.

Guaranteed by design, not production tested.

SMBus timeout disabled by default. See the SMBus section for more information.

Figure 2. Serial Bus Timing Diagram

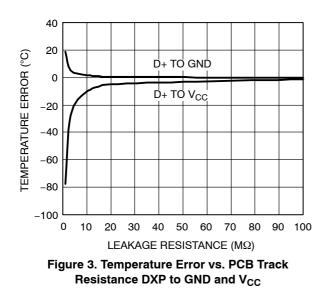

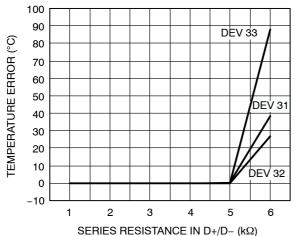

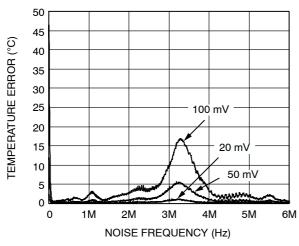

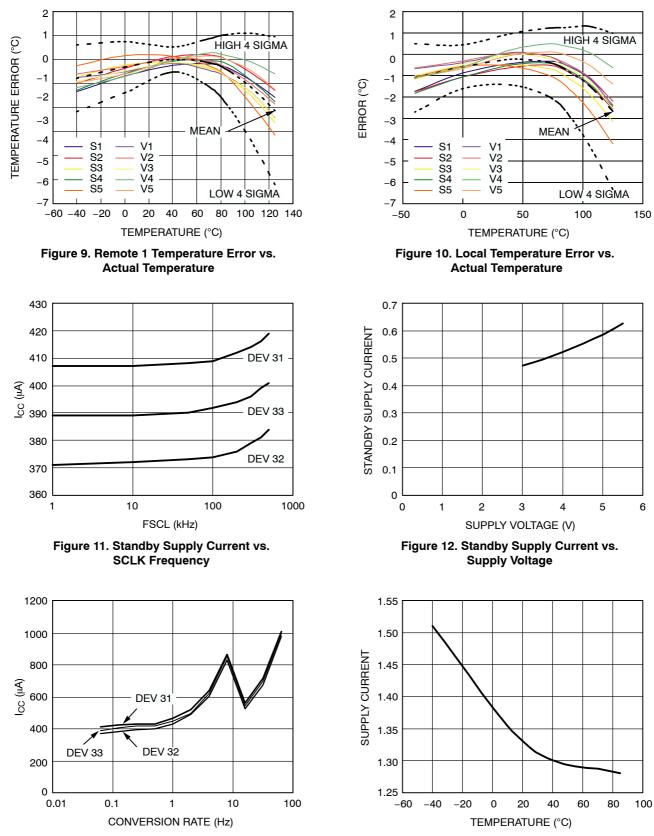

#### **TYPICAL PERFORMANCE CHARACTERISTICS**

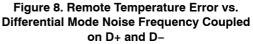

Figure 5. Remote Temperature Error vs. Series Resistance on D+ and D-

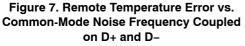

Figure 4. Remote Temperature Error vs. D+, D- Capacitance

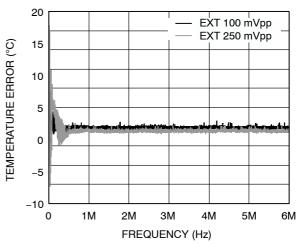

Figure 6. Remote Temperature Error vs. Power Supply Noise Frequency

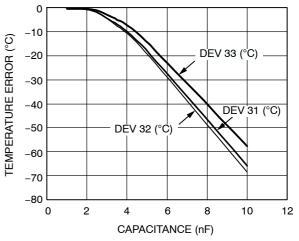

#### TYPICAL PERFORMANCE CHARACTERISTICS (Cont'd)

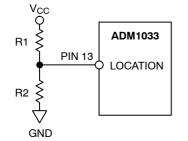

Figure 14. Supply Current vs. ADM1033 Temperature

#### **Functional Description**

The ADM1033 is a local- and remote-temperature monitor and fan controller for use in a variety of applications, including microprocessor-based systems. The device accurately monitors remote and ambient temperature and uses that information to quietly control the speed of a cooling fan. Whenever a fan stalls, the device asserts a FAN FAULT output.

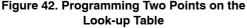

The ADM1033 features a THERM I/O. As an input, this measures assertions on the THERM pin. As an output, it asserts a low signal to indicate when the measured temperature exceeds the programmed THERM temperature. The ADM1033 communicates over an SMBus 2.0 interface. Its LOCATION input determines which version of SMBus to use, as well as the SMBus address (in fixed and discoverable mode) and the LOCATION bits in the UDID (in ARP-capable mode).

#### **Internal Registers**

Table 5 gives a brief description of the ADM1033's principal internal registers. For more detailed information on the function of each register, refer to Table 35.

#### **Serial Bus Interface**

The ADM1033 communicates with the master via the 2-wire SMBus 2.0 interface. It supports two versions of SMBus 2.0, determined by the value of the LOCATION input's resistors.

The first version is fully ARP-capable. This means that it supports address resolution protocol (ARP), allowing the master to dynamically address the device on powerup. It responds to ARP commands such as "Prepare to ARP."

The second SMBus version, fixed and discoverable, is backwards compatible with SMBus 1.0 and 1.1. In this mode, the ADM1033 powers up with a fixed address, which is determined by the state of the LOCATION pin on powerup.

# NOTE: When using the ADM1033, Addresses 0xC2 and 0xCA should not be used by any other device on the bus.

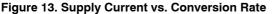

#### Location Input

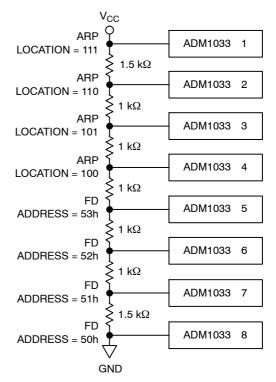

The LOCATION input is a resistor divider input. It has multiple functions and can specify the SMBus version (in fixed and discoverable or ARP-capable modes); the SMBus address (in fixed and discoverable mode); and the LLL bits (in UDID in ARP-capable mode).

#### Figure 15. Bootstrapping the LOCATION Input

The voltage of this 8-level input is set by a potential divider. The voltage on LOCATION is sampled on powerup

and digitized by the on-chip ADC to determine the LOCATION input value. Because the LOCATION input is sampled only at powerup, changes made while power is applied have no effect.

#### SMBus 2.0 ARP-Capable Mode

In ARP-capable mode, the ADM1033 supports features such as address resolution protocol (ARP) and unique device identifier (UDID). The UDID is a 128-bit message that describes the ADM1033's capabilities to the master. The UDID also includes a vendor specific ID for functionally equivalent devices.

#### Figure 16. Setting Up Multiple ADM1033 Addresses in SMBus 2.0 ARP-capable Mode

In SMBus 2.0 mode, this vendor specific ID is generated by an on-chip random number generator. This should enable two adjacent ADM1033s in the same system to powerup with a different vendor specific ID, allowing the master to identify the two separate ADM1033's and assign a different address to each.

The state of the LOCATION input on powerup is also reflected in the UDID. This is useful when there is more than one ADM1033 in the system, so the master knows which one it is communicating with. The complete UDID is listed in Table 7.

The SMBus 2.0 master issues both general and directed ARP commands. A general command is directed at all ARP devices. A directed command is targeted at a single device once an address has been established. The PEC byte must be used for ARP commands. (Refer to the Packet Error Checking (PEC) section.)

The ADM1033 responds to the following commands:

- Prepare to ARP (General)

- Reset Device (General and Directed)

- Get UDID (General and Directed)

- Assign Address (General)

#### Table 5. INTERNAL REGISTER DESCRIPTIONS

| Register                             | Description                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Configuration                        | Provides control and configuration of various functions on the device.                                                                                                                                                                                                                                                                                           |

| Conversion Rate                      | Determines the number of measurements per second completed by the ADM1033.                                                                                                                                                                                                                                                                                       |

| Address Pointer                      | Contains the address that selects one of the other internal registers. When writing to the ADM1033, the first byte of data is always a register address, written to the address pointer register.                                                                                                                                                                |

| Status                               | Provides the status of each limit comparison.                                                                                                                                                                                                                                                                                                                    |

| Interrupt Mask                       | Allows the option to mask ALERTs due to particular out-of-limit conditions.                                                                                                                                                                                                                                                                                      |

| Value and Limit                      | Stores the results of temperature and fan speed measurements, along with their limit values.                                                                                                                                                                                                                                                                     |

| Offset                               | Allows the local and remote temperature channel readings to be offset by a twos complement value written to them. These values are automatically added to the temperature values (or subtracted from them if negative). This allows the systems designer to optimize the system if required, by adding or subtracting up to 15.875°C from a temperature reading. |

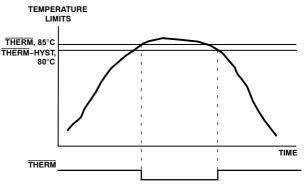

| THERM Limit and Hysteresis           | Contains the temperature value at which THERM is asserted and indicates the level of hysteresis.                                                                                                                                                                                                                                                                 |

| Look-up Table                        | Used to program the look-up table for the fan speed-to-temperature profile.                                                                                                                                                                                                                                                                                      |

| THERM % On-time and<br>THERM % Limit | Reflects the state of the THERM input and monitors the duration of the assertion time of the signal as a percentage of a time window. The user can program the length of the time window.                                                                                                                                                                        |

#### Table 6. RESISTOR RATIOS FOR SETTING LOCATION BITS

|                          |               |             |                     |         | SMBus Ver |               |          |

|--------------------------|---------------|-------------|---------------------|---------|-----------|---------------|----------|

| Ideal Ratio R2/(R1 + R2) | R1 k $\Omega$ | <b>R2</b> Ω | Actual R2/(R1 + R2) | Error % | (Note 1)  | SMBus Address | UDID LLL |

| N/A                      | 0             | O/C         | 1                   | 0       | ARP       | N/A           | 111      |

| 0.8125                   | 18            | 82          | 0.82                | +0.75   | ARP       | N/A           | 110      |

| 0.6875                   | 22            | 47          | 0.6812              | -0.63   | ARP       | N/A           | 101      |

| 0.5625                   | 12            | 15          | 0.5556              | -0.69   | ARP       | N/A           | 100      |

| 0.4375                   | 15            | 12          | 0.4444              | +0.69   | FD        | 0x53          | N/A      |

| 0.3125                   | 47            | 22          | 0.3188              | +0.63   | FD        | 0x52          | N/A      |

| 0.1875                   | 82            | 18          | 0.18                | -0.75   | FD        | 0x51          | N/A      |

| N/A                      | O/C           | 0           | 0                   | 0       | FD        | 0x50          | N/A      |

1. ARP denotes ARP-capable mode, FD denotes fixed and discoverable mode.

#### Table 7. UDID VALUES

| Bit No.   | Name                | Function                                                                                                                                                  | Value                                        |

|-----------|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| <127:120> | Device Capabilities | Describes the ADM1033's capabilities (for instance, that it supports PEC and uses a random number address device).                                        | 11000001                                     |

| <119:112> | Version/Revision    | UDID version number (Version 1) and silicon revision identification                                                                                       | 00001010                                     |

| <111:96>  | Vendor ID           | Analog Devices vendor ID number, as assigned by the SBS<br>Implementer's Forum or the PCI SIG.                                                            | 00010001<br>11010100                         |

| <95:80>   | Device ID           | Device ID.                                                                                                                                                | 00010000<br>00110100                         |

| <79:64>   | Interface           | Identifies the protocol layer interfaces supported by the ADM1033.<br>This represents SMBus 2.0 as the Interface version                                  | 0000000<br>00000100                          |

| <63:48>   | Subsystem Vendor ID | Subsystem Vendor ID = 0 (subsystem fields are unsupported).                                                                                               | 0000000<br>0000000                           |

| <47:32>   | Subsystem Device ID | Subsystem Device ID = 0 (subsystem fields are unsupported).                                                                                               | 0000000<br>0000000                           |

| <31:0>    | Vendor Specific ID  | A unique number per device. Contains LOCATION information (LL)<br>and a 16-bit random number (x). See Table 9 for information on<br>setting the LLL bits. | 00000000<br>00000LLL<br>xxxxxxxx<br>xxxxxxxx |

#### SMBus 2.0 Fixed and Discoverable Mode

The ADM1033 also supports fixed and discoverable mode, which is backwards compatible with SMBus 1.0 and 1.1. Fixed and discoverable mode supports all the same functionality as ARP-capable mode, except for assign address in which case it powers up with a fixed address and is not changed by the assign address call. The fixed address is determined by the state of the LOCATION pin on powerup.

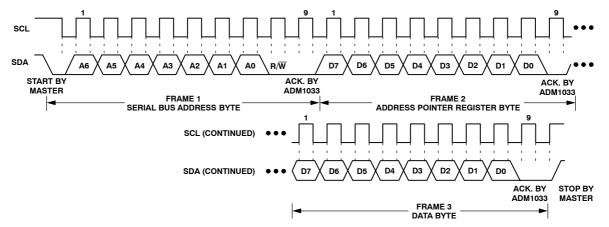

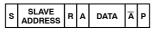

#### **SMBus 2.0 Read and Write Operations**

The master initiates data transfer by establishing a start condition, defined as a high-to-low transition on the serial data line (SDA) while the serial clock line (SCL) remains high. This indicates that an address/data stream is to follow. All slave peripherals connected to the serial bus respond to the start condition and shift in the next 8 bits, which consist of a 7-bit address (MSB first) plus an  $R/\overline{W}$  bit. This last bit determines the direction of the data transfer (whether data is written to or read from the slave device).

- 1. The peripheral that corresponds to the transmitted address responds by pulling the data line low during the low period before the 9th clock pulse, which is known as the acknowledge bit. All other devices on the bus remain idle while the selected device waits for data to be read from or written to it. If the  $R/\overline{W}$  bit is a 0, the master writes to the slave device. If the  $R/\overline{W}$  bit is a 1, the master reads from it.

- 2. Data is sent over the serial bus in sequences of 9 clock pulses 8 bits of data followed by an acknowledge bit from the slave device. Transitions on the data line must occur during the low period of the clock signal and remain stable during the high period, because a low-to-high transition when the clock is high may be interpreted as a stop signal. The number of data bytes that can be transmitted over the serial bus in a single read or write operation is limited only by what the master and slave devices can handle.

- 3. When all data bytes have been read or written, stop conditions are established. In write mode, the master pulls the data line high during the 10th

clock pulse to assert a stop condition. In read mode, the master device overrides the acknowledge bit by pulling the data line high during the low period before the 9th clock pulse. This is known as no acknowledge. The master takes the data line low during the low period before the 10th clock pulse, then high during the 10th clock pulse to assert a stop condition.

It is not possible to mix read and write in one operation, because the type of operation is determined at the beginning and cannot be changed without starting a new operation.

To write data to one of the device data registers or to read data from it, the address pointer register (APR) must be set so that the correct data register is addressed; then data can be written into that register or read from it. The first byte of a write operation always contains an address that is stored in the APR. If data is to be written to the device, then the write operation contains a second data byte, which is written to the register selected by the APR.

As illustrated in Figure 17, the device address is sent over the bus, followed by  $R/\overline{W}$  set to 0. This is followed by two data bytes. The first data byte is the address of the internal data register to be written to, which is stored in the APR. The second data byte is the data to be written to the internal data register.

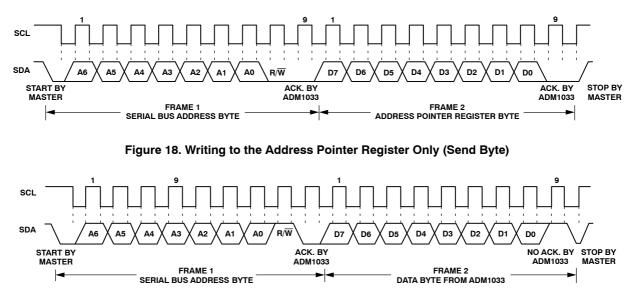

When reading data from a register there are two possibilities.

If the ADM1033's APR value is unknown or incorrect, it must be set to the correct value before data can be read from the desired data register. To do this, perform a write to the ADM1033 as before, but send only the data byte containing the register (See Figure 18.) A read operation is then performed, using the serial bus address and the  $R/\overline{W}$  bit set to 1, followed by the data byte read from the data register. (See Figure 19.)

However, if the APR is already at the desired address, data can be read from the corresponding data register without first writing to the APR. In this case, see Figure 18 can be omitted.

In Figure 17 to Figure 19, the serial bus address is determined by the state of the LOCATION pin on powerup.

Figure 17. Writing a Register Address to the Address Pointer Register, then Writing Data to the Selected Register

Figure 19. Reading Data from a Previously Selected Register

#### **Register Addresses for Single/Block Byte Modes**

The ADM1033 supports single byte as well as block read and write operations. The register address determines whether a single byte or multiple byte (block) operation is run. For a single byte operation, the MSB of the register address is set to 0; for a multiple byte operation, it is set to 1. The number of bytes read in a multiple byte operation is set in the #Bytes/Block Read Register at Address 0x00. The number of bytes written to the ADM1033 is specified during the block write operation. The addresses quoted in the register map and throughout this data sheet assume single byte operation. For multiple byte operations, set the MSB of each register address to 1.

#### Write Operations

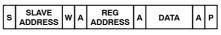

The SMBus specifications define protocols for read and write operations. The ADM1033 supports send byte, write byte, and block byte SMBus write protocols. The following abbreviations are used in the diagrams:

- S START

- P STOP

- R READ

- W WRITE

- A ACKNOWLEDGE

- A NO ACKNOWLEDGE

#### Send Byte

In this operation, the master device sends a single-command byte to a slave device as follows:

- 1. The master device asserts a start condition on SDA.

- 2. The master sends a 7-bit address followed by the write bit (low).

- 3. The addressed slave device asserts ACK on SDA.

- 4. The master sends the register address.

- 5. The slave asserts ACK on SDA.

- 6. The master asserts a stop condition on SDA, and the transaction ends.

| s | SLAVE<br>ADDRESS | / A | REG<br>ADDRESS | A | Р |

|---|------------------|-----|----------------|---|---|

|---|------------------|-----|----------------|---|---|

#### Figure 20. Send Byte

The ADM1033 uses the send byte operation to write a register address to the APR for a subsequent read from the same address. (See Figure 24). The user may be required to read data from the register immediately after setting up the address. If so, the master can assert a repeat start condition immediately after the final ACK and carry out a single byte read without asserting an intermediate stop condition.

#### Write Byte

In this operation, the master device sends a register address and one data byte to the slave device as follows:

- 1. The master asserts a start condition on SDA.

- 2. The master sends the 7-bit slave address followed by a write bit (low).

- 3. The addressed slave device asserts ACK on SDA.

- 4. The master sends the register address. The MSB of the register address should equal 0 for a write byte operation. If the MSB equals 1, a block write operation takes place.

- 5. The slave asserts ACK on SDA.

- 6. The master sends a data byte.

- 7. The slave asserts ACK on SDA.

- 8. The master asserts a stop condition on SDA to end the transaction.

Figure 21. Write Byte Operation

#### **Block Write**

In this operation, the master device writes a block of data to a slave address as follows. A maximum of 32 bytes can be written.

- 1. The master asserts a start condition on SDA.

- 2. The master sends the 7-bit slave address followed by a write bit (low).

- 3. The addressed slave device asserts ACK on SDA.

- 4. The master sends the register address. The register address sets up the address pointer register and determines whether a block write (MSB = 1) or a byte write (MSB = 0) takes place.

- 5. The slave asserts ACK on SDA.

- 6. The master sends the byte count.

- 7. The slave asserts ACK on SDA.

- 8. The master sends N data bytes.

- 9. The slave asserts ACK on SDA after each byte.

- 10. The master asserts a stop condition on SDA to end the transaction.

| _ |                  |   |   |                     |   |               |   |        |   |        |   | ))     | _ |   |

|---|------------------|---|---|---------------------|---|---------------|---|--------|---|--------|---|--------|---|---|

| s | SLAVE<br>ADDRESS | w | A | REGISTER<br>ADDRESS | A | BYTE<br>COUNT | А | DATA 1 | А | DATA 2 | A | DATA N | A | Ρ |

|   |                  |   |   |                     |   |               |   |        |   |        |   | "      |   |   |

#### Figure 22. Block Write to RAM

#### **Read Operations**

#### **Receive Byte**

This is useful when repeatedly reading a single register. The register address must be set up prior to this, with the MSB at 0 to read a single byte. In this operation, the master device receives a single byte from a slave device as follows:

- 1. The master device asserts a start condition on SDA.

- 2. The master sends the 7-bit slave address followed by the read bit (high).

- 3. The addressed slave device asserts ACK on SDA.

- 4. The master receives a data byte.

- 5. The master sends NO ACK on SDA.

- 6. The master asserts a stop condition on SDA, and the transaction ends.

In the ADM1033, the receive byte protocol is used to read a single byte from a register whose address has previously been set by a send byte or write byte operation.

Figure 23. Receive Byte

#### **Block Read**

In this operation, the master reads a block of data from a slave device. The number of bytes to be read must be set in advance. To do this, use a write byte operation to the #Bytes/Block Read Register at Address 0x00. The register address determines whether a block-read or a read-byte operation is to be completed (set MSB to 1 to specify a block-read operation). A maximum of 32 bytes can be read.

- 1. The master asserts a start condition on SDA.

- 2. The master sends the 7-bit slave address followed by the write bit (low).

- 3. The addressed slave device asserts ACK on SDA.

- 4. The master sends the register address (MSB = 1).

- 5. The slave asserts ACK on SDA.

- 6. The master asserts a repeated start on SDA.

- 7. The master sends the 7-bit slave address followed by the read bit (high).

- 8. The slave asserts ACK on SDA.

- 9. The slave sends the byte count.

- 10. The master asserts ACK on SDA.

- 11. The slave sends N data bytes.

- 12. The master asserts ACK on SDA after each data byte.

- 13. The master does not acknowledge after the Nth data byte.

- 14. The master asserts a stop condition on SDA to end the transaction.

|   |                  |   |   |                     | _ |   |                  |   |   |               | _ |        |   |                        |

|---|------------------|---|---|---------------------|---|---|------------------|---|---|---------------|---|--------|---|------------------------|

| s | SLAVE<br>ADDRESS | w | А | REGISTER<br>ADDRESS | A | s | SLAVE<br>ADDRESS | R | A | BYTE<br>COUNT | А | DATA 1 | A | (C<br>DATA N Ā P<br>)) |

|   |                  |   |   |                     |   |   |                  |   |   |               |   |        |   |                        |

#### Figure 24. Block Read from RAM

#### SMBus Timeout

The ADM1033 has a programmable SMBus timeout feature. When this is enabled, the SMBus typically times out after 25 ms of no activity. The timeout is disabled by default. It prevents hangups by releasing the bus after a period of inactivity.

To enable the SDA timeout, set the SDA timeout bit (Bit 5) of Configuration Register 1 (Address 0x01) to 1.

To enable the SCL timeout, set the SCL timeout bit (Bit 4) of Configuration Register 1 (Address 0x01) to 1.

#### Packet Error Checking (PEC)

The ADM1033 also supports packet error checking (PEC). This optional feature is triggered by the extra clock for the PEC byte. The PEC byte is calculated using CRC-8. The frame check sequence (FCS) conforms to CRC-8 by the following:

$$C(x) = x^8 + x^2 + x + 1$$

(eq. 1)

For more information, consult <u>www.SMBus.org</u>.

#### Alert Response Address (ARA)

| S ALERT RESPONSE<br>ADDRESS | R | Α | DEVICE<br>ADDRESS | Ā | Ρ |

|-----------------------------|---|---|-------------------|---|---|

|-----------------------------|---|---|-------------------|---|---|

Figure 25. ALERT Response Address

When multiple devices exist on the same bus, the ARA feature allows an interrupting device to identify itself to the host.

The <u>ALERT</u> output can be used as an interrupt output or as an <u>SMBusALERT</u>. One or more <u>ALERT</u> outputs can be connected to a common <u>SMBusALERT</u> line, connected to the master. If a device's  $\overline{\text{ALERT}}$  line goes low, the following occurs:

- 1. SMBusALERT is pulled low.

- 2. The master initiates a receive byte operation and sends the alert response address (ARA 0001 100). This is a general call address that must not be used as a specific address.

- 3. The device with the low  $\overline{\text{ALERT}}$  output responds to the ARA, and the master reads its device address. Once the address is known, it can be interrogated in the usual way.

- 4. If low ALERT output is detected in more than one device, the one with the lowest device address has priority, in accordance with normal SMBus arbitration.

- 5. Once the ADM1033 has responded to the ARA, it resets its <u>ALERT</u> output. However, if the error persists, the <u>ALERT</u> is re-asserted on the next monitoring cycle.

#### **Temperature Measurement System**

#### **Internal Temperature Measurement**

The ADM1033 contains an on-chip band gap temperature sensor. The on-chip ADC performs conversions on the sensor's output, outputting the data in 13-bit format. The resolution of the local temperature sensor is 0.03125°C.

Table 8 shows the format of the temperature data MSBs. Table 9 shows the same for the LSBs. To ensure accurate readings, read the LSBs first. This locks the current LSBs and MSBs until the MSBs are read. They then start to update again. (Reading only the MSBs does not lock the registers.) Temperature updates to the look-up table take place in parallel; so fan speeds may be updated even if the MSBs are locked.

#### Table 8. TEMPERATURE DATA FORMAT (LOCAL TEMPERATURE AND REMOTE TEMPERATURE HIGH BYTES)

| Temperature (°C) | Digital Output |

|------------------|----------------|

| –64°C            | 0000 0000      |

| -40°C            | 0001 1000      |

| –32°C            | 0010 0000      |

| –2°C             | 0011 1110      |

| −1°C             | 0011 1111      |

| 0°C              | 0100 0000      |

| 1°C              | 0100 0001      |

| 2°C              | 0100 0010      |

| 10°C             | 0100 1010      |

| 20°C             | 0101 0100      |

| 50°C             | 0111 0010      |

| 75°C             | 1000 1011      |

| 100°C            | 1010 0100      |

| 125°C            | 1011 1101      |

| 150°C            | 1101 0110      |

| 191°C            | 1111 1111      |

# Table 9. LOCAL AND REMOTE SENSOR EXTENDEDRESOLUTION

| Extended Resolution (°C) | Temperature Low Bits |

|--------------------------|----------------------|

| 0.0000                   | 00000                |

| 0.03125                  | 00001                |

| 0.0625                   | 00010                |

| 0.125                    | 00100                |

| 0.250                    | 01000                |

| 0.375                    | 01100                |

| 0.500                    | 10000                |

| 0.625                    | 10100                |

| 0.750                    | 11000                |

| 0.875                    | 11100                |

Temperature (°C) = (MSB –  $64^{\circ}$ C) + (LSB x 0.03125) Example: MSB = 0101 0100 = 84d LSB = 11100 = 28

Temperature  $^{\circ}C = (84 - 64) + (28 \times 0.03125) = 20.875$

#### **Remote Temperature Measurement**

The ADM1033 can measure the temperature of external diode sensor or diode-connected transistor, which are connected to Pins 9 and 10. These pins are dedicated temperature input channels. The series resistance cancellation (SRC) feature can automatically cancel out the effect of up to 1 k $\Omega$  of resistance in series with the remote thermal diode.

The forward voltage of a diode or diode-connected transistor, operated at a constant current, exhibits a negative temperature coefficient of about  $-2 \text{ mV/}^{\circ}\text{C}$ . Unfortunately, the absolute value of V<sub>BE</sub> varies from device to device, and individual calibration is required to null this out. Therefore, the technique is unsuitable for mass production.

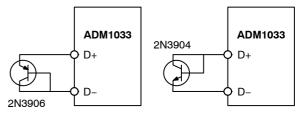

#### Figure 26. Measuring Temperature by Using Discreet Transistors

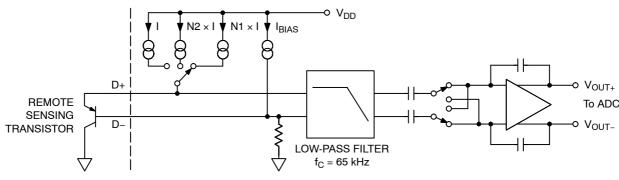

The ADM1033 operates at three different currents to measure the change in  $V_{BE}$ . Figure 27 shows the input signal conditioning used to measure the output of an external temperature sensor. It also shows the external sensor as a substrate transistor, provided for temperature monitoring on some microprocessors. The external sensor could work equally well as a discrete transistor.

If a discrete transistor is used, the collector is not grounded, and should be linked to the base. If a PNP transistor is used, the base is connected to the D– input and the emitter to the D+ input. If an NPN transistor is used, the emitter is connected to the D– input and the base to the D+ input. If the sensor is used in a very noisy environment, a capacitor value up to 1000 pF may be placed between the D+ and D- inputs to filter the noise. However, additional parasitic capacitance on the lines between D+, D-, and the thermal diode should also be considered. The total capacitance should never be greater than 1000 pF.

To measure each  $\Delta V_{BE}$ , the sensor is switched between operating currents of I, (N1 × I), and (N2 × I). The resulting waveform is passed through a 65 kHz low-pass filter to remove noise, then to a chopper-stabilized amplifier that amplifies and rectifies the waveform. This produces a dc voltage proportional to  $\Delta V_{BE}$ . These voltage measurements determine the temperature of the thermal diode, while automatically compensating for any series resistance on the D+ and/or D- lines. The temperature is stored in two registers as a 13-bit word.

To further reduce the effects of noise, digital filtering is performed by averaging the results of 16 measurement cycles at conversion rates of less than or equal to 8 Hz. An external temperature measurement takes nominally 32 ms when averaging is enabled and 6 ms when averaging is disabled.

One LSB of the ADC corresponds to  $0.03125^{\circ}$ C. The ADM1033 can theoretically measure temperatures from  $-64^{\circ}$ C to  $+191.96875^{\circ}$ C, although these are outside its operating range. The extended temperature resolution data format is shown in Table 9. The data for the local and remote channels is stored in the extended temperature resolution registers (Reg. 0x40 = Local, Reg. 0x42 = Remote 1).

# Table 10. TEMPERATURE MEASUREMENT REGISTERS

| Register | Description                | Default |

|----------|----------------------------|---------|

| 0x40     | Local Temperature, LSBs    | 0x00    |

| 0x41     | Local Temperature, MSBs    | 0x00    |

| 0x42     | Remote 1 Temperature, LSBs | 0x00    |

| 0x43     | Remote 1 Temperature, MSBs | 0x00    |

High and low temperature limit registers are associated with each temperature measurement channel. Exceeding the programmed high and low limits sets the appropriate status bit. Exceeding either limit can cause an SMBusALERT interrupt.

#### Table 11. TEMPERATURE MEASUREMENT LIMIT REGISTERS

| Register | Description          | Default     |

|----------|----------------------|-------------|

| 0x0B     | Local High Limit     | 0x8B (75°C) |

| 0x0C     | Local Low Limit      | 0x54 (20°C) |

| 0x0D     | Local THERM Limit    | 0x95 (85°C) |

| 0x0E     | Remote 1 High Limit  | 0x8B (75°C) |

| 0x0F     | Remote 1 Low Limit   | 0x54 (20°C) |

| 0x10     | Remote 1 THERM Limit | 0x95 (85°C) |

Figure 27. ADM1033 Signal Conditioning

#### **Additional Functions**

Several other temperature measurement functions available on the ADM1033 offer the systems designer added flexibility.

#### **Turn-off Averaging**

The ADM1033 performs averaging at conversion rates of less than or equal to 8 conversions per second. This means that the value in the measurement register is the average of 16 measurements. For faster measurements, set the conversion rate to 16 conversions per second or greater. (Averaging is not carried out at these conversion rates.) Alternatively, switch off averaging at the slower conversion rates by setting Bit 1 (AVG) of Configuration 1 Register (Address 0x01).

#### Single-channel ADC Conversions

In normal operating mode, the ADM1033 converts on two temperature channels: the local temperature channel, and the remote channel. However, the user has the option to set up the ADM1033 to convert on one channel only. To enable single-channel mode, the user sets the round-robin bit (Bit 7) in Configuration Register 2 (Address 0x02) to 0. When the round-robin bit equals 1, the ADM1033 converts on all temperature channels. In single-channel mode, it converts on one channel only, to be determined by the state of the channel selector bits (Bits 5 and 4) of the Configuration Register 2 (Address 0x02).

| Table 12. C | HANNEL S | ELECTO | R |

|-------------|----------|--------|---|

|             |          |        |   |

| Bits 5:4 | Channel Selector (Configuration 2) |

|----------|------------------------------------|

| 00       | Local Channel = Default            |

| 01       | Remote 1 Channel                   |

| 10       | Reserved                           |

| 11       | Reserved                           |

#### **Removing Temperature Errors**

As CPUs run faster and faster, it gets more difficult to avoid high frequency clocks when routing the D+ and Dtraces around a system board. Even when the recommended layout guidelines are followed, temperature errors attributed to noise coupled onto the D+ and D- lines remain. High frequency noise generally gives temperature measurements that are consistently too high. The ADM1033 has Local and Remote temperature offset registers at 0x16 and 0x17; one for each channel. By completing a one-time calibration, the user can determine the offset registers. The registers automatically add a twos compliment word to the remote temperature measurements, ensuring correct readings in the value registers.

#### Table 13. OFFSET REGISTERS

| Registration | Description     | Default |

|--------------|-----------------|---------|

| 0x16         | Local Offset    | 0x00    |

| 0x17         | Remote 1 Offset | 0x00    |

| Code       | Offset Value        |

|------------|---------------------|

| 0 0000 000 | 0°C (Default Value) |

| 0 0000 001 | 0.125°C             |

| 0 0000 111 | 0.875°C             |

| 0 0001 111 | 1.875°C             |

| 0 0111 111 | 7.875°C             |

| 0 1111 111 | 15.875°C            |

| 1 0000 000 | –16°C               |

| 1 1111 000 | –0.875°C            |

#### Table 14. OFFSET REGISTER VALUES

#### **Layout Considerations**

Digital boards can be electrically noisy environments. Try to protect the analog inputs from noise, particularly when measuring the very small voltages from a remote diode sensor. Take the following precautions:

- Place the ADM1033 as close as possible to the remote sensing diode. A distance of 4 inches to 8 inches is adequate, provided that the worst noise sources such as clock generators, data/address buses, and CRTs are avoided.

- Route the D+ and D- tracks close together, in parallel, with grounded guard tracks on each side. Provide a ground plane under the tracks if possible.

• Use wide tracks to minimize inductance and reduce noise pickup. At least 5 mil track width and spacing are recommended.

Figure 28. Arrangement of Signal Tracks

- Try to minimize the number of copper/solder joints, because they can cause thermocouple effects. Where copper/solder joints are used, make sure that they are in both the D+ and D- paths and at the same temperature. Thermocouple effects are not a major problem because 1°C corresponds to approximately 200  $\mu$ V, and thermocouple voltages are approximately 3  $\mu$ V/°C of temperature difference. Unless there are two thermocouples with a big temperature differential between them, the voltages should be much less than 200  $\mu$ V.

- Place a 0.1  $\mu$ F bypass capacitor close to the ADM1033.

- If the distance to the remote sensor is more than 8 inches, twisted pair cable is recommended. This works up to about 6 feet to 12 feet.

- For very long distances (up to 100 feet), use shielded twisted pair such as Belden #8451 microphone cable. Connect the twisted pair to D+ and D- and the shield to GND, close to the ADM1033. Leave the remote end of the shield unconnected to avoid ground loops.

Because the measurement technique uses switched current sources, excessive cable and/or filter capacitance can affect the measurement. When using long cables, the filter capacitor C1 may be reduced or removed. In any case, the total shunt capacitance should never exceed 1000 pF.

#### **Noise Filtering**

For temperature sensors operating in noisy environments, common practice is to place a capacitor across the D+ and D- pins to help combat the effects of noise. However, large capacitances affect the accuracy of the temperature measurement, leading to a recommended maximum capacitor value of 1000 pF. While this capacitor reduces the noise, it does not eliminate it, making it difficult to use the sensor in a very noisy environment.

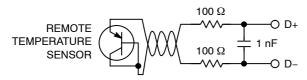

The ADM1033 has a major advantage over other devices when it comes to eliminating the effects of noise on the external sensor. The series resistance cancellation feature allows a filter to be constructed between the external temperature sensor and the part. The effect of any filter resistance seen in series with the remote sensor is automatically cancelled from the temperature. The construction of a filter allows the ADM1033 and the remote temperature sensor to operate in noisy environments. Figure 29 shows a low-pass R-C-R filter with the following values:  $R = 100 \Omega$  and C = 1 nF. This filtering reduces both common-mode noise and differential noise.

Figure 29. Filter between Remote Sensor and ADM1033

#### Limits, Status Registers, and Interrupts

High and low limits are associated with each measurement channel on the ADM1033. These can form the basis of system status monitoring. A status bit can be set for any out-of-limit condition and detected by polling the device. Alternatively, SMBusALERTs can be generated to flag a processor or microcontroller of an out-of-limit condition.

#### 8-bit Limits

The following is a list of all the 8-bit limits on the ADM1033:

| Register | Description          | Default     |

|----------|----------------------|-------------|

| 0x0B     | Local High Limit     | 0x8B (75°C) |

| 0x0C     | Local Low Limit      | 0x54 (20°C) |

| 0x0D     | Local THERM Limit    | 0x95 (85°C) |

| 0x0E     | Remote 1 High Limit  | 0x8B (75°C) |

| 0x0F     | Remote 1 Low Limit   | 0x54 (20°C) |

| 0x10     | Remote 1 THERM Limit | 0x95 (85°C) |

Table 15. TEMPERATURE LIMIT REGISTERS

#### Table 16. THERM LIMIT REGISTERS

| Register | Description   | Default      |

|----------|---------------|--------------|

| 0x19     | THERM % Limit | 0xFF default |

#### **Out-of-Limit Comparisons**

The ADM1033 measures all parameters in a round-robin format and sets the appropriate status bit for out-of-limit conditions. Comparisons are made differently, depending on whether the measured value is compared to a high or low limit.

High Limit: ≥ Comparison Performed

Low Limit: < Comparison Performed

#### Analog Monitoring Cycle Time

The analog monitoring cycle time begins on powerup, or, if monitoring has been disabled, by writing a 1 to the monitor/ STBY bit of Configuration Register 1, (Address 0x01). The ADC measures each one of the analog inputs in turn; as each measurement is completed, the result is automatically stored in the appropriate value register. The round-robin monitoring cycle continues unless it is disabled by writing a 0 to the monitor/STBY bit (Bit 0) of Configuration Register 1 (Address 0x01).

The ADC performs round-robin conversions and takes 11 ms for the local temperature measurement and 32 ms for each remote temperature measurement with averaging enabled.

The total monitoring cycle time for the average temperatures is therefore nominally.

$$32 + 11 = 43 \text{ ms}$$

(eq. 2)

Once the conversion time elapses, the round robin starts again. For more information, refer to the Conversion Rate Register section.

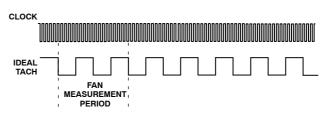

Fan TACH measurements take place in parallel and are not synchronized with the temperature measurements in any way.

#### **Status Registers**

The results of limit comparisons are stored in the status registers. A 1 represents an out-of-limit measurement; a 0 represents an in-limit measurement. The status registers are located at Addresses 0x4F to 0x51.

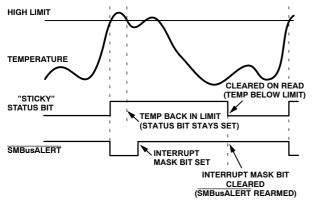

If the measurement is outside its limits, the corresponding status register bit is set to 1. It remains set at 1 until the measurement falls back within its limits and it is read or until an ARA is completed.

Poll the state of the various measurements by reading the status registers over the serial bus. If Bit 0 ( $\overline{\text{ALERT}}$  low) of Status Register 3 (Address 0x51) is set, this means that the  $\overline{\text{ALERT}}$  output has been pulled low by the ADM1033.

Pin 14 can be configured as a SMBusALERT output. This automatically notifies the system supervisor of an out-of-limit condition. Reading the status register clears the status bit as long as the error condition is gone.

Status register bits are sticky. Whenever a status bit is set due to an out-of-limit condition, it remains set even after the triggering event has gone. The only way to clear the status bit is to read the status register (after the event has gone). Interrupt mask registers (Reg. 0x08, Reg. 0x09, Reg. 0x0A) allow individual interrupt sources to be masked from causing an  $\overline{\text{ALERT}}$ . However, if one of these masked interrupt sources goes out of limit, its associated status bit is set in the status register.

# Table 17. INTERRUPT STATUS REGISTER 1 (REG. 0X4F)

| Bit # | Name   | Description                                                               |

|-------|--------|---------------------------------------------------------------------------|

| 7     | LH     | 1 = Local high temperature limit has been exceeded.                       |

| 6     | LL     | 1 = Local low temperature limit has<br>been exceeded.                     |

| 5     | R1H    | 1 = Remote 1 high temperature limit has<br>been exceeded                  |

| 4     | R1L    | 1 = Remote 1 low temperature limit has been exceeded.                     |

| 3     | R1D    | 1 = Remote 1 diode error; indicates an open or short on the D1+/D1- pins. |

| 2     | Unused | Reserved                                                                  |

| 1     | Unused | Reserved                                                                  |

| 0     | Unused | Reserved                                                                  |

#### Table 18. STATUS REGISTER 2 (REG. 0X50)

| Bit # | Name   | Description                                                                                                                                          |

|-------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7     | LT     | 1 = Local THERM temperature limit has<br>been exceeded.                                                                                              |

| 6     | R1T    | 1 = Remote 1 THERM temperature limit has been exceeded.                                                                                              |

| 5     | Unused | Reserved                                                                                                                                             |

| 4     | Т%     | 1 = THERM % on-time limit has been exceeded.                                                                                                         |

| 3     | TA     | 1 = One of the THERM limits has been<br>exceeded; and the THERM output<br>signal has been asserted.                                                  |

| 2     | TS     | 1 = THERM state. Indicates the THERM<br>pin is active; clears on a read if THERM<br>is not active. Does not generate an<br>ALERT in ALERT comp mode. |

| 1     | Res    | Reserved                                                                                                                                             |

| 0     | Res    | Reserved                                                                                                                                             |

#### Table 19. STATUS REGISTER 3 (REG. 0X51)

| Bit # | Name  | Description                                                                                          |

|-------|-------|------------------------------------------------------------------------------------------------------|

| 7     | F1S   | 1 = Fan 1 has stalled.                                                                               |

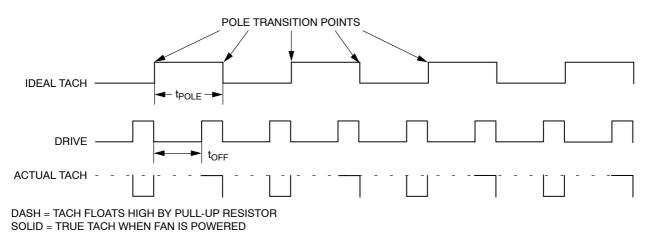

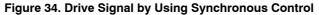

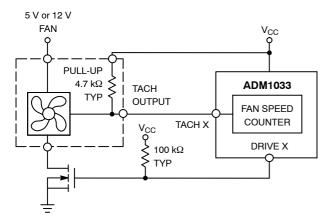

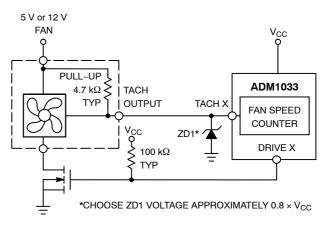

| 6     | FA    | 1 = Fan alarm speed. Fan 1 and Fan 2 are running at alarm speed.                                     |