Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# ANALOG Hot Swap Controller and Digital Power and DEVICES Finergy Monitoring with PMRus Interface **Energy Monitoring with PMBus Interface**

**ADM1276 Data Sheet**

### **FEATURES**

Controls supply voltages from 2 V to 20 V 370 ns response time to short circuit Resistor-programmable 5 mV to 25 mV current limit ±1% accurate, 12-bit ADC for current, VIN/VOUT readback Charge pumped gate drive for multiple external N-channel FETs High gate drive voltage to ensure lowest RDSON Foldback for tighter FET SOA protection Automatic retry or latch-off on current fault **Programmable current-limit timer for SOA Programmable, multifunction GPO** Power-good status output **Analog UV and OV protection ENABLE** pin Reports power and energy consumption over time Peak detect registers for current and voltage PMBus fast mode compliant interface

#### **APPLICATIONS**

20-lead LFCSP

Power monitoring and control/power budgeting **Central office equipment** Telecommunication and data communication equipment **PCs/servers**

### **GENERAL DESCRIPTION**

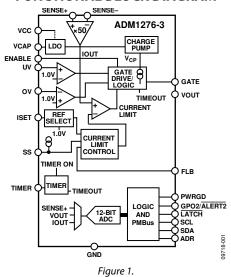

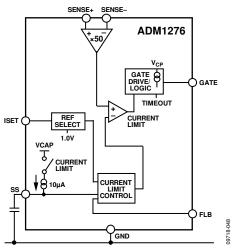

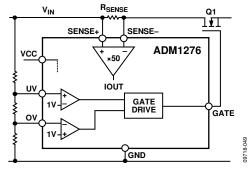

The ADM1276 is a hot swap controller that allows a circuit board to be removed from or inserted into a live backplane. It also features current and voltage readback via an integrated 12-bit analog-todigital converter (ADC), accessed using a PMBus™ interface.

The load current is measured using an internal current sense amplifier that measures the voltage across a sense resistor in the power path via the SENSE+ and SENSE- pins. A default limit of 20 mV is set, but this limit can be adjusted, if required, using a resistor divider network from the internal reference voltage to the ISET pin.

The ADM1276 limits the current through the sense resistor by controlling the gate voltage of an external N-channel FET in the power path, via the GATE pin. The sense voltage—and, therefore, the load current—is maintained below the preset maximum. The ADM1276 protects the external FET by limiting the time that the FET remains on while the current is at its maximum value. This current-limit time is set by the choice of capacitor connected to the TIMER pin. In addition, a foldback resistor network can be used to actively lower the current limit as the voltage across the FET is increased. This helps to maintain constant power in the

#### **Document Feedback** Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

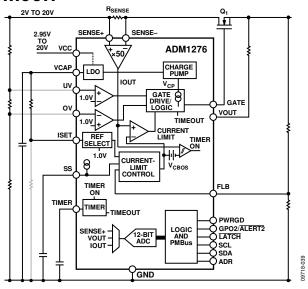

#### FUNCTIONAL BLOCK DIAGRAM

FET and allows the safe operating area (SOA) to be adhered to in an effective manner.

In case of a short-circuit event, a fast internal overcurrent detector responds within 370 ns and signals the gate to shut down. A 1500 mA pull-down device ensures a fast FET response. The ADM1276 features overvoltage (OV) and undervoltage (UV) protection, programmed using external resistor dividers on the UV and OV pins. A PWRGD signal can be used to detect when the output supply is valid, using the FLB pin to monitor the output. A GPO pin can be configured as an output signal that can be asserted when a programmed current or voltage level is reached.

The 12-bit ADC can measure the current in the sense resistor, as well as the supply voltage on the SENSE+ pin or the output voltage. A PMBus interface allows a controller to read current and voltage data from the ADC. Measurements can be initiated by a PMBus command. Alternatively, the ADC can run continuously, and the user can read the latest conversion data whenever required. As many as four unique PMBus addresses can be selected, depending on the way that the ADR pin is connected.

The ADM1276 is available in a 20-lead LFCSP with a LATCH pin that can be configured for automatic retry or latch-off when an overcurrent fault occurs.

## **ADM1276\* PRODUCT PAGE QUICK LINKS**

Last Content Update: 02/23/2017

## COMPARABLE PARTS -

View a parametric search of comparable parts.

## **EVALUATION KITS**

· ADM1276 Evaluation Board

### **DOCUMENTATION**

### **Application Notes**

- AN-1135: ADC Sampling Information ADM1275/ ADM1276/ADM1075

- AN-1343: Energy Metering on Hot Swap and Power Monitor Devices

### **Data Sheet**

ADM1276: Hot Swap Controller and Digital Power and Energy Monitoring with PMBus Interface Data Sheet

### **User Guides**

- UG-241: Using the Simulation Model for ADI Hotswap Controllers

- UG-263: Evaluating the ADM1275 and ADM1276

- UG-353: Hot Swap and Power Monitor Software

- UG-404: USB-SDP-CABLEZ Serial Interface Board

## SOFTWARE AND SYSTEMS REQUIREMENTS 🖵

- · ADMxxxx Common Run-Time

- Hot-Swap & Power Monitoring Evaluation Software

## DESIGN RESOURCES 🖵

- · ADM1276 Material Declaration

- PCN-PDN Information

- · Quality And Reliability

- Symbols and Footprints

### **DISCUSSIONS**

View all ADM1276 EngineerZone Discussions.

### SAMPLE AND BUY 🖵

Visit the product page to see pricing options.

## **TECHNICAL SUPPORT**

Submit a technical question or find your regional support number.

## DOCUMENT FEEDBACK 🖳

Submit feedback for this data sheet.

## **TABLE OF CONTENTS**

| Features 1                                   | Power Monitor Commands                          | 28 |

|----------------------------------------------|-------------------------------------------------|----|

| Applications1                                | Warning Limit Setup Commands                    | 29 |

| General Description                          | PMBus Direct Format Conversion                  | 30 |

| Functional Block Diagram1                    | Voltage and Current Conversion Using LSB Values | 32 |

| Revision History3                            | GPO2/ALERT2 Pin Behavior                        | 33 |

| Specifications4                              | Faults and Warnings                             | 33 |

| Serial Bus Timing Characteristics            | Generating an Alert                             | 33 |

| Absolute Maximum Ratings8                    | Handling/Clearing an Alert                      | 33 |

| Thermal Characteristics8                     | SMBus Alert Response Address                    | 33 |

| ESD Caution8                                 | Example Use of SMBus Alert Response Address     | 34 |

| Pin Configuration and Function Descriptions9 | PMBus Command Reference                         | 35 |

| Typical Performance Characteristics11        | OPERATION                                       | 36 |

| Typical Application Circuit                  | CLEAR_FAULTS                                    | 36 |

| Theory of Operation                          | CAPABILITY                                      | 36 |

| Powering the ADM1276                         | VOUT_OV_WARN_LIMIT                              | 36 |

| Current Sense Inputs                         | VOUT_UV_WARN_LIMIT                              | 36 |

| Current-Limit Reference                      | IOUT_OC_WARN_LIMIT                              | 36 |

| Setting the Current Limit (ISET)             | IOUT_WARN2_LIMIT                                | 36 |

| Soft Start                                   | VIN_OV_WARN_LIMIT                               | 37 |

| Foldback                                     | VIN_UV_WARN_LIMIT                               | 37 |

| Timer                                        | PIN_OP_WARN_LIMIT                               | 37 |

| Hot Swap Retry Duty Cycle21                  | STATUS_BYTE                                     | 37 |

| FET Gate Drive Clamps21                      | STATUS_WORD                                     | 38 |

| Fast Response to Severe Overcurrent          | STATUS_VOUT                                     | 38 |

| Undervoltage and Overvoltage                 | STATUS_IOUT                                     | 38 |

| ENABLE Input                                 | STATUS_INPUT                                    | 39 |

| Power Good22                                 | STATUS_MFR_SPECIFIC                             | 39 |

| VOUT Measurement                             | READ_EIN                                        | 40 |

| FET Health                                   | READ_VIN                                        | 40 |

| Power Monitor                                | READ_VOUT                                       | 40 |

| PMBus Interface                              | READ_IOUT                                       | 40 |

| Device Addressing                            | READ_PIN                                        | 40 |

| SMBus Protocol Usage                         | PMBUS_REVISION                                  | 40 |

| Packet Error Checking                        | MFR_ID                                          | 41 |

| SMBus Message Formats                        | MFR_MODEL                                       | 41 |

| Group Commands                               | MFR_REVISION                                    | 41 |

| Hot Swap Control Commands                    | PEAK_IOUT                                       | 41 |

| ADM1276 Information Commands                 | PEAK_VIN                                        | 41 |

| Status Commands                              | PEAK_VOUT                                       | 42 |

| GPO and Alert Pin Setup Commands28           | PMON_CONTROL                                    | 42 |

| PMON_CONFIG42                                                                              |

|--------------------------------------------------------------------------------------------|

| ALERT2_CONFIG43                                                                            |

| DEVICE_CONFIG44                                                                            |

| POWER_CYCLE44                                                                              |

| PEAK_PIN44                                                                                 |

|                                                                                            |

| REVISION HISTORY                                                                           |

| 11/13—Rev. B to Rev. C                                                                     |

| Changes to GATE Pin Parameter, Table 14                                                    |

| 4/13—Rev. A to Rev. B                                                                      |

| $\label{eq:Added Partial Transactions on I^2C Bus Section24} \\ Changes to Ordering Guide$ |

| 7/11—Rev. 0 to Rev. A                                                                      |

| Changes to Features Section                                                                |

| 3/11—Revision 0: Initial Version                                                           |

| READ_PIN_EXT       | 4  |

|--------------------|----|

| READ_EIN_EXT       | 4  |

| Outline Dimensions | 45 |

| Ordering Guide     | 4  |

## **SPECIFICATIONS**

$V_{\text{CC}} = 2.95 \text{ V to 20 V, } V_{\text{CC}} \geq V_{\text{SENSE+}}, V_{\text{SENSE+}} = 2 \text{ V to 20 V, } V_{\text{SENSE}} = (V_{\text{SENSE+}} - V_{\text{SENSE-}}) = 0 \text{ V, } T_{\text{A}} = -40 ^{\circ}\text{C to } +85 ^{\circ}\text{C, unless otherwise noted.}$

Table 1.

| Parameter                      | Symbol                   | Min  | Тур  | Max  | Unit | Test Conditions/Comments                                                                                                |

|--------------------------------|--------------------------|------|------|------|------|-------------------------------------------------------------------------------------------------------------------------|

| POWER SUPPLY                   |                          |      |      |      |      |                                                                                                                         |

| Operating Voltage Range        | Vcc                      | 2.95 |      | 20   | V    |                                                                                                                         |

| Undervoltage Lockout           |                          | 2.4  |      | 2.7  | V    | V <sub>CC</sub> rising                                                                                                  |

| Undervoltage Hysteresis        |                          |      | 90   | 120  | mV   |                                                                                                                         |

| Quiescent Current              | Icc                      |      |      | 5    | mA   | GATE on and power monitor running                                                                                       |

| UV PIN                         |                          |      |      |      |      |                                                                                                                         |

| Input Current                  | luv                      |      |      | 100  | nA   | UV ≤ 3.6 V                                                                                                              |

| UV Threshold                   | UV <sub>TH</sub>         | 0.97 | 1.0  | 1.03 | V    | UV falling                                                                                                              |

| <b>UV Threshold Hysteresis</b> | UV <sub>HYST</sub>       | 40   | 50   | 60   | mV   |                                                                                                                         |

| UV Glitch Filter               | $UV_GF$                  | 2    |      | 7    | μs   | 50 mV overdrive                                                                                                         |

| <b>UV Propagation Delay</b>    | $UV_PD$                  |      | 5    | 8    | μs   | UV low to GATE pull-down active                                                                                         |

| OV PIN                         |                          |      |      |      |      |                                                                                                                         |

| Input Current                  | lov                      |      |      | 100  | nA   | OV ≤ 3.6 V                                                                                                              |

| OV Threshold                   | $OV_TH$                  | 0.97 | 1.0  | 1.03 | V    | OV rising                                                                                                               |

| OV Threshold Hysteresis        | $OV_{HYST}$              | 50   | 60   | 70   | mV   | _                                                                                                                       |

| OV Glitch Filter               | $OV_GF$                  | 0.5  |      | 1.5  | μs   | 50 mV overdrive                                                                                                         |

| OV Propagation Delay           | $OV_PD$                  |      | 1.0  | 2    | μs   | OV high to GATE pull-down active                                                                                        |

| SENSE+ AND SENSE- PINS         |                          |      |      |      |      |                                                                                                                         |

| Input Current                  | I <sub>SENSEx</sub>      |      |      | 150  | μΑ   | Per individual pin; SENSE+, SENSE- = 20 V                                                                               |

| Input Imbalance                | I <sub>ΔSENSE</sub>      |      |      | 5    | μΑ   | IASENSE = (ISENSE+) - (ISENSE-)                                                                                         |

| VCAP PIN                       |                          |      |      |      |      | County (county)                                                                                                         |

| Internally Regulated           | $V_{VCAP}$               | 2.66 | 2.7  | 2.74 | V    | $0 \mu A \le I_{VCAP} \le 100 \mu A$ ; $C_{VCAP} = 1 \mu F$                                                             |

| Voltage                        | VCAI                     | 2.00 | _,,  |      | -    | o part = text = 100 party event 1 par                                                                                   |

| ISET PIN                       |                          |      |      |      |      |                                                                                                                         |

| Reference Select Threshold     | VISETRSTH                | 1.35 | 1.5  | 1.65 | V    | If V <sub>ISET</sub> > V <sub>ISETRSTH</sub> , an internal 1 V reference (V <sub>CLREF</sub> ) is used                  |

| Internal Reference             | V <sub>CLREF</sub>       |      | 1    |      | V    | Accuracies included in total sense voltage accuracies                                                                   |

| Gain of Current Sense          | AV <sub>CSAMP</sub>      |      | 50   |      | V/V  | Accuracies included in total sense voltage accuracies                                                                   |

| Amplifier                      |                          |      |      |      |      | _                                                                                                                       |

| Input Current                  | I <sub>ISET</sub>        |      |      | 100  | nA   | $V_{ISET} \leq V_{VCAP}$                                                                                                |

| GATE PIN                       |                          |      |      |      |      | Maximum voltage on the gate is always clamped to ≤31 V                                                                  |

| Gate Drive Voltage             | $\Delta V_{GATE}$        |      |      |      |      | $\Delta V_{GATE} = V_{GATE} - V_{SENSE+}$                                                                               |

|                                |                          | 10   | 12   | 14   | V    | $15 \text{ V} \ge \text{V}_{CC} \ge 8 \text{ V}$ ; $\text{I}_{GATE} \le 5 \mu\text{A}$                                  |

|                                |                          | 4.5  |      | 13   | V    | $20 \text{ V} \ge \text{V}_{CC} \ge 15 \text{ V}; I_{GATE} \le 5 \mu\text{A}$                                           |

|                                |                          | 8    |      | 10   | V    | $V_{SENSE+} = V_{CC} = 5 \text{ V}; I_{GATE} \le 5 \mu\text{A}$                                                         |

|                                |                          | 4.5  |      | 6    | V    | $V_{SENSE+} = V_{CC} = 2.95 \text{ V}; I_{GATE} \leq 1 \mu\text{A}$                                                     |

| Gate Pull-Up Current           | IGATEUP                  | -20  |      | -30  | μΑ   | $V_{GATE} = 0 V$                                                                                                        |

| Gate Pull-Down Current         | I <sub>GATEDN</sub>      |      |      |      |      |                                                                                                                         |

| Regulation                     | I <sub>GATEDN_REG</sub>  | 45   | 60   | 75   | μΑ   | $V_{GATE} \ge 2 \text{ V}$ ; $V_{ISET} = 1.0 \text{ V}$ ; $(SENSE+) - (SENSE-) = 30 \text{ mV}$                         |

| Slow                           | I <sub>GATEDN_SLOW</sub> | 5    | 10   | 15   | mA   | $V_{GATE} \ge 2 V$                                                                                                      |

| Fast                           | I <sub>GATEDN_FAST</sub> | 750  | 1500 | 2000 | mA   | $V_{GATE} \ge 12 \text{ V}; V_{CC} \ge 12 \text{ V}$                                                                    |

| <b>Gate Holdoff Resistance</b> |                          |      | 20   |      | Ω    | $V_{CC} = 0 V$                                                                                                          |

| HOT SWAP SENSE VOLTAGE         |                          |      |      |      |      |                                                                                                                         |

| Hot Swap Sense Voltage         | V <sub>SENSECL</sub>     | 19.6 | 20   | 20.4 | mV   | $V_{ISET} > 1.65 \text{ V; } V_{FLB} > 1.12 \text{ V; } V_{GATE} = (SENSE+) + 3 \text{ V; } I_{GATE} = 0  \mu\text{A;}$ |

| Current Limit                  |                          |      |      |      |      | $V_{SS} \ge 2 V$                                                                                                        |

| Foldback Inactive              |                          |      |      |      |      | $V_{GATE} = (SENSE+) + 3 \text{ V}; I_{GATE} = 0  \mu\text{A}; V_{SS} \ge 2 \text{ V}$                                  |

|                                |                          | 24.6 | 25   | 25.4 | mV   | $V_{ISET} = 1.25 \text{ V}; V_{FLB} > 1.395 \text{ V}$                                                                  |

|                                |                          | 19.6 | 20   | 20.4 | mV   | $V_{ISET} = 1.0 \text{ V}; V_{FLB} > 1.12 \text{ V}$                                                                    |

|                                |                          | 9.6  | 10   | 10.4 | mV   | $V_{ISET} = 0.5 \text{ V}; V_{FLB} > 0.57 \text{ V}$                                                                    |

|                                |                          | 4.6  | 5    | 5.4  | mV   | $V_{ISET} = 0.25 \text{ V}; V_{FLB} > 0.295 \text{ V}$                                                                  |

Rev. C | Page 4 of 48

| Parameter                                | Symbol                  | Min      | Тур  | Max  | Unit     | Test Conditions/Comments                                                                                                                  |

|------------------------------------------|-------------------------|----------|------|------|----------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Foldback Active                          |                         | 3.5      | 4    | 4.5  | mV       | $V_{FLB} = 0 \text{ V; } V_{GATE} = (SENSE+) + 3 \text{ V; } I_{GATE} = 0  \mu\text{A; } V_{SS} \ge 1 \text{ V}$                          |

|                                          |                         | 9.6      | 10   | 10.4 | mV       | $V_{ISET} > 1.0 \text{ V}; V_{FLB} = 0.5 \text{ V}; V_{GATE} = (SENSE+) + 3 \text{ V}; I_{GATE} = 0  \mu\text{A}; V_{SS} \ge 1 \text{ V}$ |

| Circuit Breaker Offset                   | V <sub>CBOS</sub>       | 0.6      | 0.88 | 1.12 | mV       | Circuit breaker trip voltage, $V_{CB} = V_{SENSECL} - V_{CBOS}$                                                                           |

| SEVERE OVERCURRENT                       |                         |          |      |      |          |                                                                                                                                           |

| Voltage Threshold                        | V <sub>SENSEOC</sub>    | 40       |      | 50   | mV       | $V_{ISET} = 1.0 \text{ V}; V_{FLB} > 1.1 \text{ V}; V_{SS} \ge 2 \text{ V}$                                                               |

| _                                        |                         | 9.5      |      | 13.0 | mV       | $V_{ISET} = 0.25 \text{ V}; V_{FLB} > 1.1 \text{ V}; V_{SS} \ge 2 \text{ V}$                                                              |

| Short Glitch Filter Duration             |                         | 90       |      | 200  | ns       | $V_{ISET} > 1.65 \text{ V}$ ; $V_{SENSE}$ driven from 18 mV to 52 mV; selectable via PMBus                                                |

| Long Glitch Filter Duration<br>(Default) |                         | 530      |      | 900  | ns       | V <sub>SENSE</sub> driven from 18 mV to 52 mV                                                                                             |

| Response Time                            |                         |          |      |      |          |                                                                                                                                           |

| With Short Glitch Filter                 |                         | 180      |      | 370  | ns       | 2 mV overdrive maximum severe overcurrent threshold                                                                                       |

| With Long Glitch Filter                  |                         | 645      |      | 1020 | ns       |                                                                                                                                           |

| SOFT START (SS PIN)                      |                         |          |      |      |          |                                                                                                                                           |

| SS Pull-Up Current                       | I <sub>SS</sub>         | -12      | -10  | -8   | μΑ       | $V_{SS} = 0 V$                                                                                                                            |

| Default V <sub>SENSECL</sub> Limit       |                         | 0.5      | 1.25 | 1.8  | mV       | When $V_{SENSE}$ reaches this level, $I_{SS}$ is enabled, ramping $V_{SENSECL}$ ; $V_{SS} = 0 \text{ V}$                                  |

| SS Pull-Down Current                     |                         |          | 100  |      | μΑ       | $V_{SS} = 1 \text{ V}$                                                                                                                    |

| TIMER PIN                                |                         |          |      |      | ļ '      |                                                                                                                                           |

| Timer Pull-Up Current                    | ITIMERUP                |          |      |      |          |                                                                                                                                           |

| Power-On Reset(POR)                      | I <sub>TIMERUPPOR</sub> | -2       | -3   | -4   | μΑ       | Initial power-on reset; V <sub>TIMER</sub> = 0.5 V                                                                                        |

| Overcurrent (OC) Fault                   | ITIMERUPFLT             | _<br>_57 | -60  | -63  | μΑ       | Overcurrent fault; $0.2 \text{ V} \leq \text{V}_{TIMER} \leq 1 \text{ V}$                                                                 |

| Timer Pull-Down Current                  | THMENOTTE               | 3,       | 00   | 03   | μ, τ     | Overeal entradity 6.2 v = v inview = 1 v                                                                                                  |

| Retry                                    | I <sub>TIMERDNRT</sub>  | 1.7      | 2    | 2.3  | μΑ       | After fault when GATE is off; V <sub>TIMER</sub> = 0.5 V                                                                                  |

| Hold                                     | ITIMERDNHOLD            | 1.7      | 100  | 2.5  | μΑ       | Holds TIMER at 0 V when inactive; V <sub>TIMER</sub> = 0.5 V                                                                              |

| Timer Retry/OC Fault                     | THMERDINHOLD            |          | 3.33 | 3.8  | μ/\<br>% | Defines the limits of the autoretry duty cycle                                                                                            |

| Current Ratio                            |                         |          | 3.33 | 5.0  | /0       | Defines the limits of the autoretry duty cycle                                                                                            |

| Timer High Threshold                     | V <sub>TIMERH</sub>     | 0.98     | 1.0  | 1.02 | V        |                                                                                                                                           |

| Timer Low Threshold                      | V <sub>TIMERL</sub>     | 0.18     | 0.2  | 0.22 | V        |                                                                                                                                           |

| FOLDBACK (FLB PIN)                       |                         |          |      |      |          |                                                                                                                                           |

| FLB and PWRGD Threshold                  | V <sub>FLBTH</sub>      | 1.08     | 1.1  | 1.12 | V        | FLB rising; V <sub>ISET</sub> = 1.0 V                                                                                                     |

| Input Current                            | I <sub>FLB</sub>        |          |      | 100  | nA       | $V_{FLB} \le 1.0 \text{ V}; V_{ISET} = 1.25 \text{ V}$                                                                                    |

| •                                        |                         |          |      | 100  | nA       | $V_{VCAP} \le V_{FLB} \le 20 \text{ V}$                                                                                                   |

| Hysteresis Current                       |                         | 1.7      |      | 2.3  | μΑ       |                                                                                                                                           |

| Internal Hysteresis Voltage              |                         | 1.9      |      | 3.1  | mV       | Voltage drop across the internal 1.3 kΩ resistor                                                                                          |

| Power-Good Glitch Filter                 | PWRGD <sub>GF</sub>     | 0.3      | 0.7  | 1    | μs       | 50 mV overdrive                                                                                                                           |

| Minimum Foldback Clamp                   | l IIII di               |          | 200  |      | mV       | Accuracies included in total sense voltage accuracies                                                                                     |

| VOUT PIN                                 |                         |          |      |      |          |                                                                                                                                           |

| Input Current                            |                         |          |      | 20   | μΑ       | VOUT = 20 V                                                                                                                               |

| LATCH PIN                                |                         |          |      |      | μπ       | V001 - 20 V                                                                                                                               |

| Output Low Voltage                       | Vo                      |          |      | 0.4  | V        | I <sub>LATCH</sub> = 1 mA                                                                                                                 |

| output tow voltage                       | V <sub>OL_LATCH</sub>   |          |      | 1.5  | V        | ILATCH = 1 MA  ILATCH = 5 mA                                                                                                              |

| Loakago Current                          |                         |          |      | 1.5  |          | $V_{LATCH} = 5 \text{ mA}$<br>$V_{LATCH} \le 2 \text{ V}; \overline{LATCH} \text{ output high-Z}$                                         |

| Leakage Current                          |                         |          |      |      | nA<br>   |                                                                                                                                           |

|                                          |                         |          |      | 1    | μΑ       | V <sub>LATCH</sub> = 20 V; LATCH output high-Z                                                                                            |

| ENABLE PIN                               |                         |          |      |      |          | No internal pull-up present on this pin                                                                                                   |

| Leakage Current                          |                         |          |      | 100  | nA       | $V_{GPO2} \le 2 V$                                                                                                                        |

|                                          |                         |          |      | 1    | μΑ       | $V_{GPO2} = 20 \text{ V}$                                                                                                                 |

| Input High Voltage                       | V <sub>IH</sub>         | 1.1      |      |      | V        |                                                                                                                                           |

| Input Low Voltage                        | V <sub>IL</sub>         |          |      | 8.0  | V        |                                                                                                                                           |

| Parameter                           | Symbol                | Min | Тур   | Max          | Unit   | Test Conditions/Comments                                                                                                                                            |

|-------------------------------------|-----------------------|-----|-------|--------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPO2/ALERT2 PIN                     |                       |     |       |              |        |                                                                                                                                                                     |

| Output Low Voltage                  | V <sub>OL GPO2</sub>  |     |       | 0.4          | V      | $I_{GPO2} = 1 \text{ mA}$                                                                                                                                           |

|                                     | 1 22 2 2 2            |     |       | 1.5          | V      | $I_{GPO2} = 5 \text{ mA}$                                                                                                                                           |

| Leakage Current                     |                       |     |       | 100          | nA     | $V_{GPO2} \le 2 \text{ V}$ ; GPO output high-Z                                                                                                                      |

|                                     |                       |     |       | 1            | μΑ     | $V_{GPO2} = 20 \text{ V}$ ; GPO output high-Z                                                                                                                       |

| PWRGD PIN                           |                       |     |       |              |        | 3.55 × 7.5 × 5.5 4.5 × 3                                                                                                                                            |

| Output Low Voltage                  | V <sub>OL PWRGD</sub> |     |       | 0.4          | V      | I <sub>PWRGD</sub> = 1 mA                                                                                                                                           |

|                                     | - OL_I WINGD          |     |       | 1.5          | V      | I <sub>PWRGD</sub> = 5 mA                                                                                                                                           |

| VCC That Guarantees Valid<br>Output |                       | 1   |       | 5            | V      | $I_{SINK} = 100 \mu A; V_{OL\_PWRGD} = 0.4 V$                                                                                                                       |

| Leakage Current                     |                       |     |       | 100          | nA     | V <sub>PWRGD</sub> ≤ 2 V; PWRGD output high-Z                                                                                                                       |

|                                     |                       |     |       | 1            | μΑ     | $V_{PWRGD} = 20 \text{ V}$ ; PWRGD output high-Z                                                                                                                    |

| CURRENT AND VOLTAGE                 |                       |     |       |              | Ċ      | , , ,                                                                                                                                                               |

| MONITORING                          |                       |     |       |              |        |                                                                                                                                                                     |

| Current Sense Absolute<br>Error     |                       |     |       |              |        | 25 mV input range; 128 sample averaging (unless otherwise noted)                                                                                                    |

|                                     |                       |     | ±0.2  | ±0.7         | %      | $V_{SENSE} = 20 \text{ mV}; V_{SENSE+} = 12 \text{ V}; T_A = 0^{\circ}\text{C} \text{ to } 65^{\circ}\text{C}$                                                      |

|                                     |                       |     | ±0.08 |              | %      | $V_{SENSE} = 20 \text{ mV}; V_{SENSE+} = 12 \text{ V}; T_A = 25^{\circ}\text{C}$                                                                                    |

|                                     |                       |     |       | ±1.0         | %      | $V_{SENSE} = 20 \text{ mV}$                                                                                                                                         |

|                                     |                       |     | ±0.08 |              | %      | $V_{SENSE} = 20 \text{ mV}; T_A = 25^{\circ}\text{C}$                                                                                                               |

|                                     |                       |     | ±0.2  |              | %      | $V_{SENSE} = 20 \text{ mV}$ ; $T_A = 0^{\circ}\text{C}$ to $65^{\circ}\text{C}$                                                                                     |

|                                     |                       |     |       | ±1.0         | %      | $V_{\text{SENSE}} = 20 \text{ mV}$ ; 16 sample averaging                                                                                                            |

|                                     |                       |     | ±0.08 |              | %      | $V_{SENSE} = 20 \text{ mV}$ ; 16 sample averaging; $T_A = 25^{\circ}\text{C}$                                                                                       |

|                                     |                       |     | ±0.2  |              | %      | $V_{SENSE} = 20 \text{ mV}$ ; 16 sample averaging; $T_A = 0^{\circ}\text{C}$ to 65°C                                                                                |

|                                     |                       |     | _0.2  | ±2.8         | %      | $V_{\text{SENSE}} = 20 \text{ mV}$ ; 1 sample averaging                                                                                                             |

|                                     |                       |     | ±0.09 | _2.0         | %      | $V_{SENSE} = 20 \text{ mV}$ ; 1 sample averaging; $T_A = 25^{\circ}\text{C}$                                                                                        |

|                                     |                       |     | ±0.05 |              | %      | $V_{SENSE} = 20 \text{ mV}$ ; 1 sample averaging; $T_A = 25 \text{ C}$<br>$V_{SENSE} = 20 \text{ mV}$ ; 1 sample averaging; $T_A = 0^{\circ}\text{C}$ to 65°C       |

|                                     |                       |     | ±0.2  | ±0.7         | %      | $V_{SENSE} = 25 \text{ mV}$ ; $V_{SENSE} = 12 \text{ V}$                                                                                                            |

|                                     |                       |     | ±0.04 | ±0.7         | %      | V <sub>SENSE</sub> = 25 mV; V <sub>SENSE+</sub> = 12 V; T <sub>A</sub> = 25°C                                                                                       |

|                                     |                       |     | ±0.04 |              | %      | V <sub>SENSE</sub> = 25 mV; V <sub>SENSE</sub> = 12 V; T <sub>A</sub> = 25 C<br>V <sub>SENSE</sub> = 25 mV; V <sub>SENSE</sub> = 12 V; T <sub>A</sub> = 0°C to 65°C |

|                                     |                       |     | ±0.13 | ±0.75        | %      | V <sub>SENSE</sub> = 20 mV; V <sub>SENSE+</sub> = 12 V                                                                                                              |

|                                     |                       |     |       | ±0.73        | %      | Vsense = 15 mV; Vsense <sub>+</sub> = 12 V                                                                                                                          |

|                                     |                       |     |       | ±0.6<br>±1.1 | %<br>% | • • •                                                                                                                                                               |

|                                     |                       |     |       |              |        | $V_{SENSE} = 10 \text{ mV}; V_{SENSE+} = 12 \text{ V}$                                                                                                              |

|                                     |                       |     |       | ±2.0         | %      | $V_{SENSE} = 5 \text{ mV}; V_{SENSE+} = 12 \text{ V}$                                                                                                               |

| CENICE A ACUIT AL. I.               |                       |     |       | ±4.3         | %      | V <sub>SENSE</sub> = 2.5 mV; V <sub>SENSE+</sub> = 12 V                                                                                                             |

| SENSE+/VOUT Absolute<br>Error       |                       |     |       | ±1.0         | %      | Low input range; input voltage ≥ 3 V                                                                                                                                |

| .s.c.                               |                       |     |       | ±1.0         | %      | High input range; input voltage ≥ 10 V                                                                                                                              |

| ADC Conversion Time                 |                       |     |       |              |        | Includes time for power multiplication                                                                                                                              |

|                                     |                       |     | 237   | 280          | μs     | 1 sample of VIN and IOUT; from command received to valid data in register                                                                                           |

|                                     |                       |     | 360   | 426          | μs     | 1 sample of VIN, VOUT, and IOUT; from command received to valid data in register                                                                                    |

|                                     |                       |     | 3753  | 4233         | μs     | 16 samples of VIN and IOUT averaged; from command received to valid data in register                                                                                |

|                                     |                       |     | 5545  | 6570         | μs     | 16 samples of VIN, VOUT, and IOUT averaged; from command received to valid data in register                                                                         |

| Power Multiplication Time           | <u> </u>              |     | 14    |              | μs     |                                                                                                                                                                     |

| ADR PIN                             |                       |     |       |              |        |                                                                                                                                                                     |

| Address Set to 00                   |                       | 0   |       | 0.8          | ٧      | Connect to GND                                                                                                                                                      |

| Input Current for Address 00        |                       | -40 | -22   |              | μΑ     | $V_{ADR} = 0 \text{ V to } 0.8 \text{ V}$                                                                                                                           |

| Address Set to 01                   |                       | 135 | 150   | 165          | kΩ     | Resistor to GND                                                                                                                                                     |

| Address Set to 10                   | 1                     | -1  |       | +1           | μΑ     | No connect state; maximum leakage current allowed                                                                                                                   |

| Parameter                            | Symbol                | Min | Тур | Max | Unit | Test Conditions/Comments                                                                |

|--------------------------------------|-----------------------|-----|-----|-----|------|-----------------------------------------------------------------------------------------|

| Address Set to 11                    |                       | 2   |     |     | V    | Connect to VCAP                                                                         |

| Input Current for Address 11         |                       |     | 3   | 10  | μΑ   | $V_{ADR}$ = 2.0 V to VCAP; must not exceed the maximum allowable current draw from VCAP |

| SERIAL BUS DIGITAL INPUTS (SDA, SCL) |                       |     |     |     |      |                                                                                         |

| Input High Voltage                   | V <sub>IH</sub>       | 1.1 |     |     | V    |                                                                                         |

| Input Low Voltage                    | $V_{IL}$              |     |     | 8.0 | V    |                                                                                         |

| Output Low Voltage                   | V <sub>OL</sub>       |     |     | 0.4 | V    | $I_{OL} = 4 \text{ mA}$                                                                 |

| Input Leakage                        | I <sub>LEAK-PIN</sub> | -10 |     | +10 | μΑ   |                                                                                         |

|                                      |                       | -5  |     | +5  | μΑ   | Device is not powered                                                                   |

| Nominal Bus Voltage                  | $V_{DD}$              | 2.7 |     | 5.5 | V    | 3 V to 5 V ± 10%                                                                        |

| Capacitance for SDA, SCL<br>Pins     | C <sub>PIN</sub>      |     | 5   |     | pF   |                                                                                         |

| Input Glitch Filter                  | t <sub>SP</sub>       | 0   |     | 50  | ns   |                                                                                         |

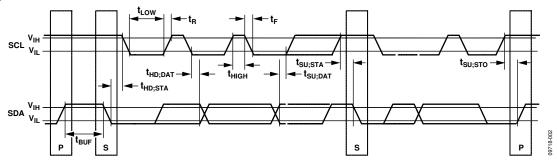

### **SERIAL BUS TIMING CHARACTERISTICS**

Table 2.

| Parameter               | Description        | Min | Тур | Max | Unit | Test Conditions/Comments                            |

|-------------------------|--------------------|-----|-----|-----|------|-----------------------------------------------------|

| f <sub>SCLK</sub>       | Clock frequency    |     |     | 400 | kHz  |                                                     |

| <b>t</b> <sub>BUF</sub> | Bus free time      | 1.3 |     |     | μs   | Following the stop condition of a read transaction  |

|                         |                    | 4.7 |     |     | μs   | Following the stop condition of a write transaction |

| t <sub>HD;STA</sub>     | Start hold time    | 0.6 |     |     | μs   |                                                     |

| t <sub>SU;STA</sub>     | Start setup time   | 0.6 |     |     | μs   |                                                     |

| t <sub>SU;STO</sub>     | Stop setup time    | 0.6 |     |     | μs   |                                                     |

| t <sub>HD;DAT</sub>     | SDA hold time      | 300 |     | 900 | ns   |                                                     |

| t <sub>SU;DAT</sub>     | SDA setup time     | 100 |     |     | ns   |                                                     |

| $t_{\text{LOW}}$        | SCL low time       | 1.3 |     |     | μs   |                                                     |

| t <sub>HIGH</sub>       | SCL high time      | 0.6 |     |     | μs   |                                                     |

| $t_R^1$                 | SCL, SDA rise time | 20  |     | 300 | ns   |                                                     |

| $t_{\text{F}}$          | SCL, SDA fall time | 20  |     | 300 | ns   |                                                     |

$<sup>^{1}</sup>Note: t_{R} = (V_{IL(MAX)} - 0.15) \text{ to } (V_{IH3V3} + 0.15) \text{ and } t_{F} = 0.9 \text{ V}_{DD} \text{ to } (V_{IL(MAX)} - 0.15); \text{ where } V_{IH3V3} = 2.1 \text{ V}, \text{ and } V_{DD} = 3.3 \text{ V}.$

### **Timing Diagram**

Figure 2. Serial Bus Timing Diagram

### **ABSOLUTE MAXIMUM RATINGS**

Table 3.

| Table 5.                                                        |                            |

|-----------------------------------------------------------------|----------------------------|

| Parameter                                                       | Rating                     |

| VCC Pin                                                         | −0.3 V to +25 V            |

| UV Pin                                                          | -0.3  V to  +4  V          |

| OV Pin                                                          | -0.3  V to  +4  V          |

| SS Pin                                                          | -0.3  V to VCAP $+ 0.3  V$ |

| TIMER Pin                                                       | -0.3  V to VCAP $+ 0.3  V$ |

| VCAP Pin                                                        | -0.3  V to  +4  V          |

| ISET Pin                                                        | -0.3  V to VCAP $+ 0.3  V$ |

| LATCH Pin                                                       | -0.3  V to  +25  V         |

| SCL Pin                                                         | -0.3 V to +6.5 V           |

| SDA Pin                                                         | -0.3 V to +6.5 V           |

| ADR Pin                                                         | -0.3  V to VCAP $+ 0.3  V$ |

| ENABLE Pin                                                      | −0.3 V to +25 V            |

| GPO2/ALERT2 Pin                                                 | -0.3  V to  +25  V         |

| PWRGD Pin                                                       | -0.3 V to +25 V            |

| FLB Pin                                                         | -0.3 V to +25 V            |

| VOUT Pin                                                        | -0.3 V to +25 V            |

| GATE Pin (Internal Supply Only) <sup>1</sup>                    | -0.3  V to  +36  V         |

| SENSE+ Pin                                                      | -0.3  V to  +25  V         |

| SENSE– Pin                                                      | -0.3  V to  +25  V         |

| V <sub>SENSE</sub> (V <sub>SENSE+</sub> – V <sub>SENSE</sub> –) | ±0.3 V                     |

| Continuous Current into Any Pin                                 | ±10 mA                     |

| Storage Temperature Range                                       | −65°C to +125°C            |

| Operating Temperature Range                                     | -40°C to +85°C             |

| Lead Temperature, Soldering (10 sec)                            | 300°C                      |

| Junction Temperature                                            | 150°C                      |

$<sup>^1</sup>$  The GATE pin has internal clamping circuits to prevent the GATE pin voltage from exceeding the maximum ratings of a MOSFET with V $_{\rm GSMAX}=20$  V and internal process limits. Applying a voltage source to this pin externally may cause irreversible damage.

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### THERMAL CHARACTERISTICS

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

**Table 4. Thermal Resistance**

| Package Type            | θ <sub>JA</sub> | Unit |

|-------------------------|-----------------|------|

| 20-lead LFCSP (CP-20-9) | 30.4            | °C/W |

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

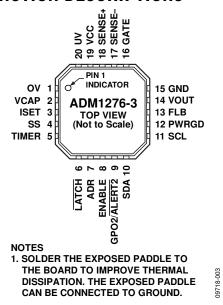

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 3. Pin Configuration

**Table 5. Pin Function Descriptions**

| Pin No. | Mnemonic    | Description                                                                                                                                                                                                                                                                                                                         |

|---------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19      | VCC         | Positive Supply Input Pin. An undervoltage lockout (UVLO) circuit resets the device when a low supply voltage is detected. GATE is held low when the supply is below UVLO. During normal operation, this pin should remain greater than or equal to SENSE+ to ensure that specifications are adhered to. No sequencing is required. |

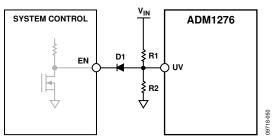

| 20      | UV          | Undervoltage Input Pin. An external resistor divider is used from the supply to this pin to allow an internal comparator to detect whether the supply is under the UV limit.                                                                                                                                                        |

| 1       | OV          | Overvoltage Input Pin. An external resistor divider is used from the supply to this pin to allow an internal comparator to detect whether the supply is above the OV limit.                                                                                                                                                         |

| 2       | VCAP        | Internal Regulated Supply. Place a capacitor with a value of 1 $\mu$ F or greater on this pin to maintain good accuracy. This pin can be used as a reference to program the ISET pin voltage.                                                                                                                                       |

| 3       | ISET        | Current Limit. This pin allows the current-limit threshold to be programmed. The default limit is set when this pin is connected directly to VCAP. To achieve a user defined sense voltage, the current limit can be adjusted using a resistor divider from VCAP. An external reference can also be used.                           |

| 4       | SS          | Soft Start Pin. A capacitor is used on this pin to set the soft start ramp profile. The voltage on the SS pin controls the current sense voltage limit, which controls the inrush current profile.                                                                                                                                  |

| 5       | TIMER       | Timer Pin. An external capacitor, C <sub>TIMER</sub> , sets an initial timing cycle delay and a fault delay. The GATE pin is pulled low when the voltage on the TIMER pin exceeds the upper threshold.                                                                                                                              |

| 6       | LATCH       | Latch Pin. This pin signals that the device is latching off after an overcurrent fault. The device can be configured for automatic retry after latch-off by connecting this pin directly to the UV or the ENABLE pin.                                                                                                               |

| 7       | ADR         | PMBus Address Pin. This pin can be tied to GND, tied to VCAP, remain floating, or tied low through a resistor to set four different PMBus addresses (see the Device Addressing section).                                                                                                                                            |

| 8       | ENABLE      | Enable Pin. This pin is a digital logic input. This input must be high to allow the ADM1276 hot swap controller to begin a power-up sequence. If this pin is held low, the ADM1276 is prevented from powering up. There is no internal pull-up on this pin.                                                                         |

| 9       | GPO2/ALERT2 | General-Purpose Digital Output/Alert. This is a dual function pin. There is no internal pull-up on this pin. The ALERT2 function of this pin can be configured to generate an alert signal when one or more fault or warning conditions are detected. At power-up, ALERT2 indicates the FET health mode by default.                 |

| 10      | SDA         | Serial Data Input/Output Pin. Open-drain input/output. Requires an external resistive pull-up.                                                                                                                                                                                                                                      |

| 11      | SCL         | Serial Clock Pin. Open-drain input. Requires an external resistive pull-up.                                                                                                                                                                                                                                                         |

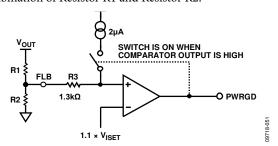

| 12      | PWRGD       | Power-Good Signal. Used to indicate that the supply is within tolerance. This signal is based on the voltage present on the FLB pin.                                                                                                                                                                                                |

| 13      | FLB         | Foldback Pin. A foldback resistor divider is placed from the source of the FET to this pin. Foldback is used to reduce the current limit when the source voltage drops. The foldback feature ensures that the power through the FET is not increased beyond the SOA limits.                                                         |

| Pin No.          | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14               | VOUT     | Output Voltage. This pin is used to read back the output voltage using the internal ADC. A 1 k $\Omega$ resistor should be inserted in series between the source of a FET and the VOUT pin.                                                                                                                                                                                                       |

| 15               | GND      | Ground Pin.                                                                                                                                                                                                                                                                                                                                                                                       |

| 16               | GATE     | Gate Output Pin. This pin is the high-side gate drive of an external N-channel FET. This pin is driven by the FET drive controller, which uses a charge pump to provide a pull-up current to charge the FET gate pin. The FET drive controller regulates to a maximum load current by regulating the GATE pin. GATE is held low when the supply is below UVLO.                                    |

| 17               | SENSE-   | Negative Current Sense Input Pin. A sense resistor between the SENSE+ pin and the SENSE- pin sets the analog current limit. The hot swap operation of the ADM1276 controls the external FET gate to maintain the sense voltage (V <sub>SENSE+</sub> – V <sub>SENSE-</sub> ). This pin also connects to the FET drain pin.                                                                         |

| 18               | SENSE+   | Positive Current Sense Input Pin. This pin connects to the main supply input. A sense resistor between the SENSE+ pin and the SENSE- pin sets the analog current limit. The hot swap operation of the ADM1276 controls the external FET gate to maintain the sense voltage (V <sub>SENSE+</sub> – V <sub>SENSE-</sub> ). This pin is also used to measure the supply input voltage using the ADC. |

| N/A <sup>1</sup> | EP       | Exposed Pad. The exposed pad is located on the underside of the LFCSP package. Solder the exposed pad to the printed circuit board (PCB) to improve thermal dissipation. The exposed pad can be connected to ground.                                                                                                                                                                              |

<sup>&</sup>lt;sup>1</sup> N/A means not applicable.

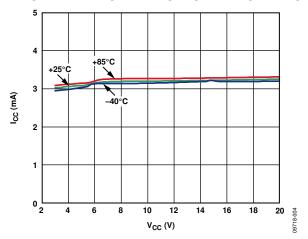

## TYPICAL PERFORMANCE CHARACTERISTICS

Figure 4. Supply Current (Icc) vs. Supply Voltage (Vcc)

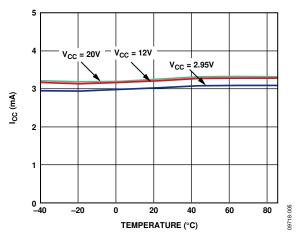

Figure 5. Supply Current (Icc) vs. Temperature

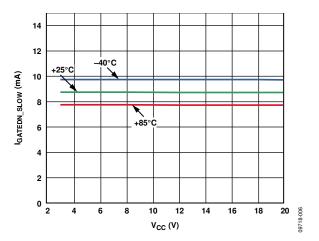

Figure 6. Gate Pull-Down Current (IGATEDN\_SLOW) vs. Supply Voltage (Vcc)

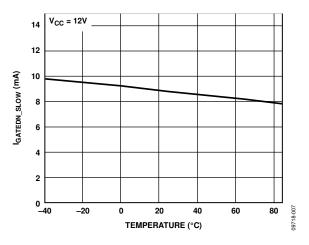

Figure 7. Gate Pull-Down Current (IGATEDN\_SLOW) vs. Temperature

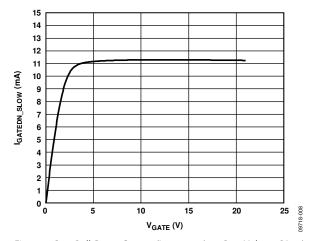

Figure 8. Gate Pull-Down Current ( $I_{GATEDN\_SLOW}$ ) vs. Gate Voltage ( $V_{GATE}$ )

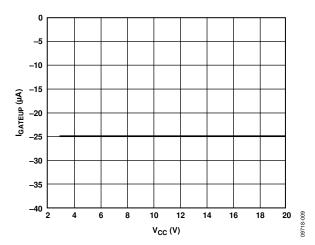

Figure 9. Gate Pull-Up Current (IGATEUP) vs. Supply Voltage (VCC)

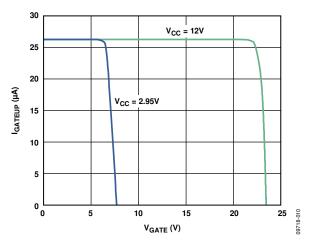

Figure 10. Gate Pull-Up Current (IGATEUP) vs. Gate Voltage (VGATE)

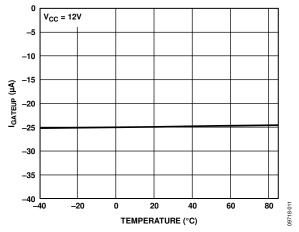

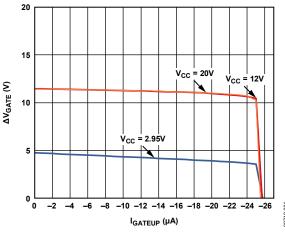

Figure 11. Gate Pull-Up Current ( $I_{GATEUP}$ ) vs. Temperature

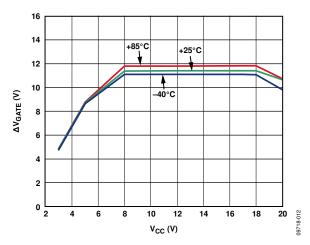

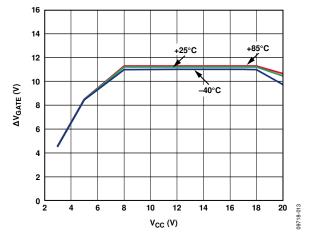

Figure 12. Gate Drive Voltage ( $\Delta V_{GATE}$ ) vs. Supply Voltage ( $V_{CC}$ ), No Load

Figure 13. Gate Drive Voltage ( $\Delta V_{GATE}$ ) vs. Supply Voltage ( $V_{CC}$ ), 5  $\mu A$  Load

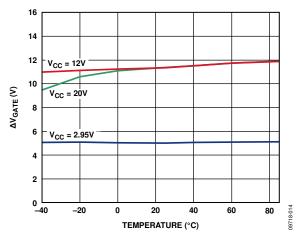

Figure 14. Gate Drive Voltage ( $\Delta V_{GATE}$ ) vs. Temperature, No Load

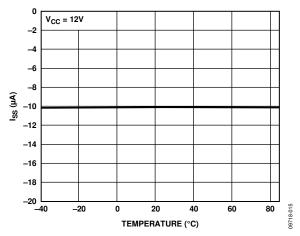

Figure 15. Soft Start Pull-Up Current (Iss) vs. Temperature

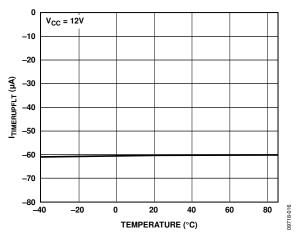

Figure 16. Timer Pull-Up Current, Overcurrent Fault (ITIMERUPFLT) vs. Temperature

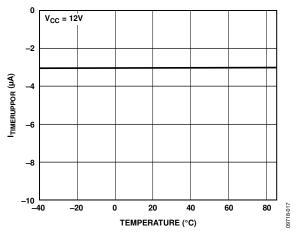

Figure 17. Timer Pull-Up Current, Power-On Reset (ITIMERUPPOR) vs. Temperature

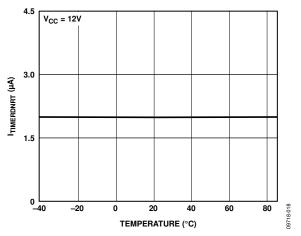

Figure 18. Timer Pull-Down Current, Retry (ITIMERDNRT) vs. Temperature

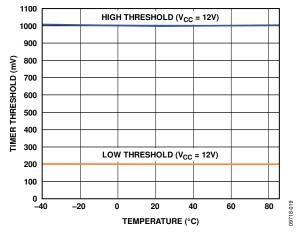

Figure 19. Timer Thresholds vs. Temperature

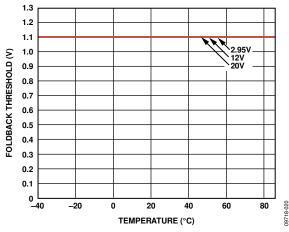

Figure 20. Foldback Threshold vs. Temperature

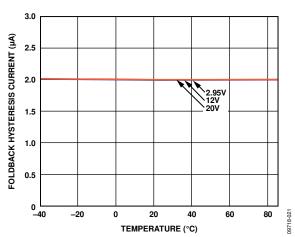

Figure 21. Foldback Hysteresis Current vs. Temperature

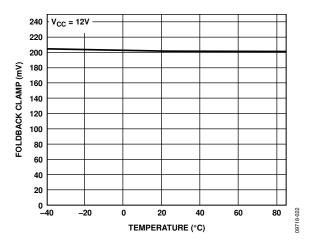

Figure 22. Foldback Clamp vs. Temperature

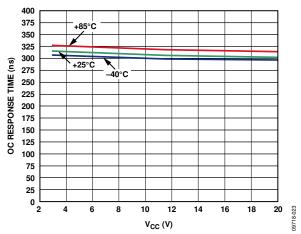

Figure 23. Severe Overcurrent Response Time vs. Supply Voltage ( $V_{CC}$ ),  $V_{ISET} = 0.25 \text{ V}$

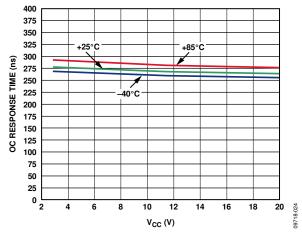

Figure 24. Severe Overcurrent Response Time vs. Supply Voltage ( $V_{CC}$ ),  $V_{ISET} = 1 \text{ V}$

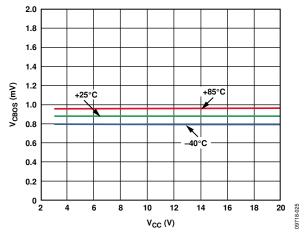

Figure 25. Circuit Breaker Offset (V<sub>CBOS</sub>) vs. Supply Voltage (V<sub>CC</sub>)

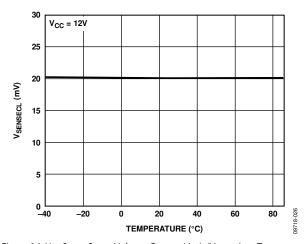

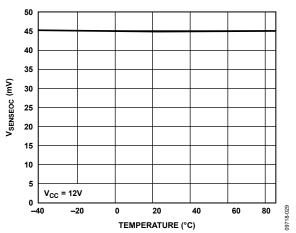

$\textit{Figure 26. Hot Swap Sense Voltage Current Limit (V_{\textit{SENSECL}}) vs. Temperature}$

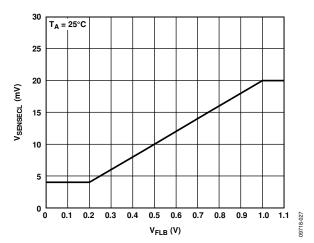

Figure 27. Hot Swap Sense Voltage Current Limit (V<sub>SENSECL</sub>) vs. Foldback Voltage (V<sub>FLB</sub>)

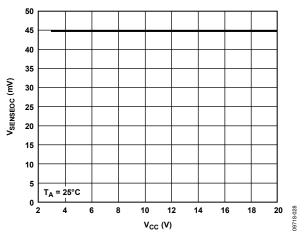

Figure 28. Severe Overcurrent Voltage Threshold ( $V_{SENSEOC}$ ) vs. Supply Voltage ( $V_{CC}$ ),  $V_{ISET} = V_{VCAP}$

Figure 29. Severe Overcurrent Voltage Threshold ( $V_{SENSEOC}$ ) vs. Temperature,  $V_{ISET} = V_{VCAP}$

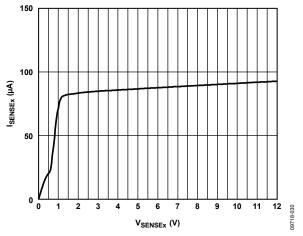

Figure 30. SENSE+/SENSE- Input Current (Isensex) vs. Voltage (Vsensex)

Figure 31. Gate Drive Voltage (ΔV<sub>GATE</sub>) vs. Gate Pull-Up Current (I<sub>GATEUP</sub>)

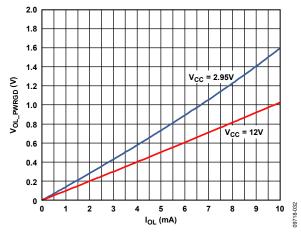

Figure 32. PWRGD Pin, Vol vs. Iol

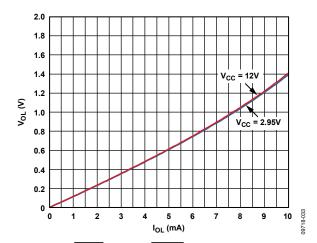

Figure 33. LATCH and GPO2/ALERT2 Digital Outputs, Vol vs. Iol

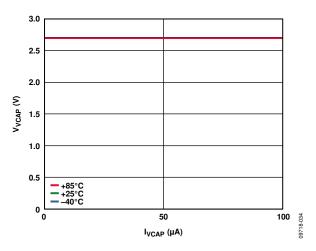

Figure 34. VCAP Voltage (V<sub>VCAP</sub>) vs. VCAP Load (I<sub>VCAP</sub>)

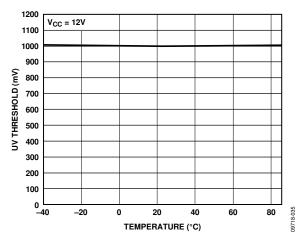

Figure 35. UV Threshold (UV $_{TH}$ ) vs. Temperature

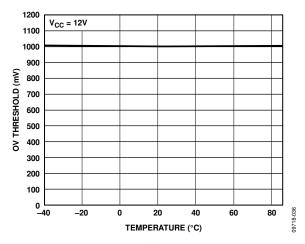

Figure 36. OV Threshold (OV $_{TH}$ ) vs. Temperature

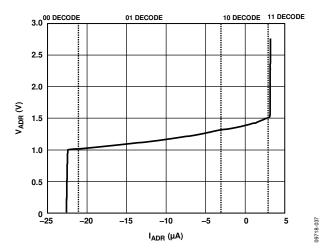

Figure 37. ADR Pin Voltage (VADR) vs. Current (IADR)

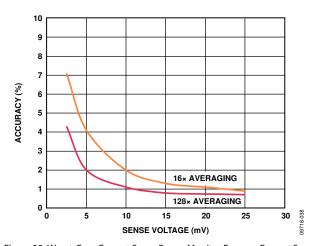

Figure 38. Worst-Case Current Sense Power Monitor Error vs. Current Sense Voltage ( $V_{SENSE}$ ),  $0^{\circ}C$  to  $65^{\circ}C$ ,  $V_{SENSE+} = 12 V$

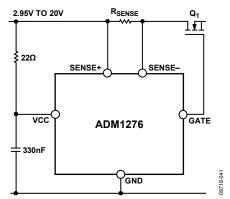

## TYPICAL APPLICATION CIRCUIT

Figure 39. Typical Application Circuit

### THEORY OF OPERATION

When circuit boards are inserted into a live backplane, discharged supply bypass capacitors draw large transient currents from the backplane power bus as they charge. These transient currents can cause permanent damage to connector pins, as well as dips on the backplane supply that can reset other boards in the system.

The ADM1276 is designed to control the powering on and off of a system in a controlled manner, allowing a board to be removed from, or inserted into, a live backplane by protecting it from excess currents. The ADM1276 can reside on the backplane or on the removable board.

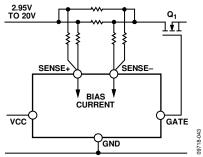

### **POWERING THE ADM1276**

A supply voltage from 2.95 V to 20 V is required to power the ADM1276 via the VCC pin. The VCC pin provides the majority of the bias current for the device; the remainder of the current needed to control the gate drive and best regulate the  $V_{GS}$  voltage is supplied by the SENSE+ pin.

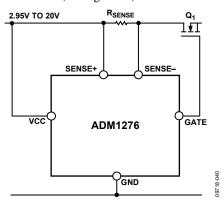

To ensure correct operation of the ADM1276, the voltage on the VCC pin must be greater than or equal to the voltage on the SENSE+ pin. No sequencing of the VCC and SENSE+ rails is necessary. The SENSE+ pin can be as low as 2 V for normal operation provided that a voltage of at least 2.95 V is connected to the VCC pin. In most applications, both the VCC and SENSE+ pins are connected to the same voltage rail, but they are connected via separate traces to prevent accuracy loss in the sense voltage measurement (see Figure 40).

Figure 40. Powering the ADM1276

To protect the ADM1276 from unnecessary resets due to transient supply glitches, an external resistor and capacitor can be added, as shown in Figure 41. Choose the values of these components so as to provide a time constant that can filter any expected glitches. The resistor should, however, be small enough to keep voltage drops due to quiescent current to a minimum. Unless a resistor is used to limit the inrush current, do not place a supply decoupling capacitor on the rail before the FET.

Figure 41. Transient Glitch Protection Using an RC Network

### **CURRENT SENSE INPUTS**

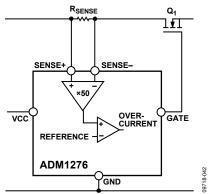

The load current is monitored by measuring the voltage drop across an external sense resistor,  $R_{\text{SENSE}}$  (see Figure 42). An internal current sense amplifier provides a gain of 50 to the voltage drop detected across  $R_{\text{SENSE}}$ . The result is compared to an internal reference and used by the hot swap control logic to detect when an overcurrent condition occurs.

Figure 42. Hot Swap Current Sense Amplifier

The SENSE± inputs may be connected to multiple parallel sense resistors, which can affect the voltage drop detected by the ADM1276. The current flowing through the sense resistors creates an offset, resulting in reduced accuracy.

To achieve better accuracy, the averaging resistors sum the current from the nodes of each sense resistor, as shown in Figure 43. The typical value for the averaging resistors is 10  $\Omega.$  The averaging resistors are chosen to balance the input current to both sense pins to within 5  $\mu A.$  This ensures that the same offset is seen by both sense inputs.

Figure 43. Connection of Multiple Sense Resistors to the SENSE± Pins

#### **CURRENT-LIMIT REFERENCE**

The current-limit reference voltage determines the load current level to which the ADM1276 limits the current during an over-current event. This reference voltage is compared to the gained-up current sense voltage to determine whether the limit is reached.

An internal current-limit reference selector block continuously compares the ISET, soft start, and foldback voltages to determine which voltage is the lowest at any given time; the lowest voltage is used as the current-limit reference. This ensures that the programmed current limit, ISET, is used in normal operation, and that the soft start and foldback features reduce the current limit when required during startup and/or fault conditions.

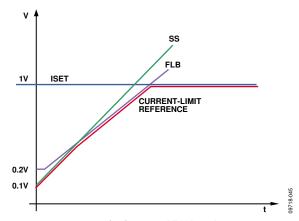

Figure 44. Current-Limit Reference Selection

The foldback and soft start voltages vary during different modes of operation and are, therefore, clamped to minimum levels of 200 mV and 100 mV, respectively, to prevent zero current flow due to the current limit being too low. Figure 45 provides an example of how the soft start, foldback, and ISET voltages interact during startup as the ADM1276 is enhancing the FET and charging the load capacitances. Depending on how the soft start and foldback features are configured, the hand-off point can vary to ensure that the FET is being operated within the correct limits.

Figure 45. Interaction of Soft Start, Foldback, and ISET Current Limits

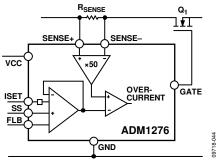

### **SETTING THE CURRENT LIMIT (ISET)**

The maximum current limit is partially determined by selecting a sense resistor to match the current sense voltage limit on the controller for the desired load current. However, as currents become larger, the sense resistor requirements become smaller, and resolution can be difficult to achieve when selecting the appropriate sense resistor. The ADM1276 provides an adjustable current sense voltage limit to handle this issue. The device allows the user to program the required current sense voltage limit from 5 mV to 25 mV.

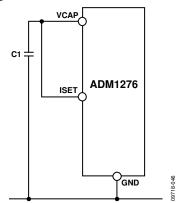

The default value of 20 mV is achieved by connecting the ISET pin directly to the VCAP pin. This configures the device to use an internal 1 V reference, which equates to 20 mV at the sense inputs (see Figure 46).

Figure 46. Fixed 20 mV Current Sense Limit

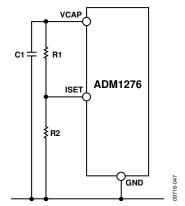

To program the sense voltage from 5 mV to 25 mV, a resistor divider is used to set a reference voltage on the ISET pin (see Figure 47).

Figure 47. Adjustable 5 mV to 25 mV Current Sense Limit

The VCAP pin has a 2.7 V internal generated voltage that can be used to set a voltage at the ISET pin. Assuming that  $V_{\text{ISET}}$  equals the voltage on the ISET pin, size the resistor divider to set the ISET voltage as follows:

$$V_{ISET} = V_{SENSE} \times 50$$

where  $V_{SENSE}$  is the current sense voltage limit.

The VCAP rail can also be used as the pull-up supply for setting the  $I^2C$  address. Do not use the VCAP pin for any other purpose. To guarantee accuracy specifications, do not load the VCAP pin by more than 100  $\mu A$ .

### **SOFT START**

A capacitor connected to the SS pin determines the inrush current profile. Before the FET is enabled, the output voltage of the current-limit reference selector block is clamped at 100 mV. This, in turn, holds the hot swap sense voltage current limit,  $V_{\mbox{\scriptsize SENSECL}}$ , at approximately 2 mV. When the FET receives a request to turn on, the SS pin is held at ground until the voltage between the SENSE+ and SENSE– pins ( $V_{\mbox{\scriptsize SENSE}}$ ) reaches the circuit breaker voltage,  $V_{\mbox{\tiny CB}}$ .

$$V_{CB} = V_{SENSECL} - V_{CBOS}$$

where  $V_{CBOS}$  is typically 0.88 mV, making  $V_{CB} = 1.12$  mV.

When the load current generates a sense voltage equal to  $V_{\text{CB}}$ , a 10  $\mu A$  current source is enabled, which charges the SS capacitor and results in a linear ramping voltage on the SS pin. The current-limit reference also ramps up accordingly, allowing the regulated load current to ramp up while avoiding sudden transients during power-up. The SS capacitor value is given by

$$C_{SS} = \frac{I_{SS} \times t}{V_{ISFT}}$$

where:

$I_{SS} = 10 \, \mu A$ .

t = SS ramp time.

For example, a 10 nF capacitor gives a soft start time of 1 ms.

Note that the SS voltage may intersect with the FLB (foldback) voltage, and the current-limit reference may change to follow

FLB (see Figure 45). This change has minimal impact on startup because the output voltage rises at a similar rate to the SS voltage.

Figure 48. Soft Start

### **FOLDBACK**