Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Digital Controller for Isolated Power Supply Applications

Data Sheet ADP1046A

#### **FEATURES**

Integrates all typical PWM controller functions

7 PWM control signals

**Digital control loop**

Integrated programmable loop filters

Programmable voltage line feedforward

**Dedicated soft start filter**

Remote and local voltage sense

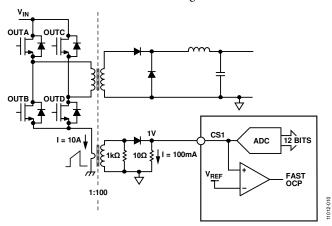

Primary and secondary side current sense

Synchronous rectifier control

**Current sharing**

**OrFET control**

I<sup>2</sup>C interface

**Extensive fault detection and protection**

**Extensive programming and telemetry**

Fast digital calibration

**User accessible EEPROM**

#### **APPLICATIONS**

AC-to-DC power supplies

Isolated dc-to-dc power supplies

Redundant power supply systems

Server, storage, network, and communications

infrastructure

#### **GENERAL DESCRIPTION**

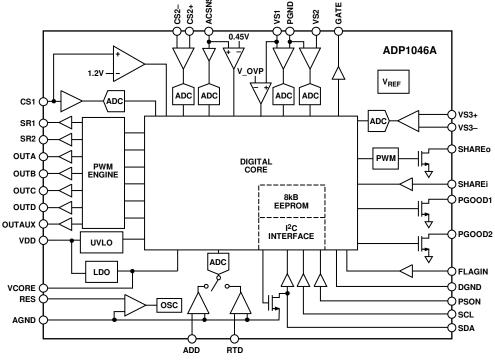

The ADP1046A is a flexible, digital secondary side controller designed for ac-to-dc and isolated dc-to-dc secondary side applications. The ADP1046A is pin-compatible with the ADP1043A and offers several enhancements and new features, including voltage feedforward and improved loop response to maximize efficiency.

The ADP1046A is optimized for minimal component count, maximum flexibility, and minimum design time. Features include local and remote voltage sense, primary and secondary side current sense, digital pulse-width modulation (PWM) generation, current sharing, and redundant OrFET control. The control loop digital filter and compensation terms are integrated and can be programmed over the I<sup>2</sup>C interface. Programmable protection features include overcurrent protection (OCP), overvoltage protection (OVP), undervoltage lockout (UVLO), and overtemperature protection (OTP).

The built-in EEPROM provides extensive programming of the integrated loop filter, PWM signal timing, inrush current, and soft start timing and sequencing. Reliability is improved through a built-in checksum and programmable protection circuits.

A comprehensive GUI is provided for easy design of loop filter characteristics and programming of the safety features. The industry-standard  $\rm I^2C$  bus provides access to the many monitoring and system test functions.

The ADP1046A is available in a 32-lead LFCSP and operates from a single 3.3 V supply.

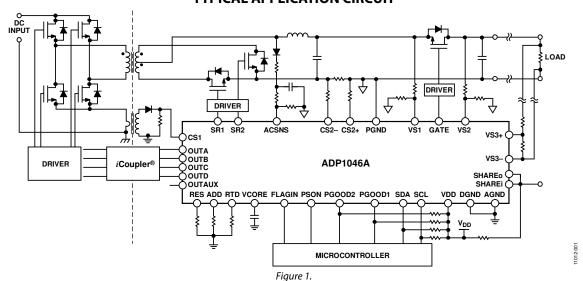

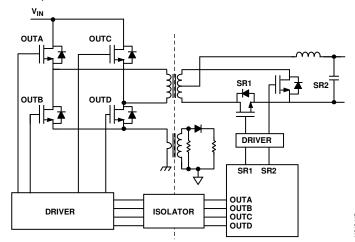

### **TYPICAL APPLICATION CIRCUIT**

Rev. 0

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2013 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

# **ADP1046A\* PRODUCT PAGE QUICK LINKS**

Last Content Update: 02/23/2017

## COMPARABLE PARTS -

View a parametric search of comparable parts.

## **EVALUATION KITS**

· ADP1046A Evaluation Board

## **DOCUMENTATION**

#### **Application Notes**

- AN-1253: Layout Considerations for Digital Power Management (ADP1046A)

- AN-1383: ADP1046A EEPROM Programming

#### **Data Sheet**

ADP1046A: Digital Controller for Isolated Power Supply Applications Data Sheet

#### **User Guides**

- UG-589: Interleaved Two-Switch Forward Topology Featuring the ADP1046A

- UG-734: Wide Input Range, Full Bridge Phase Shifted Topology using the ADP1046A

- UG-768: Evaluating the ADP1046A Digital Controller in Resonant Mode for Isolated Power Supply

## SOFTWARE AND SYSTEMS REQUIREMENTS 🖳

ADP1046A Software, Ver. 1.3.2

## REFERENCE MATERIALS 🖵

#### **Technical Articles**

• Designing Digital Power Supplies With A State Machine

# DESIGN RESOURCES 🖵

- · ADP1046A Material Declaration

- PCN-PDN Information

- · Quality And Reliability

- · Symbols and Footprints

## **DISCUSSIONS**

View all ADP1046A EngineerZone Discussions.

## SAMPLE AND BUY 🖳

Visit the product page to see pricing options.

## **TECHNICAL SUPPORT**

Submit a technical question or find your regional support number.

## DOCUMENT FEEDBACK 🖳

Submit feedback for this data sheet.

# **ADP1046A**

# **TABLE OF CONTENTS**

| Features 1                                    | First Flag Fault ID and Value Registers  | 28 |

|-----------------------------------------------|------------------------------------------|----|

| Applications1                                 | External Flag Input (FLAGIN Pin)         | 28 |

| General Description1                          | Temperature Readings (RTD Pin)           | 28 |

| Typical Application Circuit                   | Overtemperature Protection (OTP)         | 29 |

| Revision History                              | Overcurrent Protection (OCP)             | 29 |

| Specifications4                               | Constant Current Mode                    | 30 |

| Absolute Maximum Ratings9                     | Overvoltage Protection (OVP)             | 30 |

| Thermal Resistance                            | Undervoltage Protection (UVP)            | 31 |

| Soldering9                                    | AC Sense (ACSNS)                         | 31 |

| ESD Caution                                   | Volt-Second Balance                      | 31 |

| Pin Configuration and Function Descriptions10 | Digital Load Line and Slew Rate          | 32 |

| Typical Performance Characteristics           | Power Supply Calibration and Trim        | 33 |

| Theory of Operation14                         | CS1 Trim                                 | 33 |

| Current Sense                                 | CS2 Trim                                 | 33 |

| Voltage Sense and Control Loop                | Voltage Calibration and Trim             | 34 |

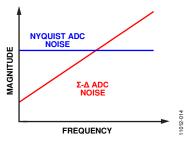

| ADCs16                                        | Output Voltage Setting (VS3+, VS3- Trim) | 34 |

| VS1 Operation (VS1)                           | VS1 Trim                                 | 34 |

| VS2 Operation (VS2)                           | VS2 Trim                                 | 34 |

| VS3 Operation (VS3+, VS3-)17                  | RTD/OTP Trim                             | 34 |

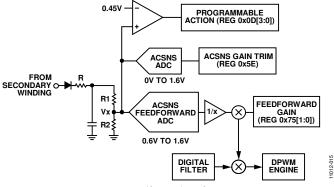

| Voltage Line Feedforward and ACSNS17          | ACSNS Calibration and Trim               | 35 |

| Digital Filter17                              | Layout Guidelines                        | 36 |

| PWM and Synchronous Rectifier Outputs         | CS2+ and CS2                             | 36 |

| (OUTA, OUTB, OUTC, OUTD, OUTAUX, SR1, SR2) 18 | VS3+ and VS3                             | 36 |

| Synchronous Rectification                     | VDD                                      | 36 |

| Synchronous Rectifier (SR) Delay              | SDA and SCL                              | 36 |

| Light Load Mode                               | CS1                                      | 36 |

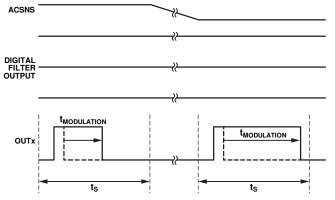

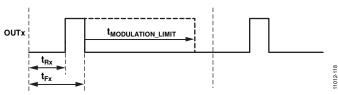

| Modulation Limit                              | Exposed Pad                              | 36 |

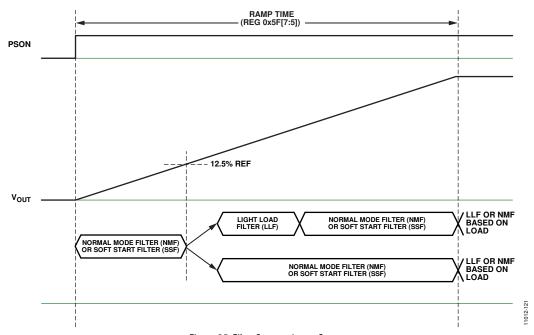

| Soft Start                                    | VCORE                                    | 36 |

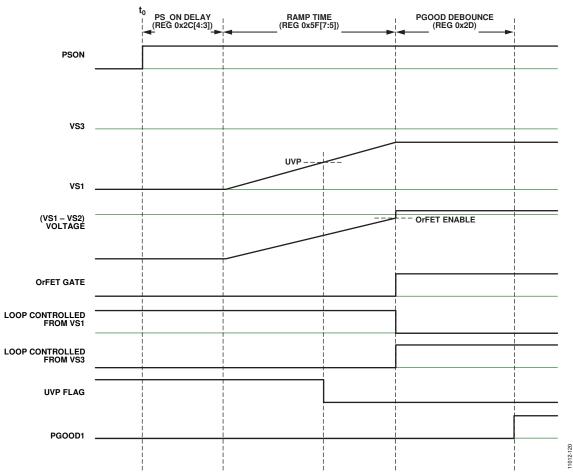

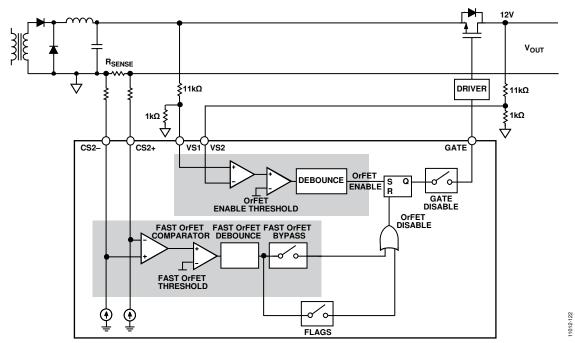

| OrFET Control (GATE Pin)                      | RES                                      | 36 |

| VDD                                           | RTD                                      | 36 |

| VDD/VCORE OVLO24                              | AGND, DGND, and PGND                     | 36 |

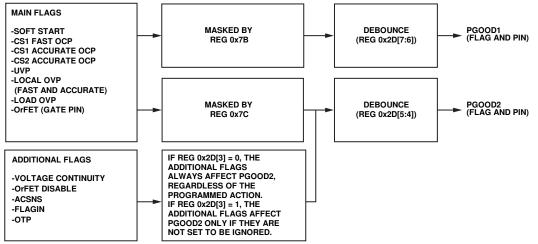

| Power Good                                    | I <sup>2</sup> C Interface Communication | 37 |

| Current Sharing25                             | I <sup>2</sup> C Overview                | 37 |

| Power Supply System and Fault Monitoring27    | I <sup>2</sup> C Address                 | 37 |

| Flags                                         | Data Transfer                            | 37 |

| Monitoring Functions                          | General Call Support                     | 39 |

| Voltage Readings                              | 10-Bit Addressing                        | 39 |

| Current Readings                              | Fast Mode                                | 39 |

| Power Readings                                | Repeated Start Condition                 | 39 |

| Power Monitoring Accuracy                     | Electrical Specifications                | 39 |

| Fault Conditions39                                  | ID Registers62                                   |

|-----------------------------------------------------|--------------------------------------------------|

| Timeout Condition39                                 | PWM and Synchronous Rectifier Timing Registers63 |

| Data Transmission Faults39                          | Digital Filter Programming Registers73           |

| Data Content Faults39                               | Soft Start Filter Programming Registers75        |

| EEPROM41                                            | Extended Functions Registers75                   |

| EEPROM Overview41                                   | EEPROM Registers79                               |

| Page Erase Operation41                              | Resonant Mode Operation82                        |

| Read Operation (Byte Read and Block Read)41         | Resonant Mode Enable82                           |

| Write Operation (Byte Write and Block Write)42      | PWM Timing in Resonant Mode82                    |

| EEPROM Password42                                   | Synchronous Rectification in Resonant Mode82     |

| Downloading EEPROM Settings to Internal Registers42 | Adjusting the Timing of the PWM Outputs83        |

| Saving Register Settings to the EEPROM43            | Frequency Limit Setting83                        |

| EEPROM CRC Checksum43                               | Feedback Control in Resonant Mode83              |

| Software GUI44                                      | Soft Start in Resonant Mode83                    |

| Register Listing45                                  | Light Load Operation (Burst Mode)83              |

| Detailed Register Descriptions48                    | OUTAUX Pin in Resonant Mode83                    |

| Fault Registers48                                   | Protections in Resonant Mode83                   |

| Value Registers51                                   | Resonant Mode Register Descriptions84            |

| Current Sense and Current Limit Registers54         | Outline Dimensions                               |

| Voltage Sense Registers59                           | Ordering Guide88                                 |

## **REVISION HISTORY**

2/13—Revision 0: Initial Version

# **SPECIFICATIONS**

$V_{\rm DD}$  = 3.0 V to 3.6 V,  $T_{\rm A}$  = -40°C to +125°C, unless otherwise noted. FSR = full-scale range.

Table 1.

| Parameter                                 | Symbol          | Test Conditions/Comments                                          | Min            | Тур          | Max      | Unit   |

|-------------------------------------------|-----------------|-------------------------------------------------------------------|----------------|--------------|----------|--------|

| SUPPLY                                    |                 |                                                                   |                |              |          |        |

| Supply Voltage                            | $V_{DD}$        | 4.7 μF capacitor connected to AGND                                | 3.0            | 3.3          | 3.6      | V      |

| Supply Current                            | I <sub>DD</sub> | Normal operation (PSON is high or low)                            |                | 20           |          | mA     |

|                                           |                 | During EEPROM programming (40 ms)                                 |                | $I_{DD} + 8$ |          | mA     |

|                                           |                 | Shutdown (V <sub>DD</sub> below UVLO)                             |                | 100          |          | μΑ     |

| POWER-ON RESET                            |                 |                                                                   |                |              |          |        |

| Power-On Reset                            |                 | V <sub>DD</sub> rising                                            |                |              | 3.0      | V      |

| UVLO                                      |                 | V <sub>DD</sub> falling                                           | 2.75           | 2.85         | 2.97     | V      |

| UVLO Hysteresis                           |                 |                                                                   |                | 40           |          | mV     |

| OVLO                                      |                 |                                                                   | 3.8            | 4.0          | 4.1      | V      |

| OVLO Debounce                             |                 | When set to 2 µs                                                  |                | 2.0          |          | μs     |

|                                           |                 | When set to 500 μs                                                |                | 500          |          | μs     |

| VCORE PIN                                 |                 | 0.33 μF capacitor connected to DGND                               |                |              |          | -      |

| Output Voltage                            |                 | $T_A = 25^{\circ}C$                                               | 2.4            | 2.5          | 2.7      | V      |

| OSCILLATOR AND PLL                        |                 |                                                                   |                |              |          | 1      |

| PLL Frequency                             |                 | RES = $10 \text{ k}\Omega \text{ ($\pm 0.1\%$)}$                  | 190            | 200          | 210      | MHz    |

| OUTA, OUTB, OUTC, OUTD,                   |                 | ,,                                                                |                |              | <u> </u> | _      |

| OUTAUX, SR1, SR2, GATE PINS               |                 |                                                                   |                |              |          |        |

| Output Low Voltage                        | V <sub>OL</sub> | Source current = 10 mA                                            |                |              | 0.4      | V      |

| Output High Voltage                       | V <sub>OH</sub> | Source current = 10 mA                                            | $V_{DD} - 0.4$ |              |          | V      |

| Rise Time                                 | OII             | $C_{LOAD} = 50 \text{ pF}$                                        | 55             | 3.5          |          | ns     |

| Fall Time                                 |                 | $C_{LOAD} = 50 \text{ pF}$                                        |                | 1.5          |          | ns     |

| VS1, VS2, VS3 LOW SPEED ADCs              |                 | LOND                                                              |                |              |          |        |

| Input Voltage Range                       | V <sub>IN</sub> | Differential voltage from VS1, VS2 to PGND, and from VS3+ to VS3- | 0              | 1            | 1.6      | V      |

| Usable Input Voltage Range                |                 |                                                                   | 0              |              | 1.4      | V      |

| ADC Clock Frequency                       |                 |                                                                   |                | 1.56         |          | MHz    |

| Register Update Rate                      |                 |                                                                   |                | 10           |          | ms     |

| Voltage Sense Measurement<br>Accuracy     |                 | Factory trimmed at 1.0 V                                          |                |              |          |        |

| ŕ                                         |                 | 0% to 100% of usable input voltage range                          | -3.0           |              | +3.0     | % FSR  |

|                                           |                 |                                                                   | -48            |              | +48      | mV     |

|                                           |                 | 10% to 90% of usable input voltage range                          | -2.0           |              | +2.0     | % FSR  |

|                                           |                 |                                                                   | -32            |              | +32      | mV     |

|                                           |                 | 900 mV to 1.1 V                                                   | -1.0           |              | +1.0     | % FSR  |

|                                           |                 |                                                                   | -16            |              | +16      | mV     |

| Temperature Coefficient                   |                 |                                                                   |                |              | 65       | ppm/°C |

| Leakage Current                           |                 |                                                                   |                |              | 1.0      | μΑ     |

| Voltage Sense Measurement<br>Resolution   |                 |                                                                   |                | 12           |          | Bits   |

| Common-Mode Voltage Offset                |                 |                                                                   | -0.25          |              | +0.25    | % FSR  |

| Voltage Differential from VS3–<br>to PGND |                 |                                                                   | -200           |              | +200     | mV     |

| VS1 Accurate OVP Speed                    |                 | Register 0x32[1:0] = 00; equivalent resolution is 7 bits          |                | 80           |          | μs     |

| VS1 OVP Threshold Accuracy                |                 | Relative to nominal voltage (1 V) on VS1                          | -2.0           |              | +2.0     | % FSR  |

| VS2 and VS3 OVP Speed                     |                 | Register 0x33[1:0] = 00; equivalent resolution is 7 bits          |                | 80           |          | μs     |

| VS2 and VS3 OVP Threshold<br>Accuracy     |                 | Relative to nominal voltage (1 V) on VS2 and VS3                  | -2.0           |              | +2.0     | % FSR  |

Rev. 0 | Page 4 of 88

| Parameter                                            | Symbol             | Test Conditions/Comments                                     | Min   | Тур      | Max   | Unit  |

|------------------------------------------------------|--------------------|--------------------------------------------------------------|-------|----------|-------|-------|

| VS3 HIGH SPEED ADC                                   |                    |                                                              |       |          |       |       |

| Equivalent Sampling<br>Frequency                     | f <sub>SAMP</sub>  |                                                              |       | $f_{sw}$ |       | kHz   |

| <b>Equivalent Resolution</b>                         |                    | $f_{SW} = 390.6 \text{ kHz}$                                 |       | 6        |       | Bits  |

| Dynamic Range                                        |                    |                                                              |       | ±30      |       | mV    |

| VS1 FAST OVP COMPARATOR                              |                    |                                                              |       |          |       |       |

| Threshold Accuracy                                   |                    | At factory trim of 1.2 V                                     |       | 1        | 1.60  | %     |

|                                                      |                    | At other thresholds (0.8 V to 1.6 V)                         | -2.06 |          | +2.06 | %     |

| Propagation Delay                                    |                    | Does not include debounce time (Register 0x0A[7] = 1)        |       | 40       |       | ns    |

| VS1 UVP DIGITAL COMPARATOR                           |                    |                                                              |       |          |       |       |

| VS1 UVP Accuracy                                     |                    |                                                              | -2.0  |          | +2.0  | % FSR |

| Propagation Delay                                    |                    | Does not include debounce time (Register 0x0B[3] = 1)        |       | 80       |       | μs    |

| AC SENSE COMPARATOR                                  |                    | PWM and resonant mode                                        |       |          |       |       |

| Input Voltage Threshold                              |                    |                                                              | 0.4   | 0.45     | 0.5   | V     |

| Propagation Delay                                    |                    | From ACSNS threshold to SRx rising edge (resonant mode only) |       | 160      |       | ns    |

| ADC Clock Frequency                                  |                    |                                                              |       | 1.56     |       | MHz   |

| Input Voltage Range                                  | V <sub>ACSNS</sub> |                                                              | 0     | 1        | 1.6   | V     |

| Usable Input Voltage Range                           | riesiis            |                                                              | 0     |          | 1.4   | V     |

| Sampling Frequency for I <sup>2</sup> C<br>Reporting |                    |                                                              |       | 100      |       | Hz    |

| Sampling Period for<br>Feedforward                   |                    | Equivalent resolution is 11 bits                             |       | 10       |       | μs    |

| Measurement Accuracy                                 |                    | Factory trimmed at 1.0 V                                     |       |          |       |       |

| ŕ                                                    |                    | 0% to 100% of usable input voltage range                     | -5.0  |          | +3.0  | % FSR |

|                                                      |                    | 10% to 90% of usable input voltage range                     | -2.0  |          | +2.0  | % FSR |

|                                                      |                    | 900 mV to 1.1 V                                              | -1.0  |          | +1.0  | % FSR |

|                                                      |                    |                                                              | -16   |          | +16   | mV    |

| Leakage Current                                      |                    |                                                              |       |          | 1.0   | μΑ    |

| CURRENT SENSE 1 (CS1 PIN)                            |                    |                                                              |       |          |       |       |

| Input Voltage Range                                  | V <sub>IN</sub>    |                                                              | 0     | 1        | 1.4   | V     |

| Usable Input Voltage Range                           |                    |                                                              | 0     |          | 1.3   | V     |

| ADC Clock Frequency                                  |                    |                                                              |       | 1.56     |       | MHz   |

| Register Update Rate                                 |                    |                                                              |       | 10       |       | ms    |

| Current Sense Measurement<br>Accuracy                |                    | Factory trimmed at 0.7 V; tested under dc input conditions   |       |          |       |       |

|                                                      |                    | 10% to 50% of usable input voltage range                     | -3.0  |          | +3.0  | % FSR |

|                                                      |                    |                                                              | -41.4 |          | +41.4 | mV    |

|                                                      |                    | 0% to 100% of usable input voltage range                     | -6.0  |          | +3.0  | % FSR |

|                                                      |                    |                                                              | -84   |          | +42   | mV    |

|                                                      |                    | 40% to 60% of usable input voltage range                     | -1.0  |          | +1.0  | % FSR |

| Current Sense Measurement<br>Resolution              |                    |                                                              |       | 12       |       | Bits  |

| CS1 Fast OCP Threshold                               |                    |                                                              | 1.184 | 1.2      | 1.216 | V     |

| CS1 Fast OCP Speed                                   |                    |                                                              |       | 80       | 100   | ns    |

| CS1 Accurate OCP DC Accuracy                         |                    | 10% to 90% of usable input voltage range                     | -2.0  |          | +2.0  | % FSR |

| ŕ                                                    |                    |                                                              | -28   |          | +28   | mV    |

| CS1 Accurate OCP Speed                               |                    |                                                              |       | 2.62     | 5.24  | ms    |

| Leakage Current                                      |                    |                                                              |       |          | 1.0   | μΑ    |

| Parameter                                        | Symbol          | Test Conditions/Comments                                        | Min    | Тур    | Max    | Unit   |

|--------------------------------------------------|-----------------|-----------------------------------------------------------------|--------|--------|--------|--------|

| CURRENT SENSE 2 (CS2+, CS2–<br>PINS)             |                 |                                                                 |        |        |        |        |

| Input Voltage Range                              | V <sub>IN</sub> | Differential voltage from CS2+ to CS2-,<br>LSB = 29.297 $\mu$ V | 0      |        | 120    | mV     |

| Usable Input Voltage Range                       |                 |                                                                 | 0      |        | 110    | mV     |

| ADC Clock Frequency                              |                 |                                                                 |        | 1.56   |        | MHz    |

| Temperature Coefficient                          |                 |                                                                 |        |        |        |        |

| 120 mV Range                                     |                 | 0 mV to 100 mV                                                  |        |        | 78     | ppm/°C |

|                                                  |                 | 0 mV to 50 mV                                                   |        |        | 70     | ppm/°C |

| 60 mV Range                                      |                 | 0 mV to 50 mV                                                   |        |        | 156    | ppm/°C |

|                                                  |                 | 0 mV to 25 mV                                                   |        |        | 140    | ppm/°C |

| Current Sense Measurement                        |                 |                                                                 |        |        |        |        |

| 120 mV Setting                                   |                 | 0 mV to 110 mV                                                  | -2.1   |        | +2.1   | % FSR  |

|                                                  |                 |                                                                 | -2.52  |        | +2.52  | mV     |

| 60 mV Setting                                    |                 | 0 mV to 55 mV                                                   | -4.2   |        | +4.2   | % FSR  |

|                                                  |                 |                                                                 | -5.04  |        | +5.04  | mV     |

| Current Sense Measurement<br>Accuracy            |                 | With 0.01% level shifting resistors                             |        |        |        |        |

| 120 mV Setting                                   |                 | $0 \text{ mV to } 100 \text{ mV}, V_{DD} = 3.3 \text{ V}$       | -0.9   |        | +0.9   | % FSR  |

|                                                  |                 |                                                                 | -1.08  |        | +1.08  | mV     |

| 60 mV Setting                                    |                 | $0 \text{ mV to } 55 \text{ mV, V}_{DD} = 3.3 \text{ V}$        | -1.8   |        | +1.8   | % FSR  |

|                                                  |                 |                                                                 | -2.16  |        | +2.16  | mV     |

| Current Sense Measurement<br>Resolution          |                 |                                                                 |        | 12     |        | Bits   |

| CS2 Accurate OCP Speed                           |                 |                                                                 |        | 2.62   | 5.24   | ms     |

| Current Sink (High Side)                         |                 |                                                                 |        | 2      |        | mA     |

| Current Source (Low Side)                        |                 |                                                                 |        | 200    |        | μΑ     |

| Common-Mode Voltage at the<br>CS2+ and CS2– Pins |                 | To achieve CS2 measurement accuracy                             | 0.8    | 1.0    | 1.4    | V      |

| OrFET PROTECTION (CS2+, CS2-)                    |                 | Low-side and high-side current sensing                          |        |        |        |        |

| Fast OrFET Accuracy                              |                 | −3 mV setting                                                   | +3.5   | -3.00  | -9.5   | mV     |

|                                                  |                 | –6 mV setting                                                   | +0.29  | -6.21  | -12.71 | mV     |

|                                                  |                 | –9 mV setting                                                   | -2.68  | -9.43  | -16.18 | mV     |

|                                                  |                 | –12 mV setting                                                  | -5.89  | -12.64 | -19.39 | mV     |

|                                                  |                 | –15 mV setting                                                  | -9.01  | -15.86 | -22.71 | mV     |

|                                                  |                 | –18 mV setting                                                  | -12.22 | -19.07 | -25.92 | mV     |

|                                                  |                 | –21 mV setting                                                  | -15.29 | -22.29 | -29.29 | mV     |

|                                                  |                 | –24 mV setting                                                  | -18.50 | -25.50 | -32.50 | mV     |

| Fast OrFET Speed                                 |                 | Debounce = 40 ns                                                |        | 110    | 150    | ns     |

| RTD TEMPERATURE SENSE                            |                 |                                                                 |        |        |        | 1      |

| ADC Clock Frequency                              |                 |                                                                 |        | 1.56   |        | MHz    |

| Input Voltage Range                              |                 | RTD to AGND                                                     | 0      |        | 1.6    | V      |

| Usable Input Voltage Range                       |                 |                                                                 | 0      |        | 1.3    | V      |

| Source Current                                   |                 | Factory trimmed to 46 μA (Register 0x11 set to 0xE6)            | 44.35  | 46     | 47.65  | μΑ     |

|                                                  |                 | Current source set to 10 μA                                     | 9.25   | 10.1   | 10.85  | μΑ     |

|                                                  |                 | Current source set to 20 μA                                     | 18.35  | 20.1   | 21.85  | μΑ     |

|                                                  |                 | Current source set to 30 μA                                     | 28.45  | 30.2   | 31.95  | μΑ     |

|                                                  |                 | Current source set to 40 μA                                     | 38.45  | 40.3   | 41.95  | μΑ     |

| Source Current Fine Setting RTD ADC              |                 | See Register 0x11[5:0]                                          |        | 160    |        | nA     |

| Register Update Rate                             |                 |                                                                 |        | 10     |        | ms     |

| Resolution                                       |                 |                                                                 |        | 12     |        | Bits   |

| Parameter                                                   | Symbol               | Test Conditions/Comments                                                                                                                  | Min                   | Тур  | Max        | Unit  |

|-------------------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------|------------|-------|

| Measurement Accuracy                                        |                      | Factory trimmed at 1 V                                                                                                                    |                       |      |            |       |

| •                                                           |                      | 10 mV to 160 mV                                                                                                                           | -0.5                  |      | +0.5       | % FSR |

|                                                             |                      |                                                                                                                                           | -8                    |      | +8         | mV    |

|                                                             |                      | 0% to 100% of usable input voltage range                                                                                                  | -3.0                  |      | +3.0       | % FSR |

|                                                             |                      |                                                                                                                                           | -42                   |      | +42        | mV    |

| Temperature Readings Using<br>Internal Linearization Scheme |                      | RTD source set to 46 $\mu$ A (Register 0x11 set to 0xE6); NTC R0 = 100 k $\Omega$ , 1%; beta = 4250, 1%; $R_{EXT}$ = 16.5 k $\Omega$ , 1% | -                     |      |            |       |

|                                                             |                      | 25°C to 100°C                                                                                                                             |                       |      | 7          | °C    |

|                                                             |                      | 100°C to 125°C                                                                                                                            |                       |      | 5          | °C    |

| OTP                                                         |                      |                                                                                                                                           |                       |      |            |       |

| Threshold Accuracy                                          |                      | T = 85°C with 100 kΩ  16.5 kΩ                                                                                                             | -0.9                  |      | +0.25      | % FSR |

|                                                             |                      |                                                                                                                                           | -14.4                 |      | +4         | mV    |

|                                                             |                      | T = 100°C with 100 kΩ  16.5 kΩ                                                                                                            | -0.5                  |      | +1.1       | % FSR |

|                                                             |                      |                                                                                                                                           | -8                    |      | +17.6      | mV    |

| Comparator Speed                                            |                      |                                                                                                                                           |                       | 10.5 |            | ms    |

| OTP Threshold Hysteresis                                    |                      |                                                                                                                                           |                       | 16   |            | mV    |

| PGOOD1, PGOOD2, SHAREo PINS                                 |                      | Open-drain outputs                                                                                                                        |                       |      |            |       |

| Output Low Voltage                                          | V <sub>OL</sub>      | ·                                                                                                                                         |                       |      | 0.4        | V     |

| PSON, SHAREI PINS                                           | OL.                  | Digital inputs                                                                                                                            |                       |      |            |       |

| Input Low Voltage                                           | V <sub>IL</sub>      |                                                                                                                                           |                       |      | 0.8        | V     |

| Input High Voltage                                          | V <sub>IH</sub>      |                                                                                                                                           | $V_{DD} - 0.8$        |      |            | V     |

| Leakage Current                                             | * IH                 |                                                                                                                                           | 100 0.0               |      | 1.0        | μA    |

| FLAGIN PIN                                                  |                      | Digital input                                                                                                                             |                       |      | 1.0        | μιτ   |

| Input Low Voltage                                           | V <sub>IL</sub>      |                                                                                                                                           |                       |      | 0.4        | V     |

| Input High Voltage                                          | V <sub>IL</sub>      |                                                                                                                                           | V <sub>DD</sub> - 0.8 |      | 0.4        | v     |

| Propagation Delay                                           | V IH                 | Does not include debounce time (Register                                                                                                  | V <sub>DD</sub> — 0.0 | 200  |            | - T   |

| Fropagation Delay                                           |                      | 0x0A[3] = 1); flag action set to disable PSU                                                                                              |                       | 200  |            | ns    |

| Leakage Current                                             |                      |                                                                                                                                           |                       |      | 1.0        | μΑ    |

| GATE PIN                                                    |                      |                                                                                                                                           |                       |      |            | 1.    |

| Output Low Voltage                                          | V <sub>OL</sub>      |                                                                                                                                           |                       |      | 0.4        | V     |

| Output High Voltage                                         | V <sub>OH</sub>      |                                                                                                                                           | V <sub>DD</sub> - 0.4 |      | 0.1        | v     |

| SDA/SCL PINS                                                | OH                   | V <sub>DD</sub> = 3.3 V                                                                                                                   | • DD • O. I           |      |            |       |

| Input Low Voltage                                           | V <sub>IL</sub>      | V <sub>DD</sub> = 3.3 V                                                                                                                   |                       |      | 0.8        | V     |

| Input High Voltage                                          | V <sub>IL</sub>      |                                                                                                                                           | V <sub>DD</sub> - 0.8 |      | 0.0        | v     |

| Output Low Voltage                                          |                      |                                                                                                                                           | V <sub>DD</sub> - 0.8 |      | 0.4        | v     |

| Leakage Current                                             | V <sub>OL</sub>      |                                                                                                                                           |                       |      | 0.4<br>1.0 |       |

|                                                             |                      | Con Figure 2                                                                                                                              |                       |      | 1.0        | μΑ    |

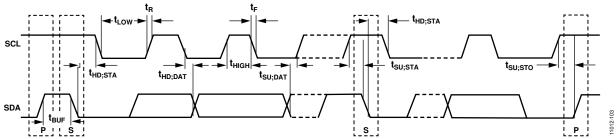

| SERIAL BUS TIMING                                           |                      | See Figure 2                                                                                                                              | 10                    | 100  | 400        | 1.11= |

| Clock Operating Frequency                                   |                      |                                                                                                                                           | 10                    | 100  | 400        | kHz   |

| Bus-Free Time                                               | t <sub>BUF</sub>     | Between stop and start conditions                                                                                                         | 1.3                   |      |            | μs    |

| Start Hold Time                                             | t <sub>HD;STA</sub>  | Hold time after (repeated) start condition; after this period, the first clock is generated                                               | 0.6                   |      |            | μs    |

| Start Setup Time                                            | t <sub>SU;STA</sub>  | Repeated start condition setup time                                                                                                       | 0.6                   |      |            | μs    |

| Stop Setup Time                                             | t <sub>su;sto</sub>  |                                                                                                                                           | 0.6                   |      |            | μs    |

| SDA Setup Time                                              | t <sub>SU;DAT</sub>  |                                                                                                                                           | 100                   |      |            | ns    |

| SDA Hold Time                                               | t <sub>HD;DAT</sub>  | For readback                                                                                                                              | 125                   |      |            | ns    |

|                                                             | ,                    | For write                                                                                                                                 | 300                   |      |            | ns    |

| SCL Low Timeout                                             | t <sub>TIMEOUT</sub> |                                                                                                                                           | 25                    |      | 35         | ms    |

| SCL Low Period                                              | t <sub>LOW</sub>     |                                                                                                                                           | 1.3                   |      |            | μs    |

| SCL High Period                                             | t <sub>HIGH</sub>    |                                                                                                                                           | 0.6                   |      |            | μs    |

| Clock Low Extend Time                                       | t <sub>LO:SEXT</sub> |                                                                                                                                           |                       |      | 25         | ms    |

| CIOCK LOW EXTERIO TITLE                                     |                      |                                                                                                                                           | Ī                     |      | -          | 1 1   |

| SCL, SDA Fall Time                                          | t <sub>F</sub>       |                                                                                                                                           | 20                    |      | 300        | ns    |

| Parameter                   | Symbol | Test Conditions/Comments | Min    | Тур | Max | Unit   |

|-----------------------------|--------|--------------------------|--------|-----|-----|--------|

| EEPROM RELIABILITY          |        |                          |        |     |     |        |

| Endurance <sup>1</sup>      |        | T <sub>J</sub> = 85°C    | 10,000 |     |     | Cycles |

|                             |        | T <sub>J</sub> = 125°C   | 1000   |     |     | Cycles |

| Data Retention <sup>2</sup> |        | T <sub>J</sub> = 85°C    | 20     |     |     | Years  |

|                             |        | T <sub>J</sub> = 125°C   | 10     |     |     | Years  |

<sup>&</sup>lt;sup>1</sup> Endurance is qualified as per JEDEC Standard 22, Method A117, and is measured at –40°C, +25°C, +85°C, and +125°C. Endurance conditions are subject to change pending EEPROM qualification.

<sup>2</sup> Retention lifetime equivalent at junction temperature (T<sub>J</sub>) = 85°C as per JEDEC Standard 22, Method A117. The derated retention lifetime equivalent at junction temperature T<sub>J</sub> = 125°C is 2.87 years and is subject to change pending EEPROM qualification.

## **Timing Diagram**

Figure 2. Serial Bus Timing Diagram

## **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| 1 able 2.                                                                          |                                            |

|------------------------------------------------------------------------------------|--------------------------------------------|

| Parameter                                                                          | Rating                                     |

| Supply Voltage (Continuous), V <sub>DD</sub>                                       | 4.2 V                                      |

| Digital Pins: OUTA, OUTB, OUTC, OUTD,<br>OUTAUX, SR1, SR2, GATE, PGOOD1,<br>PGOOD2 | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$ |

| VS3- to PGND, AGND, DGND                                                           | −0.3 V to +0.3 V                           |

| VS1, VS2, VS3+, ACSNS                                                              | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$ |

| RTD, ADD                                                                           | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$ |

| CS1, CS2+, CS2-                                                                    | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$ |

| FLAGIN, PSON                                                                       | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$ |

| SDA, SCL                                                                           | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$ |

| SHAREo, SHAREi                                                                     | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$ |

| Operating Temperature Range                                                        | −40°C to +125°C                            |

| Storage Temperature Range                                                          | −65°C to +150°C                            |

| Junction Temperature                                                               | 150°C                                      |

| Peak Solder Reflow Temperature                                                     |                                            |

| SnPb Assemblies (10 sec to 30 sec)                                                 | 240°C                                      |

| RoHS-Compliant Assemblies (20 sec to 40 sec)                                       | 260°C                                      |

| ESD Charged Device Model                                                           | 1.5 kV                                     |

| ESD Human Body Model                                                               | 3.5 kV                                     |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

**Table 3. Thermal Resistance**

| Package Type  | $\theta_{JA}$ | θ <sub>JC</sub> | Unit |

|---------------|---------------|-----------------|------|

| 32-Lead LFCSP | 44.4          | 6.4             | °C/W |

#### **SOLDERING**

It is important to follow the correct guidelines when laying out the PCB footprint for the ADP1046A and when soldering the part onto the PCB. For detailed information about these guidelines, see the AN-772 Application Note.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

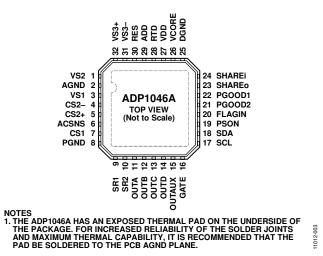

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 3. Pin Configuration

**Table 4. Pin Function Descriptions**

| Pin No. | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

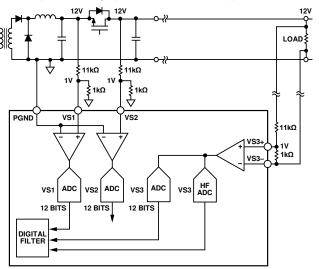

| 1       | VS2      | Power Supply Output Voltage Sense Input. This signal is referenced to PGND and is the input to a low frequency $\Sigma$ - $\Delta$ ADC. Nominal voltage at this pin should be 1 V. The resistor divider on this input must have a tolerance specification of 0.5% or better to allow for trimming.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2       | AGND     | Analog Ground. This pin is the ground for the analog circuitry and the return for the VDD pin of the ADP1046A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3       | VS1      | Local Output Voltage Sense Input. This signal is referenced to PGND. Nominal voltage at this pin should be 1 V. The resistor divider on this input must have a tolerance specification of 0.5% or better to allow for trimming.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

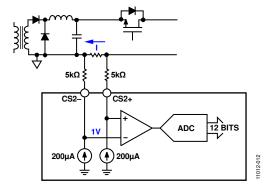

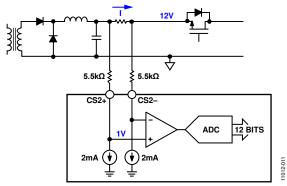

| 4       | CS2-     | Inverting Differential Current Sense Input. Nominal voltage at this pin should be 1 V for best operation. When using low-side current sensing, place a 5 k $\Omega$ resistor between the sense resistor and this pin. When using high-side current sensing in a 12 V application, place a 5.5 k $\Omega$ resistor between the sense resistor and this pin. When using high-side current sensing with a voltage other than 12 V, use the following formula to calculate the resistor value: R = ( $V_{OUT} - 1$ )/2 mA. A 0.1% resistor must be used to connect this circuit. If this pin is not used, connect it to PGND and set CS2± to high-side current sense mode (set Bit 2 of Register 0x27). It is recommended that a 500 pF to 1000 pF capacitor be connected either across the resistor or from this pin to AGND.    |

| 5       | CS2+     | Noninverting Differential Current Sense Input. Nominal voltage at this pin should be 1 V for best operation. When using low-side current sensing, place a 5 k $\Omega$ resistor between the sense resistor and this pin. When using high-side current sensing in a 12 V application, place a 5.5 k $\Omega$ resistor between the sense resistor and this pin. When using high-side current sensing with a voltage other than 12 V, use the following formula to calculate the resistor value: R = ( $V_{OUT} - 1$ )/2 mA. A 0.1% resistor must be used to connect this circuit. If this pin is not used, connect it to PGND and set CS2± to high-side current sense mode (set Bit 2 of Register 0x27). It is recommended that a 500 pF to 1000 pF capacitor be connected either across the resistor or from this pin to AGND. |

| 6       | ACSNS    | AC Sense Input. This input is connected upstream of the main output inductor through a resistor divider network. The nominal voltage for this circuit is 0.45 V. This pin is also connected to the voltage feedforward ADC (nominal voltage 1 V). This signal is referenced to PGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 7       | CS1      | Primary Side Current Sense Input. This pin is connected to the primary side current sensing ADC and to the fast OCP comparator. This signal is referenced to PGND. The resistors on this input must have a tolerance specification of 0.5% or better to allow for trimming. If this pin is not used, connect it to PGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 8       | PGND     | Power Ground. This pin is the ground connection for the main power rail of the power supply and is the reference for all voltage and current sensing other than CS2± and VS3±. Star connect to AGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 9       | SR1      | Synchronous Rectifier Output. This PWM output connects to the input of a FET driver. This signal is referenced to AGND. This pin can be disabled when not in use.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 10      | SR2      | Synchronous Rectifier Output. This PWM output connects to the input of a FET driver. This signal is referenced to AGND. This pin can be disabled when not in use.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 11      | OUTA     | PWM Output for Primary Side Switch. This signal is referenced to AGND. This pin can be disabled when not in use.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 12      | OUTB     | PWM Output for Primary Side Switch. This signal is referenced to AGND. This pin can be disabled when not in use.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 13      | OUTC     | PWM Output for Primary Side Switch. This signal is referenced to AGND. This pin can be disabled when not in use.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Pin No. | Mnemonic | Description                                                                                                                                                                                                                                                                                                        |

|---------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14      | OUTD     | PWM Output for Primary Side Switch. This signal is referenced to AGND. This pin can be disabled when not in use.                                                                                                                                                                                                   |

| 15      | OUTAUX   | Auxiliary PWM Output. This signal is referenced to AGND. This pin can be disabled when not in use.                                                                                                                                                                                                                 |

| 16      | GATE     | OrFET Gate Drive Output. This signal is referenced to AGND. If this pin is not used, leave it floating.                                                                                                                                                                                                            |

| 17      | SCL      | I <sup>2</sup> C Serial Clock Input. This signal is referenced to AGND.                                                                                                                                                                                                                                            |

| 18      | SDA      | I <sup>2</sup> C Serial Data Input and Output (Open Drain). This signal is referenced to AGND.                                                                                                                                                                                                                     |

| 19      | PSON     | Power Supply On Input. This signal is referenced to AGND. This pin is the hardware PSON control signal. It is recommended that a 1 nF capacitor be connected from the PSON pin to AGND for noise debouncing and decoupling.                                                                                        |

| 20      | FLAGIN   | Flag Input. An external signal can be input at this pin to generate a flag condition.                                                                                                                                                                                                                              |

| 21      | PGOOD2   | Power-Good Output (Open Drain). This signal is referenced to AGND. This pin is controlled by the PGOOD2 flag. This pin is set by a programmable combination of internal flags. If this pin is not used, connect it to AGND.                                                                                        |

| 22      | PGOOD1   | Power-Good Output (Open Drain). This signal is referenced to AGND. This pin is controlled by the PGOOD1 flag. This pin is set by a programmable combination of internal flags. If this pin is not used, connect it to AGND.                                                                                        |

| 23      | SHAREo   | Share Bus Output Voltage Pin. Connect this pin to 3.3 V through a pull-up resistor (typically 2.2 k $\Omega$ ). When configured for a digital share bus, this pin is a digital output. This signal is referenced to AGND. If this pin is not used, connect it to AGND.                                             |

| 24      | SHAREi   | Share Bus Feedback Pin. Connect this pin to the SHAREo pin. This signal is referenced to AGND. If this pin is not used, connect it to AGND.                                                                                                                                                                        |

| 25      | DGND     | Digital Ground. This pin is the ground reference for the digital circuitry of the ADP1046A. Star connect to AGND.                                                                                                                                                                                                  |

| 26      | VCORE    | Output of the 2.5 V Regulator. Connect a decoupling capacitor of at least 330 nF (1 µF maximum) from this pin to DGND as close to the IC as possible to minimize PCB trace length. It is recommended that the VCORE pin not be used as a reference or to generate other logic levels using resistive dividers.     |

| 27      | VDD      | Positive Supply Input. This signal is referenced to AGND. Connect a 4.7 µF decoupling capacitor from this pin to AGND as close to the IC as possible to minimize PCB trace length.                                                                                                                                 |

| 28      | RTD      | Thermistor Input. Place a thermistor (100 k $\Omega$ , 1%; beta = 4250, 1%) in parallel with a 16.5 k $\Omega$ , 1% resistor. This pin is referenced to AGND. If this pin is not used, connect it to AGND.                                                                                                         |

| 29      | ADD      | Address Select Input. This pin is used to program the I <sup>2</sup> C address. Connect a resistor from ADD to AGND. This signal is referenced to AGND.                                                                                                                                                            |

| 30      | RES      | Resistor Input. This pin sets up the internal voltage reference for the ADP1046A. Connect a 10 k $\Omega$ , $\pm$ 0.1% resistor from RES to AGND. This signal is referenced to AGND.                                                                                                                               |

| 31      | VS3-     | Inverting Remote Voltage Sense Input. There should be a low ohmic connection to AGND. The resistor divider on this input must have a tolerance specification of 0.5% or better to allow for trimming. Connect a 0.1 $\mu$ F capacitor from VS3— to AGND.                                                           |

| 32      | VS3+     | Noninverting Remote Voltage Sense Input. This signal is referenced to VS3—, and the nominal input voltage at this pin is 1 V. The resistor divider on this input must have a tolerance specification of 0.5% or better to allow for trimming. This pin is the input to the high frequency $\Delta$ - $\Sigma$ ADC. |

|         | EP       | Exposed Pad. The ADP1046A has an exposed thermal pad on the underside of the package. For increased reliability of the solder joints and maximum thermal capability, it is recommended that the pad be soldered to the PCB AGND plane.                                                                             |

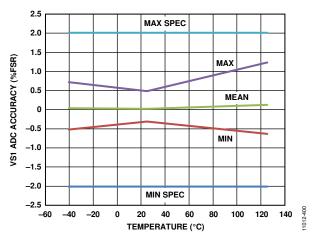

## TYPICAL PERFORMANCE CHARACTERISTICS

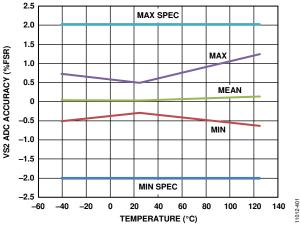

Figure 4. VS1 ADC Accuracy vs. Temperature (from 10% to 90% of FSR)

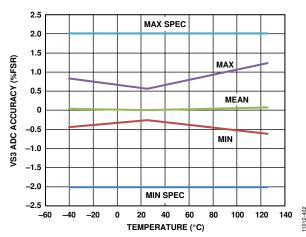

Figure 5. VS2 ADC Accuracy vs. Temperature (from 10% to 90% of FSR)

Figure 6. VS3 ADC Accuracy vs. Temperature (from 10% to 90% of FSR)

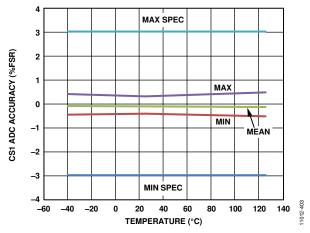

Figure 7. CS1 ADC Accuracy vs. Temperature (from 10% to 50% of FSR)

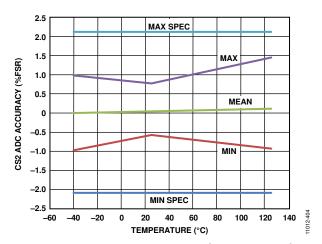

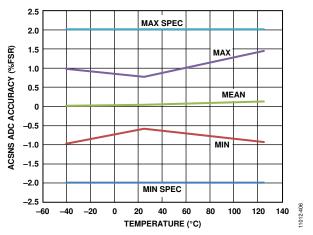

Figure 8. CS2 ADC Accuracy vs. Temperature (from 10% to 90% of FSR)

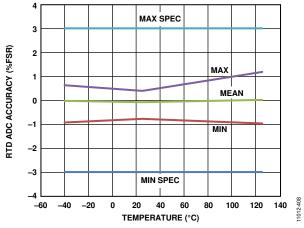

Figure 9. RTD ADC Accuracy vs. Temperature (from 10% to 90% of FSR)

Figure 10. ACSNS ADC Accuracy vs. Temperature (from 10% to 90% of FSR)

Figure 11. CS1 Fast OCP Threshold vs. Temperature

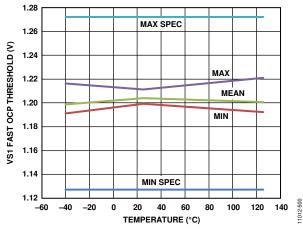

Figure 12. VS1 Fast OCP Threshold vs. Temperature

## THEORY OF OPERATION

The ADP1046A is a secondary side controller for switch mode power supplies. It is designed for use in isolated redundant applications. The ADP1046A integrates the typical functions that are needed to control a power supply, such as

- Output voltage sense and feedback

- Voltage line feedforward control

- Digital loop filter compensation

- PWM generation

- Current sharing

- Current, voltage, and temperature sense

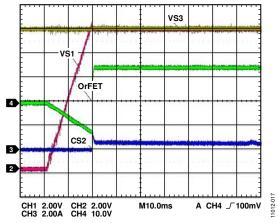

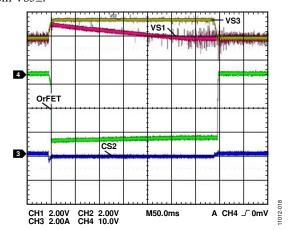

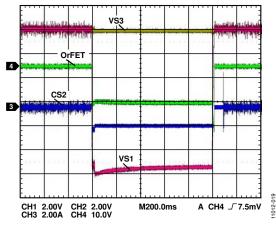

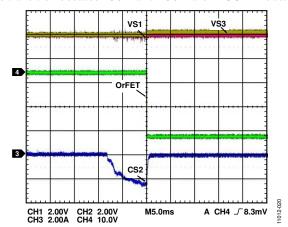

- OrFET control