# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

**Data Sheet**

# Photometric Front End

# ADPD103

# FEATURES

**Multifunction photometric front end** Fully integrated AFE, ADC, LED drivers, and timing core Usable in a broad range of optical measurement applications, including photoplethysmography Enables best-in-class ambient light rejection capability without the need for photodiode optical filters Three 8 mA to 250 mA LED drivers Separate data registers for each LED/photodiode combination 1 to 8 optical inputs Flexible, multiple, short LED pulses per optical sample 20-bit burst accumulator enabling 20 bits per sample period On-board sample to sample accumulator, enabling up to 27 bits per data read Low power operation I<sup>2</sup>C interface and 1.8 V analog/digital core Flexible sampling frequency ranging from 0.122 Hz to 3.820 kHz **FIFO data operation** APPLICATIONS

Body worn health and fitness monitors, for example, heart rate monitoring Clinical measurements, for example, SpO<sub>2</sub> Industrial monitoring Background light measurements

# **GENERAL DESCRIPTION**

The ADPD103 is a highly efficient photometric front end with an integrated 14-bit analog-to-digital converter (ADC) and a 20-bit burst accumulator that works in concert with flexible light emitting diode (LED) drivers. It is designed to stimulate an LED and measure the corresponding optical return signal. The data output and functional configuration occur over a 1.8 V I<sup>2</sup>C interface. The control circuitry includes flexible LED signaling and synchronous detection.

The analog front end (AFE) features best-in-class rejection of signal offset and corruption due to modulated interference commonly caused by ambient light.

Couple the ADPD103 with a low capacitance photodiode of <100 pF for optimal performance. The ADPD103 can be used with any LED.

#### Rev. B

#### Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

# ADPD103\* PRODUCT PAGE QUICK LINKS

Last Content Update: 02/23/2017

# COMPARABLE PARTS

View a parametric search of comparable parts.

# EVALUATION KITS

ADPD103 Evaluation Board

# DOCUMENTATION

# Data Sheet

ADPD103: Photometric Front End Data Sheet

# **User Guides**

• UG-947: Evaluating the ADPD103 Photometric Front End

# DESIGN RESOURCES

## ADPD103 Material Declaration

- PCN-PDN Information

- Quality And Reliability

- Symbols and Footprints

# DISCUSSIONS

View all ADPD103 EngineerZone Discussions.

# SAMPLE AND BUY

Visit the product page to see pricing options.

# TECHNICAL SUPPORT

Submit a technical question or find your regional support number.

# DOCUMENT FEEDBACK

Submit feedback for this data sheet.

# TABLE OF CONTENTS

| Features 1                                   |

|----------------------------------------------|

| Applications                                 |

| General Description                          |

| Revision History                             |

| Functional Block Diagram                     |

| Specifications                               |

| Temperature and Power Specifications         |

| Performance Specifications                   |

| Analog Specifications                        |

| Digital Specifications7                      |

| Timing Specifications                        |

| Absolute Maximum Ratings                     |

| Thermal Resistance                           |

| Recommended Soldering Profile9               |

| ESD Caution                                  |

| Pin Configurations and Function Descriptions |

| Typical Performance Characteristics          |

| Theory of Operation                          |

| Introduction                                 |

| Dual Time Slot Operation                     |

| Time Slot Switch                             |

| Adjustable Sampling Frequency                |

| State Machine Operation16                    |

| Normal Mode Operation and Data Flow16        |

| AFE Operation                                |

|                                              |

#

| AFE Integration Offset Adjustment      |

|----------------------------------------|

| I <sup>2</sup> C Serial Interface      |

| Typical Connection Diagram 21          |

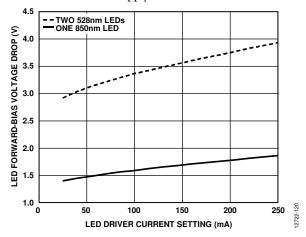

| LED Driver Pins and LED Supply Voltage |

| LED Driver Operation                   |

| Determining the Average Current        |

| $Determining  C_{\text{VLED}}  23$     |

| LED Inductance Considerations          |

| Recommended Start-Up Sequence          |

| Reading Data24                         |

| Clocks and Timing Calibration          |

| Calculating Current Consumption        |

| Optimizing SNR per Watt 27             |

| Single AFE channel mode 28             |

| TIA_ADC Mode                           |

| Digital Integrate Mode                 |

| egister Listing                        |

| LED Control Registers                  |

| AFE Configuration Registers            |

| System Registers                       |

| ADC Registers                          |

| Data Registers                         |

| utline Dimensions                      |

| Ordering Guide                         |

# **REVISION HISTORY**

2/16—Revision B: Initial Version

12722-001

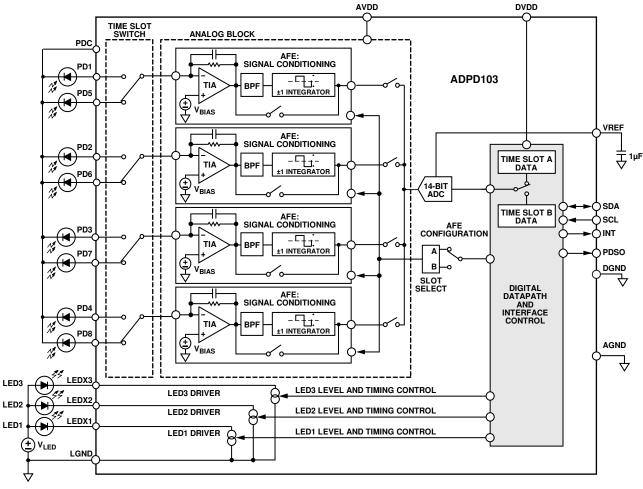

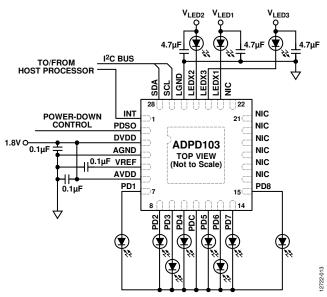

# FUNCTIONAL BLOCK DIAGRAM

Figure 1. Typical Functional Block Diagram

# **SPECIFICATIONS**

# **TEMPERATURE AND POWER SPECIFICATIONS**

### **Table 1. Operating Conditions**

| Parameter             | Test Conditions/Comments          | Min | Тур | Мах  | Unit |

|-----------------------|-----------------------------------|-----|-----|------|------|

| TEMPERATURE RANGE     |                                   |     |     |      |      |

| Operating Range       |                                   | -40 |     | +85  | °C   |

| Storage Range         |                                   | -65 |     | +150 | °C   |

| POWER SUPPLY VOLTAGES |                                   |     |     |      |      |

| V <sub>DD</sub>       | Applied at the AVDD and DVDD pins | 1.7 | 1.8 | 1.9  | V    |

AVDD = DVDD = 1.8 V, ambient temperature, unless otherwise noted.

#### Table 2. Current Consumption<sup>1, 2</sup>

| Parameter                                      | Symbol                   | Test Conditions/Comments                                  | Min | Тур | Max | Unit |

|------------------------------------------------|--------------------------|-----------------------------------------------------------|-----|-----|-----|------|

| POWER SUPPLY (VDD) CURRENT                     |                          |                                                           |     |     |     |      |

| V <sub>DD</sub> Supply Current                 |                          | LED_OFFSET = 25 µs; LED_PERIOD =19 µs; LED peak current = |     |     |     |      |

|                                                |                          | 25 mA, 4 channels active                                  |     |     |     |      |

| 1 Pulse                                        |                          | 100 Hz data rate; Time Slot A only                        |     | 106 |     | μΑ   |

|                                                |                          | 100 Hz data rate; Time Slot B only                        |     | 94  |     | μA   |

|                                                |                          | 100 Hz data rate; both Time Slot A and Time Slot B        |     | 151 |     | μΑ   |

| 10 Pulses                                      |                          | 100 Hz data rate; Time Slot A only                        |     | 258 |     | μA   |

|                                                |                          | 100 Hz data rate; Time Slot B only                        |     | 246 |     | μA   |

|                                                |                          | 100 Hz data rate; both Time Slot A and Time Slot B        |     | 455 |     | μA   |

| Peak V <sub>DD</sub> Supply Current<br>(1.8 V) | IV <sub>DD_PEAK</sub>    |                                                           |     |     |     |      |

| 4-Channel Operation                            |                          |                                                           |     | 9.3 |     | mA   |

| 1-Channel Operation                            |                          |                                                           |     | 2.3 |     | mA   |

| Standby Mode Current                           | IV <sub>DD_STANDBY</sub> |                                                           |     | 3.5 |     | μA   |

| VLEDA AND VLEDB SUPPLY<br>CURRENT              |                          |                                                           |     |     |     |      |

| Average Supply Current                         |                          |                                                           |     |     |     |      |

| VLEDA OR VLEDB                                 |                          | Peak LED current = 100 mA; LED_PULSE width = 3 μs         |     |     |     |      |

| 1 Pulse                                        |                          | 50 Hz data rate                                           |     | 15  |     | μA   |

|                                                |                          | 100 Hz data rate                                          |     | 30  |     | μA   |

|                                                |                          | 200 Hz data rate                                          |     | 60  |     | μA   |

| 10 Pulses                                      |                          | 50 Hz data rate                                           |     | 150 |     | μA   |

|                                                |                          | 100 Hz data rate                                          |     | 300 |     | μA   |

|                                                |                          | 200 Hz data rate                                          |     | 600 |     | μA   |

$^1$  LEDA or LEDB is one of LED1, LED2, or LED3.  $V_{\text{LEDA}}$  or  $V_{\text{LEDB}}$  is one of  $V_{\text{LED1}}$ ,  $V_{\text{LED2}}$ , or  $V_{\text{LED3}}$ .  $^2$   $V_{\text{DD}}$  is the voltage applied at the AVDD and DVDD pins.

## PERFORMANCE SPECIFICATIONS

AVDD = DVDD = 1.8 V,  $T_A =$  full operating temperature range, unless otherwise noted.

| Table  | 2  |

|--------|----|

| I able | э. |

| Parameter                               | Test Conditions/Comments                                                          | Min   | Тур       | Max  | Unit |

|-----------------------------------------|-----------------------------------------------------------------------------------|-------|-----------|------|------|

| DATA AQUISITION                         |                                                                                   |       |           |      |      |

| Resolution                              | Single pulse                                                                      |       | 14        |      | Bits |

| Resolution/Sample                       | 64 to 255 pulses                                                                  |       | 20        |      | Bits |

| Resolution/Data Read                    | 64 to 255 pulses and sample average = 128                                         |       | 27        |      | Bits |

| LED DRIVER                              |                                                                                   |       |           |      |      |

| LED Current Slew Rate <sup>1</sup>      |                                                                                   |       |           |      |      |

| Rise                                    | Slew rate control setting = 0; $T_A = 25^{\circ}$ C; $I_{LED} = 70 \text{ mA}$    |       | 240       |      | mA/μ |

|                                         | Slew rate control setting = 7; $T_A = 25^{\circ}$ C; $I_{LED} = 70 \text{ mA}$    |       | 1400      |      | mA/μ |

| Fall                                    | Slew rate control setting = 0, 1, 2; $T_A = 25^{\circ}$ C; $I_{LED} = 70$ mA      |       | 3200      |      | mA/μ |

|                                         | Slew rate control setting = 6, 7; $T_A = 25^{\circ}C$ ; $I_{LED} = 70 \text{ mA}$ |       | 4500      |      | mA/μ |

| LED Peak Current                        | LED pulse enabled                                                                 | 8     |           | 250  | mA   |

| Driver Compliance Voltage               | Voltage above ground required for LED driver operation                            | 0.2   |           |      | V    |

| LED PERIOD                              | AFE width = 4 $\mu$ s                                                             | 19    |           |      | μs   |

|                                         | AFE width = $3 \mu s$                                                             | 17    |           |      | μs   |

| Sampling Frequency <sup>2</sup>         | Time Slot A only; normal mode; 1 pulse; OFFSET_LEDA = 23 μs; PERIOD_LEDA = 19 μs  | 0.122 |           | 3230 | Hz   |

|                                         | Time Slot B only; normal mode; 1 pulse; OFFSET_LEDA = 23 µs; PERIOD_LEDA = 19 µs  | 0.122 |           | 3820 | Hz   |

|                                         | Both time slots; normal mode; 1 pulse; OFFSET_LEDA = 23 µs; PERIOD_LEDA = 19 µs   | 0.122 |           | 1750 | Hz   |

|                                         | Time Slot A only; normal mode; 8 pulses; OFFSET_LEDA = 23 μs; PERIOD_LEDA = 19 μs | 0.122 |           | 2257 | Hz   |

|                                         | Time Slot B only; normal mode; 8 pulses; OFFSET_LEDA = 23 μs; PERIOD_LEDA = 19 μs | 0.122 |           | 2531 | Hz   |

|                                         | Both time slots; normal mode; 8 pulses; OFFSET_LEDA = 23 μs; PERIOD_LEDA = 19 μs  | 0.122 |           | 1193 | Hz   |

| CATHODE PIN (PDC) VOLTAGE               |                                                                                   |       |           |      |      |

| During All Sampling Periods             | Register 0x54, Bit 7 = 0x0; Register 0x3C, Bit 9 = $1^3$                          |       | 1.8       |      | v    |

|                                         | Register 0x54, Bit 7 = 0x0; Register 0x3C, Bit 9 = 0                              |       | 1.3       |      | v    |

| During Slot A Sampling                  | Register 0x54, Bit 7 = 0x1; Register 0x54, Bits[9:8] = $0x0^3$                    |       | 1.8       |      | V    |

|                                         | Register 0x54, Bit 7 = $0x1$ ; Register 0x54, Bits[9:8] = $0x1$                   |       | 1.3       |      | v    |

|                                         | Register 0x54, Bit 7 = $0x1$ ; Register 0x54, Bits[9:8] = $0x2$                   |       | 1.55      |      | v    |

|                                         | Register 0x54, Bit 7 = 0x1; Register 0x54, Bits[9:8] = $0x3^4$                    |       | 0         |      | v    |

| During Slot B Sampling                  | Register 0x54, Bit 7 = 0x1; Register 0x54, Bits[11:10] = $0x0^3$                  |       | 1.8       |      | V    |

|                                         | Register 0x54, Bit 7 = 0x1; Register 0x54, Bits[11:10] = 0x1                      |       | 1.3       |      | v    |

|                                         | Register 0x54, Bit 7 = 0x1; Register 0x54, Bits[11:10] = 0x2                      |       | 1.55      |      | v    |

|                                         | Register 0x54, Bit 7 = 0x1; Register 0x54, Bits[11:10] = $0x3^4$                  |       | 0         |      | V    |

| During Sleep Periods                    | Register 0x54, Bit 7 = 0x0; Register 0x3C, Bit 9 = 1                              |       | 1.8       |      | v    |

|                                         | Register 0x54, Bit 7 = 0x0; Register 0x3C, Bit 9 = 0                              |       | 1.3       |      | v    |

|                                         | Register 0x54, Bit 7 = 0x1; Register 0x54, Bits[13:12] = 0x0                      |       | 1.8       |      | V    |

|                                         | Register 0x54, Bit 7 = $0x1$ ; Register 0x54[13:12] = $0x1$                       |       | 1.3       |      | v    |

|                                         | Register 0x54, Bit 7 = 0x1; Register 0x54[13:12] = 0x2                            |       | 1.55      |      | v    |

|                                         | Register 0x54, Bit 7 = 0x1; Register 0x54[13:12] = 0x3                            |       | 0         |      | v    |

| PHOTODIODE INPUT PINS/ ANODE<br>VOLTAGE |                                                                                   |       |           |      |      |

| During All Sampling Periods             |                                                                                   |       | 1.3       |      | v    |

| During Sleep Periods                    |                                                                                   | Catl  | node volt | tage | V    |

<sup>1</sup> LED inductance is negligible for these values. The effective slew rate slows with increased inductance.

<sup>2</sup> The maximum values in this specification are the internal ADC sampling rates in normal mode. The I<sup>2</sup>C read rates in some configurations may limit the actual output data rate of the device

<sup>3</sup> This mode may induce additional noise and is not recommended unless absolutely necessary. The 1.8 V setting uses  $V_{DD}$ , which contains greater amounts of differential voltage noise with respect to the anode voltage. A differential voltage between the anode and cathode injects a differential current across the capacitance of the photodiode of the magnitude C × dV/dt.

<sup>4</sup> This setting is not recommended for photodiodes because it causes a 1.3 V forward bias of the photodiode.

# ANALOG SPECIFICATIONS

AVDD = DVDD = 1.8 V,  $T_A = full$  operating temperature range, unless otherwise noted. Compensation of the AFE offset is explained in the AFE Operation section.

| Table 4. |

|----------|

|----------|

| Parameter                                                   | Test Conditions/Comments                                                                                             | Min | Тур  | Max | Unit   |

|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-----|------|-----|--------|

| INPUT CAPACITANCE                                           |                                                                                                                      |     |      | 100 | pF     |

| PULSED SIGNAL CONVERSIONS, 3 µs WIDE LED PULSE <sup>1</sup> | 4 μs wide AFE integration; normal operation, Register 0x43<br>(Time Slot A) and Register 0x45 (Time Slot B) = 0xADA5 |     |      |     |        |

| ADC Resolution <sup>2</sup>                                 | Transimpedance amplifier (TIA) feedback resistor                                                                     |     |      |     |        |

|                                                             | 25 kΩ                                                                                                                |     | 1.64 |     | nA/LSB |

|                                                             | 50 kΩ                                                                                                                |     | 0.82 |     | nA/LSB |

|                                                             | 100 kΩ                                                                                                               |     | 0.41 |     | nA/LSB |

|                                                             | 200 kΩ                                                                                                               |     | 0.2  |     | nA/LSB |

| ADC Saturation Level                                        | TIA feedback resistor                                                                                                |     |      |     |        |

|                                                             | 25 kΩ                                                                                                                |     | 13.4 |     | μΑ     |

|                                                             | 50 kΩ                                                                                                                |     | 6.7  |     | μΑ     |

|                                                             | 100 kΩ                                                                                                               |     | 3.35 |     | μΑ     |

|                                                             | 200 kΩ                                                                                                               |     | 1.67 |     | μΑ     |

| Ambient Signal Headroom on Pulsed Signal                    | TIA feedback resistor                                                                                                |     |      |     |        |

|                                                             | 25 kΩ                                                                                                                |     | 37   |     | μA     |

|                                                             | 50 kΩ                                                                                                                |     | 18.5 |     | μA     |

|                                                             | 100 kΩ                                                                                                               |     | 9.25 |     | μA     |

|                                                             | 200 kΩ                                                                                                               |     | 4.63 |     | μA     |

| PULSED SIGNAL CONVERSIONS, 2 µs WIDE LED PULSE <sup>1</sup> | 3 μs wide AFE integration; normal operation, Register 0x43<br>(Time Slot A) and Register 0x45 (Time Slot B) = 0xADA5 |     |      |     |        |

| ADC Resolution <sup>2</sup>                                 | TIA feedback resistor                                                                                                |     |      |     |        |

|                                                             | 25 kΩ                                                                                                                |     | 2.31 |     | nA/LSB |

|                                                             | 50 kΩ                                                                                                                |     | 1.15 |     | nA/LSB |

|                                                             | 100 kΩ                                                                                                               |     | 0.58 |     | nA/LSB |

|                                                             | 200 kΩ                                                                                                               |     | 0.29 |     | nA/LSB |

| ADC Saturation Level                                        | TIA feedback resistor                                                                                                |     |      |     |        |

|                                                             | 25 kΩ                                                                                                                |     | 18.9 |     | μΑ     |

|                                                             | 50 kΩ                                                                                                                |     | 9.46 |     | μA     |

|                                                             | 100 kΩ                                                                                                               |     | 4.73 |     | μA     |

|                                                             | 200 kΩ                                                                                                               |     | 2.37 |     | μA     |

| Ambient Signal Headroom on Pulsed Signal                    | TIA feedback resistor                                                                                                |     |      |     |        |

|                                                             | 25 kΩ                                                                                                                |     | 31.5 |     | μA     |

|                                                             | 50 kΩ                                                                                                                |     | 15.7 |     | μA     |

|                                                             | 100 kΩ                                                                                                               |     | 7.87 |     | μA     |

|                                                             | 200 kΩ                                                                                                               |     | 3.93 |     | μA     |

| FULL SIGNAL CONVERSIONS <sup>3</sup>                        |                                                                                                                      |     |      |     |        |

| TIA Saturation Level of Pulsed Signal and Ambient Level     | TIA feedback resistor                                                                                                |     |      |     |        |

|                                                             | 25 kΩ                                                                                                                |     | 50.4 |     | μA     |

|                                                             | 50 kΩ                                                                                                                |     | 25.2 |     | μA     |

|                                                             | 100 kΩ                                                                                                               |     | 12.6 |     | μA     |

|                                                             | 200 kΩ                                                                                                               |     | 6.3  |     | μA     |

| Parameter                                 | Test Conditions/Comments                                                       | Min | Тур  | Max | Unit    |

|-------------------------------------------|--------------------------------------------------------------------------------|-----|------|-----|---------|

| SYSTEM PERFORMANCE                        |                                                                                |     |      |     |         |

| Total Output Noise Floor                  | Normal mode; per pulse; per channel; no LED; $C_{PD} = 70 \text{ pF}$          |     |      |     |         |

|                                           | 25 kΩ; referred to ADC input                                                   |     | 2.0  |     | LSB rms |

|                                           | 25 k $\Omega$ ; referred to peak input signal for 2 $\mu$ s LED pulse          |     | 4.6  |     | nA rms  |

|                                           | 25 k $\Omega$ ; referred to peak input signal for 3 $\mu$ s LED pulse          |     | 3.3  |     | nA rms  |

|                                           | 25 k $\Omega$ ; saturation signal-to-noise ratio (SNR) per pulse per channel^4 |     | 72.3 |     | dB      |

|                                           | 50 k $\Omega$ ; referred to ADC input                                          |     | 2.4  |     | LSB rms |

|                                           | 50 k\Omega; referred to peak input signal for 2 $\mu s$ LED pulse              |     | 2.8  |     | nA rms  |

|                                           | 50 k\Omega; referred to peak input signal for 3 $\mu s$ LED pulse              |     | 2.0  |     | nA rms  |

|                                           | 50 k $\Omega$ ; saturation SNR per pulse per channel <sup>4</sup>              |     | 70.6 |     | dB      |

|                                           | 100 kΩ; referred to ADC input                                                  |     | 3.4  |     | LSB rms |

|                                           | 100 k\Omega; referred to peak input signal for 2 $\mu s$ LED pulse             |     | 1.9  |     | nA rms  |

|                                           | 100 k\Omega; referred to peak input signal for 3 $\mu s$ LED pulse             |     | 1.4  |     | nA rms  |

|                                           | 100 k $\Omega$ ; saturation SNR per pulse per channel <sup>4</sup>             |     | 67.6 |     | dB      |

|                                           | 200 kΩ; referred to ADC input                                                  |     | 5.5  |     | LSB rms |

|                                           | 200 k\Omega; referred to peak input signal for 2 $\mu s$ LED pulse             |     | 1.6  |     | nA rms  |

|                                           | 200 k\Omega; referred to peak input signal for 3 $\mu s$ LED pulse             |     | 1.1  |     | nA rms  |

|                                           | 200 k $\Omega$ ; saturation SNR per pulse per channel <sup>4</sup>             |     | 63.5 |     | dB      |

| DC Power Supply Rejection Ratio (DC PSRR) |                                                                                |     | -37  |     | dB      |

<sup>1</sup> This saturation level applies to the ADC only and, therefore, includes only the pulsed signal. Any nonpulsatile signal is removed prior to the ADC stage.

<sup>2</sup> ADC resolution is listed per pulse when the AFE offset is correctly compensated per the AFE Operation section. If using multiple pulses, divide by the number of pulses.

<sup>3</sup> This saturation level applies to the full signal path and, therefore, includes both the ambient signal and the pulsed signal. <sup>4</sup> The noise term of the saturation SNR value refers to the receive noise only and does not include photon shot noise or any noise on the LED signal itself.

### **DIGITAL SPECIFICATIONS**

DVDD = 1.7 V to 1.9 V, unless otherwise noted.

| Parameter                 | Symbol           | <b>Test Conditions/Comments</b> | Min                      | Тур | Max                      | Unit |

|---------------------------|------------------|---------------------------------|--------------------------|-----|--------------------------|------|

| LOGIC INPUTS (SCL, SDA)   |                  |                                 |                          |     |                          |      |

| Input Voltage Level       |                  |                                 |                          |     |                          |      |

| High                      | VIH              |                                 | $0.7 \times \text{DVDD}$ |     | 3.6                      | V    |

| Low                       | VIL              |                                 |                          |     | $0.3 \times \text{DVDD}$ | ٧    |

| Input Current Level       |                  |                                 |                          |     |                          |      |

| High                      | IIH              |                                 | -10                      |     | +10                      | μA   |

| Low                       | lı∟              |                                 | -10                      |     | +10                      | μA   |

| Input Capacitance         | CIN              |                                 |                          | 10  |                          | pF   |

| LOGIC OUTPUTS             |                  |                                 |                          |     |                          |      |

| INT Output Voltage Level  |                  |                                 |                          |     |                          |      |

| High                      | V <sub>OH</sub>  | 2 mA high level output current  | DVDD - 0.5               |     |                          | V    |

| Low                       | Vol              | 2 mA low level output current   |                          |     | 0.5                      | V    |

| PDSO Output Voltage Level |                  |                                 |                          |     |                          |      |

| High                      | Vон              | 2 mA high level output current  | DVDD - 0.5               |     |                          | V    |

| Low                       | Vol              | 2 mA low level output current   |                          |     | 0.5                      | ٧    |

| SDA Output Voltage Level  |                  |                                 |                          |     |                          |      |

| Low                       | V <sub>OL1</sub> | 2 mA low level output current   |                          |     | $0.2 \times \text{DVDD}$ | V    |

| SDA Output Current Level  |                  |                                 |                          |     |                          |      |

| Low                       | lol              | $V_{OL1} = 0.6 V$               | 6                        |     |                          | mA   |

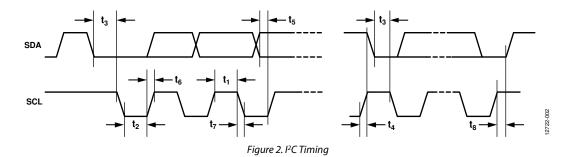

# TIMING SPECIFICATIONS

# Table 6. I<sup>2</sup>C Timing Specifications

| Parameter                          | Symbol         | <b>Test Conditions/Comments</b> | Min  | Тур | Max  | Unit |

|------------------------------------|----------------|---------------------------------|------|-----|------|------|

| I <sup>2</sup> C PORT <sup>1</sup> |                | See Figure 2                    |      |     |      |      |

| SCL                                |                |                                 |      |     |      |      |

| Frequency                          |                |                                 |      | 400 |      | kHz  |

| Minimum Pulse Width                |                |                                 |      |     |      |      |

| High                               | t1             |                                 | 600  |     |      | ns   |

| Low                                | t <sub>2</sub> |                                 | 1300 |     |      | ns   |

| Start Condition                    |                |                                 |      |     |      |      |

| Hold Time                          | t3             |                                 | 600  |     |      | ns   |

| Setup Time                         | t4             |                                 | 600  |     |      | ns   |

| SDA Setup Time                     | t <sub>5</sub> |                                 | 100  |     |      | ns   |

| SCL and SDA                        |                |                                 |      |     |      |      |

| Rise Time                          | t <sub>6</sub> |                                 |      |     | 1000 | ns   |

| Fall Time                          | t7             |                                 |      |     | 300  | ns   |

| Stop Condition                     |                |                                 |      |     |      |      |

| Setup Time                         | t <sub>8</sub> |                                 | 600  |     |      | ns   |

<sup>1</sup> Guaranteed by design.

# **ABSOLUTE MAXIMUM RATINGS**

Table 7.

| 1                         |                  |

|---------------------------|------------------|

| Parameter                 | Rating           |

| AVDD to AGND              | –0.3 V to +2.2 V |

| DVDD to DGND              | –0.3 V to +2.2 V |

| INT to DGND               | –0.3 V to +2.2 V |

| PDSO to DGND              | –0.3 V to +2.2 V |

| LEDXx to LGND             | –0.3 V to +3.6 V |

| SCL to DGND               | –0.3 V to +3.9 V |

| SDA to DGND               | –0.3 V to +3.9 V |

| Junction Temperature      | 150°C            |

| ESD                       |                  |

| 28-Lead LFCSP             |                  |

| Human Body Model (HBM)    | 1500 V           |

| Charge Device Model (CDM) | 1250 V           |

| Machine Model (MM)        | 100 V            |

| 16-Ball WLCSP             |                  |

| Human Body Model (HBM)    | 1500 V           |

| Charge Device Model (CDM) | 500 V            |

| Machine Model (MM)        | 100 V            |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

## THERMAL RESISTANCE

#### Table 8. Thermal Resistance

| Package Type     | θ <sub>JA</sub> | Unit |

|------------------|-----------------|------|

| 28-Lead LFCSP_WQ | 54.9            | °C/W |

| 16-Ball WLCSP    | 60              | °C/W |

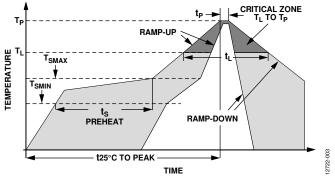

### **RECOMMENDED SOLDERING PROFILE**

Figure 3 and Table 9 provide details about the recommended soldering profile.

#### Figure 3. Recommended Soldering Profile

#### Table 9. Recommended Soldering Profile

| Tuble 31 Recommended Soldering 110               | Tuble 7. Recommended oblacting I tome |  |  |  |  |  |

|--------------------------------------------------|---------------------------------------|--|--|--|--|--|

| Profile Feature                                  | Condition (Pb-Free)                   |  |  |  |  |  |

| Average Ramp Rate ( $T_L$ to $T_P$ )             | 3°C/sec max                           |  |  |  |  |  |

| Preheat                                          |                                       |  |  |  |  |  |

| Minimum Temperature (T <sub>SMIN</sub> )         | 150°C                                 |  |  |  |  |  |

| Maximum Temperature (T <sub>SMAX</sub> )         | 200°C                                 |  |  |  |  |  |

| Time ( $T_{SMIN}$ to $T_{SMAX}$ ) ( $t_s$ )      | 60 sec to 180 sec                     |  |  |  |  |  |

| T <sub>SMAX</sub> to T <sub>L</sub> Ramp-Up Rate | 3°C/sec maximum                       |  |  |  |  |  |

| Time Maintained Above Liquidous                  |                                       |  |  |  |  |  |

| Temperature                                      |                                       |  |  |  |  |  |

| Liquidous Temperature (T <sub>L</sub> )          | 217°C                                 |  |  |  |  |  |

| Time (t∟)                                        | 60 sec to 150 sec                     |  |  |  |  |  |

| Peak Temperature (T <sub>P</sub> )               | +260 (+0/-5)°C                        |  |  |  |  |  |

| Time Within 5°C of Actual Peak                   | <30 sec                               |  |  |  |  |  |

| Temperature (t <sub>P</sub> )                    |                                       |  |  |  |  |  |

| Ramp-Down Rate                                   | 6°C/sec maximum                       |  |  |  |  |  |

| Time from 25°C to Peak Temperature               | 8 minutes maximum                     |  |  |  |  |  |

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

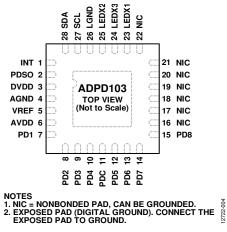

# **PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS**

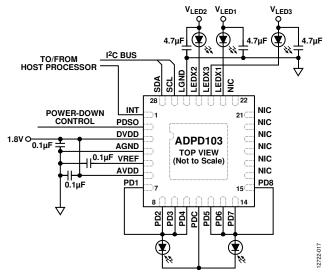

Figure 4. 28-Lead LFCSP Pin Configuration

Table 10. 28-Lead LFCSP Pin Function Descriptions

| Pin No.  | Mnemonic    | Type <sup>1</sup> | Description                                                                                     |

|----------|-------------|-------------------|-------------------------------------------------------------------------------------------------|

| 1        | INT         | DO                | Interrupt Output.                                                                               |

| 2        | PDSO        | DO                | Power-Down Status Output.                                                                       |

| 3        | DVDD        | S                 | 1.8 V Digital Supply.                                                                           |

| 4        | AGND        | S                 | Analog Ground.                                                                                  |

| 5        | VREF        | REF               | Internally Generated ADC Voltage Reference. Buffer this pin with a 1 $\mu$ F capacitor to AGND. |

| 6        | AVDD        | S                 | 1.8 V Analog Supply.                                                                            |

| 7        | PD1         | AI                | Photodiode Current Input (Anode). If not in use, leave this pin floating.                       |

| 8        | PD2         | AI                | Photodiode Current Input (Anode). If not in use, leave this pin floating.                       |

| 9        | PD3         | AI                | Photodiode Current Input (Anode). If not in use, leave this pin floating.                       |

| 10       | PD4         | AI                | Photodiode Current Input (Anode). If not in use, leave this pin floating.                       |

| 11       | PDC         | AO                | Photodiode Common Cathode Bias.                                                                 |

| 12       | PD5         | AI                | Photodiode Current Input (Anode). If not in use, leave this pin floating.                       |

| 13       | PD6         | AI                | Photodiode Current Input (Anode). If not in use, leave this pin floating.                       |

| 14       | PD7         | AI                | Photodiode Current Input (Anode). If not in use, leave this pin floating.                       |

| 15       | PD8         | AI                | Photodiode Current Input (Anode). If not in use, leave this pin floating.                       |

| 16 to 22 | NIC         | R                 | Not Internally Connected (Nonbonded Pad). This pin can be grounded.                             |

| 23       | LEDX1       | AO                | LED Driver 1 Current Sink. If not in use, leave this pin floating.                              |

| 24       | LEDX3       | AO                | LED Driver 3 Current Sink. If not in use, leave this pin floating.                              |

| 25       | LEDX2       | AO                | LED Driver 2 Current Sink. If not in use, leave this pin floating.                              |

| 26       | LGND        | S                 | LED Driver Ground.                                                                              |

| 27       | SCL         | DI                | I <sup>2</sup> C Clock Input.                                                                   |

| 28       | SDA         | DIO               | I <sup>2</sup> C Data Input/Output.                                                             |

|          | EPAD (DGND) | S                 | Exposed Pad (Digital Ground). Connect the exposed pad to ground.                                |

<sup>1</sup> DO means digital output, S means supply, REF means voltage reference, AI means analog input, AO means analog output, R means reserved, DI means digital input, and DIO means digital input/output.

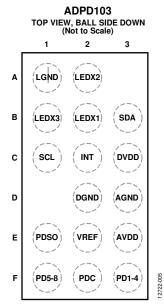

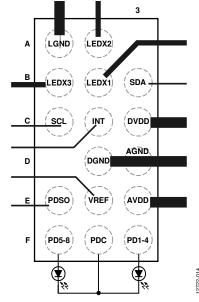

Figure 5. 16-Ball WLCSP Pin Configuration

| Pin No. | Mnemonic | Type <sup>1</sup> | Description                                                                                     |

|---------|----------|-------------------|-------------------------------------------------------------------------------------------------|

| A1      | LGND     | S                 | LED Driver Ground.                                                                              |

| A2      | LEDX2    | AO                | LED Driver 2 Current Sink. If not in use, leave this pin floating.                              |

| B1      | LEDX3    | AO                | LED Driver 3 Current Sink. If not in use, leave this pin floating.                              |

| B2      | LEDX1    | AO                | LED Driver 1 Current Sink. If not in use, leave this pin floating.                              |

| B3      | SDA      | DIO               | I <sup>2</sup> C Data Input/Output.                                                             |

| C1      | SCL      | S                 | I <sup>2</sup> C Clock Input.                                                                   |

| C2      | INT      | DO                | Interrupt Output.                                                                               |

| C3      | DVDD     | S                 | 1.8 V Digital Supply.                                                                           |

| D2      | DGND     | S                 | Digital Ground.                                                                                 |

| D3      | AGND     | S                 | Analog Ground.                                                                                  |

| E1      | PDSO     | DO                | Power-Down Status Output.                                                                       |

| E2      | VREF     | REF               | Internally Generated ADC Voltage Reference. Buffer this pin with a 1 $\mu$ F capacitor to AGND. |

| E3      | AVDD     | S                 | 1.8 V Analog Supply.                                                                            |

| F1      | PD5-8    | AI                | Photodiode Combined Current Input of PD5 to PD8. If not in use, leave this pin floating.        |

| F2      | PDC      | AO                | Photodiode Common Cathode Bias.                                                                 |

| F3      | PD1-4    | AI                | Photodiode Combined Current Input of PD1 to PD4. If not in use, leave this pin floating.        |

<sup>1</sup> S means supply, AO means analog output, DIO means digital input/output, DO means digital output, REF means voltage reference, and AI means analog input.

# **TYPICAL PERFORMANCE CHARACTERISTICS**

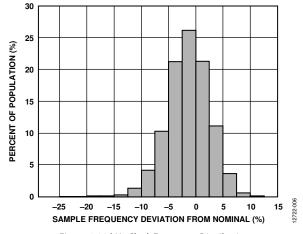

Figure 6. 32 kHz Clock Frequency Distribution (Default Settings, Before User Calibration: Register 0x4B = 0x2612)

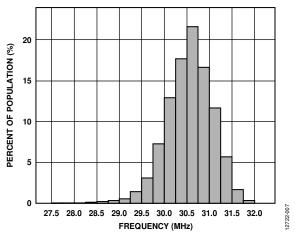

Figure 7. 32 MHz Clock Frequency Distribution (Default Settings, Before User Calibration: Register 0x4D = 0x425E)

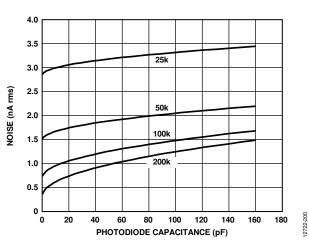

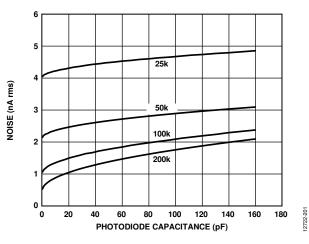

Figure 8. Input Referred Noise vs. Photodiode Capacitance, LED Pulse Width = 3  $\mu s$

Figure 9. Input Referred Noise vs. Photodiode Capacitance, LED Pulse Width =  $2 \mu s$

# THEORY OF OPERATION INTRODUCTION

The ADPD103 operates as a complete optical transceiver stimulating up to three LEDs and measuring the return signal on up to eight separate current inputs. The core consists of a photometric front end coupled with an ADC, digital block, and three independent LED drivers. The core circuitry stimulates the LEDs and measures the return in the analog block through one to eight photodiode inputs, storing the results in discrete data locations. The eight inputs are broken into two blocks of four simultaneous input channels. Data can be read directly by a register, or through a FIFO. This highly integrated system includes an analog signal processing block, digital signal processing block, I<sup>c</sup>C communication interface, and programmable pulsed LED current sources.

The LED driver is a current sink and is agnostic to LED supply voltage and LED type. The photodiode (PDx) inputs can accommodate any photodiode with an input capacitance of less than 100 pF. The ADPD103 is purposefully designed to produce a high SNR for relatively low LED power while greatly reducing the effect of ambient light on the measured signal.

# **DUAL TIME SLOT OPERATION**

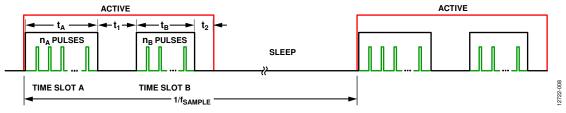

The ADPD103 operates in two independent time slots, Time Slot A and Time Slot B, which are carried out sequentially. The entire signal path from LED stimulation to data capture and processing is executed during each time slot. Each time slot has a separate datapath that uses independent settings for the LED driver, AFE setup, and the resulting data. Time Slot A and Time Slot B operate in sequence for every sampling period, as shown in Figure 10.

The timing parameters are defined as follows:

$t_A$  (µs) = SLOTA\_LED\_OFFSET +  $n_A \times$  SLOTA\_LED\_PERIOD

where  $n_A$  is the number of pulses for Time Slot A (Register 0x31, Bits[15:8]).

$t_B$  (µs) = SLOTB\_LED\_OFFSET +  $n_B \times$  SLOTB\_LED\_PERIOD where  $n_B$  is the number of pulses for Time Slot B (Register 0x36, Bits[15:8]).

Calculate the LED period using the following equation:

*LED\_PERIOD, minimum* =  $2 \times AFE_WIDTH + 11$

$t_1$  and  $t_2$  are fixed and based on the computation time for each slot. If a slot is not in use, these times do not add to the total active time. Table 12 defines the values for these LED and sampling time parameters.

Figure 10. Time Slot Timing Diagram

| Table 12. LE | D Timing and | l Sample Timi | ng Parameters |

|--------------|--------------|---------------|---------------|

|--------------|--------------|---------------|---------------|

| Parameter                     | Register | Bits  | Test Conditions/Comments                                            | Min                                                                | Тур | Мах | Unit |

|-------------------------------|----------|-------|---------------------------------------------------------------------|--------------------------------------------------------------------|-----|-----|------|

| SLOTA_LED_OFFSET <sup>1</sup> | 0x30     | [7:0] | Delay from power-up to LEDA rising edge                             | elay from power-up to LEDA rising edge 23 63                       |     | 63  | μs   |

| SLOTB_LED_OFFSET <sup>1</sup> | 0x35     | [7:0] | Delay from power-up to LEDB rising edge                             | 23                                                                 |     | 63  | μs   |

| SLOTA_LED_PERIOD <sup>2</sup> | 0x31     | [7:0] | Time between LED pulses in Time Slot A; SLOTx_AFE_WIDTH = 4 $\mu$ s | ne between LED pulses in Time Slot A; SLOTx_AFE_WIDTH = 4 µs 19 63 |     | 63  | μs   |

| SLOTB_LED_PERIOD <sup>2</sup> | 0x36     | [7:0] | ne between LED pulses in Time Slot B; SLOTx_AFE_WIDTH = 4 μs 19 63  |                                                                    | μs  |     |      |

| t1                            |          |       | Compute time for Time Slot A                                        |                                                                    | 68  |     | μs   |

| t <sub>2</sub>                |          |       | Compute time for Time Slot B                                        |                                                                    | 20  |     | μs   |

| t <sub>sleep</sub>            |          |       | Sleep time between sample periods                                   | 222                                                                |     |     | μs   |

<sup>1</sup> Setting the SLOTx\_LED\_OFFSET below the specified minimum value may cause failure of ambient light rejection for large photodiodes.

<sup>2</sup> Setting the SLOTx\_LED\_PERIOD below the specified minimum value can cause invalid data captures.

## TIME SLOT SWITCH

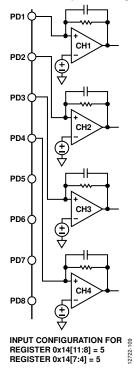

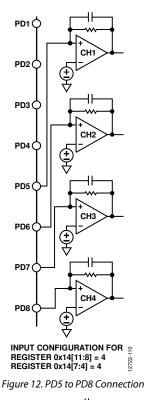

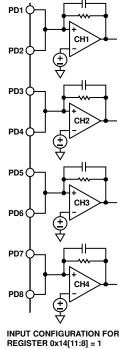

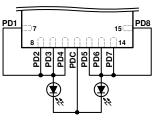

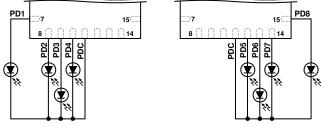

Up to eight photodiodes (PD1 to PD8) can be connected to the ADPD103. The photodiode anodes are connected to the PD1 to PD8 input pins; the photodiode cathodes are connected to the cathode pin, PDC. The anodes are assigned in three different configurations depending on the settings of Register 0x14 (see Figure 11, Figure 12, and Figure 13).

A switch sets which photodiode group is connected during Time Slot A and Time Slot B. See Table 13 for the time slot switch registers. When using less than eight photodiodes, it is important to leave the unused inputs floating for proper operation of the device. The photodiode inputs are current inputs and as such, these pins are also considered to be voltage outputs. Tying these inputs to a voltage may saturate the analog block.

#### Register 0x14, PD1 to PD8 Input Configurations

Figure 11. PD1 to PD4 Connection

Figure 13. 2-to-1 PD Current Summation

REGISTER 0x14[7:4] = 1

#### Table 13. Time Slot Switch (Register 0x14)

| Address | Bits   | Name         | Description                                                                                       |

|---------|--------|--------------|---------------------------------------------------------------------------------------------------|

| 0x14    | [11:8] | SLOTB_PD_SEL | Selects connection of photodiode for Time Slot B as shown in Figure 11, Figure 12, and Figure 13. |

|         |        |              | 0x0: inputs are floating in Time Slot B.                                                          |

|         |        |              | 0x1: all PDx pins (PD1 to PD8) are connected during Time Slot B.                                  |

|         |        |              | 0x4: PD5 to PD8 are connected during Time Slot B.                                                 |

|         |        |              | 0x5: PD1 to PD4 are connected during Time Slot B.                                                 |

|         |        |              | Other: reserved.                                                                                  |

|         | [7:4]  | SLOTA_PD_SEL | Selects connection of photodiode for Time Slot A as shown in Figure 11, Figure 12, and Figure 13. |

|         |        |              | 0x0: inputs are floating in Time Slot A.                                                          |

|         |        |              | 0x1: All PDx pins (PD1 to PD8) are connected during Time Slot A.                                  |

|         |        |              | 0x4: PD5 to PD8 are connected during Time Slot A.                                                 |

|         |        |              | 0x5: PD1 to PD4 are connected during Time Slot A.                                                 |

|         |        |              | Other: reserved.                                                                                  |

### ADJUSTABLE SAMPLING FREQUENCY

Register 0x12 controls the sampling frequency setting of the ADPD103 and Register 0x4B, Bits[5:0] further tunes this clock for greater accuracy. The sampling frequency is governed by an internal 32 kHz sample rate clock that also drives the transition of the internal state machine. The maximum sampling frequencies for some sample conditions are listed in Table 3. The maximum sample frequency for all conditions is determined by the following equation:

$f_{SAMPLE, MAX} = 1/(t_A + t_1 + t_B + t_2 + t_{SLEEP, MIN})$

If a given time slot is not in use, elements from that time slot do not factor into the calculation. For example, if Time Slot A is not in use,  $t_A$  and  $t_1$  do not add to the sampling period and the new maximum sampling frequency is calculated as follows:

$f_{SAMPLE, MAX} = 1/(t_B + t_2 + t_{SLEEP, MIN})$

where  $t_{SLEEP, MIN}$  is the minimum sleep time required between samples. See the Dual Time Slot Operation section for the definitions of  $t_A$ ,  $t_1$ ,  $t_B$ , and  $t_2$ .

### **External Sync for Sampling**

The ADPD103 provides an option to use an external sync signal to trigger the sampling periods. This external sample sync signal can be provided either on the INT pin or the PDSO pin. This functionality is controlled by Register 0x4F, Bits[3:2]. When enabled, a rising edge on the selected input specifies when the next sample cycle occurs. When triggered, there is a delay of one to two internal sampling clock (32 kHz) cycles, and then the normal start-up sequence occurs. This sequence is the same as if the normal sample timer provided the trigger. To enable the external sync signal feature, use the following procedure:

- 1. Write 0x1 to Register 0x10 to enter program mode.

- 2. Write the appropriate value to Register 0x4F, Bits[3:2] to select whether the INT pin or the PDSO pin specifies when

the next sample cycle occurs. Also, enable the appropriate input buffer using Register 0x4F, Bit 1, for the INT pin, or Register 0x4F, Bit 5, for the PDSO pin.

- 3. Write b1 to EXT\_SYNC\_ENA, Register 0x38, Bit 14 to enable the external sampling trigger.

- 4. Write 0x2 to Register 0x10 to start the sampling operations.

- 5. Apply the external sync signal on the selected pin at the desired rate; sampling occurs at that rate. As with normal sampling operations, read the data using the FIFO or the data registers.

The maximum frequency constraints also apply in this case.

### Providing an External 32kHz Clock

The ADPD103 has an option for the user to provide an external 32 kHz clock to the device for system synchronization or for situations where a clock with better accuracy than the internal 32 kHz clock is required. The external 32 kHz clock is provided on the PDSO pin. To enable the 32 kHz external clock, use the following procedure at startup:

- 1. Drive the PDSO pin to a valid logic level or with the desired 32 kHz clock prior to enabling the PDSO pin as an input. Do not leave the pin floating prior to enabling it.

- 2. Write b1 to Register 0x4F, Bit 5 to enable the PDSO pin as an input.

- 3. Write b11 to register 0x4B, Bit 7 and Bit 8 (CLK32K\_EN and CLK32K\_BYP, respectively) to configure the device to use an external 32 kHz clock.

- 4. Write 0x1 to Register 0x10 to enter program mode.

- 5. Write additional control registers in any order while the device is in program mode to configure the device as required.

- 6. Write 0x2 to Register 0x10 to start the normal sampling operation.

# **STATE MACHINE OPERATION**

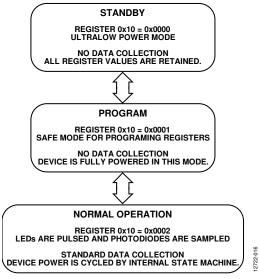

During each time slot, the ADPD103 operates according to a state machine. The state machine operates in the following sequence, shown in Figure 14.

Figure 14. State Machine Operation Flowchart

The ADPD103 operates in one of three modes: standby, program, and normal sampling mode.

Standby mode is a power saving mode in which no data collection occurs. All register values are retained in this mode. To place the device in standby mode, write 0x0 to Register 0x10, Bits[1:0]. The device powers up in standby mode.

Program mode is used for programming registers. Always cycle the ADPD103 through program mode when writing registers or changing modes. Because no power cycling occurs in this mode, the device may consume higher current in program mode than in normal operation. To place the device in program mode, write 0x1 to Register 0x10, Bits[1:0].

In normal operation, the ADPD103 pulses light and collects data. Power consumption in this mode depends on the pulse count and data rate. To place the device in normal sampling mode, write 0x2 to Register 0x10, Bits[1:0].

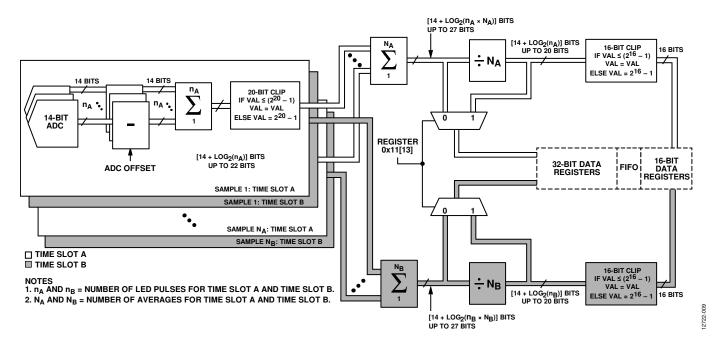

## NORMAL MODE OPERATION AND DATA FLOW

In normal mode, the ADPD103 follows a specific pattern set up by the state machine. This pattern is shown in the corresponding data flow in Figure 15. The pattern is as follows:

- 1. LED pulse and sample. The ADPD103 pulses external LEDs. The response of a photodiode or photodiodes to the reflected light is measured by the ADPD103. Each data sample is constructed from the sum of n individual pulses, where n is user configurable between 1 and 255.

- 2. Intersample averaging. If desired, the logic can average n samples, from 2 to 128 in powers of 2, to produce output data. New output data is saved to the output registers every N samples.

- 3. Data read. The host processor reads the converted results from the data register or the FIFO.

- 4. Repeat. The sequence has a few different loops that enable different types of averaging while keeping both time slots close in time relative to each other.

Figure 15. ADPD103 Datapath

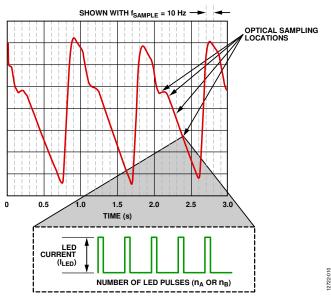

## LED Pulse and Sample

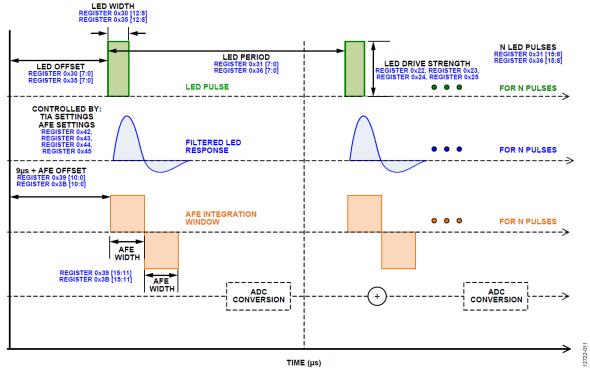

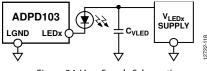

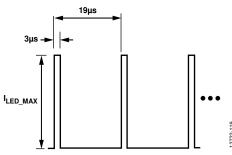

At each sampling period, the selected LED driver drives a series of LED pulses, as shown in Figure 16. The magnitude, duration, and number of pulses are programmable over the I<sup>2</sup>C interface. Each LED pulse coincides with a sensing period so that the sensed value represents the total charge acquired on the photodiode in response to only the corresponding LED pulse. Charge, such as ambient light, that does not correspond to the LED pulse is rejected.

After each LED pulse, the photodiode output relating the pulsed LED signal is sampled and converted to a digital value by the 14-bit ADC. Each subsequent conversion within a sampling period is summed with the previous result. Up to 255 pulse values from the ADC can be summed in an individual sampling period. There is a 20-bit maximum range for each sampling period.

### Averaging

The ADPD103 offers sample accumulation and averaging functionality to increase signal resolution.

Within a sampling period, the AFE can sum up to 256 sequential pulses. As shown in Figure 15, samples acquired by the AFE are clipped to 20 bits at the output of the AFE. Additional resolution, up to 27 bits, can be achieved by averaging between sampling periods. This accumulated data of N samples is stored as 27-bit values and can be read out directly by using the 32-bit output registers or the 32-bit FIFO configuration.

When using the averaging feature set up by the register, subsequent pulses can be averaged by powers of 2. The user can select from 2, 4, 8 ... up to 128 samples to be averaged. Pulse data is still acquired by the AFE at the sampling frequency,  $f_{SAMPLE}$  (Register 0x12), but new data is written to the registers at the rate of  $f_{SAMPLE}/N$  every N<sup>th</sup> sample. This new data consists of the sum of the previous N samples. The full 32-bit sum is stored in the 32-bit registers. However, before sending this data to the FIFO, a divide by N operation occurs. This divide operation maintains bit depth to prevent clipping on the FIFO.

Use this between sample averaging to lower the noise while maintaining 16-bit resolution. If the pulse count registers are kept to 8 or less, the 16-bit width is never exceeded. Therefore, when using Register 0x15 to average subsequent pulses, many pulses can be accumulated without exceeding the 16-bit word width. This can reduce the number of FIFO reads required by the host processor.

### Data Read

The host processor reads output data from the ADPD103, via the I<sup>2</sup>C protocol, from the data registers or from the FIFO. New output data is made available every N samples, where N is the user configured averaging factor. The averaging factors for Time Slot A and Time Slot B are configurable independently of each other. If they are the same, both time slots can be configured to save data to the FIFO. If the two averaging factors are different, only one time slot can save data to the FIFO; data from the other time slot can be read from the output registers.

The data read operations are described in more detail in the Reading Data section.

Figure 16. Example of a Photoplethysmography (PPG) Signal Sampled at a Data Rate of 10 Hz Using Five Pulses per Sample

# **AFE OPERATION**

The timing within each pulse burst is important for optimizing the operation of the ADPD103. Figure 17 shows the timing waveforms for a single time slot as an LED pulse response propagates through the analog block of the AFE. The first graph, shown in green, shows the ideal LED pulsed output. The filtered LED response, shown in blue, shows the output of the analog integrator. The third graph, shown in orange, illustrates an optimally placed integration window. When programmed to the optimized value, the full signal of the filtered LED response can be integrated. The AFE integration window is then applied to the output of the bandpass filter (BPF) and the result is sent to the ADC and summed for N pulses. If the AFE window is not correctly sized or located, all of the receive signal is not properly reported and system performance is not optimal; therefore, it is important to verify proper AFE position for every new hardware design or the LED width.

# AFE INTEGRATION OFFSET ADJUSTMENT

The AFE integration width must be equal or larger than the LED width. As AFE width increases, the output noise increases and the ability to suppress high frequency content from the environment decreases. It is therefore desirable to keep the AFE integration width small. However, if the AFE width is too small, the LED signal is attenuated. With most hardware selections, the AFE width produces the optimal SNR at 1  $\mu$ s more than the LED width. After setting LED width, LED offset, and AFE width, the ADC offset can then be optimized. The AFE offset must be manually set such that the falling edge of the first segment of the integration window matches the zero crossing of the filtered LED response.

Figure 17. AFE Operation Diagram

# **Data Sheet**

### **AFE Integration Offset Starting Point**

The starting point of this offset, as expressed in microseconds, is set such that the falling edge of the integration window aligns with the falling edge of the LED.

*LED\_FALLING\_EDGE = LED\_OFFSET + LED\_WIDTH*

and,

AFE\_INTEGRATION\_FALLING\_EDGE = 9 + AFE\_OFFSET + AFE\_WIDTH

If both falling edges are set equal to each other, solve for AFE\_OFFSET to obtain the following equation:

AFE\_OFFSET\_STARTING\_POINT = LED\_OFFSET + LED\_WIDTH – 9 – AFE\_WIDTH

Setting the AFE offset to any point in time earlier than the starting point is equivalent to setting the integration in the future; the AFE cannot integrate the result from an LED pulse that has not yet occurred. As a result, an AFE\_OFFSET value less than the AFE\_OFFSET\_STARTING\_POINT is an erroneous setting. Such a result may indicate that current in the TIA is operating in the reverse direction from the intended schematic, where the LED pulse is causing the current to leave the TIA rather than enter it.

Because, for most setups, the AFE\_WIDTH is 1 µs wider than the LED\_WIDTH, the AFE\_OFFSET\_STARTING\_POINT value is typically 10 µs less than the LED\_OFFSET value. Any value less than LED\_OFFSET – 10 is erroneous. The optimal AFE offset is some time after the AFE\_OFFSET\_STARTING\_ POINT. The band-pass filter response, LED response, and photodiode response each add some delay. In general, the component choice, board layout, LED\_OFFSET, and LED\_WIDTH are the variables that can change the AFE\_OFFSET. After a specific design is set, the AFE\_OFFSET can be locked down and does not need to be optimized further.

### Sweeping the AFE Position

The AFE offsets for Time Slot A and Time Slot B are controlled by Bits[10:0] of Register 0x39 and Register 0x3B, respectively. Each LSB represents one cycle of the 32 MHz clock, or 31.25 ns.

| Table | 14. | AFE | Window | Settings |

|-------|-----|-----|--------|----------|

|-------|-----|-----|--------|----------|

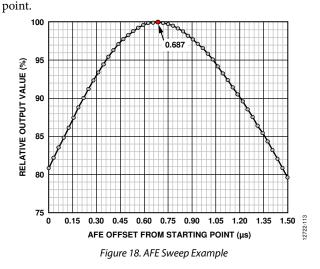

The register can be thought of as  $2^{11-1}$  of these 31.25 ns steps, or it can be broken into an AFE COARSE setting using Bits[10:5] to represent 1 µs steps and Bits[4:0] to represent 31.25 ns steps. Sweeping the AFE position from the starting point to find a local maximum is the recommended way to optimize the AFE offset. The setup for this test is to allow the LED light to fall on the photodiode in a static way. This is typically done with a reflecting surface at a fixed distance. The AFE position can then be swept to look for changes in the output level. When adjusting the AFE position, it is important to sweep the position using the 31.25 ns steps. Typically, a local maximum is found within 2 µs of the starting point for most systems. Figure 18 shows an example of an AFE sweep, where 0 on the x-axis represents the AFE starting point defined previously. Each data point in the plot corresponds to one 31.25 ns step of the AFE\_OFFSET. The optimal location for AFE\_OFFSET in this example is 0.687 µs from the AFE starting

Table 14 lists some typical LED and AFE values after optimization. In general, it is not recommended to use the AFE\_OFFSET numbers in Table 14 without first verifying them against the AFE sweep method. Repeat this method for every new LED width and with every new set of hardware made with the ADPD103. For maximum accuracy, it is recommended that the 32 MHz clock be calibrated prior to sweeping the AFE.

| Table 14: AT L Window Settings     |                                    |                                                 |

|------------------------------------|------------------------------------|-------------------------------------------------|

| LED Register 0x30 or Register 0x35 | AFE Register 0x39 or Register 0x3B | Comment                                         |

| 0x0219                             | 0x19FB                             | 2 μs LED pulse, 3 μs AFE width, 25 μs LED delay |

| 0x0319                             | 0x21F4                             | 3 μs LED pulse, 4 μs AFE width, 25 μs LED delay |

# I<sup>2</sup>C SERIAL INTERFACE

The ADPD103 supports an I<sup>2</sup>C serial interface via the SDA (data) and SCL (clock) pins. All internal registers are accessed through the I<sup>2</sup>C interface.

The ADPD103 conforms to the *UM10204 I<sup>2</sup>C-Bus Specification and User Manual*, Rev. 05—9 October 2012, available from NXP Semiconductors. It supports a fast mode (400 kbps) data transfer. Register read and write are supported, as shown in Figure 19. Figure 2 shows the timing diagram for the I<sup>2</sup>C interface.

### **Slave Address**

The default 7-bit  $I^2C$  slave address for the device is 0x64, followed by the R/W bit. For a write, the default  $I^2C$  slave address is 0xC8; for a read, the default  $I^2C$  address is 0xC9. The slave address is configurable by writing to Register 0x09, Bits[7:1]. When multiple ADPD103 devices are on the same bus lines, the INT and PDSO pins can be used to select specific devices for the address change. Register 0x0D can be used to select a key to enable address changes in specific devices. Use the following procedure to change the slave address when multiple ADPD103 devices are connected to the same  $I^2C$  bus lines:

- 1. Using Register 0x4F, enable the input buffer of the PDSO pin, the INT pin, or both, depending on the key being used.

- 2. For the device identified as requiring an address change, set the INT and/or PDSO pins high or low to match the key being used.

- Write the SLAVE\_ADDRESS\_KEY using Register 0x0D, Bits[15:0] to match the desired function. The allowed keys are shown in Table 24.

- Write the desired SLAVE\_ADDRESS using Register 0x09, Bits[7:1]. While writing to Register 0x09, Bits[7:1], write 0xAD to Register 0x09, Bit[15:8]. Register 0x09 must be written to immediately after writing to Register 0x0D.

- 5. Repeat Step 1 to Step 4 for all the devices that need the SLAVE\_ADDRESS changed.

- 6. Set the INT and PDSO pins as desired for normal operation using the new SLAVE\_ADDRESS for each device.

### I<sup>2</sup>C Write and Read Operations

Figure 19 illustrates the ADPD103 I<sup>2</sup>C write and read operations. Single word and multiword read operations are supported. For a single register read, the host sends a no acknowledge after the second data byte is read and a new register address is needed for each access.

For multiword operations, each pair of data bytes is followed by an acknowledge from the host until the last byte of the last word is read. The host indicates the last read word by sending a no acknowledge. When reading from the FIFO (Register 0x60), the data is automatically advanced to the next word in the FIFO and the space is freed. When reading from other registers, the register address is automatically advanced to the next register, except at Register 0x5F or Register 0x7F, where the address does not increment. This allows lower overhead reading of sequential registers.

All register writes are single word only and require 16 bits (one word) of data.

The software reset (Register 0x0F, Bit 0) is the only command that does not return an acknowledge because the command is instantaneous.

| Term          | Description                                                                                                  |

|---------------|--------------------------------------------------------------------------------------------------------------|

| SCL           | Serial clock.                                                                                                |

| SDA           | Serial address and data.                                                                                     |

| Master        | The master is the device that initiates a transfer, generates clock signals, and terminates a transfer.      |

| Slave         | The slave is the device addressed by a master. The ADPD103 operates as a slave device.                       |

| Start (S)     | A high to low transition on the SDA line while SCL is high; all transactions begin with a start condition.   |

| Start (Sr)    | Repeated start condition.                                                                                    |

| Stop (P)      | A low to high transition on the SDA line while SCL is high. A stop condition terminates all transactions.    |

| ACK           | During the acknowledge or no acknowledge clock pulse, the SDA line is pulled low and remains low.            |

| NACK          | During the acknowledge or no acknowledge clock pulse, the SDA line remains high.                             |

| Slave Address | After a start (S), a 7-bit slave address is sent, which is followed by a data direction bit (read or write). |

| Read (R)      | A 1 indicates a request for data.                                                                            |

| Write (W)     | A 0 indicates a transmission.                                                                                |

### Table 15. Definition of I<sup>2</sup>C Terminology

**Data Sheet**

| I <sup>2</sup> C WRITE |                             |     |                  |     |    |               |        |            |           |        |           |           |          |      |

|------------------------|-----------------------------|-----|------------------|-----|----|---------------|--------|------------|-----------|--------|-----------|-----------|----------|------|