Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Wideband Quadrature Modulator with Integrated Fractional-N PLL and VCOs

Data Sheet ADRF6720-27

#### **FEATURES**

I/Q modulator with integrated fractional-N PLL RF output frequency range: 400 MHz to 3000 MHz Internal LO frequency range: 356.25 MHz to 2855 MHz

Output P1dB: 10.8 dBm at 2140 MHz Output IP3: 31.1 dBm at 2140 MHz

Carrier feedthrough: -44.3 dBm at 2140 MHz Sideband suppression: -40.8 dBc at 2140 MHz Noise floor: -159.5 dBm/Hz at 2140 MHz

Baseband 1 dB modulation bandwidth: >1000 MHz

Baseband input bias level: 2.68 V Power supply: 3.3 V/425 mA

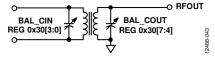

Integrated RF tunable balun allowing single-ended RF output

Multicore integrated VCOs HD3/IP3 optimization

Sideband suppression and carrier feedthrough optimization

High-side/low-side LO injection

Programmable via 3-wire serial port interface (SPI)

40-lead 6 mm × 6 mm LFCSP

#### **APPLICATIONS**

2G/3G/4G/LTE broadband communication systems Microwave point-to-point radios Satellite modems Military/aerospace Instrumentation

#### **GENERAL DESCRIPTION**

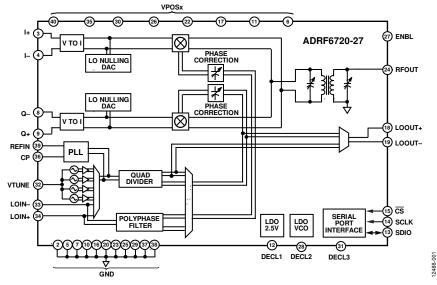

The ADRF6720-27 is a wideband quadrature modulator with an integrated synthesizer ideally suited for 3G and 4G communication systems. The ADRF6720-27 consists of a high linearity broadband modulator, an integrated fractional-N phase-locked loop (PLL), and four low phase noise multicore voltage controlled oscillators (VCOs).

The ADRF6720-27 local oscillator (LO) signal can be generated internally via the on-chip integer-N and fractional-N synthesizers, or externally via a high frequency, low phase noise LO signal. The internal integrated synthesizer enables LO coverage from 356.25 MHz to 2855 MHz using the multicore VCOs. In the case of internal LO generation or external LO input, quadrature signals are generated with a divide by 2 phase splitter. When the ADRF6720-27 is operated with an external  $1 \times LO$  input, a polyphase filter generates the quadrature inputs to the mixer.

The ADRF6720-27 offers digital programmability for carrier feedthrough optimization, sideband suppression, HD3/IP3 optimization, and high-side or low-side LO injection.

The ADRF6720-27 is fabricated using an advanced silicongermanium BiCMOS process. It is available in a 40-lead, RoHS-compliant, 6 mm  $\times$  6 mm LFCSP package with an exposed pad. Performance is specified over the  $-40^{\circ}$ C to  $+85^{\circ}$ C temperature range.

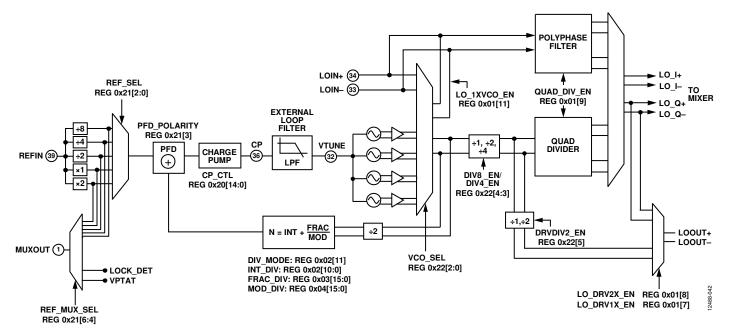

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

Rev. B

Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. No

license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Trademarks and registered trademarks are the property of their respective owners.

# ADRF6720-27\* PRODUCT PAGE QUICK LINKS

Last Content Update: 02/23/2017

# COMPARABLE PARTS -

View a parametric search of comparable parts.

## **EVALUATION KITS**

· ADRF6720-27 Evaluation Board

## **DOCUMENTATION**

## **Data Sheet**

ADRF6720-27: Wideband Quadrature Modulator with Integrated Fractional-N PLL and VCOs

## **User Guides**

UG-742: Evaluating the ADRF6720-27 Wideband Quadrature Modulator with Integrated Fractional-N PLL and VCOs

## **TOOLS AND SIMULATIONS**

ADRF6720-27 S-Parameters

## **DESIGN RESOURCES**

- ADRF6720-27 Material Declaration

- PCN-PDN Information

- · Quality And Reliability

- Symbols and Footprints

## **DISCUSSIONS**

View all ADRF6720-27 EngineerZone Discussions.

## SAMPLE AND BUY 🖵

Visit the product page to see pricing options.

## **TECHNICAL SUPPORT**

Submit a technical question or find your regional support number.

## DOCUMENT FEEDBACK 🖳

Submit feedback for this data sheet.

| Features                                                                           | LO Input                                            | 24 |

|------------------------------------------------------------------------------------|-----------------------------------------------------|----|

| Applications1                                                                      | Loop Filter                                         | 24 |

| General Description                                                                | RF Output                                           | 24 |

| Functional Block Diagram1                                                          | Applications Information                            | 25 |

| Revision History                                                                   | DAC to I/Q Modulator Interfacing                    | 25 |

| Specifications                                                                     | Baseband Bandwidth                                  | 26 |

| Timing Characteristics                                                             | Carrier Feedthrough Nulling                         | 26 |

| Absolute Maximum Ratings 8                                                         | Sideband Suppression Optimization                   | 26 |

| Thermal Resistance                                                                 | Linearity                                           | 27 |

| ESD Caution8                                                                       | LO Amplitude and Common-Mode Voltage                | 27 |

| Pin Configuration and Function Descriptions9                                       | Operating Out of Frequency Range                    | 28 |

| Typical Performance Characteristics                                                | Spurious Performance                                | 28 |

| Theory of Operation                                                                | Layout                                              | 29 |

| LO Generation Block18                                                              | Characterization Setups                             | 30 |

| Baseband21                                                                         | Register Map                                        | 32 |

| Active Mixers21                                                                    | Register Details                                    | 33 |

| Serial Port Interface22                                                            | Outline Dimensions                                  | 43 |

| Basic Connections for Operation23                                                  | Ordering Guide                                      | 43 |

| Power Supply and Grounding23                                                       |                                                     |    |

| Baseband Inputs24                                                                  |                                                     |    |

| REVISION HISTORY                                                                   |                                                     |    |

| 9/15—Rev. A to Rev. B                                                              | 3/15—Rev. 0 to Rev. A                               |    |

| Changed RF <sub>OUT</sub> = 4 dBm to RF <sub>OUT</sub> $\approx$ 4 dBm, and USB to | Added Spurious Performance Section and Figure 57 to |    |

| Sideband SuppressionThroughout                                                     | Figure 59; Renumbered Sequentially                  |    |

| Changes to Spurious Performance Section and Figure 59 28                           | Added Figure 60                                     | 29 |

| Changes to Figure 60                                                               |                                                     |    |

# **SPECIFICATIONS**

$VPOSx = 3.3 \text{ V}, T_A = 25^{\circ}\text{C}$ ; baseband I/Q amplitude = 1 V p-p differential sine waves in quadrature with a 2.68 V dc bias, unless otherwise noted.

Table 1.

| Parameter                      | Test Conditions/Comments                                                                                             | Min    | Тур    | Max  | Unit    |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------|--------|--------|------|---------|

| OPERATING FREQUENCY RANGE      | RF output range                                                                                                      | 400    |        | 3000 | MHz     |

|                                | Internal LO range                                                                                                    | 356.25 |        | 2855 | MHz     |

|                                | External LO range                                                                                                    | 400    |        | 3000 | MHz     |

| RF OUTPUT = 460 MHz            |                                                                                                                      |        |        |      |         |

| Output Power, Pout             | Baseband $V_{IQ} = 1 \text{ V p-p differential}$                                                                     |        | -0.7   |      | dBm     |

| Modulator Voltage Gain         |                                                                                                                      |        | -4.68  |      | dB      |

| Output P1dB                    |                                                                                                                      |        | 6.1    |      | dBm     |

| Carrier Feedthrough            |                                                                                                                      |        | -53.0  |      | dBm     |

| Sideband Suppression           |                                                                                                                      |        | -50.2  |      | dBc     |

| Quadrature Error               |                                                                                                                      |        | 0.18   |      | Degrees |

| I/Q Amplitude Balance          |                                                                                                                      |        | 0.023  |      | dB      |

| Second Harmonic                | $P_{OUT} - P(f_{LO} \pm (2 \times f_{BB}))$                                                                          |        | -77.1  |      | dBc     |

| Third Harmonic                 | $P_{OUT} - P(f_{LO} \pm (3 \times f_{BB}))$                                                                          |        | -61.5  |      | dBc     |

| Output IP2                     | $f1_{BB} = 3.5$ MHz, $f2_{BB} = 4.5$ MHz, baseband I/Q amplitude per tone = 0.3 V p-p differential                   |        | 58.1   |      | dBm     |

| Output IP3                     | $f1_{BB} = 3.5$ MHz, $f2_{BB} = 4.5$ MHz, baseband I/Q amplitude per tone = 0.3 V p-p differential                   |        | 27.2   |      | dBm     |

| Noise Floor                    | I/Q input with 2.68 V dc bias and no RF output, 20 MHz carrier offset                                                |        | -161.2 |      | dBm/Hz  |

|                                | I/Q input with 2.68 V dc bias and –10 dBm RF output, 20 MHz carrier offset                                           |        | -160.1 |      | dBm/Hz  |

| RF OUTPUT = 940 MHz            |                                                                                                                      |        |        |      |         |

| Output Power, P <sub>OUT</sub> | Baseband $V_{IQ} = 1 \text{ V p-p differential}$                                                                     |        | 5.0    |      | dBm     |

| Modulator Voltage Gain         |                                                                                                                      |        | 1.02   |      | dB      |

| Output P1dB                    |                                                                                                                      |        | 11.75  |      | dBm     |

| Carrier Feedthrough            |                                                                                                                      |        | -45.5  |      | dBm     |

| Sideband Suppression           |                                                                                                                      |        | -47.3  |      | dBc     |

| Quadrature Error               |                                                                                                                      |        | -0.05  |      | Degrees |

| I/Q Amplitude Balance          |                                                                                                                      |        | 0.022  |      | dB      |

| Second Harmonic                | $P_{OUT} - P(f_{LO} \pm (2 \times f_{BB}))$                                                                          |        | -69.5  |      | dBc     |

| Third Harmonic                 | $P_{OUT} - P(f_{LO} \pm (3 \times f_{BB}))$                                                                          |        | -60.6  |      | dBc     |

| Output IP2                     | $f1_{BB} = 3.5 \text{ MHz}$ , $f2_{BB} = 4.5 \text{ MHz}$ , baseband I/Q amplitude per tone = 0.3 V p-p differential |        | 65.8   |      | dBm     |

| Output IP3                     | $f1_{BB} = 3.5$ MHz, $f2_{BB} = 4.5$ MHz, baseband I/Q amplitude per tone = 0.3 V p-p differential                   |        | 34.8   |      | dBm     |

| Noise Floor                    | I/Q input with 2.68 V dc bias and no RF output, 20 MHz carrier offset                                                |        | -158.2 |      | dBm/Hz  |

|                                | I/Q input with 2.68 V dc bias and –10 dBm RF output, 20 MHz carrier offset                                           |        | -157.3 |      | dBm/Hz  |

| RF OUTPUT = 1900 MHz           |                                                                                                                      |        |        |      |         |

| Output Power, Pout             | Baseband $V_{IQ} = 1 \text{ V p-p differential}$                                                                     |        | 4.5    |      | dBm     |

| Modulator Voltage Gain         |                                                                                                                      |        | 0.52   |      | dB      |

| Output P1dB                    |                                                                                                                      |        | 11.4   |      | dBm     |

| Carrier Feedthrough            |                                                                                                                      |        | -37.5  |      | dBm     |

| Sideband Suppression           |                                                                                                                      |        | -40.4  |      | dBc     |

| Quadrature Error               |                                                                                                                      |        | 1.21   |      | Degrees |

| I/Q Amplitude Balance          |                                                                                                                      |        | 0.006  |      | dB      |

| Second Harmonic                | $P_{OUT} - P(f_{LO} \pm (2 \times f_{BB}))$                                                                          |        | -65.0  |      | dBc     |

| Third Harmonic                 | $P_{OUT} - P(f_{LO} \pm (3 \times f_{BB}))$                                                                          |        | -61.4  |      | dBc     |

| Parameter              | Test Conditions/Comments                                                                                         | Min | Тур Ма        | x Unit  |

|------------------------|------------------------------------------------------------------------------------------------------------------|-----|---------------|---------|

| Output IP2             | f1 <sub>BB</sub> = 3.5 MHz, f2 <sub>BB</sub> = 4.5 MHz, baseband I/Q amplitude per tone = 0.3 V p-p differential |     | 59.8          | dBm     |

| Output IP3             | $f1_{BB} = 3.5$ MHz, $f2_{BB} = 4.5$ MHz, baseband I/Q amplitude per tone = 0.3 V p-p differential               |     | 32.7          | dBm     |

| Noise Floor            | I/Q input with 2.68 V dc bias and no RF output, 20 MHz carrier offset                                            |     | -157.5        | dBm/Hz  |

|                        | I/Q input with 2.68 V dc bias and –10 dBm RF output, 20 MHz carrier offset                                       |     | -156.6        | dBm/Hz  |

| RF OUTPUT = 2140 MHz   |                                                                                                                  |     |               |         |

| Output Power, Pout     | Baseband $V_{IQ} = 1 \text{ V p-p differential}$                                                                 |     | 4.0           | dBm     |

| Modulator Voltage Gain |                                                                                                                  |     | 0.02          | dB      |

| Output P1dB            |                                                                                                                  |     | 10.8          | dBm     |

| Carrier Feedthrough    |                                                                                                                  |     | -44.3         | dBm     |

| Sideband Suppression   |                                                                                                                  |     | -40.8         | dBc     |

| Quadrature Error       |                                                                                                                  |     | -0.78         | Degrees |

| I/Q Amplitude Balance  |                                                                                                                  |     | -0.015        | dB      |

| Second Harmonic        | $P_{OUT} - P(f_{LO} \pm (2 \times f_{BB}))$                                                                      |     | -58.4         | dBc     |

| Third Harmonic         | $P_{OUT} - P(f_{LO} \pm (3 \times f_{BB}))$                                                                      |     | -67.3         | dBc     |

| Output IP2             | $f1_{BB} = 3.5$ MHz, $f2_{BB} = 4.5$ MHz, baseband I/Q amplitude per tone = 0.3 V p-p differential               |     | 58.7          | dBm     |

| Output IP3             | $f1_{BB} = 3.5$ MHz, $f2_{BB} = 4.5$ MHz, baseband I/Q amplitude per tone = 0.3 V p-p differential               |     | 31.1          | dBm     |

| Noise Floor            | I/Q input with 2.68 V dc bias and no RF output, 20 MHz carrier offset                                            |     | -159.5        | dBm/Hz  |

|                        | I/Q input with 2.68 V dc bias and –10 dBm RF output, 20 MHz carrier offset                                       |     | -158.6        | dBm/Hz  |

| RF OUTPUT = 2300 MHz   |                                                                                                                  |     |               |         |

| Output Power, Pout     | Baseband $V_{IQ} = 1 V p-p differential$                                                                         |     | 3.5           | dBm     |

| Modulator Voltage Gain |                                                                                                                  |     | -0.48         | dB      |

| Output P1dB            |                                                                                                                  |     | 10.3          | dBm     |

| Carrier Feedthrough    |                                                                                                                  |     | -40.8         | dBm     |

| Sideband Suppression   |                                                                                                                  |     | -37.4         | dBc     |

| Quadrature Error       |                                                                                                                  |     | -1.38         | Degrees |

| I/Q Amplitude Balance  |                                                                                                                  |     | -0.015        | dB      |

| Second Harmonic        | $P_{OUT} - P(f_{LO} \pm (2 \times f_{BB}))$                                                                      |     | -58.8         | dBc     |

| Third Harmonic         | $P_{OUT} - P(f_{LO} \pm (3 \times f_{BB}))$                                                                      |     | -65.8         | dBc     |

| Output IP2             | $f1_{BB} = 3.5$ MHz, $f2_{BB} = 4.5$ MHz, baseband I/Q amplitude per tone = 0.3 V p-p differential               |     | 57.5          | dBm     |

| Output IP3             | $f1_{BB} = 3.5$ MHz, $f2_{BB} = 4.5$ MHz, baseband I/Q amplitude per tone = 0.3 V p-p differential               |     | 28.1          | dBm     |

| Noise Floor            | I/Q input with 2.68 V dc bias and no RF output, 20 MHz carrier offset                                            |     | -158.6        | dBm/Hz  |

|                        | I/Q input with 2.68 V dc bias and –10 dBm RF output, 20 MHz carrier offset                                       |     | <b>–157.5</b> | dBm/Hz  |

| RF OUTPUT = 2600 MHz   |                                                                                                                  |     |               |         |

| Output Power, Pout     | Baseband $V_{IQ} = 1 \text{ V p-p differential}$                                                                 |     | 2.9           | dBm     |

| Modulator Voltage Gain |                                                                                                                  |     | -1.08         | dB      |

| Output P1dB            |                                                                                                                  |     | 9.9           | dBm     |

| Carrier Feedthrough    |                                                                                                                  |     | -37.1         | dBm     |

| Sideband Suppression   |                                                                                                                  |     | -40.7         | dBc     |

| Quadrature Error       |                                                                                                                  |     | -0.80         | Degrees |

| I/Q Amplitude Balance  |                                                                                                                  |     | 0.003         | dB      |

| Second Harmonic        | $P_{OUT} - P(f_{LO} \pm (2 \times f_{BB}))$                                                                      |     | -61.2         | dBc     |

| Third Harmonic         | $P_{OUT} - P(f_{LO} \pm (3 \times f_{BB}))$                                                                      |     | -59.1         | dBc     |

| Output IP2             | $f1_{BB} = 3.5$ MHz, $f2_{BB} = 4.5$ MHz, baseband I/Q amplitude per tone = 0.3 V p-p differential               |     | 53.5          | dBm     |

| Parameter                                                      | Test Conditions/Comments                                                                                             | Min  | Тур          | Max | Unit      |

|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|------|--------------|-----|-----------|

| Output IP3                                                     | $f1_{BB} = 3.5 \text{ MHz}$ , $f2_{BB} = 4.5 \text{ MHz}$ , baseband I/Q amplitude per tone = 0.3 V p-p differential |      | 27.9         |     | dBm       |

| Noise Floor                                                    | I/Q input with 2.68 V dc bias and no RF output, 20 MHz carrier offset                                                |      | -158.6       |     | dBm/Hz    |

|                                                                | I/Q input with 2.68 V dc bias and –10 dBm RF output, 20 MHz carrier offset                                           |      | -157.3       |     | dBm/Hz    |

| SYNTHESIZER SPECIFICATIONS                                     | Synthesizer specifications referenced to the modulator output                                                        |      |              |     |           |

| Figure of Merit (FOM) <sup>1</sup>                             |                                                                                                                      |      | -218.5       |     | dBc/Hz/Hz |

| REFERENCE CHARACTERISTICS                                      | REFIN, MUXOUT pins                                                                                                   |      |              |     |           |

| REFIN Input Frequency                                          |                                                                                                                      | 5.7  |              | 320 | MHz       |

| REFIN Input Amplitude                                          |                                                                                                                      |      | 4            |     | dBm       |

| Phase Detector Frequency                                       |                                                                                                                      | 11.4 |              | 40  | MHz       |

| MUXOUT Output Level                                            | Low (lock detect output selected)                                                                                    |      | 0.25         |     | V         |

| -                                                              | High (lock detect output selected)                                                                                   |      | 2.7          |     | V         |

| MUXOUT Duty Cycle                                              |                                                                                                                      |      | 50           |     | %         |

| CHARGE PUMP                                                    |                                                                                                                      |      |              |     |           |

| Charge Pump Current                                            | Programmable to 250 μA, 500 μA, 750 μA, or 1000 μA                                                                   |      | 1000         |     | μΑ        |

| Output Compliance Range                                        |                                                                                                                      | 1    |              | 2.8 | V         |

| PHASE NOISE, FREQUENCY = 460 MHz, f <sub>PFD</sub> = 38.4 MHz  | Closed-loop operation (20 kHz loop filter, see Figure 44 for loop filter design)                                     |      |              |     |           |

|                                                                | 10 kHz offset                                                                                                        |      | -102.1       |     | dBc/Hz    |

|                                                                | 100 kHz offset                                                                                                       |      | -125.2       |     | dBc/Hz    |

|                                                                | 1 MHz offset                                                                                                         |      | -144.4       |     | dBc/Hz    |

|                                                                | 5 MHz offset                                                                                                         |      | -149.6       |     | dBc/Hz    |

|                                                                | 10 MHz offset                                                                                                        |      | -150.8       |     | dBc/Hz    |

|                                                                | 20 MHz offset                                                                                                        |      | -150.6       |     | dBc/Hz    |

| Integrated Phase Noise                                         | 1 kHz to 40 MHz integration bandwidth, with spurs                                                                    |      | 0.09         |     | °rms      |

| Reference Spurs                                                | f <sub>PFD</sub>                                                                                                     |      | <b>-97.7</b> |     | dBc       |

| т.                                                             | fPFD × 2                                                                                                             |      | -93.3        |     | dBc       |

|                                                                | f <sub>PFD</sub> × 3                                                                                                 |      | -91.5        |     | dBc       |

|                                                                | fPED × 4                                                                                                             |      | -96.2        |     | dBc       |

| PHASE NOISE, FREQUENCY = 940 MHz, f <sub>PFD</sub> = 38.4 MHz  | Closed-loop operation (20 kHz loop filter, see Figure 44 for loop filter design)                                     |      |              |     |           |

|                                                                | 10 kHz offset                                                                                                        |      | -97.9        |     | dBc/Hz    |

|                                                                | 100 kHz offset                                                                                                       |      | -121.3       |     | dBc/Hz    |

|                                                                | 1 MHz offset                                                                                                         |      | -144.3       |     | dBc/Hz    |

|                                                                | 5 MHz offset                                                                                                         |      | -153.7       |     | dBc/Hz    |

|                                                                | 10 MHz offset                                                                                                        |      | -154.3       |     | dBc/Hz    |

|                                                                | 20 MHz offset                                                                                                        |      | -154.7       |     | dBc/Hz    |

| Integrated Phase Noise                                         | 1 kHz to 40 MHz integration bandwidth, with spurs                                                                    |      | 0.15         |     | °rms      |

| Reference Spurs                                                | f <sub>PFD</sub>                                                                                                     |      | -99.2        |     | dBc       |

|                                                                | f <sub>PFD</sub> × 2                                                                                                 |      | -92.3        |     | dBc       |

|                                                                | f <sub>PFD</sub> × 3                                                                                                 |      | -95.2        |     | dBc       |

|                                                                | f <sub>PFD</sub> × 4                                                                                                 |      | -101.3       |     | dBc       |

| PHASE NOISE, FREQUENCY = 1900 MHz, f <sub>PFD</sub> = 38.4 MHz | Closed-loop operation (20 kHz loop filter, see Figure 44 for loop filter design)                                     |      |              |     |           |

|                                                                | 10 kHz offset                                                                                                        |      | -92.2        |     | dBc/Hz    |

|                                                                | 100 kHz offset                                                                                                       |      | -114.8       |     | dBc/Hz    |

|                                                                | 1 MHz offset                                                                                                         |      | -139.8       |     | dBc/Hz    |

|                                                                | 5 MHz offset                                                                                                         |      | -151.4       |     | dBc/Hz    |

|                                                                | 10 MHz offset                                                                                                        |      | -152.8       |     | dBc/Hz    |

|                                                                | 20 MHz offset                                                                                                        |      | -153.4       |     | dBc/Hz    |

| Integrated Phase Noise                                         | 1 kHz to 40 MHz integration bandwidth, with spurs                                                                    |      | 0.31         |     | °rms      |

| Parameter                                                      | Test Conditions/Comments                                                                    | Min    | Тур    | Max  | Unit   |

|----------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------|--------|------|--------|

| Reference Spurs                                                | f <sub>PFD</sub>                                                                            |        | -93.2  |      | dBc    |

|                                                                | f <sub>PFD</sub> × 2                                                                        |        | -86.8  |      | dBc    |

|                                                                | f <sub>PFD</sub> × 3                                                                        |        | -89.8  |      | dBc    |

|                                                                | f <sub>PFD</sub> × 4                                                                        |        | -101.7 |      | dBc    |

| PHASE NOISE, FREQUENCY = 2140 MHz, f <sub>PFD</sub> = 38.4 MHz | Closed-loop operation (20 kHz loop filter, see Figure 44 for loop filter design)            |        |        |      |        |

| , -                                                            | 10 kHz offset                                                                               |        | -92.9  |      | dBc/Hz |

|                                                                | 100 kHz offset                                                                              |        | -116.2 |      | dBc/Hz |

|                                                                | 1 MHz offset                                                                                |        | -140.3 |      | dBc/Hz |

|                                                                | 5 MHz offset                                                                                |        | -150.7 |      | dBc/Hz |

|                                                                | 10 MHz offset                                                                               |        | -151.8 |      | dBc/Hz |

|                                                                | 20 MHz offset                                                                               |        | -152.5 |      | dBc/Hz |

| Integrated Phase Noise                                         | 1 kHz to 40 MHz integration bandwidth, with spurs                                           |        | 0.29   |      | °rms   |

| Reference Spurs                                                | f <sub>PFD</sub>                                                                            |        | -91.3  |      | dBc    |

| neierence spars                                                | $f_{PFD} \times 2$                                                                          |        | -90.3  |      | dBc    |

|                                                                | fpp × 3                                                                                     |        | -85.6  |      | dBc    |

|                                                                | $f_{PFD} \times 4$                                                                          |        | -91.0  |      | dBc    |

| PHASE NOISE, FREQUENCY = 2300 MHz, f <sub>PFD</sub> = 38.4 MHz | Closed-loop operation (20 kHz loop filter, see Figure 44 for loop filter design)            |        | 7.10   |      |        |

| 2300 1111 12, 1770 30.1 1111 12                                | 10 kHz offset                                                                               |        | -94.6  |      | dBc/Hz |

|                                                                | 100 kHz offset                                                                              |        | –114.8 |      | dBc/Hz |

|                                                                | 1 MHz offset                                                                                |        | -139.0 |      | dBc/Hz |

|                                                                | 5 MHz offset                                                                                |        | -149.4 |      | dBc/Hz |

|                                                                | 10 MHz offset                                                                               |        | -151.1 |      | dBc/Hz |

|                                                                | 20 MHz offset                                                                               |        | -151.5 |      | dBc/Hz |

| Integrated Phase Noise                                         | 1 kHz to 40 MHz integration bandwidth, with spurs                                           |        | 0.26   |      | °rms   |

| Reference Spurs                                                | f <sub>PFD</sub>                                                                            |        | -96.1  |      | dBc    |

| neierence spars                                                | fpp × 2                                                                                     |        | -91.9  |      | dBc    |

|                                                                | fpfD × 3                                                                                    |        | -88.2  |      | dBc    |

|                                                                | f <sub>PFD</sub> × 4                                                                        |        | -94.8  |      | dBc    |

| PHASE NOISE, FREQUENCY = 2600 MHz, f <sub>PFD</sub> = 38.4 MHz | Closed-loop operation (20 kHz loop filter, see Figure 44 for loop filter design)            |        |        |      |        |

|                                                                | 10 kHz offset                                                                               |        | -92.4  |      | dBc/Hz |

|                                                                | 100 kHz offset                                                                              |        | -111.4 |      | dBc/Hz |

|                                                                | 1 MHz offset                                                                                |        | -137.2 |      | dBc/Hz |

|                                                                | 5 MHz offset                                                                                |        | -147.7 |      | dBc/Hz |

|                                                                | 10 MHz offset                                                                               |        | -148.9 |      | dBc/Hz |

|                                                                | 20 MHz offset                                                                               |        | -149.9 |      | dBc/Hz |

| Integrated Phase Noise                                         | 1 kHz to 40 MHz integration bandwidth, with spurs                                           |        | 0.36   |      | °rms   |

| Reference Spurs                                                | f <sub>PFD</sub>                                                                            |        | -95.5  |      | dBc    |

| ·                                                              | f <sub>PFD</sub> × 2                                                                        |        | -85.4  |      | dBc    |

|                                                                | f <sub>PFD</sub> × 3                                                                        |        | -93.4  |      | dBc    |

|                                                                | f <sub>PFD</sub> × 4                                                                        |        | -91.0  |      | dBc    |

| LO INPUT/OUTPUT                                                |                                                                                             |        |        |      |        |

| LO Output Frequency Range                                      | 1 × LO mode                                                                                 | 356.25 |        | 2855 | MHz    |

|                                                                | 2 × LO mode                                                                                 | 712.5  |        | 5710 | MHz    |

| LO Output Level                                                | $2 \times LO$ or $1 \times LO$ mode, into a $50 \Omega$ load, LO buffer enabled at 2140 MHz |        |        |      |        |

|                                                                | LO_DRV_LVL = 0                                                                              |        | -5.8   |      | dBm    |

|                                                                | LO_DRV_LVL = 1                                                                              |        | -1.0   |      | dBm    |

|                                                                | LO_DRV_LVL = 2                                                                              |        | 2.2    |      | dBm    |

| LO Input Level                                                 | Externally applied LO, PLL disabled                                                         | -6     | 0      | +6   | dBm    |

| LO Input Impedance                                             | Externally applied LO, PLL disabled                                                         |        | 50     |      | Ω      |

| Parameter                             | Test Conditions/Comments                                                                                  | Min | Тур   | Max | Unit |

|---------------------------------------|-----------------------------------------------------------------------------------------------------------|-----|-------|-----|------|

| BASEBAND INPUTS                       | I± and Q± pins                                                                                            |     |       |     |      |

| I and Q Input DC Bias Level           |                                                                                                           |     | 2.68  |     | V    |

| Bandwidth                             | 1 dB                                                                                                      |     | >1000 |     | MHz  |

| Differential Input<br>Impedance       | Frequency = 100 MHz <sup>2</sup>                                                                          |     | 55    |     | ΚΩ   |

| Differential Input<br>Capacitance     | Frequency = 100 MHz <sup>2</sup>                                                                          |     | 0.97  |     | pF   |

| OUT ENABLE                            | ENBL pin                                                                                                  |     |       |     |      |

| Turn-On Settling Time                 | ENBL low to high (90% of envelope), when Register $0x01[10] = 1$ , Register $0x10[10] = 1$                |     | 170   |     | ns   |

| Turn-Off Settling Time                | ENBL high to low (10% of envelope), when Register $0x01[10] = 1$ , Register $0x10[10] = 1$                |     | 10    |     | ns   |

| DIGITAL LOGIC                         | SCLK, SDIO, CS, and ENBL                                                                                  |     |       |     |      |

| Input Voltage High (V <sub>IH</sub> ) |                                                                                                           | 1.4 |       |     | V    |

| Input Voltage Low $(V_{IL})$          |                                                                                                           |     |       | 0.7 | V    |

| Input Current (I⊪/I∟)                 |                                                                                                           | -1  |       | +1  | μΑ   |

| Input Capacitance (C <sub>IN</sub> )  |                                                                                                           |     | 5     |     | pF   |

| Output Voltage High (V <sub>OH)</sub> | $I_{OH} = -100 \mu\text{A}$                                                                               | 2.3 |       |     | V    |

| Output Voltage Low (V <sub>OL</sub> ) | $I_{OL} = +100  \mu A$                                                                                    |     |       | 0.2 | V    |

| POWER SUPPLIES                        |                                                                                                           |     |       |     |      |

| Voltage Range                         | VPOSx                                                                                                     |     | 3.3   |     | V    |

| Supply Current                        | Tx mode at internal LO mode (PLL, internal VCO , and modulator enabled, LO output driver disabled)        |     | 425   |     | mA   |

|                                       | Tx mode at external 1× LO mode (PLL, internal VCO disabled, modulator enabled, LO output driver disabled) |     | 218   |     | mA   |

|                                       | LO output driver; LO_DRV_LVL bits (Register 0x22[7:6]) = 10                                               |     | 42    |     | mA   |

|                                       | Power-down mode                                                                                           |     | 14.5  |     | mA   |

<sup>&</sup>lt;sup>1</sup> The figure of merit (FOM) is computed as phase noise (dBc/Hz) –  $10log10(f_{PFD})$  –  $20log10(f_{Lo}/f_{PFD})$ . The FOM was measured across the full LO range, with  $f_{REF} = 153.6$  MHz,  $f_{REF}$  power = 4 dBm with a 38.4 MHz  $f_{PFD}$ . The FOM was computed at a 50 kHz offset.

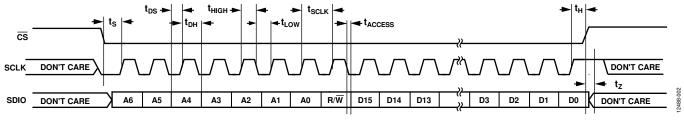

## **TIMING CHARACTERISTICS**

Table 2.

| Parameter                | Description                                                                                | Min | Тур | Max | Unit |

|--------------------------|--------------------------------------------------------------------------------------------|-----|-----|-----|------|

| <b>t</b> <sub>SCLK</sub> | Serial clock period                                                                        | 38  |     |     | ns   |

| $t_{DS}$                 | Setup time between data and rising edge of SCLK                                            | 8   |     |     | ns   |

| t <sub>DH</sub>          | Hold time between data and rising edge of SCLK                                             | 8   |     |     | ns   |

| $t_{\text{S}}$           | Setup time between falling edge of $\overline{\text{CS}}$ and SCLK                         | 10  |     |     | ns   |

| $t_{H}$                  | Hold time between rising edge of $\overline{\text{CS}}$ and SCLK                           | 10  |     |     | ns   |

| t <sub>HIGH</sub>        | Minimum period that SCLK should be in a logic high state                                   | 10  |     |     | ns   |

| t <sub>LOW</sub>         | Minimum period that SCLK should be in a logic low state                                    | 10  |     |     | ns   |

| taccess                  | Maximum time delay between falling edge of SCLK and output data valid for a read operation |     | 13  |     | ns   |

| tz                       | Maximum time delay between CS deactivation and SDIO bus return to high impedance           |     |     | 5   | ns   |

Figure 2. Serial Port Timing Diagram

<sup>&</sup>lt;sup>2</sup> Refer to Figure 47 for a plot of input impedance over frequency.

## **ABSOLUTE MAXIMUM RATINGS**

Table 3.

| Parameter                    | Rating              |

|------------------------------|---------------------|

| Supply Voltage               | −0.3 V to +3.6 V    |

| l+, l–, Q+, Q–               | −0.5 V to +3.6 V    |

| LOIN+, LOIN-                 | 16 dBm differential |

| REFIN                        | −0.3 V to +3.6 V    |

| ENBL                         | −0.3 V to +3.6 V    |

| VTUNE                        | −0.3 V to +3.6 V    |

| CS, SCLK, SDIO               | −0.3 V to +3.6 V    |

| Maximum Junction Temperature | 150°C               |

| Operating Temperature Range  | −40°C to +85°C      |

| Storage Temperature Range    | −65°C to +150°C     |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

## THERMAL RESISTANCE

$\theta_{JA}$  is thermal resistance, junction to ambient (°C/W), and  $\theta_{JC}$  is thermal resistance, junction to case (°C/W).

**Table 4. Thermal Resistance**

| Package Type  | $\theta_{JA}^1$ | $\theta_{JC}^{1}$ | Unit |

|---------------|-----------------|-------------------|------|

| 40-Lead LFCSP | 30.23           | 0.44              | °C/W |

<sup>&</sup>lt;sup>1</sup> See JEDEC standard JESD51-2 for information on optimizing thermal impedance.

## **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

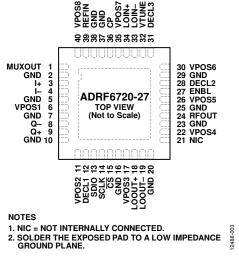

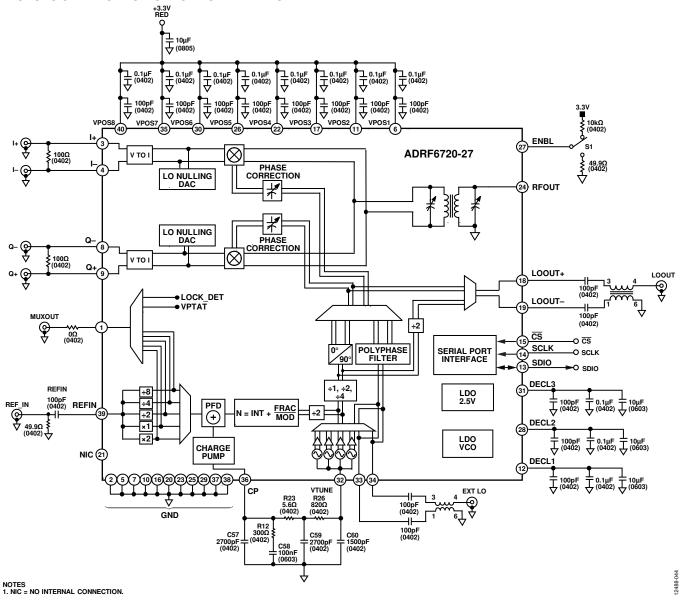

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 3. Pin Configuration

**Table 5. Pin Function Descriptions**

| Pin No. | Mnemonic          | Description                                                                                                                                                                                                                                                                |

|---------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | MUXOUT            | Multiplexer Output. This output allows a digital lock detect signal, a voltage proportional to absolute temperature (VPTAT), or a buffered, frequency-scaled reference signal to be accessed externally. The output is selected by programming Bits[6:4] in Register 0x21. |

| 2, 10   | GND               | Baseband Ground.                                                                                                                                                                                                                                                           |

| 3, 4    | l+, l–            | Differential In-Phase Baseband Inputs.                                                                                                                                                                                                                                     |

| 5, 7    | GND               | Mixer Core (I and Q) Ground.                                                                                                                                                                                                                                               |

| 6       | VPOS1             | 3.3 V Supply Voltage for Baseband. Decouple VPOS1 with 100 pF and 0.1 µF capacitors located close to the pin.                                                                                                                                                              |

| 8, 9    | Q-, Q+            | Differential Quadrature Baseband Inputs.                                                                                                                                                                                                                                   |

| 11      | VPOS2             | 3.3 V Supply Voltage for 2.5 V LDO. Decouple VPOS2 with 100 pF and 0.1 µF capacitors located close to the pin.                                                                                                                                                             |

| 12      | DECL1             | Decoupling Pin for 2.5 V LDO. Connect 100 pF, 0.1 μF, and 10 μF capacitors between this pin and ground.                                                                                                                                                                    |

| 13      | SDIO              | Serial Data Input/Output for SPI.                                                                                                                                                                                                                                          |

| 14      | SCLK              | Serial Clock Input/Output for SPI.                                                                                                                                                                                                                                         |

| 15      | <u>cs</u>         | Chip Select Input/Output for SPI.                                                                                                                                                                                                                                          |

| 16      | GND               | Digital Ground.                                                                                                                                                                                                                                                            |

| 17      | VPOS3             | 3.3 V Supply Voltage for LO. Decouple VPOS3 with 100 pF and 0.1 µF capacitors located close to the pin.                                                                                                                                                                    |

| 18, 19  | LOOUT+,<br>LOOUT- | Differential LO Outputs. Either the internally generated LO or external $1 \times LO/2 \times LO$ is available at $1 \times LO$ or $2 \times LO$ on these pins.                                                                                                            |

| 20      | GND               | LO Ground.                                                                                                                                                                                                                                                                 |

| 21      | NIC               | Not Internally Connected. This pin can be left open or tied to RF ground.                                                                                                                                                                                                  |

| 22      | VPOS4             | 3.3 V Supply Voltage for RF. Decouple VPOS4 with 100 pF and 0.1 µF capacitors located close to the pin.                                                                                                                                                                    |

| 23, 25  | GND               | RF Ground.                                                                                                                                                                                                                                                                 |

| 24      | RFOUT             | Single-Ended 0 V DC RF Output.                                                                                                                                                                                                                                             |

| 26      | VPOS5             | 3.3 V Supply Voltage for RF. Decouple VPOS5 with 100 pF and 0.1 µF capacitors located close to the pin.                                                                                                                                                                    |

| 27      | ENBL              | Enables/Disables the Circuit Blocks. References the settings at Register 0x01 and Register 0x10. Refer to the ENBL section for more information.                                                                                                                           |

| 28      | DECL2             | Decoupling Pin for VCO LDO. Connect 100 pF, 0.1 μF, and 10 μF capacitors between this pin and ground.                                                                                                                                                                      |

| 29      | GND               | VCO Ground.                                                                                                                                                                                                                                                                |

| 30      | VPOS6             | 3.3 V Supply Voltage for VCO LDO. Decouple VPOS6 with 100 pF and 0.1 µF capacitors located close to the pin.                                                                                                                                                               |

| 31      | DECL3             | Decoupling Pin for VCO LDO. Connect 100 pF, 0.1 μF, and 10 μF capacitors between this pin and ground.                                                                                                                                                                      |

| 32      | VTUNE             | VCO Tuning Voltage.                                                                                                                                                                                                                                                        |

| 33, 34  | LOIN-,<br>LOIN+   | Differential External LO Inputs.                                                                                                                                                                                                                                           |

| 35      | VPOS7             | $3.3V$ Supply Voltage for Charge Pump. Decouple VPOS7 with 100 pF and 0.1 $\mu$ F capacitors located close to the pin.                                                                                                                                                     |

| Pin No. | Mnemonic | Description                                                                                                             |

|---------|----------|-------------------------------------------------------------------------------------------------------------------------|

| 36      | СР       | Charge Pump Output.                                                                                                     |

| 37      | GND      | Charge Pump Ground.                                                                                                     |

| 38      | GND      | PLL Reference Ground.                                                                                                   |

| 39      | REFIN    | PLL Reference Input.                                                                                                    |

| 40      | VPOS8    | 3.3 V Supply Voltage for PLL Reference. Decouple VPOS8 with 100 pF and 0.1 $\mu$ F capacitors located close to the pin. |

|         | EP       | Exposed Pad. Solder the exposed pad to a low impedance ground plane.                                                    |

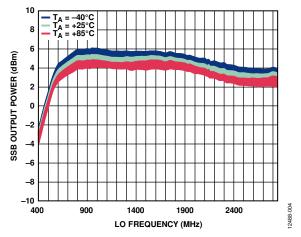

## TYPICAL PERFORMANCE CHARACTERISTICS

$VPOSx = 3.3 \text{ V; } T_A = 25^{\circ}\text{C; baseband I/Q amplitude} = 1 \text{ V p-p differential sine waves in quadrature with a 2.68 V dc bias; baseband I/Q frequency } (f_{BB}) = 1 \text{ MHz; } f_{PFD} = 38.4 \text{ MHz; } f_{REF} = 153.6 \text{ MHz at 4 dBm referred to 50 } \Omega \text{ (1 V p-p); 20 kHz loop filter, unless otherwise noted.}$

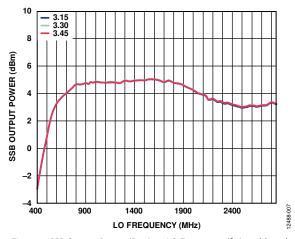

Figure 4. Single Sideband (SSB) Output Power ( $P_{OUT}$ ) vs. LO Frequency ( $f_{LO}$ ) and Temperature; Multiple Devices Shown

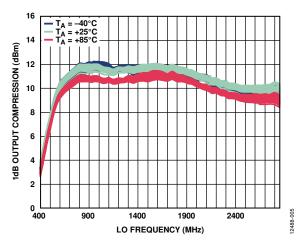

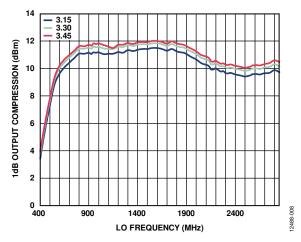

Figure 5. SSB 1 dB Output Compression Point (OP1dB) vs. LO Frequency ( $f_{LO}$ ) and Temperature; Multiple Devices Shown

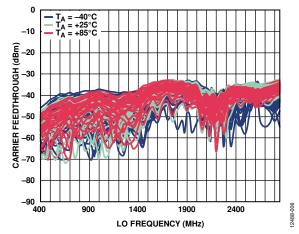

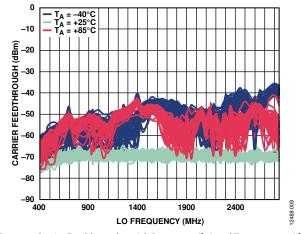

Figure 6. Carrier Feedthrough vs. LO Frequency ( $f_{LO}$ ) and Temperature Before Nulling; Multiple Devices Shown

Figure 7. SSB Output Power ( $P_{OUT}$ ) vs. LO Frequency ( $f_{LO}$ ) and Supply

Figure 8. SSB 1 dB Output Compression Point (OP1dB) vs. LO Frequency ( $f_{LO}$ ) and Supply

Figure 9. Carrier Feedthrough vs. LO Frequency (f<sub>LO</sub>) and Temperature After Nulling Using DCOFF\_I and DCOFF\_Q at 25°C; Multiple Devices Shown

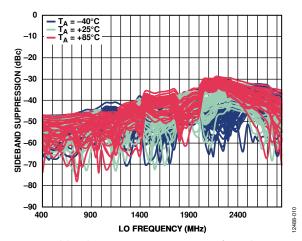

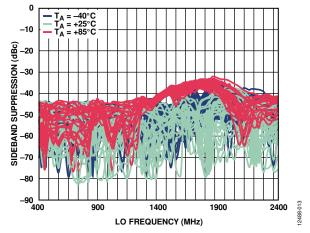

Figure 10. Sideband Suppression vs. LO Frequency (f<sub>LO</sub>) and Temperature Before Nulling; Multiple Devices Shown

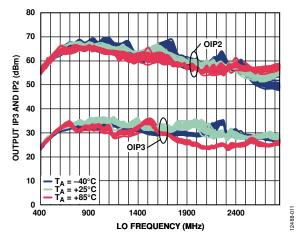

Figure 11. OIP3 and OIP2 vs. LO Frequency ( $f_{LO}$ ) and Temperature ( $P_{OUT} \approx -5$  dBm per Tone); Multiple Devices Shown

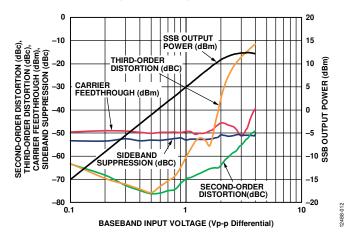

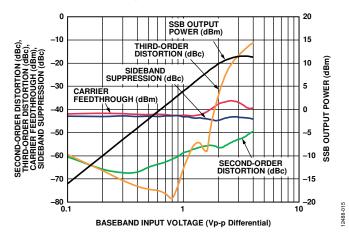

Figure 12. SSB Output Power, Second- and Third-Order Harmonics, Carrier Feedthrough, and Sideband Suppression vs. Baseband Differential Input Voltage ( $f_{OUT} = 940 \text{ MHz}$ )

Figure 13. Sideband Suppression vs. LO Frequency (f<sub>LO</sub>) and Temperature After Nulling Using I\_LO and Q\_LO at 25°C; Multiple Devices Shown

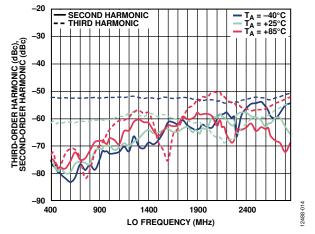

Figure 14. Second- and Third-Order Harmonics vs. LO Frequency ( $f_{LO}$ ) and Temperature ( $P_{OUT} \approx 5 \text{ dBm}$ )

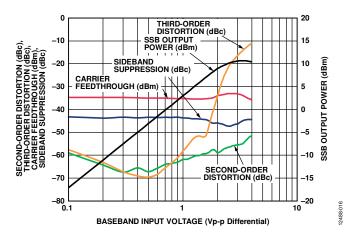

Figure 15. SSB Output Power, Second- and Third-Order Harmonics, Carrier Feedthrough, and Sideband Suppression vs. Baseband Differential Input Voltage ( $f_{OUT} = 2140 \text{ MHz}$ )

Figure 16. SSB Output Power, Second- and Third-Order Harmonics, Carrier Feedthrough, and Sideband Suppression vs. Baseband Differential Input Voltage ( $f_{OUT} = 2600 \text{ MHz}$ )

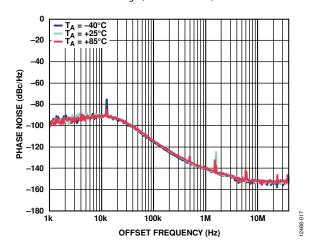

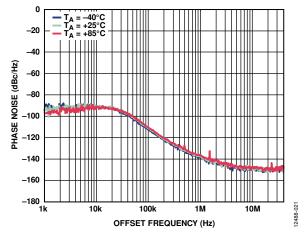

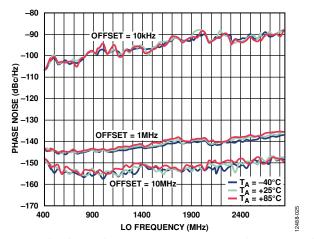

Figure 17. Closed-Loop Phase Noise vs. Offset Frequency and Temperature,  $f_{L0} = 1900 \, \text{MHz}; 20 \, \text{kHz} \, \text{Loop Filter}$

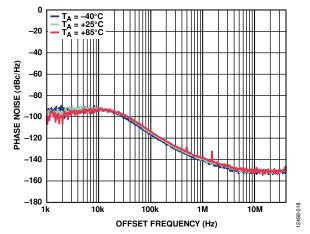

Figure 18. Closed-Loop Phase Noise vs. Offset Frequency and Temperature,  $f_{LO}$  = 2300 MHz; 20 kHz Loop Filter

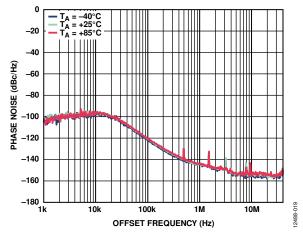

Figure 19. Closed-Loop Phase Noise vs. Offset Frequency and Temperature,  $f_{LO} = 940$  MHz; 20 kHz Loop Filter

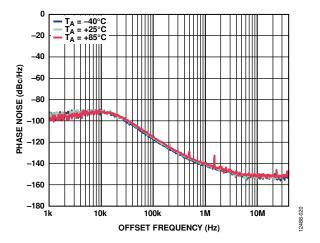

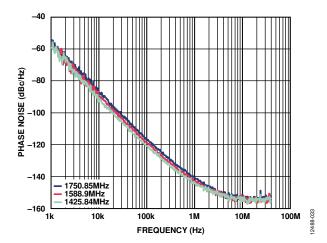

Figure 20. Closed-Loop Phase Noise vs. Offset Frequency and Temperature,  $f_{LO} = 2140 \text{ MHz}$ ; 20 kHz Loop Filter

Figure 21. Closed-Loop Phase Noise vs. Offset Frequency and Temperature,  $f_{LO} = 2600 \text{ MHz}$ ; 20 kHz Loop Filter

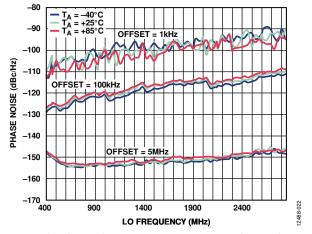

Figure 22. Closed-Loop Phase Noise vs. LO Frequency at 1 kHz, 100 kHz, and 5 MHz Offsets

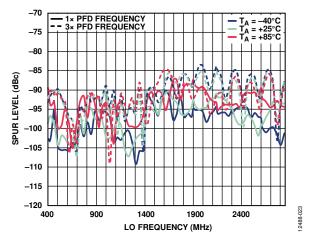

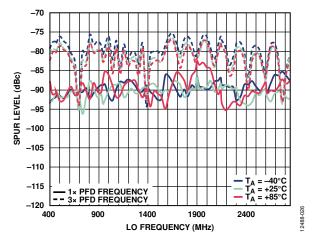

Figure 23. PLL Reference Spurs vs. LO Frequency (1  $\times$  PFD and 3  $\times$  PFD) at Modulator Output

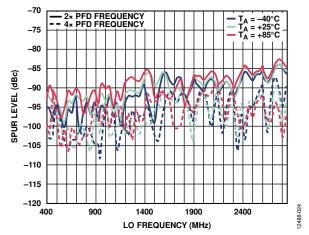

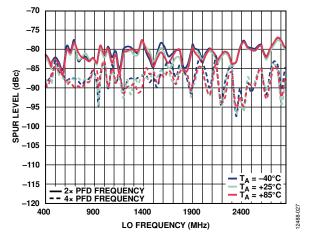

Figure 24. PLL Reference Spurs vs. LO Frequency (2  $\times$  PFD and 4  $\times$  PFD) at Modulator Output

Figure 25. Closed-Loop Phase Noise vs. LO Frequency at 10 kHz, 1 MHz, and 10 MHz Offsets

Figure 26. PLL Reference Spurs vs. LO Frequency (1  $\times$  PFD and 3  $\times$  PFD) at LO Output

Figure 27. PLL Reference Spurs vs. LO Frequency (2  $\times$  PFD and 4  $\times$  PFD) at LO Output

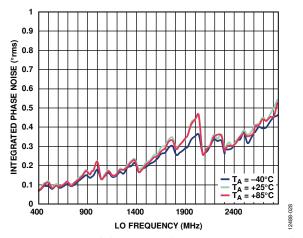

Figure 28. Integrated Phase Noise with Spurs vs. LO Frequency and Temperature

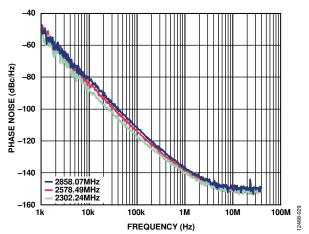

Figure 29. Open-Loop VCO Phase Noise for VCO 0 Measured at 2302.24 MHz, 2578.49 MHz, and 2858.07 MHz (VCO ÷ 2)

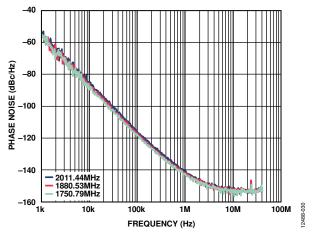

Figure 30. Open-Loop VCO Phase Noise for VCO 2 Measured at 1750.79 MHz, 1880.53 MHz, and 2011.44 MHz (VCO ÷ 2)

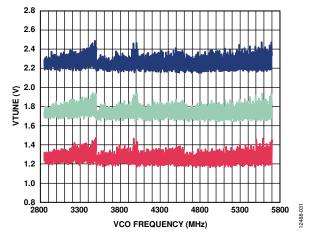

Figure 31. VTUNE vs. VCO Frequency and Temperature

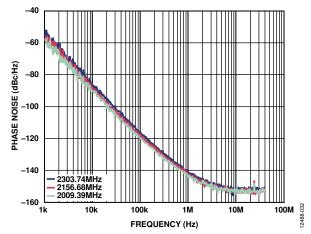

Figure 32. Open-Loop VCO Phase Noise for VCO 1 Measured at 2009.39 MHz, 2156.68 MHz, and 2303.74 MHz (VCO  $\div$  2)

Figure 33. Open-Loop VCO Phase Noise for VCO 3 Measured at 1425.84 MHz, 1588.9 MHz, and 1750.85 MHz (VCO  $\div$  2)

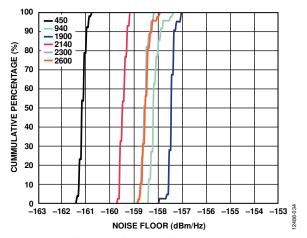

Figure 34. Noise Floor Cumulative Distribution at Various LO Frequencies Using Internal LO; I/Q Input with 2.68 V DC Bias and No RF Output

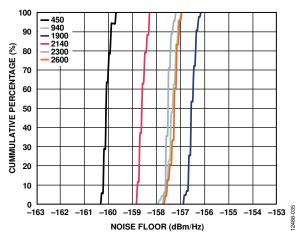

Figure 35. Noise Floor Cumulative Distribution at Various LO Frequencies Using Internal LO; I/Q Input with 2.68 V DC Bias and RF Output = -10 dBm

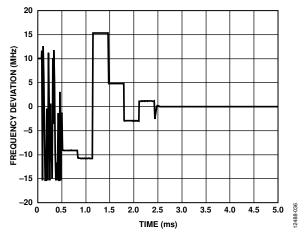

Figure 36. Frequency Deviation from LO Frequency at LO = 1.91 GHz to 1.9 GHz vs. Lock Time

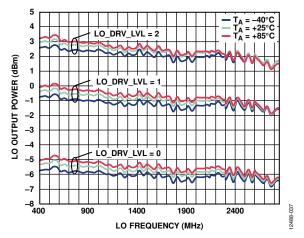

Figure 37. LO Output Power vs. LO Frequency at Various LO\_DRV\_LVL Settings

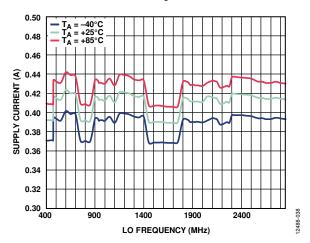

Figure 38. Supply Current vs. LO Frequency and Temperature (PLL and I/Q Modulator Enabled, LO Buffer Disabled)

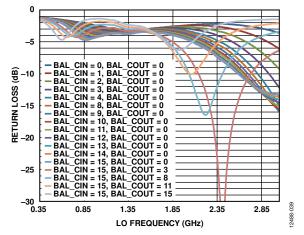

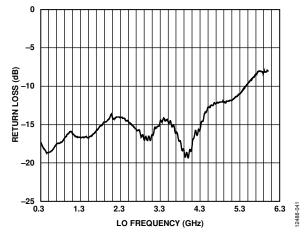

Figure 39. RF Output Return Loss vs. LO Frequency ( $f_{LO}$ ) for Multiple BAL\_CIN and BAL\_COUT Combinations

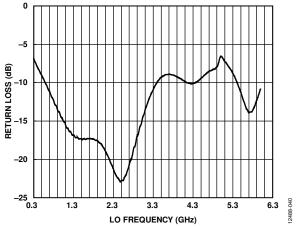

Figure 40. LO Input Return Loss vs. LO Frequency ( $f_{LO}$ )

Figure 41. LO Output Return Loss vs. LO Frequency ( $f_{LO}$ )

## THEORY OF OPERATION

The ADRF6720-27 integrates a high performance broadband I/Q modulator with a fractional-N PLL and low noise multicore VCOs. The baseband inputs mix with the LO generated internally or provided externally, and convert it to a single-ended RF using an integrated RF balun. A block diagram of the device is shown in Figure 1. The ADRF6720-27 is programmed via an SPI.

## **LO GENERATION BLOCK**

The ADRF6720-27 supports the use of both internal and external LO signals for the mixers. The internal LO is generated by an on-chip VCO, which is tunable over an octave frequency range of 2850 MHz to 5710 MHz. The output of the VCO is phase-locked to an external reference clock through a fractional-N PLL that is programmable through the SPI control registers. To produce in-phase and quadrature phase LO signals over the 356.25 MHz to 2855 MHz frequency range to drive the mixers, steer the VCO outputs through a combination of frequency dividers, as shown in Figure 42.

Alternatively, an external signal can be used with the dividers or a polyphase phase splitter to generate the LO signals in quadrature to the mixers. In demanding applications that require the lowest possible phase noise performance, it may be necessary to source the LO signal externally. The different methods of quadrature LO generation and the control register programming needed are listed in Table 6.

#### Internal LO Mode

For internal LO mode, the ADRF6720-27 uses the on-chip PLL and VCO to synthesize the frequency of the LO signal. The PLL, shown in Figure 42, consists of a reference path, phase and frequency detector (PFD), charge pump, and a programmable integer divider with prescaler. The reference path takes in a reference clock and divides it down by a factor of 2, 4, or 8, or multiplies it by a factor of 1 or 2, and then passes it to the PFD. The PFD compares this signal to the divided down signal from the VCO. Depending on the PFD polarity selected, the PFD sends either an up or down signal to the charge pump if the VCO signal is either slow or fast compared to the reference frequency. The charge pump sends a current pulse to the off-chip loop filter to increase or decrease the tuning voltage (V<sub>Tune</sub>).

The ADRF6720-27 integrates four VCO cores, covering an octave range of 2850 MHz to 5710 MHz.

Table 6 lists the frequency range covered by each VCO. The desired VCO can be selected by addressing the VCO\_SEL bits at Register 0x22[2:0].

The LO source and quadrature generation path can be selected by setting the QUAD\_DIV\_EN bit (Register 0x01[9]) and the LO\_1XVCO\_EN bit (Register 0x01[11]).

The mode of the VCO signal through a polyphase filter is intended to extend the operating frequency with an internal VCO and is only useful for baseband input frequencies high enough to prevent the RF output from pulling the VCO.

Figure 42. LO Block Diagram

**Table 6. LO Mode Selection**

| LO<br>Selection | fvco or fext (MHz) | Quadrature<br>Generation | QUAD_DIV_EN<br>(Register 0x01[9]) | LO_1XVCO_EN (Register 0x1[11]) | Enables<br>(Register 0x01[6:0]) | VCO_SEL<br>(Register 0x22[2:0]) |

|-----------------|--------------------|--------------------------|-----------------------------------|--------------------------------|---------------------------------|---------------------------------|

| Internal        | 2850 to 3500       | Divide by 2              | 1                                 | 0                              | 111 111X <sup>1</sup>           | 011                             |

| (VCO)           | 3500 to 4020       | Divide by 2              | 1                                 | 0                              | 111 111X <sup>1</sup>           | 010                             |

|                 | 4020 to 4600       | Divide by 2              | 1                                 | 0                              | 111 111X <sup>1</sup>           | 001                             |

|                 | 4600 to 5710       | Divide by 2              | 1                                 | 0                              | 111 111X <sup>1</sup>           | 000                             |

|                 | 2855 to 3000       | Polyphase                | 0                                 | 1                              | 111 111X <sup>1</sup>           | 011                             |

| External        | 700 to 6000        | Divide by 2              | 1                                 | 0                              | 101 000X <sup>1</sup>           | 1XX <sup>1</sup>                |

|                 | 700 to 3000        | Polyphase                | 0                                 | 0                              | 000 000X <sup>1</sup>           | XXX <sup>1</sup>                |

$<sup>^{1}</sup>$  X = don't care.

### **LO Frequency and Dividers**

The signal coming from the VCO or the external LO inputs goes through a series of dividers before it is buffered to drive the active mixers. Two programmable divide by 2 stages divide the frequency of the incoming signal by 1, 2, or 4 before reaching the quadrature divider that further divides the signal frequency by 2 to generate the in-phase and quadrature phase LO signals for the mixers. The control bits (Register 0x22[4:3]) needed to select the different LO frequency ranges are listed in Table 7.

Table 7. LO Frequency and Dividers

| LO Frequency<br>Range (MHz) | f <sub>vco</sub> /f <sub>Lo</sub> or<br>f <sub>EXTLO</sub> /f <sub>LO</sub> | DIV8_EN<br>(Register<br>0x22[4]) | DIV4_EN<br>(Register<br>0x22[3]) |

|-----------------------------|-----------------------------------------------------------------------------|----------------------------------|----------------------------------|

| 1425 to 2855                | 2                                                                           | 0                                | 0                                |

| 712.5 to 1425               | 4                                                                           | 0                                | 1                                |

| 356.25 to 712.5             | 8                                                                           | 1                                | 1                                |

#### **PLL Frequency Programming**

The N divider with divide by 2 divides down the VCO signal to the PFD frequency. The N divider can be configured for fractional or integer mode by addressing the DIV\_MODE bit (Register 0x02[11]). The default configuration is set for fractional mode. Use the following equations to determine the N value and PLL frequency:

$$\begin{split} f_{PFD} &= \frac{f_{VCO}}{2 \times N} \\ N &= INT + \frac{FRAC}{MOD} \\ f_{LO} &= \frac{f_{VCO}}{LO\_DIVIDER} = \frac{f_{PFD} \times 2 \times N}{LO\_DIVIDER} \end{split}$$

where:

$f_{PFD}$  is the phase frequency detector frequency.

$f_{VCO}$  is the VCO frequency.

N is the fractional divide ratio (INT + FRAC/MOD).

INT is the integer divide ratio programmed in Register 0x02. FRAC is the fractional divider programmed in Register 0x03. MOD is the modulus divide ratio programmed in Register 0x04.  $f_{LO}$  is the LO frequency going to the mixer core when the loop is locked.

*LO\_DIVIDER* is the final frequency divider ratio that divides the frequency of the VCO or the external LO signal down by 2, 4, or 8 before it reaches the mixer, as shown in Table 7.

## Loop Filter

The loop filter is connected between the CP and VTUNE pins. The recommended components for 20 kHz filter designs are shown in Table 8 and referenced in Figure 44.