# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Integrated Dual RF Transmitter, Receiver, and Observation Receiver

**Data Sheet**

## ADRV9009

#### **FEATURES**

Dual transmitters Dual receivers Dual input shared observation receiver Maximum receiver bandwidth: 200 MHz Maximum tunable transmitter synthesis bandwidth: 450 MHz Maximum observation receiver bandwidth: 450 MHz Fully integrated fractional-N RF synthesizers Fully integrated clock synthesizer Multichip phase synchronization for RF LO and baseband clocks JESD204B datapath interface Tunable range: 75 MHz to 6000 MHz

ANALOG DEVICES

#### **APPLICATIONS**

3G/4G/5G TDD macro cell base stations TDD active antenna systems Massive MIMO Phased array radar Electronic warfare Military communications Portable test equipment

#### **GENERAL DESCRIPTION**

The ADRV9009 is a highly integrated, radio frequency (RF), agile transceiver offering dual transmitters and receivers, integrated synthesizers, and digital signal processing functions. The IC delivers a versatile combination of high performance and low power consumption demanded by 3G, 4G, and 5G macro cell time division duplex (TDD) base station applications.

The receive path consists of two independent, wide bandwidth, direct conversion receivers with state-of-the-art dynamic range. The device also supports a wide bandwidth, time shared observation path receiver (ORx) for use in TDD applications. The complete receive subsystem includes automatic and manual attenuation control, dc offset correction, quadrature error correction (QEC), and digital filtering, thus eliminating the need for these functions in the digital baseband. Several auxiliary functions, such as analog to digital converters (ADCs), digital-to-analog converters (DACs), and general-purpose input/outputs (GPIOs) for the power amplifier (PA), and RF front-end control are also integrated.

In addition to automatic gain control (AGC), the ADRV9009 also features flexible external gain control modes, allowing significant flexibility in setting system level gain dynamically.

The received signals are digitized with a set of four high dynamic range, continuous time  $\Sigma$ - $\Delta$  ADCs that provide inherent antialiasing. The combination of the direct conversion architecture, which does not suffer from out of band image mixing, and the lack of aliasing, relaxes the requirements of the RF filters when compared to traditional IF receivers.

The transmitters use an innovative direct conversion modulator that achieves high modulation accuracy with exceptionally low noise.

The observation path consists of a wide bandwidth, direct conversion receiver with state-of-the-art dynamic range.

The fully integrated phase-locked loop (PLL) provides high performance, low power, fractional-N RF frequency synthesis for the transmitter (Tx) and receiver (Rx) signal paths. An additional synthesizer generates the clocks needed for the converters, digital circuits, and the serial interface. A multichip synchronization mechanism synchronizes the phase of the RF local oscillator and baseband clocks between multiple ADRV9009 chips. Precautions are taken to provide the isolation demanded in high performance base station applications. All voltage controlled oscillators (VCOs) and loop filter components are integrated.

The high speed JESD204B interface supports up to 12.288 Gbps lane rates resulting in two lanes per transmitter, and a single lane per receiver in the widest bandwidth mode. The interface also supports interleaved mode for lower bandwidths, thus reducing the total number of high speed data interface lanes to one. Both fixed and floating point data formats are supported. The floating point format allows internal AGC to be invisible to the demodulator device.

The core of the ADRV9009 can be powered directly from 1.3 V and 1.8 V regulators and is controlled via a standard 4-wire serial port. Comprehensive power-down modes are included to minimize power consumption in normal use. The ADRV9009 is packaged in a 12 mm  $\times$  12 mm, 196-ball chip scale ball grid array (CSP\_BGA).

Rev. A

#### Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2018 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

### TABLE OF CONTENTS

| Features                                       |

|------------------------------------------------|

| Applications1                                  |

| General Description                            |

| Revision History                               |

| Functional Block Diagram                       |

| Specifications                                 |

| Current and Power Consumption Specifications12 |

| Timing Diagrams14                              |

| Absolute Maximum Ratings15                     |

| Reflow Profile15                               |

| Thermal Management15                           |

| Thermal Resistance                             |

| ESD Caution15                                  |

| Pin Configuration and Function Descriptions    |

| Typical Performance Characteristics            |

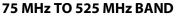

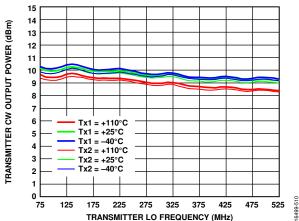

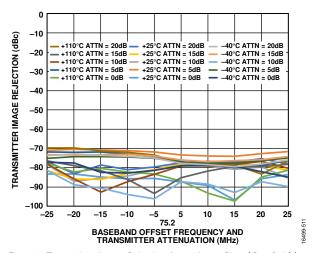

| 75 MHz to 525 MHz Band                         |

| 650 MHz to 3000 MHz Band 42                    |

| 3400 MHz to 4800 MHz Band61                    |

| 5100 MHz to 5900 MHz Band78                    |

| Transmitter Output Impedance                   |

| Observation Receiver Input Impedance           |

| Receiver Input Impedance94                     |

| Terminology                                    |

| Theory of Operation                            |

#### **REVISION HISTORY**

6/2018—Revision A: Initial Version

| Transmitter                                      |     |

|--------------------------------------------------|-----|

| Receiver                                         | 96  |

| Observation Receiver                             | 96  |

| Clock Input                                      | 96  |

| Synthesizers                                     | 96  |

| Serial Peripheral Interface (SPI)                |     |

| JTAG Boundary Scan                               |     |

| Power Supply Sequence                            |     |

| GPIO_x Pins                                      |     |

| Auxiliary Converters                             |     |

| JESD204B Data Interface                          |     |

| Applications Information                         | 99  |

| PCB Layout and Power Supply Recommendations      | 99  |

| PCB Material and Stackup Selection               | 99  |

| Fanout and Trace Space Guidelines                | 101 |

| Component Placement and Routing Guidelines       | 102 |

| RF and JESD204B Transmission Line Layout         | 109 |

| Isolation Techniques Used on the ADRV9009 Custor |     |

|                                                  |     |

| RF Port Interface Information                    |     |

| Outline Dimensions                               |     |

| Ordering Guide                                   | 128 |

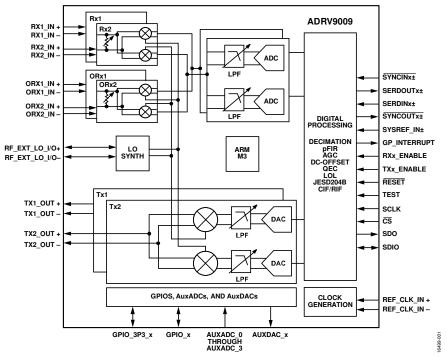

### FUNCTIONAL BLOCK DIAGRAM

Figure 1.

#### **SPECIFICATIONS**

Electrical characteristics at VDDA1P3<sup>1</sup> = 1.3 V, VDDD1P3\_DIG = 1.3 V, VDDA1P8\_TX = 1.8 V, T<sub>J</sub> = full operating temperature range. Local oscillator frequency ( $f_{LO}$ ) = 1800 MHz, unless otherwise noted. The specifications in Table 1 are not deembedded. Refer to the Typical Performance Characteristics section for input/output circuit path loss. The device configuration profile, unless otherwise specified, is as follows: receiver = 200 MHz (in-phase quadrature (IQ) rate = 245.76 MHz), transmitter = 200 MHz/450 MHz (IQ rate = 491.52 MHz), JESD204B rate = 9.8304 GSPS, and device clock = 245.76 MHz. **Table 1.**

| Parameter                                                             | Symbol           | Min  | Тур   | Мах  | Unit    | Test Conditions/Comments                                                                              |

|-----------------------------------------------------------------------|------------------|------|-------|------|---------|-------------------------------------------------------------------------------------------------------|

| TRANSMITTERS                                                          |                  |      |       |      |         |                                                                                                       |

| Center Frequency                                                      |                  | 75   |       | 6000 | MHz     |                                                                                                       |

| Transmitter Synthesis<br>Bandwidth                                    |                  |      |       | 450  | MHz     |                                                                                                       |

| Transmitter Large Signal<br>Bandwidth                                 |                  |      |       | 200  | MHz     |                                                                                                       |

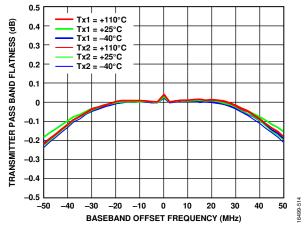

| Peak to Peak Gain<br>Deviation                                        |                  |      | 1.0   |      | dB      | 450 MHz bandwidth, compensated by<br>programmable finite impulse<br>response (FIR) filter             |

| Gain Slope                                                            |                  |      | ±0.1  |      | dB      | Any 20 MHz bandwidth span,<br>compensated by programmable FIR<br>filter                               |

| Deviation from Linear Phase                                           |                  |      | 1     |      | Degrees | 450 MHz bandwidth                                                                                     |

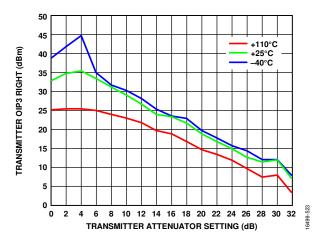

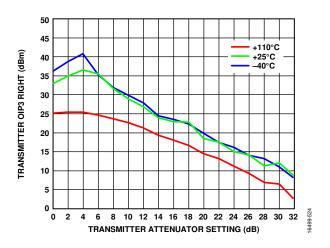

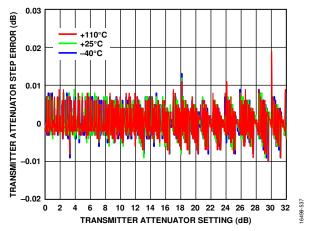

| Transmitter Attenuation<br>Power Control Range                        |                  | 0    |       | 32   | dB      | Signal-to-noise ratio (SNR) maintained for attenuation between 0 dB and 20 dB                         |

| Transmitter Attenuation<br>Power Control<br>Resolution                |                  |      | 0.05  |      | dB      |                                                                                                       |

| Transmitter Attenuation<br>Integral Nonlinearity                      | INL              |      | 0.1   |      | dB      | For any 4 dB step                                                                                     |

| Transmitter Attenuation<br>Differential Nonlinearity                  | DNL              |      | +0.04 |      | dB      | Monotonic                                                                                             |

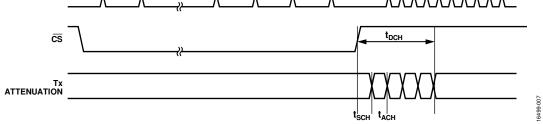

| Transmitter Attenuation<br>SPI-2 Timing                               |                  |      |       |      |         | See Figure 4                                                                                          |

| Time from CS Going High<br>to Change in Transmitter<br>Attenuation    | t <sub>scH</sub> | 19.5 |       | 24   | ns      |                                                                                                       |

| Time Between Consecutive<br>Micro Attenuation Steps                   | t <sub>ACH</sub> | 6.5  |       | 8.1  | ns      | A large change in attenuation can be<br>broken up into a series of smaller<br>attenuation changes     |

| Time Required to Reach<br>Final Attenuation Value                     | t <sub>DCH</sub> |      |       | 800  | ns      | Time required to complete the change in attenuation from start attenuation to final attenuation value |

| Maximum Attenuation<br>Overshoot During<br>Transition                 |                  | -1.0 |       | +0.5 | dB      |                                                                                                       |

| Change in Attenuation per<br>Micro Step                               |                  |      |       | 0.5  | dB      |                                                                                                       |

| Maximum Attenuation<br>Change when CS Goes<br>High                    |                  |      | 32    |      | dB      |                                                                                                       |

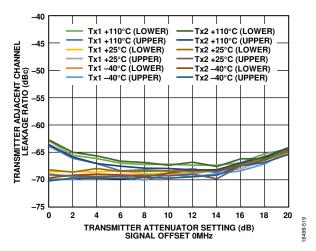

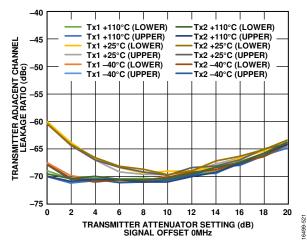

| Adjacent Channel Leakage<br>Ratio (ACLR) Long Term<br>Evolution (LTE) |                  |      |       |      |         | 20 MHz LTE at –12 dBFS                                                                                |

|                                                                       |                  |      | -67   |      | dB      | 75 MHz < f $\leq$ 2800 MHz                                                                            |

|                                                                       |                  |      | -64   |      | dB      | 2800 MHz < f $\le$ 4800 MHz                                                                           |

|                                                                       |                  |      | -60   |      | dB      | 4800 MHz < f $\le$ 6000 MHz                                                                           |

| Parameter                                                | Symbol | Min Typ | Max l | Jnit   | <b>Test Conditions/Comments</b>                                                                                                                                                                                              |

|----------------------------------------------------------|--------|---------|-------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

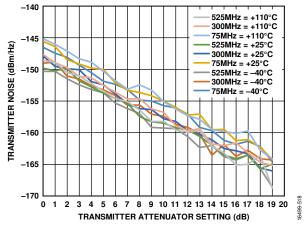

| In Band Noise Floor                                      |        |         |       |        | 0 dB attenuation; in band noise falls<br>1 dB for each dB of attenuation for<br>attenuation between 0 dB and 20 dB                                                                                                           |

|                                                          |        | -148    | c     | dBm/Hz | 600 MHz < f $\le$ 3000 MHz                                                                                                                                                                                                   |

|                                                          |        | -149    | c     | dBm/Hz | $3000 \text{ MHz} < f \le 4800 \text{ MHz}$                                                                                                                                                                                  |

|                                                          |        | -150.5  | c     | dBm/Hz | 4800 MHz < f $\le$ 6000 MHz                                                                                                                                                                                                  |

| Out of Band Noise Floor                                  |        |         |       |        | 0 dB attenuation; $3 \times$ bandwidth/2 offset                                                                                                                                                                              |

|                                                          |        | -153    | c     | dBm/Hz | 600 MHz < f $\le$ 3000 MHz                                                                                                                                                                                                   |

|                                                          |        | -154    | c     | dBm/Hz | 3000 MHz < f ≤ 4800 MHz                                                                                                                                                                                                      |

|                                                          |        | -155.5  | c     | dBm/Hz | 4800 MHz < f $\le$ 6000 MHz                                                                                                                                                                                                  |

| Interpolation Images                                     |        | -80     | c     | dBc    |                                                                                                                                                                                                                              |

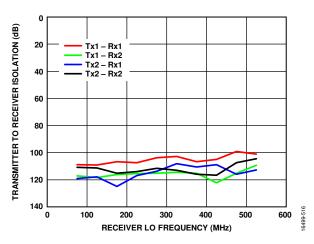

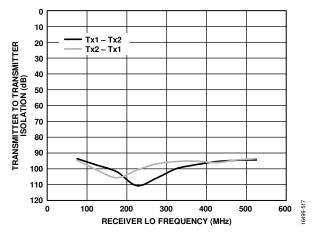

| Transmitter to Transmitter<br>Isolation                  |        | 85      | c     | dB     | 75 MHz < f $\leq$ 600 MHz                                                                                                                                                                                                    |

|                                                          |        | 75      | c     | dB     | $600 \text{ MHz} < f \le 2800 \text{ MHz}$                                                                                                                                                                                   |

|                                                          |        | 70      | c     | dB     | 2800 MHz < f $\le$ 4800 MHz                                                                                                                                                                                                  |

|                                                          |        | 65      | c     | dB     | 4800 MHz < f $\leq$ 5700 MHz                                                                                                                                                                                                 |

|                                                          |        | 56      | c     | dB     | 5700 MHz < f $\leq$ 6000 MHz                                                                                                                                                                                                 |

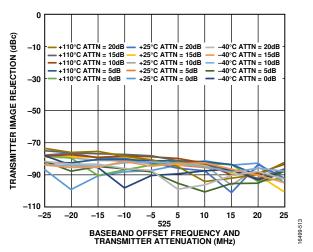

| Image Rejection<br>Within Large Signal<br>Bandwidth      |        |         |       |        | QEC active                                                                                                                                                                                                                   |

|                                                          |        | 70      | c     | dB     | 75 MHz < f $\leq$ 600 MHz                                                                                                                                                                                                    |

|                                                          |        | 65      | c     | dB     | 600 MHz < f $\le$ 4000 MHz                                                                                                                                                                                                   |

|                                                          |        | 62      | c     | dB     | 4000 MHz < f $\le$ 4800 MHz                                                                                                                                                                                                  |

|                                                          |        | 60      | c     | dB     | 4800 MHz < f $\le$ 6000 MHz                                                                                                                                                                                                  |

| Beyond Large Signal<br>Bandwidth                         |        | 40      | c     | dB     | Assumes that distortion power densit is 25 dB below desired power densit                                                                                                                                                     |

| Maximum Output Power                                     |        |         |       |        | 0 dBFS, continuous wave tone into 50 Ω load, 0 dB transmitter attenuatio                                                                                                                                                     |

|                                                          |        | 9       | c     | dBm    | 75 MHz < f $\leq$ 600 MHz                                                                                                                                                                                                    |

|                                                          |        | 7       | c     | dBm    | 600 MHz < f $\le$ 3000 MHz                                                                                                                                                                                                   |

|                                                          |        | 6       | c     | dBm    | 3000 MHz < f ≤ 4800 MHz                                                                                                                                                                                                      |

|                                                          |        | 4.5     | c     | dBm    | 4800 MHz < f $\le$ 6000 MHz                                                                                                                                                                                                  |

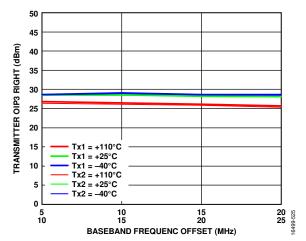

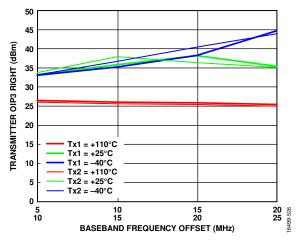

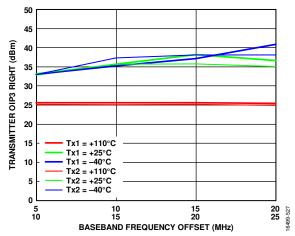

| Third Order Output<br>Intermodulation<br>Intercept Point | OIP3   |         |       |        | 0 dB transmitter attenuation                                                                                                                                                                                                 |

|                                                          |        | 29      | c     | dBm    | 75 MHz < f $\leq$ 600 MHz                                                                                                                                                                                                    |

|                                                          |        | 27      | c     | dBm    | $600 \text{ MHz} < f \le 4000 \text{ MHz}$                                                                                                                                                                                   |

|                                                          |        | 23      | c     | dBm    | 4000 MHz < f $\leq$ 6000 MHz                                                                                                                                                                                                 |

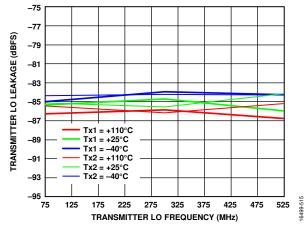

| Carrier Leakage                                          |        |         |       |        | With LO leakage correction active, 0 d<br>attenuation; scales decibel for decib<br>with attenuation; measured in 1 MH<br>bandwidth, resolution bandwidth<br>and video bandwidth = 100 kHz, rm<br>detector, 100 trace average |

| Carrier Offset from Local<br>Oscillator (LO)             |        | -84     | c     | dBFS   | 75 MHz < f ≤ 600 MHz                                                                                                                                                                                                         |

|                                                          |        | -82     | c     | dBFS   | $600 \text{ MHz} < f \le 4800 \text{ MHz}$                                                                                                                                                                                   |

|                                                          |        | -80     | c     | dBFS   | $4800 \text{ MHz} < f \le 6000 \text{ MHz}$                                                                                                                                                                                  |

| Carrier on LO                                            |        | -71     | c     | dBFS   |                                                                                                                                                                                                                              |

| Parameter                                                | Symbol            | Min | Тур   | Мах  | Unit    | <b>Test Conditions/Comments</b>                                                                                          |

|----------------------------------------------------------|-------------------|-----|-------|------|---------|--------------------------------------------------------------------------------------------------------------------------|

| Error Vector Magnitude                                   | EVM               |     |       |      |         |                                                                                                                          |

| (Third Generation                                        |                   |     |       |      |         |                                                                                                                          |

| Partnership Project                                      |                   |     |       |      |         |                                                                                                                          |

| (3GPP) Test Signals)                                     |                   |     |       |      |         |                                                                                                                          |

| 75MHz LO                                                 |                   |     | 0.5   |      | %       | 300 kHz RF PLL loop bandwidth                                                                                            |

| 1900 MHz LO                                              |                   |     | 0.7   |      | %       | 50 kHz RF PLL loop bandwidth                                                                                             |

| 3800 MHz LO                                              |                   |     | 0.7   |      | %       | 300 kHz RF PLL loop bandwidth                                                                                            |

| 5900 MHz LO                                              |                   |     | 1.1   |      | %       | 300 kHz RF PLL loop bandwidth                                                                                            |

| Output Impedance                                         | Z <sub>OUT</sub>  |     | 50    |      | Ω       | Differential (see Figure 428)                                                                                            |

| OBSERVATION RECEIVER                                     | ORx               |     |       |      |         |                                                                                                                          |

| Center Frequency                                         |                   | 75  |       | 6000 | MHz     |                                                                                                                          |

| Gain Range                                               |                   |     | 30    |      | dB      | IIP3 improves decibel for decibel for the                                                                                |

|                                                          |                   |     |       |      |         | first 18 dB of gain attenuation; QEC<br>performance optimized for 0 dB to<br>6 dB of attenuation only                    |

| Analog Gain Step                                         |                   |     | 0.5   |      | dB      | For attenuator steps from 0 dB to 6 dl                                                                                   |

| Peak to Peak Gain                                        |                   |     | 1     |      | dB      | 450 MHz bandwidth, compensated b                                                                                         |

| Deviation                                                |                   |     | I     |      | ub      | programmable FIR filter                                                                                                  |

| Gain Slope                                               |                   |     | ±0.1  |      | dB      | Any 20 MHz bandwidth span,                                                                                               |

|                                                          |                   |     |       |      |         | compensated by programmable FIR filter                                                                                   |

| Deviation from Linear Phase                              |                   |     | 1     |      | Degrees | 450 MHz RF bandwidth                                                                                                     |

| Receiver Bandwidth                                       |                   |     |       | 450  | MHz     |                                                                                                                          |

| Receiver Alias Band<br>Rejection                         |                   | 60  |       |      | dB      | Due to digital filters                                                                                                   |

| Maximum Useable Input                                    | P <sub>HIGH</sub> |     |       |      |         | 0 dB attenuation; increases decibel                                                                                      |

| Level                                                    |                   |     |       |      |         | for decibel with attenuation;<br>continuous wave corresponds to<br>–1 dBFS at ADC                                        |

|                                                          |                   |     | -11   |      | dBm     | 75 MHz < f ≤ 3000 MHz                                                                                                    |

|                                                          |                   |     | -9.5  |      | dBm     | $3000 \text{ MHz} < f \le 4800 \text{ MHz}$                                                                              |

|                                                          |                   |     | -8    |      | dBm     | $4800 \text{ MHz} < f \le 6000 \text{ MHz}$                                                                              |

| Integrated Noise                                         |                   |     | -58.5 |      | dBFS    | 450 MHz integration bandwidth                                                                                            |

| Integrated Noise                                         |                   |     | -57.5 |      | dBFS    | 2                                                                                                                        |

|                                                          | IIP2              |     |       |      |         | 491.52 MHz integration bandwidth                                                                                         |

| Second-Order Input<br>Intermodulation<br>Intercept Point | IIP2              |     | 62    |      | dBm     | Maximum observation receiver gain;<br>$P_{HIGH} - 14  dB per tone (see the Terminology section) 75 MHz < f \leq600 MHz$  |

|                                                          |                   |     | 62    |      | dBm     | Maximum observation receiver gain;<br>$P_{HIGH} - 8  dB per tone (see the Terminology section) 600 MHz < f \leq3000 MHz$ |

| Third-Order Input<br>Intermodulation                     | IIP3              |     |       |      |         |                                                                                                                          |

| Intercept Point<br>Narrow Band                           |                   |     | 4     |      | dBm     | 75 MHz < f ≤ 300 MHz; (P <sub>HIGH</sub> – 14)<br>dB/tone                                                                |

|                                                          |                   |     | 11    |      | dBm     | $300 \text{ MHz} < f \le 600 \text{ MHz}; (P_{HGH} - 14) dB/tone$                                                        |

|                                                          |                   |     |       |      |         | IM3 product < 130 MHz at baseband,<br>(P <sub>HIGH</sub> – 8) dB/tone                                                    |

|                                                          |                   |     | 12    |      | dBm     | $600 \text{ MHz} < f \le 3000 \text{ MHz}$                                                                               |

|                                                          |                   |     | 12    |      | dBm     | 3000 MHz < f ≤ 4800 MHz                                                                                                  |

|                                                          |                   |     | 11    |      | dBm     | $4800 \text{ MHz} < f \le 6000 \text{ MHz}$                                                                              |

| Wide Band<br>Third-Order Intermodulation<br>Product    | IM3               |    | 7<br>7        |      | dBm | 600 MHz < f ≤ 3000 MHz                                                                                                               |

|--------------------------------------------------------|-------------------|----|---------------|------|-----|--------------------------------------------------------------------------------------------------------------------------------------|

|                                                        | IM3               |    |               |      | dBm | 600 MHz < f ≤ 3000 MHz                                                                                                               |

|                                                        | IM3               |    | 7             |      |     | 1                                                                                                                                    |

|                                                        | IM3               |    |               |      | dBm | $3000 \text{ MHz} < f \le 4800 \text{ MHz}$                                                                                          |

|                                                        | IM3               |    | 6             |      | dBm | $4800 \text{ MHz} < f \le 6000 \text{ MHz}$                                                                                          |

|                                                        |                   |    |               |      |     | IM3 product < 130 MHz at baseband;<br>two tones, each at $(P_{HIGH} - 12) dB$                                                        |

|                                                        |                   |    | -70           |      | dBc | 600 MHz < f ≤ 3000 MHz                                                                                                               |

|                                                        |                   |    | -67           |      | dBc | $3000 \text{ MHz} < f \le 4800 \text{ MHz}$                                                                                          |

|                                                        |                   |    | -62           |      | dBc | 4800 MHz < f ≤ 6000 MHz                                                                                                              |

| Fifth-Order Intermodulation<br>Product (1800 MHz)      | IM5               |    | -80           |      | dBc | IM5 product < 50 MHz at baseband;<br>two tones, each at (P <sub>HIGH</sub> – 14) dB                                                  |

| Seventh-Order<br>Intermodulation Product<br>(1800 MHz) | IM7               |    | -80           |      | dBc | IM7 product < 50 MHz at baseband;<br>two tones, each at (P <sub>HIGH</sub> – 14) dB                                                  |

| Spurious-Free Dynamic<br>Range                         | SFDR              |    | 70            |      | dB  | Non IMx related spurs, does not include<br>HDx; (P <sub>HGH</sub> – 11) dB input signal                                              |

| Harmonic Distortion                                    |                   |    |               |      |     | (P <sub>HIGH</sub> – 11) dB input signal                                                                                             |

| Second Order Harmonic<br>Distortion Product            | HD2               |    | -80           |      | dBc | In band HD falls within $\pm 25$ MHz                                                                                                 |

|                                                        |                   |    | -80           |      | dBc | Out of band HD falls within $\pm 50$ MHz                                                                                             |

| Third-Order Harmonic<br>Distortion Product             | HD3               |    | -70           |      | dBc | In band HD falls within $\pm 25$ MHz                                                                                                 |

| Image Rejection                                        |                   |    | -60           |      | dBc | Out of band HD falls within ±50 MHz<br>QEC active                                                                                    |

| Within Large Signal<br>Bandwidth                       |                   |    | 65            |      | dB  |                                                                                                                                      |

| Outside Large Signal<br>Bandwidth                      |                   |    | 55            |      | dB  |                                                                                                                                      |

| Input Impedance<br>Isolation                           |                   |    | 100           |      | Ω   | Differential (see Figure 429)                                                                                                        |

|                                                        |                   |    | 65            |      | dB  | 600 MHz < f ≤5300 MHz                                                                                                                |

|                                                        |                   |    | 55            |      | dB  | 5300 MHz < f ≤ 6000 MHz                                                                                                              |

|                                                        |                   |    | 65            |      | dB  | 600 MHz < f ≤ 5300 MHz                                                                                                               |

|                                                        |                   |    | 55            |      | dB  | 5300 MHz < $f \le 6000$ MHz                                                                                                          |

| RECEIVERS                                              |                   |    |               |      |     |                                                                                                                                      |

| Center Frequency                                       |                   | 75 |               | 6000 | MHz |                                                                                                                                      |

| Gain Range                                             |                   |    | 30            |      | dB  |                                                                                                                                      |

| Analog Gain Step                                       |                   |    | 0.5           |      | dB  | Attenuator steps from 0 dB to 6 dB                                                                                                   |

|                                                        |                   |    | 1             |      | dB  | Attenuator steps from 6 dB to 30 dB                                                                                                  |

| Bandwidth Ripple                                       |                   |    | ±0.5          |      | dB  | 200 MHz bandwidth, compensated by programmable FIR filter                                                                            |

|                                                        |                   |    | ±0.2          |      | dB  | Any 20 MHz bandwidth span,<br>compensated by programmable FIR<br>filter                                                              |

| Receiver Bandwidth                                     |                   |    |               | 200  | MHz |                                                                                                                                      |

| Receiver Alias Band<br>Rejection                       |                   | 80 |               |      | dB  | Due to digital filters                                                                                                               |

| Maximum Useable Input<br>Level                         | P <sub>HIGH</sub> |    |               |      |     | 0 dB attenuation, increases decibel<br>for decibel with attenuation;<br>continuous wave = 1800 MHz;<br>corresponds to -1 dBFS at ADC |

|                                                        |                   |    | -11           |      | dBm | $75 \text{ MHz} < f \le 3000 \text{ MHz}$                                                                                            |

|                                                        |                   |    | -11           |      | dBm | $3000 \text{ MHz} < f \le 4800 \text{ MHz}$                                                                                          |

|                                                        |                   |    | -10.2<br>-9.5 |      | dBm | $4800 \text{ MHz} < f \le 6000 \text{ MHz}$                                                                                          |

| Parameter                                                        | Symbol  | Min | Тур  | Мах | Unit | <b>Test Conditions/Comments</b>                                                   |

|------------------------------------------------------------------|---------|-----|------|-----|------|-----------------------------------------------------------------------------------|

| Noise Figure                                                     | NF      |     |      |     |      | 0 dB attenuation, at receiver port                                                |

|                                                                  |         |     | 12   |     | dB   | $600 \text{ MHz} < f \le 3000 \text{ MHz}$                                        |

|                                                                  |         |     | 13   |     | dB   | 3000 MHz < f ≤ 4800 MHz                                                           |

|                                                                  |         |     | 15.2 |     | dB   | 4800 MHz < f ≤ 6000 MHz                                                           |

| Ripple                                                           |         |     | 1.8  |     | dB   | At band edge maximum bandwidth mode                                               |

| Input Third-Order Intercept<br>Point                             | IIP3    |     |      |     |      |                                                                                   |

| Difference Product                                               | IIP3, d |     | 12   |     | dBm  | Two (P <sub>HIGH</sub> – 12) dB tones near band<br>edge                           |

| Sum Product                                                      | IIP3, s |     | 12   |     | dBm  | Two ( $P_{HIGH} - 6$ ) dB tones, at bandwidth, offset from the LO                 |

| HD3                                                              | HD3     |     |      |     |      | (P <sub>HIGH</sub> – 6) dB continuous wave tone<br>bandwidth/6 offset from the LO |

|                                                                  |         |     | -66  |     | dBc  | $600 \text{ MHz} < f \le 4800 \text{ MHz}$                                        |

|                                                                  |         |     | -62  |     | dBc  | $4800 \text{ MHz} < f \le 6000 \text{ MHz}$                                       |

| Second-Order Input<br>Intermodulation<br>Intercept Point         | IIP2    |     | 62   |     | dBm  | 0 dB attenuation, complex                                                         |

| Image Rejection                                                  |         |     | 75   |     | dB   | Quadrature error correction (QEC)<br>active, within 200 MHz receiver<br>bandwidth |

| Input Impedance                                                  |         |     | 100  |     | Ω    | Differential (see Figure 430)                                                     |

|                                                                  |         |     | 65   |     | dB   | $600 \text{ MHz} < f \le 4800 \text{ MHz}$                                        |

|                                                                  |         |     | 61   |     | dB   | $4800 \text{ MHz} < f \le 6000 \text{ MHz}$                                       |

| Receiver Band Spurs<br>Referenced to RF Input<br>at Maximum Gain |         |     | -95  |     | dBm  | No more than one spur at this level per 10 MHz of receiver bandwidth              |

| Receiver LO Leakage at<br>Receiver Input at<br>Maximum Gain      |         |     |      |     |      | Leakage decreases decibel for decib<br>with attenuation for first 12 dB           |

|                                                                  |         |     | -70  |     | dBm  | 600 MHz < f ≤ 3000 MHz                                                            |

|                                                                  |         |     | -65  |     | dBm  | $3000 \text{ MHz} < f \le 6000 \text{ MHz}$                                       |

| Isolation                                                        |         |     |      |     |      |                                                                                   |

|                                                                  |         |     | 65   |     | dB   | $600 \text{ MHz} < f \le 4800 \text{ MHz}$                                        |

|                                                                  |         |     | 55   |     | dB   | 4800 MHz < f $\leq$ 6000 MHz                                                      |

|                                                                  |         |     | 65   |     | dB   | $600 \text{ MHz} < f \le 4800 \text{ MHz}$                                        |

|                                                                  |         |     | 55   |     | dB   | $4800 \text{ MHz} < f \le 6000 \text{ MHz}$                                       |

| O SYNTHESIZER                                                    |         |     |      |     |      |                                                                                   |

| LO Frequency Step                                                |         |     | 2.3  |     | Hz   | 1.5 GHz to 2.8 GHz, 76.8 MHz phase<br>frequency detector (PFD) frequency          |

| LO Spur                                                          |         |     | -85  |     | dBc  | Excludes integer boundary spurs                                                   |

| Integrated Phase Noise                                           |         |     |      |     |      | 2 kHz to 18 MHz                                                                   |

| 1900 MHz LO                                                      |         |     | 0.2  |     | °rms | Narrow PLL loop bandwidth (50 kHz                                                 |

| 3800 MHz LO                                                      |         |     | 0.36 |     | °rms | Wide PLL loop bandwidth (300 kHz)                                                 |

| 5900 MHz LO                                                      |         |     | 0.54 |     | °rms | Wide PLL loop bandwidth (300 kHz)                                                 |

| Parameter                                | Symbol             | Min | Тур    | Max  | Unit        | Test Conditions/Comments                                                                                             |

|------------------------------------------|--------------------|-----|--------|------|-------------|----------------------------------------------------------------------------------------------------------------------|

| Spot Phase Noise                         |                    |     |        |      |             |                                                                                                                      |

| 1900 MHz LO                              |                    |     |        |      |             | Narrow PLL loop bandwidth                                                                                            |

| 100 kHz Offset                           |                    |     | -100   |      | dBc/Hz      |                                                                                                                      |

| 200 kHz Offset                           |                    |     | -115   |      | dBc/Hz      |                                                                                                                      |

| 400 kHz Offset                           |                    |     | -120   |      | dBc/Hz      |                                                                                                                      |

| 600 kHz Offset                           |                    |     | -129   |      | dBc/Hz      |                                                                                                                      |

| 800 kHz Offset                           |                    |     | -132   |      | dBc/Hz      |                                                                                                                      |

| 1.2 MHz Offset                           |                    |     | -135   |      | dBc/Hz      |                                                                                                                      |

| 1.8 MHz Offset                           |                    |     | -140   |      | dBc/Hz      |                                                                                                                      |

| 6 MHz Offset                             |                    |     | -150   |      | dBc/Hz      |                                                                                                                      |

| 10 MHz Offset                            |                    |     | -153   |      | dBc/Hz      |                                                                                                                      |

| 3800 MHz LO                              |                    |     | -155   |      | GDC/112     | Wide PLL loop bandwidth                                                                                              |

| 100 kHz Offset                           |                    |     | -104   |      | dBc/Hz      | wide i Le loop bandwidth                                                                                             |

| 1.2 MHz Offset                           |                    |     | -125   |      | dBc/Hz      |                                                                                                                      |

| 10 MHz Offset                            |                    |     | -125   |      | dBc/Hz      |                                                                                                                      |

|                                          |                    |     | -145   |      |             | Wide DLL lean handwidth                                                                                              |

| 5900 MHz LO<br>100 kHz Offset            |                    |     | 00     |      | -ID - // I- | Wide PLL loop bandwidth                                                                                              |

|                                          |                    |     | -99    |      | dBc/Hz      |                                                                                                                      |

| 1.2 MHz Offset                           |                    |     | -119.7 |      | dBc/Hz      |                                                                                                                      |

| 10 MHz Offset                            |                    |     | -135.4 |      | dBc/Hz      |                                                                                                                      |

| LO PHASE SYNCHRONIZATION                 |                    |     |        |      |             |                                                                                                                      |

| Phase Deviation                          |                    |     | 1.6    |      | ps/°C       | Change in LO delay per temperature change                                                                            |

| EXTERNAL LO INPUT                        |                    |     |        |      |             |                                                                                                                      |

| Input Frequency                          | f <sub>extlo</sub> | 150 |        | 8000 | MHz         | Input frequency must be 2× the desired LO frequency                                                                  |

| Input Signal Power                       |                    | 0   |        | 12   | dBm         | 50 $\Omega$ matching at the source                                                                                   |

|                                          |                    |     | 3      |      | dBm         | $f_{EXTLO} \le 2 \text{ GHz}; \text{ add } 0.5 \text{ dBm/GHz}$<br>above 2 GHz                                       |

|                                          |                    |     | 6      |      | dBm         | $f_{EXTLO} = 8 GHz$                                                                                                  |

| External LO Input Signal<br>Differential |                    |     |        |      |             | To ensure adequate QEC                                                                                               |

| Phase Error                              |                    |     |        | 3.6  | ps          |                                                                                                                      |

| Amplitude Error                          |                    |     |        | 1    | dB          |                                                                                                                      |

| Duty Cycle Error                         |                    |     |        | 2    | %           |                                                                                                                      |

| Even-Order Harmonics                     |                    |     |        | -50  | dBc         |                                                                                                                      |

| CLOCK SYNTHESIZER                        |                    |     |        |      |             |                                                                                                                      |

| Integrated Phase Noise                   |                    |     |        |      |             | 1 kHz to 100 MHz                                                                                                     |

| 1966.08 MHz LO                           |                    |     | 0.4    |      | °rms        | PLL optimized for close in phase noise                                                                               |

| Spot Phase Noise                         |                    |     |        |      |             | ·                                                                                                                    |

| 1966.08 MHz                              |                    |     |        |      |             |                                                                                                                      |

| 100 kHz Offset                           |                    |     | -109   |      | dBc/Hz      |                                                                                                                      |

| 1 MHz Offset                             |                    |     | -129   |      | dBc/Hz      |                                                                                                                      |

| 10 MHz Offset                            |                    |     | -149   |      | dBc/Hz      |                                                                                                                      |

| REFERENCE CLOCK                          |                    |     |        |      |             |                                                                                                                      |

| (REF_CLK_IN)                             |                    | 10  |        | 1000 |             |                                                                                                                      |

| Frequency Range                          |                    | 10  |        | 1000 | MHz         |                                                                                                                      |

| Signal Level                             |                    | 0.3 |        | 2.0  | V р-р       | AC-coupled, common-mode voltage<br>( $V_{CM}$ ) = 618 mV; for best spurious<br>performance, use <1 V p-p input clock |

| Parameter                                                                          | Symbol | Min                        | Тур               | Max                        | Unit        | Test Conditions/Comments    |

|------------------------------------------------------------------------------------|--------|----------------------------|-------------------|----------------------------|-------------|-----------------------------|

| AUXILIARY CONVERTERS                                                               |        |                            |                   |                            |             |                             |

| ADC                                                                                |        |                            |                   |                            |             |                             |

| Resolution                                                                         |        |                            | 12                |                            | Bits        |                             |

| Input Voltage                                                                      |        |                            |                   |                            |             |                             |

| Minimum                                                                            |        |                            | 0.05              |                            | V           |                             |

| Maximum                                                                            |        |                            | VDDA_3P3 –        |                            | V           |                             |

|                                                                                    |        |                            | 0.05              |                            |             |                             |

| DAC                                                                                |        |                            | 10                |                            | <b>D</b> 11 |                             |

| Resolution                                                                         |        |                            | 10                |                            | Bits        | Includes four offset levels |

| Output Voltage                                                                     |        |                            | 0.7               |                            |             | 1.1.1.1                     |

| Minimum                                                                            |        |                            | 0.7               |                            | V           | 1 V V <sub>REF</sub>        |

| Maximum                                                                            |        |                            | VDDA_3P3 –<br>0.3 |                            | V           | 2.5 V V <sub>REF</sub>      |

| Output Drive Capability                                                            |        |                            | 10                |                            | mA          |                             |

| DIGITAL SPECIFICATIONS                                                             |        |                            |                   |                            |             |                             |

| (CMOS)—SERIAL<br>PERIPHERAL INTERFACE<br>(SPI), GPIO_x, TXx_ENABLE,<br>ORXx_ENABLE |        |                            |                   |                            |             |                             |

| Logic Inputs                                                                       |        |                            |                   |                            |             |                             |

| Input Voltage                                                                      |        |                            |                   |                            |             |                             |

| High Level                                                                         |        | VDD_<br>INTERFACE ×<br>0.8 |                   | VDD_<br>INTERFACE          | V           |                             |

| Low Level                                                                          |        | 0                          |                   | VDD_<br>INTERFACE<br>× 0.2 | V           |                             |

| Input Current                                                                      |        |                            |                   |                            |             |                             |

| High Level                                                                         |        | -10                        |                   | +10                        | μA          |                             |

| Low Level                                                                          |        | -10                        |                   | +10                        | μA          |                             |

| Logic Outputs                                                                      |        |                            |                   |                            |             |                             |

| Output Voltage                                                                     |        |                            |                   |                            |             |                             |

| High Level                                                                         |        | VDD_<br>INTERFACE ×<br>0.8 |                   |                            | V           |                             |

| Low Level                                                                          |        |                            |                   | VDD_<br>INTERFACE<br>× 0.2 | V           |                             |

| Drive Capability                                                                   |        |                            | 3                 |                            | mA          |                             |

| DIGITAL SPECFICATIONS                                                              |        |                            |                   |                            |             |                             |

| (CMOS)—GPIO_3P3_x                                                                  |        |                            |                   |                            |             |                             |

| Logic Inputs                                                                       |        |                            |                   |                            |             |                             |

| Input Voltage                                                                      |        |                            |                   |                            |             |                             |

| High Level                                                                         |        | VDDA_3P3 ×<br>0.8          |                   | VDDA_3P3                   | V           |                             |

| Low Level                                                                          |        | 0.8                        |                   | VDDA_<br>3P3 × 0.2         | v           |                             |

| Input Current                                                                      |        |                            |                   | JI J A U.Z                 |             |                             |

| High Level                                                                         |        | -10                        |                   | +10                        | μΑ          |                             |

| Low Level                                                                          |        | -10                        |                   | +10                        | μA          |                             |

| Parameter                                                           | Symbol           | Min                | Тур  | Max                | Unit | <b>Test Conditions/Comments</b>     |

|---------------------------------------------------------------------|------------------|--------------------|------|--------------------|------|-------------------------------------|

| Logic Outputs                                                       |                  |                    |      |                    |      |                                     |

| Output Voltage                                                      |                  |                    |      |                    |      |                                     |

| High Level                                                          |                  | VDDA_<br>3P3 × 0.8 |      |                    | V    |                                     |

| Low Level                                                           |                  |                    |      | VDDA_<br>3P3 × 0.2 | V    |                                     |

| Drive Capability                                                    |                  |                    | 4    |                    | mA   |                                     |

| DIGITAL SPECIFICATIONS<br>(LVDS)                                    |                  |                    |      |                    |      |                                     |

| Logic Inputs (SYSREF_IN±,<br>SYNCINx±)                              |                  |                    |      |                    |      |                                     |

| Input Voltage Range                                                 |                  | 825                |      | 1675               | mV   | Each differential input in the pair |

| Input Differential                                                  |                  | -100               |      | +100               | mV   |                                     |

| Voltage Threshold                                                   |                  |                    |      |                    |      |                                     |

| Receiver Differential<br>Input Impedance                            |                  |                    | 100  |                    | Ω    | Internal termination enabled        |

| Logic Outputs ( <u>SYNCOUTx±</u> )                                  |                  |                    |      |                    |      |                                     |

| Output Voltage                                                      |                  |                    |      |                    |      |                                     |

| High                                                                |                  |                    |      | 1375               | mV   |                                     |

| Low                                                                 |                  | 1025               |      |                    | mV   |                                     |

| Output Differential                                                 |                  |                    | 225  |                    | mV   | Programmable in 75 mV steps         |

| Voltage                                                             |                  |                    | 225  |                    | 111V |                                     |

| Output Offset Voltage                                               |                  |                    | 1200 |                    | mV   |                                     |

| SPITIMING                                                           |                  |                    | .200 |                    |      |                                     |

| SCLK Period                                                         | t <sub>CP</sub>  | 20                 |      |                    | ns   |                                     |

| SCLK Pulse Width                                                    |                  | 10                 |      |                    | ns   |                                     |

|                                                                     | t <sub>MP</sub>  |                    |      |                    |      |                                     |

| CS Setup to First SCLK<br>Rising Edge                               | t <sub>sc</sub>  | 3                  |      |                    | ns   |                                     |

| Last SCLK Falling Edge to                                           | t <sub>HC</sub>  | 0                  |      |                    | ns   |                                     |

| SDIO Data Input Setup to<br>SCLK                                    | ts               | 2                  |      |                    | ns   |                                     |

| SDIO Data Input Hold to<br>SCLK                                     | t <sub>H</sub>   | 0                  |      |                    | ns   |                                     |

| SCLK Rising Edge to<br>Output Data Delay<br>(3-Wire or 4-Wire Mode) | t <sub>co</sub>  | 3                  |      | 8                  | ns   |                                     |

| Bus Turnaround Time, Read<br>After BBP Drives Last<br>Address Bit   | t <sub>HZM</sub> | t <sub>H</sub>     |      | t <sub>co</sub>    | ns   |                                     |

| Bus Turnaround Time, Read<br>After ADRV9009 Drives<br>Last Data Bit | t <sub>HZS</sub> | 0                  |      | t <sub>co</sub>    | ns   |                                     |

| JESD204B DATA OUTPUT<br>TIMING                                      |                  |                    |      |                    |      | AC-coupled                          |

| Unit Interval                                                       | UI               | 81.38              |      | 320                | ps   |                                     |

| Data Rate per Channel,<br>Nonreturn to Zero (NRZ)                   |                  | 3125               |      | 12288              | Mbps |                                     |

| Rise Time                                                           | t <sub>R</sub>   | 24                 | 39.5 |                    | ps   | 20% to 80% in 100 Ω load            |

| Fall Time                                                           | t <sub>F</sub>   | 24                 | 39.4 |                    | ps   | 20% to 80% in 100 Ω load            |

| Output Common-Mode<br>Voltage                                       | V <sub>CM</sub>  | 0                  |      | 1.8                | V    | AC-coupled                          |

| Parameter                                       | Symbol                                | Min   | Тур    | Max   | Unit            | Test Conditions/Comments                                                                                                                                                                                                                                        |

|-------------------------------------------------|---------------------------------------|-------|--------|-------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|