# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# AN-905 Application Note

One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

### VisualAnalog<sup>™</sup> Converter Evaluation Tool Version 1.0 User Manual

#### INTRODUCTION

VisualAnalog is a new way to test and characterize data converters, ADCs, and DACs alike. Whereas tools have been available in the past, they could perform a limited set of tests. Whereas these tools did provide many features, their flexibility was limited to just a few simple options. VisualAnalog provides the ability to customize the tests in a nearly limitless manner using a simple graphical user interface.

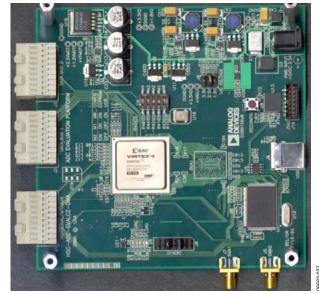

VisualAnalog interfaces seamlessly with the DAC pattern generator (DPG) for DAC evaluation and the following ADC data capture boards for ADC evaluation:

- HSC-ADC-EVALA

- HSC-ADC-EVALB

- HSC-ADC-EVALC

### **PRODUCT HIGHLIGHTS**

- 1. Quick set up of both ADC and DAC characterization

- 2. Easy testing of ADCs with reference DACs and DACs with reference ADCs

- 3. Easy configuration of custom signal flow tests for ADCs and DACs

- 4. Easy testing of converter models and comparison to real converter devices

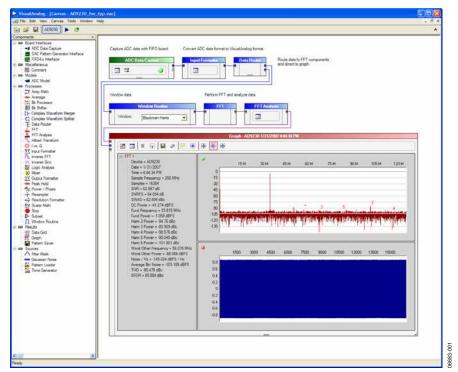

Figure 1. Typical VisualAnalog Canvas

# TABLE OF CONTENTS

| Introduction 1                                                                                                                                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Product Highlights 1                                                                                                                                                                                                                                                                                     |

| Installation of VisualAnalog                                                                                                                                                                                                                                                                             |

| Instruction Notes                                                                                                                                                                                                                                                                                        |

| Quick Start for ADC Evaluation 4                                                                                                                                                                                                                                                                         |

| VisualAnalog Software                                                                                                                                                                                                                                                                                    |

| Starting VisualAnalog6                                                                                                                                                                                                                                                                                   |

| Using the Start-Up Form 6                                                                                                                                                                                                                                                                                |

| Opening a Blank Canvas7                                                                                                                                                                                                                                                                                  |

| Using the Main Form7                                                                                                                                                                                                                                                                                     |

| Setting Canvas Properties9                                                                                                                                                                                                                                                                               |

| Placing Components                                                                                                                                                                                                                                                                                       |

| Connecting Components10                                                                                                                                                                                                                                                                                  |

| Adjusting Component Parameters12                                                                                                                                                                                                                                                                         |

| Updating Results                                                                                                                                                                                                                                                                                         |

| Making Layout Changes14                                                                                                                                                                                                                                                                                  |

| Using the Menu Bar14                                                                                                                                                                                                                                                                                     |

| Using the Tool Bar15                                                                                                                                                                                                                                                                                     |

| Using the Options Form16                                                                                                                                                                                                                                                                                 |

| Data Types Overview                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                          |

| Real Waveform Data                                                                                                                                                                                                                                                                                       |

| Real Waveform Data                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                          |

| Complex Waveform Data17                                                                                                                                                                                                                                                                                  |

| Complex Waveform Data                                                                                                                                                                                                                                                                                    |

| Complex Waveform Data                                                                                                                                                                                                                                                                                    |

| Complex Waveform Data                                                                                                                                                                                                                                                                                    |

| Complex Waveform Data17Real FFT Data17Complex FFT Data17Analysis Data17Value Collection17                                                                                                                                                                                                                |

| Complex Waveform Data17Real FFT Data17Complex FFT Data17Analysis Data17Value Collection17Numeric Value17                                                                                                                                                                                                 |

| Complex Waveform Data17Real FFT Data17Complex FFT Data17Analysis Data17Value Collection17Numeric Value17Tone List17                                                                                                                                                                                      |

| Complex Waveform Data17Real FFT Data17Complex FFT Data17Analysis Data17Value Collection17Numeric Value17Tone List17Components Overview18                                                                                                                                                                 |

| Complex Waveform Data17Real FFT Data17Complex FFT Data17Analysis Data17Value Collection17Numeric Value17Tone List17Components Overview18Board Interfaces18                                                                                                                                               |

| Complex Waveform Data17Real FFT Data17Complex FFT Data17Analysis Data17Value Collection17Numeric Value17Tone List17Components Overview18Board Interfaces18ADC Data Capture19                                                                                                                             |

| Complex Waveform Data17Real FFT Data17Complex FFT Data17Analysis Data17Value Collection17Numeric Value17Tone List17Components Overview18Board Interfaces18ADC Data Capture19DAC Pattern Generator Interface20                                                                                            |

| Complex Waveform Data17Real FFT Data17Complex FFT Data17Analysis Data17Value Collection17Numeric Value17Tone List17Components Overview18Board Interfaces18ADC Data Capture19DAC Pattern Generator Interface20DAC Pattern Generator Control Form20                                                        |

| Complex Waveform Data17Real FFT Data17Complex FFT Data17Analysis Data17Value Collection17Numeric Value17Tone List17Components Overview18Board Interfaces18ADC Data Capture19DAC Pattern Generator Interface20Pattern Limitations21                                                                       |

| Complex Waveform Data17Real FFT Data17Complex FFT Data17Analysis Data17Value Collection17Numeric Value17Tone List17Components Overview18Board Interfaces18ADC Data Capture19DAC Pattern Generator Interface20PAttern Generator Control Form20Pattern Limitations21FIFO4.x Interface21                    |

| Complex Waveform Data17Real FFT Data17Complex FFT Data17Analysis Data17Value Collection17Numeric Value17Tone List17Components Overview18Board Interfaces18ADC Data Capture19DAC Pattern Generator Interface20PAttern Generator Control Form20Pattern Limitations21FIFO4.x Interface21Components Models23 |

| Complex Waveform Data17Real FFT Data17Complex FFT Data17Analysis Data17Value Collection17Numeric Value17Tone List17Components Overview18Board Interfaces18ADC Data Capture19DAC Pattern Generator Interface20DAC Pattern Generator Control Form20Pattern Limitations21FIFO4.x Interface23ADC Model23     |

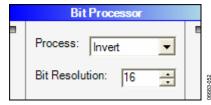

|    | Bit Processor                         | 24 |

|----|---------------------------------------|----|

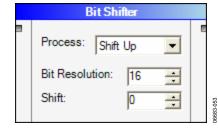

|    | Bit Shifter                           | 24 |

|    | Comment                               | 24 |

|    | Complex Waveform Merger               | 25 |

|    | Complex Waveform Splitter             | 25 |

|    | Data Router                           | 25 |

|    | FFT                                   | 25 |

|    | FFT Analysis                          | 25 |

|    | Hilbert Transform                     | 27 |

|    | Input Formatter                       | 27 |

|    | Inverse FFT                           | 27 |

|    | Inverse Sinc                          | 27 |

|    | I vs. Q                               | 27 |

|    | Logic Analysis                        | 27 |

|    | Mixer                                 | 28 |

|    | Output Formatter                      | 28 |

|    | Peak Hold                             | 28 |

|    | Power/Phase                           | 28 |

|    | Resampler                             | 29 |

|    | Resolution Formatter                  | 29 |

|    | Scalar Math                           | 29 |

|    | Stop                                  | 29 |

|    | Subset                                | 29 |

|    | Waveform Analysis                     | 29 |

|    | Window Routine                        | 29 |

| С  | omponents Results                     | 30 |

|    | Data Grid                             | 30 |

|    | Graph                                 | 30 |

|    | Pattern Saver                         | 32 |

| С  | omponents Sources                     | 33 |

|    | Filter Mask                           | 33 |

|    | Gaussian Noise                        | 33 |

|    | Pattern Loader                        | 33 |

|    | Tone Generator                        | 34 |

| Vi | sualAnalog Example Canvases           | 35 |

|    | ADC with ADC Data Capture Board       | 35 |

|    | ADIsimADC Model File                  |    |

|    | Loading the DPG with a Simple Vector  | 38 |

|    | Loading the DPG with a Complex Vector | 39 |

# **INSTALLATION OF VisualAnalog**

To install VisualAnalog, you must have the following:

- Administrator privileges

- Microsoft<sup>®</sup> .NET Framework Version 1.1

- The latest .NET Framework 1.1 service packs

The VisualAnalog installation package installs all of the items needed to use the VisualAnalog software along with the necessary drivers for the ADC and DAC hardware.

#### **INSTRUCTION NOTES**

- Disconnect all Analog Devices, Inc. ADC data capture boards and/or the DPG from the computer before installing the software. Be sure to finish the installation of the software before attempting to connect any related hardware to ensure the proper installation and registration of the device drivers.

- Note that you need administrator privileges when installing this software package and when connecting the ADC and DAC hardware to the computer for the first time. If using the Hardware Wizard, follow through the instructions to install the software automatically. This allows Windows\* to complete the driver installation process.

VisualAnalog is a Microsoft .NET application. You must have .NET Framework Version 1.1 on your machine to run VisualAnalog. The preferred way to obtain the .NET Framework is through Windows Update. Be sure to get the latest service packs available as well. To determine if the .NET Framework 1.1 is already installed on your computer, click **Start**, select **Control Panel**, and click **Add or Remove Programs**. When the window appears, scroll through the list of applications. If you see **Microsoft** .**NET Framework 1.1** listed, you have the correct version and you do not need to install it.

- 1. To ensure proper installation of all the components you must have administrator privileges.

- 2. Disconnect all ADC data capture boards and/or the DPG from the computer.

- 3. Install the .NET Framework 1.1 and the latest .NET Service Pack.

- 4. Run the VisualAnalog installation executable. Follow the on-screen instructions to install all of the necessary files. If interfacing with the DPG, be sure to launch the Hardware Wizard at the end of the installation process to set up the appropriate DPG device drivers.

- 5. Power up and connect the DPG and/or any ADC data capture board to the computer to finish the driver installation process. If using the DPG, be sure to connect the DPG before the ADC data capture board. If not using the DPG, you can plug in the ADC data capture board at any time after you install the software.

# QUICK START FOR ADC EVALUATION

With VisualAnalog, it is easy to bypass the canvas interface and begin ADC evaluation immediately. To begin interfacing to a particular ADC right away, use the following steps:

- 1. Connect and power the evaluation board, ADC data capture board, and any other required board used for data transfer. You can also supply the required clock and input signals to the ADC evaluation board.

- 2. Connect the ADC data capture board to the computer with a high speed USB cable. If a driver installation dialog appears, as happens when using the ADC data capture board for the first time, proceed through the dialog steps.

If the Hardware Wizard appears (see Figure 2), follow the instructions to install the software automatically. This allows Windows to complete the driver installation process.

Figure 2. Hardware Wizard

- 3. Start VisualAnalog. For more information, see the VISUALANALOG Software section.

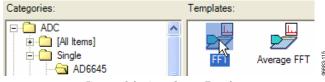

- 4. The start-up form now appears. If an ADC was connected using the preceding steps, VisualAnalog attempts to detect it and selects the canvas template that supports the ADC on the start-up form. Note that the ADC must support SPI\* functionality for the program to autodetect. If the ADC does not support SPI, or if the program does not detect the ADC for any reason, manually select the template. See the Using the Start-Up Form section for more information.

Figure 3. New Canvas Form

- 5. Select the FFT icon and click Open.

- 6. If you have an HSC-ADC-EVALC data capture board, a dialog box that asks for permission to configure the on-board FPGA may appear. If you prefer to use the current FPGA configuration, click No to bypass configuration. Otherwise, click Yes to configure the FPGA. See the Using the Start-Up Form section for more information.

| Visual/      | Analog                                                                                                                                                                                                                                   |           |  |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--|--|--|

| <b>(i)</b>   | VisualAnalog will now attempt to program the on-board FPGA with a default file for the AD9211.                                                                                                                                           |           |  |  |  |

| $\checkmark$ | Please click Yes to program the FPGA. If you prefer to use the current FPGA configuration, click No.                                                                                                                                     |           |  |  |  |

|              | Before clicking Yes, please make sure the HSC-ADC-EVALC is powered with the 5V supply and that<br>the board is connected to the computer. Also make sure the dipswitch U4 on the HSC-ADC-EVALC<br>is set to the following configuration: |           |  |  |  |

|              | M0 - ON<br>M1 - OFF<br>M2 - OFF                                                                                                                                                                                                          |           |  |  |  |

|              | If the configuration is successful, you will see the DONE light.                                                                                                                                                                         |           |  |  |  |

|              | Do not show this message again.                                                                                                                                                                                                          |           |  |  |  |

|              | Yes No                                                                                                                                                                                                                                   | 06683-006 |  |  |  |

Figure 4. FPGA Configuration Dialog

7. The main form appears in collapsed mode with your canvas open and selected. Click **Update** to run the canvas.

A **Graph** form should appear with the FFT results. If the graph does not appear, it is possible there was an error during processing. Check the board connection and try again. If this does not fix the problem, expand the main form and check the canvas settings. For more information, see the Using the Main Form and the Components Overview sections.

| AD1230   > C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                         |           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------|

| Graph - A09230 2/14/2007 1:39:5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | incom<br>An All         | E P       |

| Ele                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                         | 212       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | · ── ── ──              |           |

| FFT 1     Device = A09220     Device = A09220     Device = 314/2007     Time = 10326 FBW     Sample Treasure = 400 Mile     Sample Treasure = 400 Mile     Sample = 400 Mil | 15M 20M 45M 40M 75M 90M | 105M 120M |

| Hann S Prover - 102,004 dBc<br>Hann S Prover - 102,054 dBc<br>Wond Other Trequer - 02,054 dBc<br>Wond Other Trequer - 103,004 dBrS<br>Massey Draw Tower - 102,000 dBrS<br>Tritle - 72,026 dBc<br>STDR - 72,045 dBc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                         | -         |

Figure 6. Main Form and Graph Form

To view the time domain representation of the captured data, click **Toggle Additional Plot** on the graph form. See the Components Overview section for more information.

Figure 7. Toggle Additional Plot Button

# VisualAnalog SOFTWARE

| VisualAnalog - New Canvas |              |

|---------------------------|--------------|

| New Existing Recent       |              |

| Categories:               | Templates:   |

| ⊕- <mark>`</mark> ADC<br> | Blank Canvas |

|                           |              |

|                           | Open Cancel  |

Figure 8. VisualAnalog Start-Up Form

### STARTING VISUALANALOG

After installing the VisualAnalog software, a **Start** menu item and a desktop icon should appear. To use the **Start** menu item, click **Start**, select **Programs**, select **Analog Devices**, click **VisualAnalog**, and select **VisualAnalog**.

To use the desktop icon, click the **VisualAnalog** icon from the desktop.

When the program starts, a splash screen appears while loading is in process, and the **Start-Up Form** appears after the splash screen disappears.

### **USING THE START-UP FORM**

Select the **New** tab at any time to load a blank canvas or a predefined canvas template. VisualAnalog maintains a list of templates that set up the canvas for running a common task or interface with a particular device.

To select a canvas template, expand the **Categories** tree until the appropriate device is visible. Then, select an icon in the **Templates** list and click **Open**. VisualAnalog opens the canvas.

Figure 9. Selecting a Canvas Template

VisualAnalog can detect a connected ADC board if that ADC supports a programmable SPI interface. In addition, an ADC data capture board that supports SPI must be used. For this autodetect to work correctly, both boards must be connected to the computer via a USB cable and powered up before the software is started. Windows must also recognize the ADC data capture board to ensure correct operation. If Windows does not recognize the board, then there is a USB problem. Refer to the data sheet of the particular board for more information.

If VisualAnalog detects an ADC board, the software displays information in the status bar of the start-up form. In addition, it finds an item in the category tree that supports the ADC device.

Figure 10. Visual Analog—New Canvas Window

If the software does not detect the ADC board at this point, manually select the correct category and template.

When choosing a template that represents the detected ADC board, with an interface with to HSC-ADC-EVALC data capture board, a dialog box may appear that asks for permission to configure the on-board FPGA. If the HSC-ADC-EVALC FPGA did not configure on power-up for the particular ADC you are evaluating, click **Yes**. Click **No** to bypass the FPGA configuration.

If you check **Do not show this message again**, the software automatically performs the last selected action in the future, when choosing an applicable canvas template. If you want to change this option, access these settings from the **Options** menu in VisualAnalog.

Figure 11. FPGA Configuration Dialog

VisualAnalog maintains a list of FPGA files that correspond with a device ID that exists in the SPI register map of the ADC. When the software detects a particular device ID that exists in the table, it can choose a default FPGA configuration file. Note that this process only occurs when using the HSC-ADC-EVALC.

Select the Existing tab to browse for an existing canvas file.

VisualAnalog maintains a list of the last five recently accessed canvas files. To access this list and open one of these recent files, select the **Recent** tab.

Click **Open**, VisualAnalog opens the selected canvas file or canvas template.

Click **Cancel** and the main form appears with no open canvases.

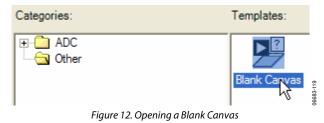

### **OPENING A BLANK CANVAS**

To open a blank canvas, navigate to **Other** in the category tree, and select the **Blank Canvas** template icon. Click **Open**.

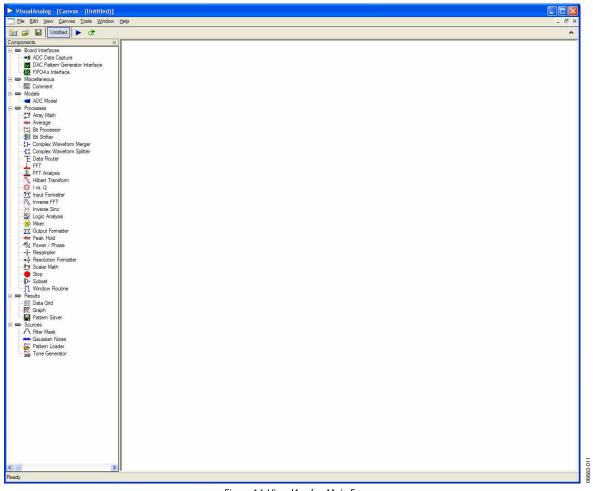

### USING THE MAIN FORM

The VisualAnalog main form maintains all currently open canvases in an MDI environment. The left side of the screen shows available **Components** (see Figure 14). This form docks to the left by default, but can be moved and docked to any of the corners of the VisualAnalog program. In addition, the **Components** form can be floated and moved anywhere on screen, even outside the VisualAnalog window.

#### **Canvas Buttons**

As you open or create canvases, buttons are created across the tool bar, each button represent a canvas. These are canvas buttons. You can use these canvas buttons to select or clear a canvas for updating. When the button appears highlighted, the canvas runs on the next update. You must select the canvas in order to run it.

The text that appears on the canvas button is the **Display Name** for the canvas. Change this property by selecting **Canvas** > **Properties**.

It is possible to collapse the main form (see Figure 13). This is useful when you want to conserve screen area and you do not need to adjust canvas settings. To collapse the main form, click the arrow on the right side of the main forms tool bar. To expand the form, simply click this button again.

Figure 13. Collapsing and Expanding the Display

Figure 14. VisualAnalog Main Form

3683-017

#### SETTING CANVAS PROPERTIES

VisualAnalog allows you to set properties that describe the canvas and the way it behaves. To access the canvas properties, click **Canvas** > (**Display Name**) **Properties...** if a blank canvas is opened, (**Display Name**) appears as **Untitled**.

| VisualAnalog - [Canvas - (Untitled)] |                 |           |              |               |   |

|--------------------------------------|-----------------|-----------|--------------|---------------|---|

| 🖂 File Edit View                     | Canvas          | Tools     | Window       | Help          |   |

| Components                           | Updat<br>Contir |           | F<br>odate C | 5<br>Ctrl +F5 | _ |

| Board Interface                      | Capture         | ed Prope  |              | ेब्           |   |

| Figure                               | 15. Canvas      | Propertie | s Menu       |               |   |

Use the **Canvas Properties** form to adjust the properties of a particular canvas.

| Canvas Properti | es       |                             | ×   |

|-----------------|----------|-----------------------------|-----|

| Display Name:   | Untitled | Collapse Window when Opened |     |

| Description:    |          |                             |     |

|                 |          |                             |     |

|                 |          |                             |     |

| 1               |          |                             |     |

|                 |          | OK Can                      | cel |

Figure 16. Canvas Properties Form

The **Display Name** refers to the name that appears on the canvas button. This is the title for the canvas.

Figure 17. Display Name

You can also enter a description of the canvas.

| Description:                                |           |

|---------------------------------------------|-----------|

| This canvas simulates a AD6645 105MSPS ADC. | 06683-016 |

| Figure 18. Description                      |           |

**Collapse Window when Opened** allows you to collapse the main window when this canvas is opened in the future. It permits opening the canvas in a more formal mode without showing the canvas itself.

**Lock Canvas** allows you to lock the canvas from further layout changes. You can still change component settings when this is set, but you cannot alter the physical layout and connectivity of your canvas.

#### PLACING COMPONENTS

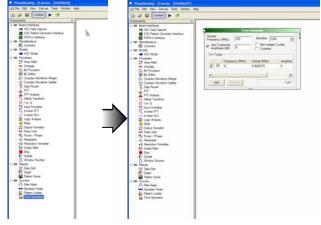

To place a component on the canvas, either double click the item in the **Components** tree or drag the item and drop it on the canvas. Dragging the item gives more control over component placement.

Figure 19. Placing a Component

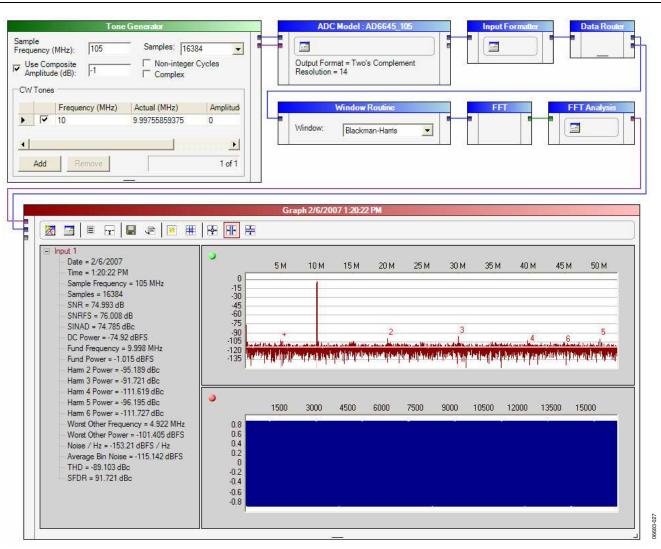

Sample placements of components are shown in Figure 19 in the following order: **Tone Generator**, **ADC Model**, **Input Formatter**, **Data Router**, **Window Routine**, **FFT**, **FFT Analysis**, and **Graph**.

For a brief summary of the functionality of each component, see the Components Overview section. The canvas should look similar to Figure 20, disregarding any component placement differences.

| 1     Tone Generator       Sample     Frequency (MHz):       100     Samples:       1024     ✓       Image: Samplitude (dB):     0       Image: Complex     Complex | 2 ADC Model                                | 3 Input Formatier    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|----------------------|

| CW Tones<br>Frequency (MHz) Actual (MHz) Amplitud<br>P V 10 9.9609375 0<br>Add Remove 1 of 1                                                                        | 5 Window Routine<br>Window: Blackman-Hamis | 6 FFT 7 FFT Analysis |

|                                                                                                                                                                     |                                            |                      |

|                                                                                                                                                                     |                                            | 800<br>800<br>888    |

Figure 20. Sample Component Placement

### **CONNECTING COMPONENTS**

To connect two components together, place a wire from the output node of one component to the input node of another, or vice versa. To place a new wire, use one of the following techniques:

- Click the node, drag the new wire to another component, and click again to connect.

- Drag the new wire to another component.

If the wire is not connected, it appears red. As soon as you apply the connection, the color changes.

Figure 21 illustrates the process of connecting the first output node of the **Tone Generator** to the first input node of the **ADC Model**.

For this example, place eight more wires. Figure 22 shows the canvas after making the remainder of these connections. Your canvas should look similar to this Figure 22.

| I ONE                                                                                  | Generator                 |               |         | ADC Model                         |  |

|----------------------------------------------------------------------------------------|---------------------------|---------------|---------|-----------------------------------|--|

| Sample<br>Frequency (MHz): 100                                                         | Samples: 1024             | _             | 8 🛛     |                                   |  |

| Amplitude (dB):                                                                        | Complex                   |               |         |                                   |  |

| Frequency (MHz)                                                                        | Actual (MHz)<br>9.9609375 | Amplitud<br>0 |         | Window Routine                    |  |

| •                                                                                      |                           | <u> </u>      | Window: | Blackman-Harris 🗾                 |  |

| Add Remove                                                                             |                           | 1 of 1        |         |                                   |  |

|                                                                                        |                           | $\checkmark$  |         |                                   |  |

| Tone                                                                                   | Generator                 |               |         | ADC Model                         |  |

| Sample                                                                                 |                           |               |         | ]                                 |  |

| Frequency (MHz): 100                                                                   | Samples: 1024             | 4 👻           |         |                                   |  |

| Frequency (MHz): 100                                                                   | Samples: 1024             |               |         | ]                                 |  |

| Frequency (MHz): 100                                                                   | - Non-integer             |               |         |                                   |  |

| Frequency (MHz):     100       Image: Use Composite Amplitude (dB):     0              | - Non-integer             |               |         | Window Routine                    |  |

| Frequency (MHz): 100                                                                   | ─                         | Cycles        |         |                                   |  |

| Frequency (MHz): 100<br>Use Composite Amplitude (dB): 0<br>CW Tones<br>Frequency (MHz) | Actual (MHz)              | Cycles        |         | Window Routine<br>Blackman-Harris |  |

Figure 21. Connecting Components

| Tone Gen <del>erator</del>                                                                                                                | ADC Model Input Formatter Data Router                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sample<br>Frequency (MHz): 100 Samples: 1024<br>Use Composite<br>Amplitude (dB): 0 Complex<br>CW Tones                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Coverage     Frequency (MHz)     Actual (MHz)     Amplitud       Ø     ✓     10     9.9609375     0       ✓     Add     Remove     1 of 1 | Window Routine         FFT         FFT Analysis           Window:         Blackman-Hams         Image: Comparison of the second |

|                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

Figure 22. Sample Connections

When you connect and move components, wires route on the canvas automatically. If the diagram begins to look convoluted, try reorganizing some components to force the wires to reroute.

To connect the end of an existing wire to a new node, do one of the following:

- Click a node, drag the opposite end of the wire to another node, and click again to connect.

- Drag the selected end to another node.

Like physical wires, wires in VisualAnalog carry information between components. Although it is transparent to the user in most cases, a wire can transfer one of several different data types. See the Data Types Overview section for more information.

### **ADJUSTING COMPONENT PARAMETERS**

Some components have adjustable parameters. The steps that follow show how to generate a simple waveform as input for an ADC model and display FFT and time domain results.

In Tone Generator, set the Sample Frequency (MHz) to 105. Also, change the Samples text to 16384, by using the drop-down arrow or entering the text manually. Update the Use Composite Amplitude (dB) to -1 (because you are evaluating ADC performance).

|                       | Tone            | Generator                  |           |

|-----------------------|-----------------|----------------------------|-----------|

| Sample<br>Frequency ( | MHz): 105       | Samples: 163               | 84 💌      |

| Use Com<br>Amplitud   | e (dB): -1      | │ Non-integer<br>│ Complex | Cycles    |

| CW Tones              |                 |                            |           |

|                       | Frequency (MHz) | Actual (MHz)               | Amplitude |

| ▶ ▼                   | 10              | 9.99755859375              | 0         |

| 4                     |                 |                            |           |

|                       |                 |                            |           |

| Add                   | Remove          |                            | 1 of 1    |

| Add                   | Nemove          |                            | 1011      |

Figure 23. Tone Generator Settings

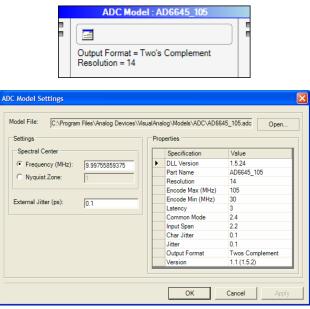

In ADC Model, click the Settings... button and click Open to browse for and select the AD6645\_105.adc model file. This file is located in the Models\ADC subdirectory in the VisualAnalog path. When the model opens, the file name appears in the Model File text box, along with information about that model in the Properties grid (see Figure 24). Click OK.

| AI                                                                               | DC Model                  |                 |

|----------------------------------------------------------------------------------|---------------------------|-----------------|

| IC Model Settings<br>Model File: C:\Program Files\Analog Devices\Vis<br>Settings | ualAnalog\Models\ADC\AD66 | 45_105.adc Open |

| Spectral Center                                                                  | Specification             | Value           |

| Frequency (MHz): 9.9609375                                                       | DLL Version               | 1.5.24          |

|                                                                                  | Part Name                 | AD6645_105      |

| C Nyquist Zone: 1                                                                | Resolution                | 14              |

|                                                                                  | Encode Max (MHz)          | 105             |

| External Jitter (ps): 0.1                                                        | Encode Min (MHz)          | 30              |

| Jo.1                                                                             | Latency                   | 3               |

|                                                                                  | Common Mode               | 2.4             |

|                                                                                  | Input Span                | 2.2             |

|                                                                                  | Char Jitter               | 0.1             |

|                                                                                  | Jitter                    | 0.1             |

|                                                                                  | Output Format             | Twos Complement |

|                                                                                  | Version                   | 1.1 (1.5.2)     |

|                                                                                  |                           |                 |

|                                                                                  |                           |                 |

|                                                                                  | ок                        | Cancel Apply    |

Figure 24. ADC Model and Settings Form

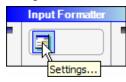

3. In **Input Formatter** (see Figure 25 through Figure 27), click the **Settings...**.button Then change the **Number Format** to two's complement. Next, change both the **Resolution** and **Alignment** to 14. Click **OK**.

| Input Formatte | r Settings 🛛 🔀   |

|----------------|------------------|

| Number Format: | Two's Complement |

| Bit Settings   |                  |

| Resolution:    | 14 🕂             |

| Alignment      | 14 🔅             |

| ОК             | Cancel Apply     |

Figure 25. Input Formatter and Settings Form

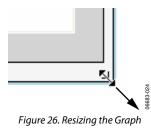

4. Resize the **Graph** component by positioning the cursor over the corner resize handle, drag the component out to a larger size (see Figure 26).

Next, resize the **Analysis Results** panel on the left side of the **Graph** component by positioning the mouse cursor over the vertical divider bar and drag to a new location (see Figure 27).

Figure 27. Resizing Analysis Results

Notice that there are two wires connected to the graph. This is because we have routed ADC samples to the graph as well as the FFT results. If you want to see the time domain representation of the data, you can click the **Toggle Additional Plot** button to view the second plot.

#### Figure 28. Toggle Additional Plot

#### **UPDATING RESULTS**

After making all required adjustments, you are ready to update the results of the canvas. There are three ways to update the canvas

- Press the Shortcut Key F5 or Ctrl + F5.

- Select the menu command **Canvas**, click **Update or Canvas**, and select **Continuous Update**.

- Click **Update** or **Continuous Update** on the tool bar.

After updating, the canvas should look similar to Figure 29.

Figure 29. Updated Canvas

### **MAKING LAYOUT CHANGES**

Most layout changes require that you select an object first. To select a component or wire, click the mouse somewhere on the object. If you are trying to select a component, be sure to click somewhere on the body (the header at the top always works). Hold down the Ctrl key to select or deselect more than one object.

Alternatively, you can draw a box on the canvas to select objects. Just press the mouse somewhere on the blank canvas, drag, and release around the objects you wish to select.

While objects are in a selected state, they can be deleted from the canvas. Click **Edit**, and select **Delete**, or just press the **Delete** key to remove the selected items.

While components are in a selected state, they can be moved to a new location. Press the left mouse button to click, hold, and drag one of the selected components to an empty location. Any connected wires automatically adjust accordingly. Some components, such as the graph, are resizable. Just click, hold, and drag on the resize handle at the bottom of the component.

You can cut, copy, or paste components and wires to new locations or other Canvas windows. To cut or copy, select the desired components. If any selected components are connected, the software copies the connecting wire as well. The appropriate **Edit** commands in the menu or use the standard Windows shortcut keys. To execute the cut, copy, or paste commands, use Ctrl + X, Ctrl + C, or Ctrl + V.

You can undo (or redo) parameter changes and layout changes. VisualAnalog maintains an undo stack and a redo stack of up to five layers of user actions.

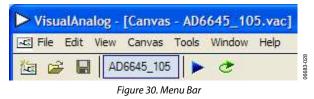

#### **USING THE MENU BAR**

The menu bar provides access to a variety of file and execution options using a standard menu format as shown in Figure 30.

#### File

**New**—Opens a blank canvas used for building a new component diagram.

**Open**—Loads an existing canvas using a standard file browser.

**Close**—Shuts down the current canvas. If you have changed the canvas since the last save, the program asks if you wish to save before closing.

**Save**—Saves the current canvas under the existing canvas file name. If the canvas does not already have a name, the software prompts for one before the save.

Save As—Saves the current template under a new name.

**Recent Files**—Displays a list of the last five canvas files opened or saved.

Exit-Exits VisualAnalog.

#### Edit

**Undo**—Reverses up to the last five actions, including deletion, parameter changes, component placement, and connectivity.

Redo—Performs the last undone action again.

**Cut**—Copies the selected objects to the clipboard and then deletes them from the canvas.

Copy—Copies the selected objects to the clipboard.

Paste—Places the items from the clipboard on the canvas.

Select All—Selects all items on the canvas.

Delete—Removes all currently selected items from the canvas.

#### View

**Components**—Displays the **Components Tool** form if it is not visible.

#### Canvas

**Update**—Runs the currently selected canvases by executing the component flow on each canvas.

**Continuous Update**—Causes the selected canvases to run continuously. When started, the **Continuous Update** menu item changes to **Stop Update**. Selecting this stops all processing. You can also automatically stop continuous update by using the **Stop Component**. See information on the **Stop Component** for more details.

**Properties**—Displays editable properties for the currently activated canvas (the canvas focused for editing).

#### Tools

**External Tools**—Displays a form with which the user can select external programs that VisualAnalog can open. Adding an executable item with this form places a new menu item underneath the **Tools** menu.

Options—Opens the VisualAnalog options form.

#### Window

Tile Horizontally—Tiles the canvases in a horizontal direction.

Tile Vertically—Tiles the canvases in a vertical direction.

Cascade—Cascades the canvases.

**Canvas Selection**—Provides a list of open canvases. From this list, the user can select a canvas for editing.

#### Help

**User Manual**—Opens this user manual with the associated PDF viewer.

**About VisualAnalog**—Displays the VisualAnalog version number and other information.

#### **USING THE TOOL BAR**

The tool bar provides quick access to common features that are available on the menu bar.

**New Canvas**—Opens a blank canvas used for building a new component diagram.

Figure 31. New Canvas Button

**File Open**—Loads an existing canvas using a standard file browser.

#### Figure 32. File Open Button

**File Save**—Saves the current canvas under the existing canvas file name. If the canvas does not already have a name, the software prompts for one before the save.

**Update**—Runs the currently selected canvases, by executing the component flow on each canvas.

**Continuous Update**–Runs the selected canvases continuously. When started, the **Continuous Update** menu item changes to **Stop Update**. Selecting this stops all processing. You can also automatically stop continuous update by using the **Stop Component**. See information on the **Stop Component** for more details.

6683-C

Figure 35. Continuous Update and Stop Update Icons

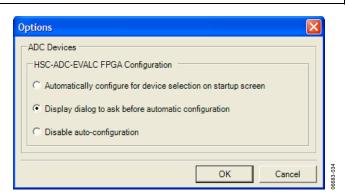

#### **USING THE OPTIONS FORM**

Ċ

The options form contains settings that affect the behavior of VisualAnalog. You can access the VisualAnalog options form by clicking the menu **Tools** and selecting **Options**.

Figure 36. Options Form

#### **ADC Devices**

**ADC Devices** contains options that affect the behavior of VisualAnalog when interfacing with ADC data capture boards.

HSC-ADC-EVALC FPGA Configuration allows you to adjust automatic FPGA configuration settings for the HSC-ADC-EVALC by selecting one of three options. These options only have an effect when choosing a template from the startup form that corresponds to a detected ADC device. For more information, see the Using the Start-Up Form section.

# DATA TYPES OVERVIEW

VisualAnalog components transfer information through wires. The wires themselves can carry any type of data, but most component inputs have limitations on what types of data they can accept. Most components that have an output pass a certain type of data to the next component.

You can pass any data type to the **Data Grid** component which displays an important portion of the data type. For example, when the **Data Grid** displays **Real Waveform Data**, it displays the list of samples.

### **REAL WAVEFORM DATA**

Real waveform data consists of an array of real samples along with the sample frequency.

### **COMPLEX WAVEFORM DATA**

Complex waveform data consists of an array of complex samples (I and Q) along with the sample frequency.

### **REAL FFT DATA**

Real FFT data consists of an array of data that is the FFT result of real waveform data, along with the sample frequency.

### **COMPLEX FFT DATA**

Complex FFT data consists of an array of data that is the FFT result of complex waveform data, along with the sample frequency.

#### **ANALYSIS DATA**

Analysis data consists of analysis results along with graph data and formatting information. This type of data can behave differently depending on the component that outputs it. Normally, this data type is passed straight to a **Graph** component because that component displays all the pertinent information. If you send this data to a **Data Grid** component, it displays the analysis results portion of the data only.

### VALUE COLLECTION

Value collection consists of parameter and value pairs. Components use this data type to display information.

#### NUMERIC VALUE

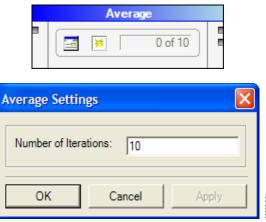

Numeric value contains only a floating-point number. However, some components treat this number as an integer. The **Average** and **Peak Hold** components both output a numeric value to indicate when their current sequence is finished. The **Stop** and **Graph** components both can use this value for a control input. See the Components Overview section for more information about the use of numeric value.

#### TONE LIST

The **Tone Generator** outputs the tone data type. The tone list contains frequency, phase, and amplitude information about the tones generated.

Note that two numeric formats can occur within VisualAnalog when using the waveform types. These are normalized data (which the majority of processing components use) and integer data.

The ADC Model, ADC Data Capture, and the FIFO4.x Interface components are all output integer data. Follow these components with an Input Formatter component to normalize the data.

The **Pattern Saver** and **Pattern Loader** components can support either data format as needed by the application. When loading a vector file, if the format is uncertain, manually examine it to determine how to process the file. Integer format should be obvious as either text-readable integers or hexadecimal values, and normalized data format appears as text-readable floatingpoint numbers. Note that VisualAnalog only assumes hexadecimal format for files with a .hex extension. To input hexadecimal values, rename the extension to .hex.

Finally, the **DPG Interface** always expects integer type format. If the waveform is not already in this format, precede this component with an **Output Formatter** component.

See the Components Overview section for more specific information on the requirements of each component.

# **COMPONENTS OVERVIEW**

VisualAnalog provides a variety of components used to accomplish tasks. Though some of these have a fixed mode of operation, others have a range of adjustable parameters that allow for customizable operation. Some of the components require you to access a settings form to adjust parameters. To access these forms, click the **Settings** button on the component.

### **BOARD INTERFACES**

The following sections are a basic overview of the functionality of the components.

Figure 38. DAC Pattern Generator

Figure 39. HSC-ADC-EVALC (ADC Data Capture Board)

### ADC DATA CAPTURE