# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# dbCOOL Remote Thermal Monitor and Fan Controller

The ADT7467 dbCOOL controller is a thermal monitor and multiple PWM fan controller for noise-sensitive or power-sensitive applications requiring active system cooling. The ADT7467 can drive a fan using either a low or high frequency drive signal, monitor the temperature of up to two remote sensor diodes plus its own internal temperature, and measure and control the speed of up to four fans so that they operate at the lowest possible speed for minimum acoustic noise.

The automatic fan speed control loop optimizes fan speed for a given temperature. A unique dynamic  $T_{MIN}$  control mode enables the system thermals/acoustics to be intelligently managed. The effectiveness of the system's thermal solution can be monitored using the THERM input. The ADT7467 also provides critical thermal protection to the system using the bidirectional THERM pin as an output to prevent system or component overheating.

#### Features

- Controls and Monitors up to 4 Fans

- High and Low Frequency Fan Drive Signal

- 1 On-chip and 2 Remote Temperature Sensors

- Series Resistance Cancellation on the Remote Channel

- Extended Temperature Measurement Range, up to 191°C

- Dynamic T<sub>MIN</sub> Control Mode Intelligently Optimizes System Acoustics

- Automatic Fan Speed Control Mode Manages System Cooling based on Measured Temperature

- Enhanced Acoustic Mode Dramatically Reduces User Perception of Changing Fan Speeds

- Thermal Protection Feature via THERM Output

- Monitors Performance Impact of Intel<sup>®</sup> Pentium<sup>®</sup> 4 Processor

- Thermal Control Circuit via THERM Input

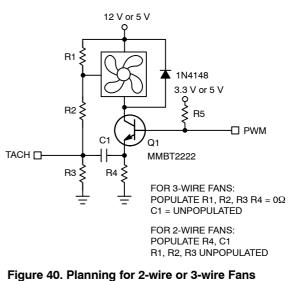

- 2-wire, 3-wire, and 4-wire Fan Speed Measurement

- Limit Comparison of All Monitored Values

- Meets SMBus 2.0 Electrical Specifications (Fully SMBus 1.1 Compliant)

- This Device is Pb-Free and is RoHS Compliant\*

- Halide-Free Packages are Available

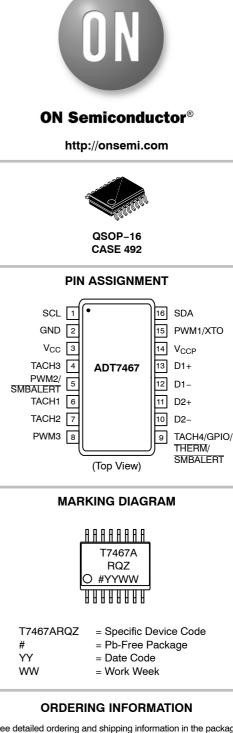

See detailed ordering and shipping information in the package dimensions section on page 70 of this data sheet.

\* For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

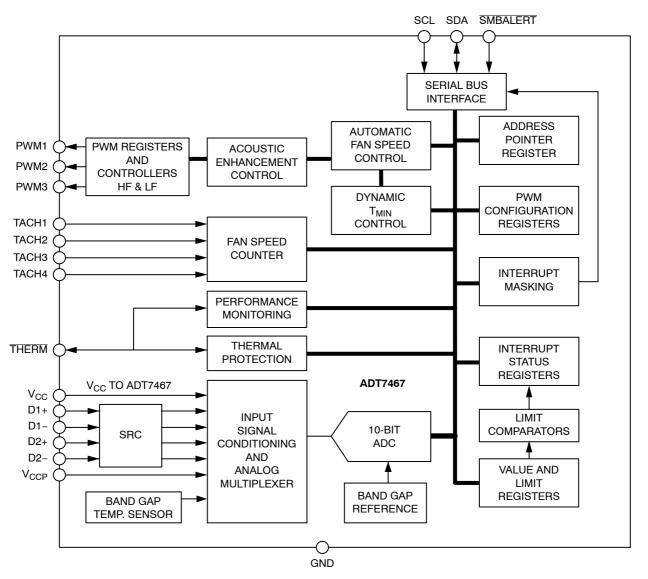

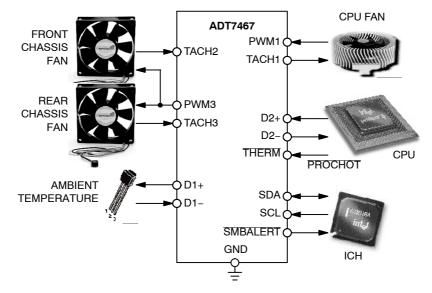

Figure 1. Functional Block Diagram

#### Table 1. ABSOLUTE MAXIMUM RATINGS

| Parameter                                                                                                               | Rating            | Unit |

|-------------------------------------------------------------------------------------------------------------------------|-------------------|------|

| Positive Supply Voltage (V <sub>CC</sub> )                                                                              | 5.5               | V    |

| Voltage on Any Input or Output Pin                                                                                      | –0.3 to +6.5      | V    |

| Input Current at Any Pin                                                                                                | ±5                | mA   |

| Package Input Current                                                                                                   | ±20               | mA   |

| Maximum Junction Temperature (T <sub>J MAX</sub> )                                                                      | 150               | °C   |

| Storage Temperature Range                                                                                               | –65 to +150       | °C   |

| Lead Temperature, Soldering<br>IR Reflow Peak Temperature<br>For Pb-Free Models<br>Lead Temperature (Soldering, 10 sec) | 220<br>260<br>300 | °C   |

| ESD Rating                                                                                                              | 1,000             | V    |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

WARNING: Electrostatic Sensitive Device - Do not open packages or handle except at a static-free workstation.

#### Table 2. PIN FUNCTION DESCRIPTIONS

| Pin No. | Mnemonic         | Description                                                                                                                                                                                                                                                                                                                                                                                      |

|---------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | SCL              | Digital Input (Open Drain). SMBus serial clock input. Requires SMBus pull-up.                                                                                                                                                                                                                                                                                                                    |

| 2       | GND              | Ground Pin for the ADT7467.                                                                                                                                                                                                                                                                                                                                                                      |

| 3       | V <sub>CC</sub>  | Power Supply. Can be powered by 3.3 V standby if monitoring in low power states is required. $V_{CC}$ is also monitored through this pin. The ADT7467 can also be powered from a 5 V supply. Setting Bit 7 of Configuration Register 1 (0x40) rescales the $V_{CC}$ input attenuators to correctly measure a 5 V supply.                                                                         |

| 4       | TACH3            | Digital Input (Open Drain). Fan tachometer input to measure speed of Fan 3. Can be reconfigured as an analog input (AIN3) to measure the speed of 2-wire fans (low frequency mode only).                                                                                                                                                                                                         |

| 5       | PWM2<br>SMBALERT | Digital Output (Open Drain). Requires 10 kΩ typical pull-up. Pulse width modulated output to control the speed of Fan 2. Can be configured as a high or low frequency drive.<br>Digital Output (Open Drain). This pin can be reconfigured as an SMBALERT interrupt output to signal out-of-limit conditions.                                                                                     |

| 6       | TACH1            | Digital Input (Open Drain). Fan tachometer input to measure speed of Fan 1. Can be reconfigured as an analog input (AIN1) to measure the speed of 2-wire fans (low frequency mode only).                                                                                                                                                                                                         |

| 7       | TACH2            | Digital Input (Open Drain). Fan tachometer input to measure speed of Fan 2. Can be reconfigured as an analog input (AIN2) to measure the speed of 2-wire fans (low frequency mode only).                                                                                                                                                                                                         |

| 8       | PWM3             | Digital I/O (Open Drain). Pulse width modulated output to control the speed of Fan 3 and Fan 4. Requires 10 k $\Omega$ typical pull-up. Can be configured as a high or low frequency drive.                                                                                                                                                                                                      |

| 9       | TACH4            | Digital Input (Open Drain). Fan tachometer input to measure speed of Fan 4. Can be reconfigured as an analog input (AIN4) to measure the speed of 2-wire fans (low frequency mode only).                                                                                                                                                                                                         |

|         | GPIO             | General-Purpose Open-Drain Digital I/O.                                                                                                                                                                                                                                                                                                                                                          |

|         | THERM            | Alternatively, the pin can be reconfigured as a bidirectional THERM pin, which can be used to time and monitor assertions on the THERM input. For example, the pin can be connected to the PROCHOT output of an Intel <sup>®</sup> Pentium <sup>®</sup> 4 processor or to the output of a trip point temperature sensor. This pin can be used as an output to signal overtemperature conditions. |

|         | SMBALERT         | Digital Output (Open Drain). This pin can be reconfigured as an SMBALERT interrupt output to signal out-of-limit conditions.                                                                                                                                                                                                                                                                     |

| 10      | D2-              | Cathode Connection to Second Thermal Diode.                                                                                                                                                                                                                                                                                                                                                      |

| 11      | D2+              | Anode Connection to Second Thermal Diode.                                                                                                                                                                                                                                                                                                                                                        |

| 12      | D1-              | Cathode Connection to First Thermal Diode.                                                                                                                                                                                                                                                                                                                                                       |

| 13      | D1+              | Anode Connection to First Thermal Diode.                                                                                                                                                                                                                                                                                                                                                         |

| 14      | V <sub>CCP</sub> | Analog Input. Monitors processor core voltage (0 V to 3 V).                                                                                                                                                                                                                                                                                                                                      |

| 15      | PWM1             | Digital Output (Open Drain). Pulse width modulated output to control the speed of Fan 1. Requires 10 k $\Omega$ typical pull-up.                                                                                                                                                                                                                                                                 |

|         | ХТО              | Also functions as the output from the XNOR tree in XNOR test mode.                                                                                                                                                                                                                                                                                                                               |

| 16      | SDA              | Digital I/O (Open Drain). SMBus bidirectional serial data. Requires 10 k $\Omega$ typical pull-up.                                                                                                                                                                                                                                                                                               |

| Parameter                                  | Test Conditions/Comments                                                                                                                                                                                                                                                                         | Min             | Тур                          | Max              | Unit     |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------------------|------------------|----------|

| POWER SUPPLY                               |                                                                                                                                                                                                                                                                                                  |                 |                              |                  | •        |

| Supply Voltage                             |                                                                                                                                                                                                                                                                                                  | 3.0             | 3.3                          | 5.5              | V        |

| Supply Current, I <sub>CC</sub>            | Interface Inactive, ADC Active<br>Standby Mode                                                                                                                                                                                                                                                   |                 | -                            | 3<br>20          | mA<br>μA |

| TEMPERATURE-TO-DIGITAL CONVER              | TER                                                                                                                                                                                                                                                                                              |                 |                              |                  |          |

| Local Sensor Accuracy                      | $\begin{array}{l} 0^{\circ}C \leq T_{A} \leq 70^{\circ}C \\ -40^{\circ}C \leq T_{A} \leq +100^{\circ}C \\ -40^{\circ}C \leq T_{A} \leq +120^{\circ}C \end{array}$                                                                                                                                | -<br>-3.5<br>-4 | -<br>-<br>-                  | ±1.5<br>+2<br>+2 | °C       |

| Resolution                                 |                                                                                                                                                                                                                                                                                                  | -               | 0.25                         | _                | °C       |

| Remote Diode Sensor Accuracy               | $\begin{array}{l} 0^{\circ}C \leq T_{A} \leq 70^{\circ}C; \ 0^{\circ}C \leq T_{D} \leq 120^{\circ}C \\ 0^{\circ}C \leq T_{A} \leq 105^{\circ}C; \ 0^{\circ}C \leq T_{D} \leq 120^{\circ}C \\ -40^{\circ}C \leq T_{A} \leq +120^{\circ}C; \ 0^{\circ}C \leq T_{D} \leq +120^{\circ}C \end{array}$ |                 | ±0.5<br>_<br>_               | ±1.5<br>+2<br>+2 | °C       |

| Resolution                                 |                                                                                                                                                                                                                                                                                                  | -               | 0.25                         | -                | °C       |

| Remote Sensor Source Current               | First Current<br>Second Current<br>Third Current                                                                                                                                                                                                                                                 | -<br>-<br>-     | 6<br>36<br>96                |                  | μΑ       |

| ANALOG-TO-DIGITAL CONVERTER (IN            | ICLUDING MUX AND ATTENUATORS)                                                                                                                                                                                                                                                                    |                 |                              | •                | •        |

| Total Unadjusted Error (TUE)               |                                                                                                                                                                                                                                                                                                  | -               | _                            | ±1.5             | %        |

| Differential Nonlinearity (DNL)            | 8 Bits                                                                                                                                                                                                                                                                                           | -               | -                            | ±1               | LSB      |

| Power Supply Sensitivity                   |                                                                                                                                                                                                                                                                                                  | -               | ±0.1                         | -                | %/V      |

| Conversion Time (Voltage Input)            | Averaging Enabled                                                                                                                                                                                                                                                                                | -               | 11                           | -                | ms       |

| Conversion Time (Local Temperature)        | Averaging Enabled                                                                                                                                                                                                                                                                                | -               | 12                           | -                | ms       |

| Conversion Time (Remote Temperature)       | Averaging Enabled                                                                                                                                                                                                                                                                                | -               | 38                           | -                | ms       |

| Total Monitoring Cycle Time                | Averaging Enabled<br>Averaging Disabled                                                                                                                                                                                                                                                          |                 | 145<br>19                    |                  | ms       |

| Input Resistance                           | For $V_{CC}$ Channel For All Channels other than $V_{CC}$                                                                                                                                                                                                                                        | 40<br>80        | 80<br>140                    | 100<br>200       | kΩ       |

| FAN RPM-TO-DIGITAL CONVERTER               |                                                                                                                                                                                                                                                                                                  |                 |                              |                  |          |

| Accuracy                                   | $\begin{array}{l} 0^{\circ}C \leq T_{A} \leq 70^{\circ}C, \ 3.3 \ V \\ -40^{\circ}C \leq T_{A} \leq +120^{\circ}C, \ 3.3 \ V \\ -40^{\circ}C \leq T_{A} \leq +120^{\circ}C, \ 5.5 \ V \end{array}$                                                                                               | -<br>-<br>-     | -<br>-                       | ±5<br>±7<br>±10  | %        |

| Full-scale Count                           |                                                                                                                                                                                                                                                                                                  | -               | -                            | 65,535           |          |

| Nominal Input RPM                          | Fan Count = 0xBFFF<br>Fan Count = 0x3FFF<br>Fan Count = 0x0438<br>Fan Count = 0x021C                                                                                                                                                                                                             | -<br>-<br>-     | 109<br>329<br>5000<br>10,000 | -<br>-<br>-<br>- | RPM      |

| Internal Clock Frequency                   | $0^{\circ}C \le T_{A} \le 70^{\circ}C, V_{CC} = 3.3 V$<br>-40°C ≤ $T_{A} \le +120^{\circ}C, V_{CC} = 3.3 V$                                                                                                                                                                                      | 85.5<br>83.7    | 90<br>90                     | 94.5<br>96.3     | kHz      |

| Internal Clock Frequency                   | $-40^{\circ}C \le T_{A} \le +120^{\circ}C, V_{CC} = 5.5 \text{ V}$                                                                                                                                                                                                                               | 81              | 90                           | 99               | kHz      |

| OPEN-DRAIN DIGITAL OUTPUTS, PWN            | 11 to PWM3, XTO                                                                                                                                                                                                                                                                                  |                 |                              |                  |          |

| Current Sink, I <sub>OL</sub>              |                                                                                                                                                                                                                                                                                                  | -               | _                            | 8.0              | mA       |

| Output Low Voltage, V <sub>OL</sub>        | $I_{OUT} = -8.0 \text{ mA}, V_{CC} = 3.3 \text{ V}$                                                                                                                                                                                                                                              | -               | _                            | 0.4              | V        |

| High Level Output Current, I <sub>OH</sub> | V <sub>OUT</sub> = V <sub>CC</sub>                                                                                                                                                                                                                                                               | -               | 0.1                          | 1.0              | μΑ       |

| OPEN-DRAIN SERIAL DATA BUS OUTI            | PUT (SDA)                                                                                                                                                                                                                                                                                        |                 |                              |                  |          |

| Output Low Voltage, V <sub>OL</sub>        | $I_{OUT} = -4.0 \text{ mA}, V_{CC} = 3.3 \text{ V}$                                                                                                                                                                                                                                              | -               | _                            | 0.4              | V        |

| High Level Output Current, I <sub>OH</sub> | V <sub>OUT</sub> = V <sub>CC</sub>                                                                                                                                                                                                                                                               | -               | 0.1                          | 1.0              | μA       |

| Parameter                              | Test Conditions/Comments          | Min  | Тур                   | Max      | Unit  |

|----------------------------------------|-----------------------------------|------|-----------------------|----------|-------|

| SMBus DIGITAL INPUTS (SCL, SI          | DA)                               | 1    |                       |          |       |

| Input High Voltage, V <sub>IH</sub>    |                                   | 2.0  | _                     | -        | V     |

| Input Low Voltage, V <sub>IL</sub>     |                                   | -    | _                     | 0.4      | V     |

| Hysteresis                             |                                   | -    | 500                   | -        | mV    |

| DIGITAL INPUT LOGIC LEVELS (           | TACH INPUTS)                      |      |                       |          |       |

| Input High Voltage, V <sub>IH</sub>    | Maximum Input Voltage             | 2.0  |                       | _<br>5.5 | V     |

| Input Low Voltage, V <sub>IL</sub>     | Minimum Input Voltage             | -0.3 |                       | 0.8<br>_ | V     |

| Hysteresis                             |                                   | -    | 0.5                   | -        | V p-p |

| DIGITAL INPUT LOGIC LEVELS (           | THERM) ADTL+                      | I    |                       |          |       |

| Input High Voltage, V <sub>IH</sub>    |                                   | -    | $0.75 \times V_{CCP}$ | -        | V     |

| Input Low Voltage, V <sub>IL</sub>     |                                   | -    | -                     | 0.4      | V     |

| DIGITAL INPUT CURRENT                  |                                   | I    |                       |          |       |

| Input High Current, I <sub>IH</sub>    | V <sub>IN</sub> = V <sub>CC</sub> | -1   | _                     | _        | μΑ    |

| Input Low Current, IIL                 | V <sub>IN</sub> = 0               | -    | _                     | 1        | μA    |

| Input Capacitance, C <sub>IN</sub>     |                                   | -    | 5                     | _        | pF    |

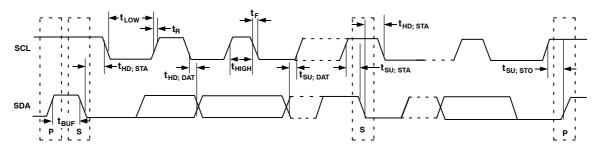

| SERIAL BUS TIMING                      |                                   |      |                       |          |       |

| Clock Frequency, f <sub>SCLK</sub>     |                                   | 10   | _                     | 400      | kHz   |

| Glitch Immunity, t <sub>SW</sub>       |                                   | -    | _                     | 50       | ns    |

| Bus Free Time, t <sub>BUF</sub>        |                                   | 4.7  | _                     | -        | μs    |

| Start Setup Time, t <sub>SU; STA</sub> |                                   | 4.7  | _                     | _        | μs    |

| Start Hold Time, t <sub>HD; STA</sub>  |                                   | 4.0  | _                     | _        | μs    |

| SCL Low Time, t <sub>LOW</sub>         |                                   | 4.7  | _                     | -        | μs    |

| SCL High Time, t <sub>HIGH</sub>       |                                   | 4.0  | _                     | 50       | μs    |

| SCL, SDA Rise Time, t <sub>r</sub>     |                                   | -    | _                     | 1000     | ns    |

| SCL, SDA Fall Time, t <sub>f</sub>     |                                   | -    | -                     | 300      | μs    |

| Data Setup Time, t <sub>SU; DAT</sub>  |                                   | 250  | -                     | -        | ns    |

| Data Hold Time, t <sub>HD; DAT</sub>   |                                   | 300  | -                     | -        | ns    |

| Detect Clock Low Timeout, tTIMEOL      | T Can be Optionally Disabled      | 15   | _                     | 35       | ms    |

1. All voltages are measured with respect to GND, unless otherwise specified. Typicals are at  $T_A = 25^{\circ}C$  and represent the most likely parametric norm. Logic inputs accept input high voltages up to  $V_{MAX}$  even when the device is operating down to  $V_{MIN}$ . Timing specifications are tested at logic levels of  $V_{IL} = 0.8$  V for a falling edge and  $V_{IH} = 2.0$  V for a rising edge. SMBus timing specifications are guaranteed by design and are not production tested.

Figure 2. Serial Bus Timing Diagram

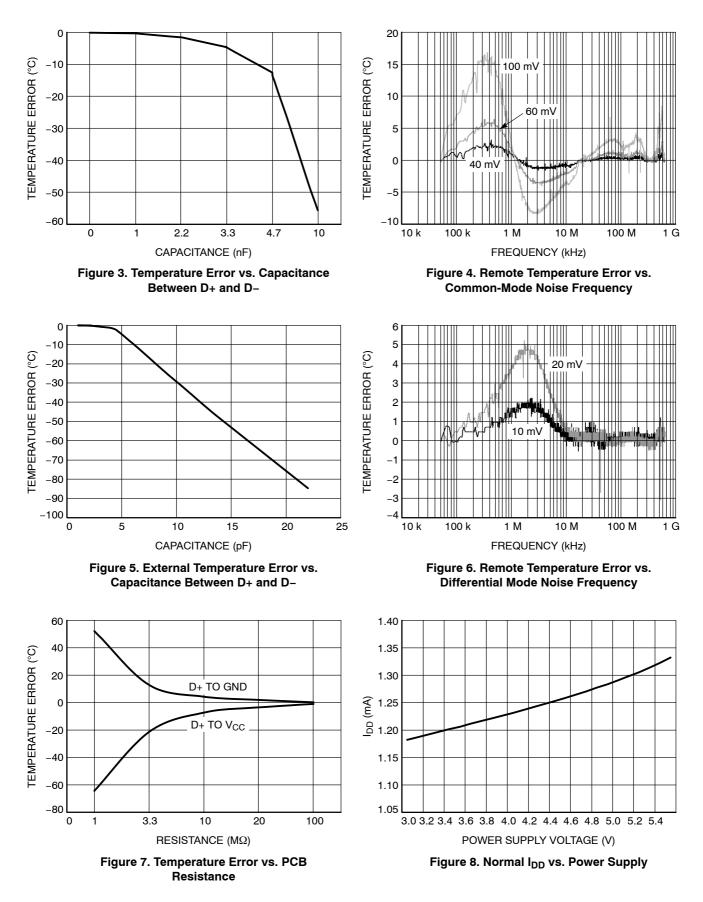

### **TYPICAL PERFORMANCE CHARACTERISTICS**

### TYPICAL PERFORMANCE CHARACTERISTICS (Cont'd)

### **Product Description**

The ADT7467 is a complete thermal monitor and multiple fan controller for systems requiring thermal monitoring and cooling. The device communicates with the system via a serial system management bus. The serial bus controller has a serial data line for reading and writing addresses and data (Pin 16) and an input line for the serial clock (Pin 1). All control and programming functions for the ADT7467 are performed over the serial bus. In addition, one of two pins can be reconfigured as an SMBALERT output to signal out-of-limit conditions.

#### Comparison between ADT7460 and ADT7467

The ADT7467 is an upgrade from the ADT7460. The ADT7467 and ADT7460 are almost pin and register map compatible. The ADT7467 and ADT7460 have the following differences:

- 1. On the ADT7467, the PWM drive signals can be configured as either high frequency or low frequency drives. The low frequency option is programmable between 10 Hz and 100 Hz. The high frequency option is 22.5 kHz. On the ADT7460, only the low frequency option is available.

- 2. Once  $V_{CC}$  and  $V_{CCP}$  are powered up, monitoring of temperature and fan speeds is enabled on the ADT7467. If  $V_{CCP}$  is never powered up, monitoring is enabled when the first SMBus transaction with the ADT7467 is complete. On the ADT7460, the STRT bit in Configuration Register 1 must be set to enable monitoring.

- 3. The fans are switched off by default upon power-up of the ADT7467. On the ADT7460, the fans run at full speed upon power-up. Fail-safe cooling is provided on the ADT7467. If the measured temperature exceeds the THERM limit (100°C), the fans run at full speed. Fail-safe cooling is also provided 4.6 sec after V<sub>CCP</sub> is powered up. The fans operate at full speed if the ADT7467 has not been addressed via the SMBus within 4.6 sec of when the V<sub>CCP</sub> is powered up. This protects the system in the event that the SMBus fails. The ADT7467 can be programmed at any time, and it behaves as programmed. If V<sub>CCP</sub> is never powered up, fail-safe cooling is effectively disabled. If V<sub>CCP</sub> is disabled, writing to the ADT7467 at any time causes the ADT7467 to operate normally.

- 4. Series resistance cancellation (SRC) is provided on the remote temperature channels on the ADT7467, but not on the ADT7460. SRC automatically cancels linear offset introduced by a series resistance between the thermal diode and the sensor.

- 5. The ADT7467 has an extended temperature measurement range. The measurement range goes

from  $-64^{\circ}$ C to  $+191^{\circ}$ C. On the ADT7460, the measurement range is from  $-127^{\circ}$ C to  $+127^{\circ}$ C. This means that the ADT7467 can measure higher temperatures. The ADT7467 also includes the ADT7460 temperature range; the temperature measurement range can be switched by setting Bit 0 of Configuration Register 5.

- 6. The ADT7467 maximum fan speed (% duty cycle) in the automatic fan speed control loop can be programmed. The maximum fan speed is 100% duty cycle on the ADT7460 and is not programmable.

- 7. The offset register in the ADT7467 is programmable up to  $\pm 64^{\circ}$ C with 0.50°C resolution. The offset register of the ADT7460 is programmable up to  $\pm 32^{\circ}$ C with 0.25°C resolution.

- 8.  $V_{CCP}$  is monitored on Pin 14 of the ADT7467 and can be used to set the threshold for THERM (PROCHOT) (2/3 of  $V_{CCP}$ ). 2.5 V is monitored on Pin 14 of the ADT7460. The threshold for THERM (PROCHOT) is set at  $V_{IH} = 1.7$  V and  $V_{IL} = 0.8$  V on the ADT7460.

- 9. On the ADT7460, Pin 14 could be reconfigured as <u>SMBALERT</u>. This is not available on the ADT7467. <u>SMBALERT</u> can be enabled instead on Pin 9.

- A GPIO can also be made available on Pin 9 on the ADT7467. This is not available on the ADT7460. Set the GPIO polarity and direction in Configuration Register 5. The GPIO status bit is Bit 5 of Status Register 2 (it is shared with TACH4 and THERM because only one can be enabled at a time).

- 11. The ADT7460 has three possible SMBus addresses, which are selectable using the address select and address enable pins. The ADT7467 has one SMBus address available at Address 0x2E.

Due to the inclusion of extra functionality, the register map has changed, including an additional configuration register, Configuration Register 5 at Address 0x7C.

### **Configuration Register 5**

Bit 0: If Bit 0 is set to 1, the ADT7467, in terms of temperature, is backward compatible with the ADT7460. Measurements, including  $T_{MIN}$  calibration circuit and fan control, work in the range  $-127^{\circ}$ C to  $+127^{\circ}$ C. In addition, care should be taken in reprogramming the temperature limits ( $T_{MIN}$ , operating point, THERM) to their desired twos complement value, because the power-on default for them is at Offset 64. The extended temperature range is  $-64^{\circ}$ C to  $+191^{\circ}$ C temperature range.

Bit 1 = 0 is the high frequency (22.5 kHz) fan drive signal.

Bit 1 = 1 switches the fan drive to low frequency PWM, programmable between 10 Hz and 100 Hz, the same as the ADT7460. The default is 0, or HF PWM.

Bit 2 sets the direction for the GPIO: 0 = input, 1 = output. Bit 3 sets the GPIO polarity: 0 = active low, 1 = active high.

#### Setting the Functionality of Pin 9

Pin 9 on the ADT7467 has four possible functions: <u>SMBALERT</u>, <u>THERM</u>, GPIO, and TACH4. The user chooses the required functionality by setting Bit 0 and Bit 1 of Configuration Register 4 at Address 0x7D.

#### Table 4. PIN 9 SETTINGS

| Bit 1 | Bit 0 | Function |

|-------|-------|----------|

| 0     | 0     | TACH4    |

| 0     | 1     | THERM    |

| 1     | 0     | SMBALERT |

| 1     | 1     | GPIO     |

#### **Recommended Implementation**

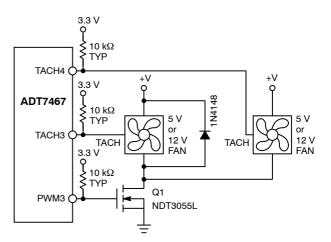

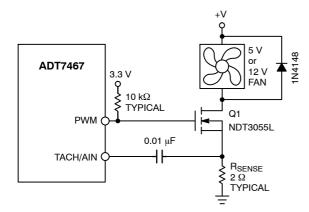

Configuring the ADT7467 as in Figure NO TAG allows the system designer to use the following features:

- Two PWM Outputs for Fan Control of Up to Three Fans (The Front and Rear Chassis Fans are Connected in Parallel)

- Three TACH Fan Speed Measurement Inputs

- V<sub>CC</sub> Measured Internally through Pin 3

- CPU Temperature Measured Using the Remote 1 Temperature Channel

- Ambient Temperature Measured through the Remote 2 Temperature Channel

- Bidirectional THERM Pin. This Feature Allows Intel<sup>®</sup> Pentium<sup>®</sup> 4 PROCHOT Monitoring and Can Function as an Overtemperature THERM Output. Alternatively, it Can be Programmed as an SMBALERT System Interrupt Output

Figure 14. ADT7467 Implementation

#### Serial Bus Interface

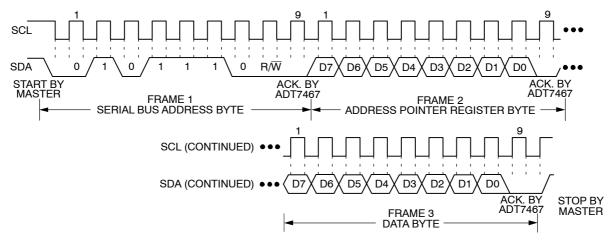

On PCs and servers, control of the ADT7467 is carried out using the serial system management bus (SMBus). The ADT7467 is connected to this bus as a slave device under the control of a master controller, which is usually (but not necessarily) the ICH.

The ADT7467 has a fixed 7-bit serial bus address of 0101110 or 0x2E. The read/write bit must be added to get the 8-bit address (01011100 or 0x5C). Data is sent over the serial bus in sequences of nine clock pulses: eight bits of data followed by an acknowledge bit from the slave device. Transitions on the data line must occur during the low period of the clock signal and remain stable during the high period, because a low-to-high transition might be interpreted as a stop signal when the clock is high. The number of data bytes that can be transmitted over the serial bus in a single read or

write operation is only limited by what the master and slave devices can handle.

When all data bytes have been read or written, stop conditions are established. In write mode, the master pulls the data line high during the 10th clock pulse to assert a stop condition. In read mode, the master device overrides the acknowledge bit by pulling the data line high during the low period before the ninth clock pulse. This is known as a no acknowledge. The master then takes the data line low during the low period before the 10th clock pulse, and then high during the 10th clock pulse to assert a stop condition.

Any number of bytes of data can be transferred over the serial bus in one operation. It is not possible to mix a read and a write in one operation, however, because the type of operation is determined at the beginning and cannot subsequently be changed without starting a new operation.

In the ADT7467, write operations contain either one or two bytes, and read operations contain one byte. To write data to a device data register or read data from it, the address pointer register must first be set. The first byte of a write operation always contains an address, which is stored in the address pointer register, and the second byte, if there is a second byte, is written to the register selected by the address pointer register.

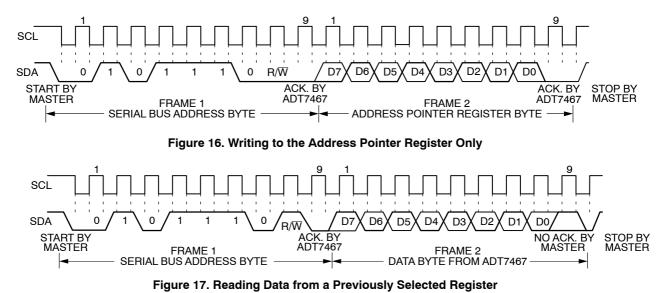

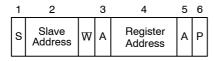

This write operation is illustrated in Figure 15. The device address is sent over the bus, and then  $R/\overline{W}$  is set to 0. This is followed by two data bytes. The first data byte is the address of the internal data register, and the second data byte is the data written to that internal data register.

When reading data from a register, there are two possibilities:

1. If the address pointer register value of the ADT7467 is unknown or not the desired value, it must be set to the correct value before data can be read from the desired data register. This is achieved by writing a data byte containing the register address to the ADT7467. This is shown in Figure 16. A read operation is then performed consisting of the serial bus address and the  $R/\overline{W}$  bit set to 1, followed by the data byte read from the data register. This is shown in Figure 17.

2. If the address pointer register is known to be at the desired address, data can be read from the corresponding data register without first writing to the address pointer register, as shown in Figure 17.

If the address pointer register is already at the correct value, it is possible to read a data byte from the data register without first writing to the address pointer register. However, it is not possible to write data to a register without writing to the address pointer register, because the first data byte of a write is always written to the address pointer register.

In addition to supporting the send byte and receive byte protocols, the ADT7467 also supports the read byte protocol. (See the Intel *System Management Bus Specifications Rev. 2* for more information.)

If several read or write operations must be performed in succession, the master can send a repeat start condition instead of a stop condition to begin a new operation.

Figure 15. Writing a Register Address to the Address Pointer Register, then Writing Data to the Selected Register

### Write Operations

The SMBus specification defines several protocols for different types of read and write operations. The ones used in the ADT7467 are discussed here. The following abbreviations are used in Figure 18 through Figure 20:

- S = start

- P = stop

- R = read

- W = write

- A = acknowledge

- $\overline{A}$  = no acknowledge

The ADT7467 uses the following SMBus write protocols.

### Send Byte

In this operation, the master device sends a single command byte to a slave device as follows:

- 1. The master device asserts a start condition on SDA.

- 2. The master sends the 7-bit slave address followed by the write bit (low).

- 3. The addressed slave device asserts an acknowledge on SDA.

- 4. The master sends a command code.

- 5. The slave asserts an acknowledge on SDA.

- 6. The master asserts a stop condition on SDA, and the transaction ends.

For the ADT7467, the send byte protocol is used to write a register address to RAM for a subsequent single byte read from the same address. This operation is illustrated in Figure 18.

#### Figure 18. Setting a Register Address for Subsequent Read

If the master is required to read data from the register directly after setting up the address, it can assert a repeat start condition immediately after the final acknowledge and carry out a single byte read without asserting an intermediate stop condition.

#### Write Byte

In this operation, the master device sends a command byte and one data byte to the slave device as follows:

- 1. The master device asserts a start condition on SDA.

- 2. The master sends the 7-bit slave address followed by the write bit (low).

- 3. The addressed slave device asserts an acknowledge on SDA.

- 4. The master sends a command code.

- 5. The slave asserts an acknowledge on SDA.

- 6. The master sends a data byte.

- 7. The slave asserts an acknowledge on SDA.

8. The master asserts a stop condition on SDA to end the transaction.

This operation is illustrated in Figure 19.

| 1 | 2                |   | 3 | 4                | 5 | 6    | 7 | 8 |

|---|------------------|---|---|------------------|---|------|---|---|

| s | Slave<br>Address | w | A | Slave<br>Address | А | Data | А | Ρ |

Figure 19. Single Byte Write to a Register

#### **Read Operations**

The ADT7467 uses the following SMBus read protocols.

#### **Receive Byte**

This operation is useful when repeatedly reading a single register. The register address must have been set up previously. In this operation, the master device receives a single byte from a slave device as follows:

- 1. The master device asserts a start condition on SDA.

- 2. The master sends the 7-bit slave address followed by the read bit (high).

- 3. The addressed slave device asserts an acknowledge on SDA.

- 4. The master receives a data byte.

- 5. The master asserts a no acknowledge on SDA.

- 6. The master asserts a stop condition on SDA, and the transaction ends.

In the ADT7467, the receive byte protocol is used to read a single byte of data from a register whose address has previously been set by a send byte or write byte operation. This operation is illustrated in Figure 20.

| 1 | 2                |   | 3 | 4    | 5 | 6 |  |

|---|------------------|---|---|------|---|---|--|

| s | Slave<br>Address | R | A | Data | Ā | Ρ |  |

Figure 20. Single Byte Read from a Register

#### Alert Response Address

Alert response address (ARA) is a feature of SMBus devices that allows an interrupting device to identify itself to the host when multiple devices exist on the same bus.

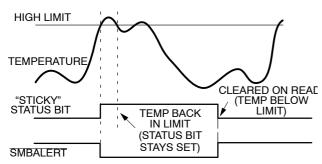

The <u>SMBALERT</u> output can be used as either an interrupt output or an <u>SMBALERT</u>. One or more outputs can be connected to a common <u>SMBALERT</u> line connected to the master. If a device's <u>SMBALERT</u> line goes low, the following procedure occurs:

- 1. **SMBALERT** is pulled low.

- 2. The master initiates a read operation and sends the alert response address (ARA = 0001 100). This is a general call address that must not be used as a specific device address.

- 3. The device whose SMBALERT output is low responds to the alert response address, and the master reads its device address. The address of the

device is now known and can be interrogated in the usual way.

- 4. If more than one device's <u>SMBALERT</u> output is low, the one with the lowest device address has priority in accordance with normal SMBus arbitration.

- 5. Once the ADT7467 has responded to the alert response address, the master must read the status registers. The SMBALERT is cleared only if the error condition is absent.

#### **SMBus Timeout**

The ADT7467 includes an SMBus timeout feature. If there is no SMBus activity for 35 ms, the ADT7467 assumes that the bus is locked and releases the bus. This prevents the device from locking or holding the SMBus in anticipation of receiving data. Some SMBus controllers cannot handle the SMBus timeout feature, so it can be disabled.

#### Configuration Register 1 (0x40)

<6> TODIS = 0, SMBus timeout enabled (default) <6> TODIS = 1, SMBus timeout disabled

#### Analog-to-Digital Converter

All analog inputs are multiplexed into the on-chip, successive approximation, analog-to-digital converter, which has a resolution of 10 bits. The basic input range is 0 V to 2.25 V, but the input has built-in attenuators to allow measurement of  $V_{\rm CCP}$  without any external components. To allow for the tolerance of the supply voltage, the ADC produces an output of 3/4 full scale (decimal 768 or 300 hexadecimal) for the nominal input voltage and, therefore, has adequate headroom to deal with overvoltages.

#### **Voltage Measurement Input**

The ADT7467 has one external voltage measurement channel. It can also measure its own supply voltage,  $V_{CC}$ . Pin 14 can measure  $V_{CCP}$ . The  $V_{CC}$  supply voltage measurement is carried out through the  $V_{CC}$  pin (Pin 3). Setting Bit 7 of Configuration Register 1 (0x40) allows a 5 V supply to power the ADT7467 and be measured without overranging the  $V_{CC}$  measurement channel. The  $V_{CCP}$  input can be used to monitor a chipset supply voltage in computer systems.

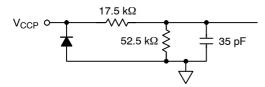

#### Input Circuitry

The internal structure for the  $V_{CCP}$  analog input is shown in Figure 21. The input circuit consists of an input protection diode, an attenuator, and a capacitor to form a first-order low-pass filter that gives the input immunity to high frequency noise.

#### Voltage Measurement Registers

Register 0x21 V<sub>CCP</sub> reading = 0x00 default Register 0x22 V<sub>CC</sub> reading = 0x00 default

#### V<sub>CCP</sub> Limit Registers

Associated with the  $V_{CCP}$  and  $V_{CC}$  measurement channels is a high and low limit register. Exceeding the programmed high or low limit causes the appropriate status bit to be set. Exceeding either limit can also generate SMBALERT interrupts.

Register 0x46  $V_{CCP}$  low limit = 0x00 default Register 0x47  $V_{CCP}$  high limit = 0xFF default Register 0x48  $V_{CC}$  low limit = 0x00 default

Register  $0x49 V_{CC}$  high limit = 0xFF default

Table 6 shows the input ranges of the analog inputs and output codes of the 10-bit ADC.

When the ADC is running, it samples and converts a voltage input in 0.7 ms and averages 16 conversions to reduce noise; a measurement takes nominally 11 ms.

#### Additional ADC Functions for Voltage Measurements

A number of other functions are available on the ADT7467 to offer the system designer increased flexibility.

#### **Turn-off Averaging**

For each voltage measurement read from a value register, 16 readings are made internally, the results of which are averaged and then placed into the value register. For instances where faster conversions are needed, setting Bit 4 of Configuration Register 2 (0x73) turns averaging off. This produces a reading that is 16 times faster (0.7 ms), but the reading may be noisier.

#### **Bypass Voltage Input Attenuator**

Setting Bit 5 of Configuration Register 2 (0x73) removes the attenuation circuitry from the  $V_{CCP}$  input. This allows the user to directly connect external sensors or to rescale the analog voltage measurement inputs for other applications. The input range of the ADC without the attenuators is 0 V to 2.25 V.

#### Single-channel ADC Conversion

Setting Bit 6 of Configuration Register 2 (0x73) places the ADT7467 into single-channel ADC conversion mode. In this mode, the ADT7467 can be made to read a single voltage channel only. If the internal ADT7467 clock is used, the selected input is read every 0.7 ms. The appropriate ADC channel is selected by writing to Bits <7:5> of the TACH1 minimum high byte register (0x55).

Figure 21. Structure of Analog Inputs

# Table 5. PROGRAMMING SINGLE-CHANNEL ADC MODE

| Bits <7:5>, Register 0x55 | Channel Selected     |

|---------------------------|----------------------|

| 001                       | V <sub>CCP</sub>     |

| 010                       | V <sub>CC</sub>      |

| 101                       | Remote 1 Temperature |

| 110                       | Local Temperature    |

| 111                       | Remote 2 Temperature |

### Configuration Register 2 (0x73)

<4> = 1, Averaging Off

- <5> = 1, Bypass Input Attenuators

- <6> = 1, Single-channel Conversion Mode

### TACH1 Minimum High Byte (0x55)

<7:5> Selects ADC Channel for Single-channel Convert Mode

### Table 6. 10-BIT ANALOG-TO-DIGITAL OUTPUT CODE VS. VIN

| Input Voltage                        |                                        |                  | A/D Output      |                  |  |

|--------------------------------------|----------------------------------------|------------------|-----------------|------------------|--|

| V <sub>CC</sub> (5 V <sub>IN</sub> ) | V <sub>CC</sub> (3.3 V <sub>IN</sub> ) | V <sub>CCP</sub> | Decimal         | Binary (10 Bits) |  |

| <0.0065                              | <0.0042                                | <0.00293         | 0               | 00000000 00      |  |

| 0.0065 to 0.0130                     | 0.0042 to 0.0085                       | 0.0293 to 0.0058 | 1               | 0000000 01       |  |

| 0.0130 to 0.0195                     | 0.0085 to 0.0128                       | 0.0058 to 0.0087 | 2               | 0000000 10       |  |

| 0.0195 to 0.0260                     | 0.0128 to 0.0171                       | 0.0087 to 0.0117 | 3               | 00000000 11      |  |

| 0.0260 to 0.0325                     | 0.0171 to 0.0214                       | 0.0117 to 0.0146 | 4               | 00000001 00      |  |

| 0.0325 to 0.0390                     | 0.0214 to 0.0257                       | 0.0146 to 0.0175 | 5               | 00000001 01      |  |

| 0.0390 to 0.0455                     | 0.0257 to 0.0300                       | 0.0175 to 0.0205 | 6               | 00000001 10      |  |

| 0.0455 to 0.0521                     | 0.0300 to 0.0343                       | 0.0205 to 0.0234 | 7               | 00000001 11      |  |

| 0.0521 to 0.0586                     | 0.0343 to 0.0386                       | 0.0234 to 0.0263 | 8               | 00000010 00      |  |

|                                      |                                        |                  |                 |                  |  |

| 1.6675 to 1.6740                     | 1.100 to 1.1042                        | 0.7500 to 0.7529 | 256 (1/4 scale) | 01000000 00      |  |

|                                      |                                        |                  |                 |                  |  |

| 3.330 to 3.3415                      | 2.200 to 2.2042                        | 1.5000 to 1.5029 | 512 (1/2 scale) | 1000000 00       |  |

|                                      |                                        |                  |                 |                  |  |

| 5.0025 to 5.0090                     | 3.300 to 3.3042                        | 2.2500 to 2.2529 | 768 (3/4 scale) | 11000000 00      |  |

|                                      |                                        |                  |                 |                  |  |

| 6.5983 to 6.6048                     | 4.3527 to 4.3570                       | 2.9677 to 2.9707 | 1013            | 11111101 01      |  |

| 6.6048 to 6.6113                     | 4.3570 to 4.3613                       | 2.9707 to 2.9736 | 1014            | 11111101 10      |  |

| 6.6113 to 6.6178                     | 4.3613 to 4.3656                       | 2.9736 to 2.9765 | 1015            | 11111101 11      |  |

| 6.6178 to 6.6244                     | 4.3656 to 4.3699                       | 2.9765 to 2.9794 | 1016            | 11111110 00      |  |

| 6.6244 to 6.6309                     | 4.3699 to 4.3742                       | 2.9794 to 2.9824 | 1017            | 11111110 01      |  |

| 6.6309 to 6.6374                     | 4.3742 to 4.3785                       | 2.9824 to 2.9853 | 1018            | 11111110 10      |  |

| 6.6374 to 6.4390                     | 4.3785 to 4.3828                       | 2.9853 to 2.9882 | 1019            | 11111110 11      |  |

| 6.6439 to 6.6504                     | 4.3828 to 4.3871                       | 2.9882 to 2.9912 | 1020            | 11111111 00      |  |

| 6.6504 to 6.6569                     | 4.3871 to 4.3914                       | 2.9912 to 2.9941 | 1021            | 11111111 01      |  |

| 6.6569 to 6.6634                     | 4.3914 to 4.3957                       | 2.9941 to 2.9970 | 1022            | 11111111 10      |  |

| >6.6634                              | >4.3957                                | >2.9970          | 1023            | 1111111 11       |  |

#### **Temperature Measurement**

A simple method of measuring temperature is to exploit the negative temperature coefficient of a diode, measuring the base-emitter voltage ( $V_{BE}$ ) of a transistor operated at constant current. Unfortunately, this technique requires calibration to null the effect of the absolute value of  $V_{BE}$ , which varies from each device.

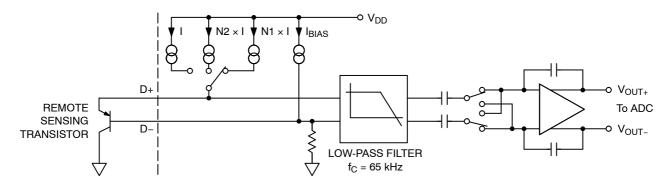

The technique used in the ADT7467 is to measure the change in  $V_{BE}$  when the device is operated at three currents. Previous devices have used only two operating currents, but the use of a third current allows automatic cancellation of resistances in series with the external temperature sensor.

Figure 23 shows the input signal conditioning used to measure the output of an external temperature sensor. This figure shows the external sensor as a substrate transistor, but it could equally be a discrete transistor. If a discrete transistor is used, the collector is not grounded and should be linked to the base. To prevent ground noise from interfering with the measurement, the more negative terminal of the sensor is not referenced to ground but is biased above ground by an internal diode at the D– input. C1 can optionally be added as a noise filter (the recommended maximum value is 1,000 pF). However, a better option in noisy environments is to add a filter as described in the Noise Filtering section.

#### Local Temperature Measurement

The ADT7467 contains an on-chip band gap temperature sensor whose output is digitized by the on-chip 10-bit ADC. The 8-bit MSB temperature data is stored in the local temperature register (Address 0x26). Because both positive and negative temperatures can be measured, the temperature data is stored in Offset 64 format or twos complement format, as shown in Table 7 and Table 8. Theoretically, the

temperature sensor and ADC can measure temperatures from  $-128^{\circ}$ C to  $+127^{\circ}$ C (or  $-64^{\circ}$ C to  $+191^{\circ}$ C in the extended temperature range) with a resolution of 0.25°C. However, this exceeds the operating temperature range of the device, preventing local temperature measurements outside the ADT7467 operating temperature range.

#### **Remote Temperature Measurement**

The ADT7467 can measure the temperature of two remote diode sensors or diode-connected transistors connected to Pin 10 and Pin 11 or to Pin 12 and Pin 13.

The forward voltage of a diode or diode-connected transistor operated at a constant current exhibits a negative temperature coefficient of about  $-2 \text{ mV/}^{\circ}\text{C}$ . Unfortunately, the absolute value of V<sub>BE</sub> varies from each device and thus requires individual calibration; therefore, the technique is unsuitable for mass production. The technique used in the ADT7467 is to measure the change in V<sub>BE</sub> when the device is operated at three currents. This is given by:

$$\Delta V_{BE} = kT/q \times \ln(N)$$

(eq. 1)

where:

k is Boltzmann's constant.

q is the charge on the carrier.

T is the absolute temperature in Kelvins.

N is the ratio of the two currents.

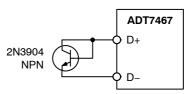

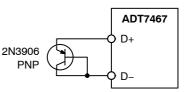

Figure 22 shows the input signal conditioning used to measure the output of a remote temperature sensor. This figure shows the external sensor as a substrate transistor provided for temperature monitoring on some microprocessors. It could also be a discrete transistor such as a 2N3904/2N3906.

Figure 22. Signal Conditioning for Remote Diode Temperature Sensors

If a discrete transistor is used, the collector is not grounded and should be linked to the base. If a PNP transistor is used, the base is connected to the D– input and the emitter is connected to the D+ input. If an NPN transistor is used, the emitter is connected to the D– input and the base is connected to the D+ input. Figure 24 and Figure 25 show how to connect the ADT7467 to an NPN or PNP transistor for temperature measurement. To prevent ground noise from interfering with the measurement, the more negative terminal of the sensor is not referenced to ground but is biased above ground by an internal diode at the D- input.

To measure  $\Delta V_{BE}$ , the operating current through the sensor is switched among three related currents. Shown in Figure 22, N1 × I and N2 × I are different multiples of the current I. The currents through the temperature diode are switched between I and N1 × I, resulting in  $\Delta V_{BE1}$ ; then

they are switched between I and N2 × I, resulting in  $\Delta V_{BE2}$ . The temperature can then be calculated using the two  $\Delta V_{BE}$  measurements. This method can also cancel the effect of series resistance on the temperature measurement.

The resulting  $\Delta V_{BE}$  waveforms are passed through a 65 kHz low-pass filter to remove noise and then sent to a chopper-stabilized amplifier that amplifies and rectifies the waveform to produce a dc voltage proportional to  $\Delta V_{BE}$ . The ADC digitizes this voltage, and a temperature measurement is produced. To reduce the effects of noise, digital filtering is performed by averaging the results of 16 measurement cycles.

The results of remote temperature measurements are stored in 10-bit twos complement format, as listed in Table 7. The extra resolution for the temperature measurements is held in the Extended Resolution Register 2 (0x77). This produces temperature readings with a resolution of  $0.25^{\circ}$ C.

#### **Series Resistance Cancellation**

Parasitic resistance to the ADT7467 D+ and D- inputs (seen in series with the remote diode) is caused by a variety of factors, including PCB track resistance and track length. This series resistance appears as a temperature offset in the remote sensor's temperature measurement. This error typically causes a 0.5°C offset per 1  $\Omega$  of parasitic resistance in series with the remote diode.

The ADT7467 automatically cancels the effect of this series resistance on the temperature reading, providing a more accurate result without the need for user characterization of this resistance. The ADT7467 is designed to automatically cancel, typically up to 3 k $\Omega$  of resistance. By using an advanced temperature measurement method, this is transparent to the user. This feature allows resistances to be added to the sensor path to produce a filter, allowing the part to be used in noisy environments. See the Noise Filtering section for details.

#### **Noise Filtering**

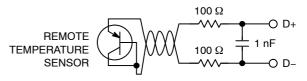

For temperature sensors operating in noisy environments, previous practice involved placing a capacitor across the D+ and D- pins to help combat the effects of noise. However, large capacitances affect the accuracy of the temperature measurement, leading to a recommended maximum capacitor value of 1,000 pF. A capacitor of this value reduces the noise but does not eliminate it, making use of the sensor difficult in a very noisy environment.

The ADT7467 has a major advantage over other devices for eliminating the effects of noise on the external sensor. Using the series resistance cancellation feature, a filter can be constructed between the external temperature sensor and the device. The effect of filter resistance seen in series with the remote sensor is automatically canceled from the temperature result.

The construction of a filter allows the ADT7467 and the remote temperature sensor to operate in noisy environments.

Figure 23 shows a low-pass R-C-R filter with the following values:

$$R = 100 \Omega, C = 1 nF$$

This filtering reduces both common-mode noise and differential noise.

Figure 23. Filter Between Remote Sensor and ADT7467

#### **Factors Affecting Diode Accuracy**

#### Remote Sensing Diode

The ADT7467 is designed to work with either substrate transistors built into processors or discrete transistors. Substrate transistors are generally PNP types with the collector connected to the substrate. Discrete types can be either PNP or NPN transistors connected as a diode (base-shorted to the collector). If an NPN transistor is used, the collector and base are connected to D+ and the emitter is connected to D–. If a PNP transistor is used, the collector and base are connected to D+ and the emitter base are connected to D+.

To reduce the error due to variations in both substrate and discrete transistors, a number of factors should be taken into consideration:

• The ideality factor, n<sub>f</sub>, of the transistor is a measure of the deviation of the thermal diode from ideal behavior. The ADT7467 is trimmed for an n<sub>f</sub> value of 1.008. Use the following equation to calculate the error introduced at a temperature, T (°C), when using a transistor whose n<sub>f</sub> does not equal 1.008. See the processor's data sheet for the n<sub>f</sub> values.

$\Delta T = (n_f - 1.008)/1.008 \times (273.15 \text{ K} + T)$

- To correct for this error, the user can write the  $\Delta T$  value to the offset register, and the ADT7467 automatically adds it to or subtracts it from the temperature measurement.

- Some CPU manufacturers specify the high and low current levels of the substrate transistors. The high current level of the ADT7467,  $I_{HIGH}$ , is 96  $\mu$ A, and the low level current,  $I_{LOW}$ , is 6  $\mu$ A. If the ADT7467 current levels do not match the current levels specified by the CPU manufacturer, it may be necessary to remove an offset. The CPU's data sheet should provide information relating to n<sub>f</sub> to compensate for differences. An offset can be programmed to the offset register. It is important to note that if more than one offsets must be considered, the algebraic sum of these offsets must be programmed to the offset register.

If a discrete transistor is used with the ADT7467, the best accuracy is obtained by choosing devices according to the following criteria:

- Base-emitter voltage is greater than 0.25 V at 6  $\mu$ A with the highest operating temperature.

- Base-emitter voltage is less than 0.95 V at  $100 \,\mu\text{A}$  with the lowest operating temperature.

- Base resistance is less than 100  $\Omega$ .

- There is a small variation in h<sub>FE</sub> (for example, 50 to 150) that indicates tight control of V<sub>BE</sub> characteristics.

Transistors such as 2N3904, 2N3906, or equivalents in SOT-23 packages are suitable devices to use.

# Table 7. TWOS COMPLEMENT TEMPERATURE DATA FORMAT

| Temperature | Digital Output (10-bit) (Note 1) |

|-------------|----------------------------------|

| –128°C      | 1000 0000 <b>00</b>              |

| –125°C      | 1000 0011 <b>00</b>              |

| -100°C      | 1001 1100 <b>00</b>              |

| –75°C       | 1011 0101 <b>00</b>              |

| –50°C       | 1100 1110 <b>00</b>              |

| –25°C       | 1110 0111 <b>00</b>              |

| -10°C       | 1111 0110 <b>00</b>              |

| 0°C         | 0000 0000 <b>00</b>              |

| +10.25°C    | 0000 1010 <b>01</b>              |

| +25.5°C     | 0001 1001 <b>10</b>              |

| +50.75°C    | 0011 0010 <b>11</b>              |

| +75°C       | 0100 1011 <b>00</b>              |

| +100°C      | 0110 0100 <b>00</b>              |

| +125°C      | 0111 1101 <b>00</b>              |

| +127°C      | 0111 1111 <b>00</b>              |

Bold numbers denote 2 LSBs of measurement in Extended Resolution Register 2 (0x77) with 0.25°C resolution.

| Temperature | Digital Output (10-bit) (Note 1) |

|-------------|----------------------------------|

| –64°C       | 0000 0000 <b>00</b>              |

| -1°C        | 0011 1111 <b>00</b>              |

| 0°C         | 0100 0000 <b>00</b>              |

| +1°C        | 0100 0001 <b>00</b>              |

| +10°C       | 0100 1010 <b>00</b>              |

| +25°C       | 0101 1001 <b>00</b>              |

| +50°C       | 0111 0010 <b>00</b>              |

| +75°C       | 1000 1001 <b>00</b>              |

| +100°C      | 1010 0100 <b>00</b>              |

| +125°C      | 1011 1101 <b>00</b>              |

| +191°C      | 1111 1111 <b>00</b>              |

1. Bold numbers denote 2 LSBs of measurement in Extended Resolution Register 2 (0x77) with 0.25°C resolution.

Figure 24. Measuring Temperature by Using an NPN Transistor

#### Figure 25. Measuring Temperature by Using a PNP Transistor

#### **Nulling Temperature Errors**

As CPUs run faster, it is more difficult to avoid high frequency clocks when routing the D+/D- traces around a system board. Even when recommended layout guidelines are followed, some temperature errors may still be attributed to noise coupled onto the D+/D- lines. Constant high frequency noise usually attenuates or increases temperature measurements by a linear, constant value.

The ADT7467 has temperature offset registers at Address 0x70 and Address 0x72 for the Remote 1 and Remote 2 temperature channels, respectively. By performing a one-time calibration of the system, the user can determine the offset caused by system board noise and null it using the offset registers. The offset registers automatically add an Offset 64/twos complement 8-bit reading to every temperature measurement. The LSBs add 0.5°C offset to the temperature reading; therefore, the 8-bit register effectively allows temperature offsets of up to  $\pm 64^{\circ}$ C with a resolution of 0.5°C. This ensures that the readings in the temperature measurement registers are as accurate as possible.

#### **Temperature Offset Registers**

Register 0x70 Remote 1 Temperature Iffset = 0x00(0°C Default)

Register 0x71 Local Temperature Offset = 0x00(0°C Default)

Register 0x72 Remote 2 Temperature Offset = 0x00(0°C Default)

#### ADT7460/ADT7467 Backwards-compatible Mode

By setting Bit 1 of Configuration Register 5 (0x7C), all temperature measurements are stored in the zone temperature value registers (Register 0x25, Register 0x26, and Register 0x27) in twos complement format in the range  $-128^{\circ}$ C to  $+127^{\circ}$ C. (The ADT7468 makes calculations based on the Offset 64 extended range and clamps the results if necessary.) The temperature limits must be reprogrammed in twos complement format. If a twos complement

temperature below  $-63^{\circ}$ C is entered, the temperature is clamped to  $-63^{\circ}$ C. In this mode, the diode fault condition remains  $-128^{\circ}$ C = 1000 0000, whereas the fault condition is represented by  $-64^{\circ}$ C = 0000 0000 in the extended temperature range ( $-64^{\circ}$ C to  $+191^{\circ}$ C).

# Table 9. TEMPERATURE MEASUREMENT REGISTERS

| Register | Description           | Default |

|----------|-----------------------|---------|

| 0x25     | Remote 1 Temperature  | 0x01    |

| 0x26     | Local Temperature     | 0x01    |

| 0x27     | Remote 2 Temperature  | 0x01    |

| 0x77     | Extended Resolution 2 | 0x00    |

#### Table 10. EXTENDED RESOLUTION TEMPERATURE MEASUREMENT REGISTER BITS

| Bit   | Mnemonic | Description               |

|-------|----------|---------------------------|

| <7:6> | TDM2     | Remote 2 Temperature LSBs |

| <5:4> | LTMP     | Local Temperature LSBs    |

| <3:2> | TDM1     | Remote 1 Temperature LSBs |

#### **Temperature Measurement Limit Registers**

High and low limit registers are associated with each temperature measurement channel. Exceeding the programmed high or low limit sets the appropriate status bit and can also generate **SMBALERT** interrupts.

# Table 11. TEMPERATURE MEASUREMENT LIMIT REGISTERS

| Register | Description                     | Default |

|----------|---------------------------------|---------|

| 0x4E     | Remote 1 Temperature Low Limit  | 0x01    |

| 0x4F     | Remote 1 Temperature High Limit | 0x7F    |

| 0x50     | Local Temperature Low Limit     | 0x01    |

| 0x51     | Local Temperature High Limit    | 0x7F    |

| 0x52     | Remote 2 Temperature Low Limit  | 0x01    |

| 0x53     | Remote 2 Temperature High Limit | 0x7F    |

#### **Reading Temperature from the ADT7467**

It is important to note that temperature can be read from the ADT7467 as an 8-bit value (with 1°C resolution) or as a 10-bit value (with 0.25°C resolution). If only 1°C resolution is required, the temperature readings can be read at any time and in no particular order.

If the 10-bit measurement is required, this involves a 2-register read for each measurement. The extended resolution register (0x77) should be read first. Then all temperature reading registers freeze until all temperature reading registers are read. This prevents updating of an MSB reading while its two LSBs are read and vice versa.

# Additional ADC Functions for Temperature Measurement

A number of other functions are available on the ADT7467 to offer the system designer increased flexibility.

#### Turn-off Averaging

For each temperature measurement read from a value register, 16 readings are made internally, the results of which are averaged and then placed into the value register. Sometimes it is necessary to perform a very fast measurement. Setting Bit 4 of Configuration Register 2 (0x73) turns averaging off.

| Table 12. CONVERSION TIME WITH AVERAGING |  |

|------------------------------------------|--|

| DISABLED                                 |  |

| Channel              | Measurement Time |

|----------------------|------------------|

| Voltage Channels     | 0.7 ms           |

| Remote Temperature 1 | 7 ms             |

| Remote Temperature 2 | 7 ms             |

| Local Temperature    | 1.3 ms           |

# Table 13. CONVERSION TIME WITH AVERAGING ENABLED

| Channel            | Measurement Time |

|--------------------|------------------|

| Voltage Channels   | 11 ms            |

| Remote Temperature | 39 ms            |

| Local Temperature  | 12 ms            |

#### Single-channel ADC Conversions

Setting Bit 6 of Configuration Register 2 (0x73) places the ADT7467 into single-channel ADC conversion mode. In this mode, users can read a single temperature channel only. The appropriate ADC channel is selected by writing to Bits <7:5> of the TACH1 minimum high byte register (0x55).

#### Table 14. CHANNEL SELECTION

| Bits <7:5>, Register 0x55 | Channel Selected     |

|---------------------------|----------------------|

| 101                       | Remote 1 Temperature |

| 110                       | Local Temperature    |

| 111                       | Remote 2 Temperature |

#### Configuration Register 2 (0x73)

<4> = 1, Averaging Off

<6> = 1, Single-channel Convert Mode

#### TACH1 Minimum High Byte (0x55)

<7:5> Selects ADC Channel for Single-channel Convert Mode

#### **Overtemperature Events**

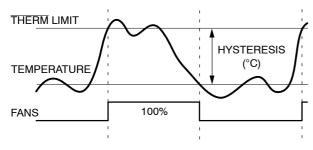

Overtemperature events on a temperature channel can be automatically detected and dealt with in automatic fan speed control mode. Register 0x6A to Register 0x6C contain the THERM temperature limits. When a temperature exceeds its THERM temperature limit, all PWM outputs run at the maximum PWM duty cycle (0x38, 0x39, 0x3A); therefore, fans run at the fastest speed allowed and continue running at this speed until the temperature drops below THERM minus hysteresis. (This can be disabled by setting the BOOST bit in Configuration Register 3, Bit 2, Register 0x78.) The hysteresis value for that THERM temperature limit is the value programmed into Register 0x6D and Register 0x6E (hysteresis registers). The default hysteresis value is 4°C.

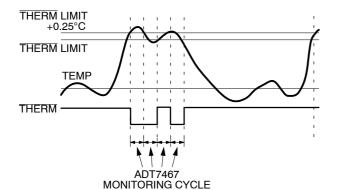

Figure 26. THERM Temperature Limit Operation

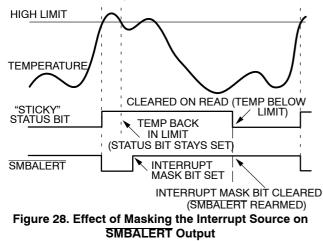

#### Limits, Status Registers, and Interrupts

#### **Limit Values**

High and low limits are associated with each measurement channel on the ADT7467. These limits form the basis of system-status monitoring in that a status bit can be set for any out-of-limit condition and detected by polling the device. Alternatively, SMBALERT interrupts can be generated to flag a processor or microcontroller of out-of-limit conditions.

#### 8-bit Limits

The following is a list of 8-bit limits on the ADT7467.

| Register | Description                 | Default |

|----------|-----------------------------|---------|

| 0x46     | V <sub>CCP</sub> Low Limit  | 0x00    |

| 0x47     | V <sub>CCP</sub> High Limit | 0xFF    |

| 0x48     | V <sub>CC</sub> Low Limit   | 0x00    |

| 0x49     | V <sub>CC</sub> High Limit  | 0xFF    |

#### Table 16. THERM TIMER LIMIT REGISTERS

| Register | Description       | Default |

|----------|-------------------|---------|

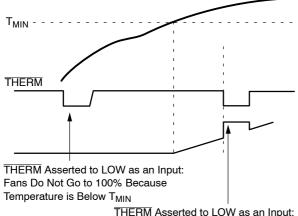

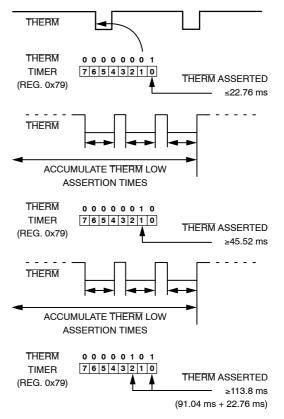

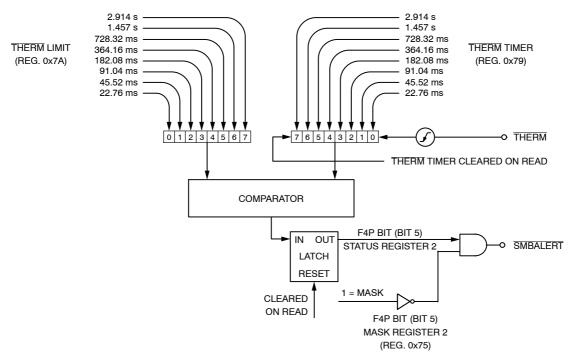

| 0x7A     | THERM Timer Limit | 0x00    |