# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **ANALOG DEVICES**

**FEATURES**

# MicroConverter<sup>®</sup>, Small Package 12-Bit ADC with Embedded Flash MCU

# ADuC814

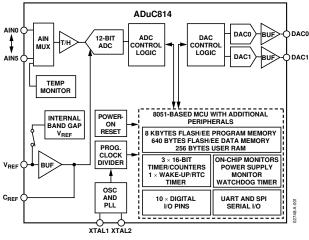

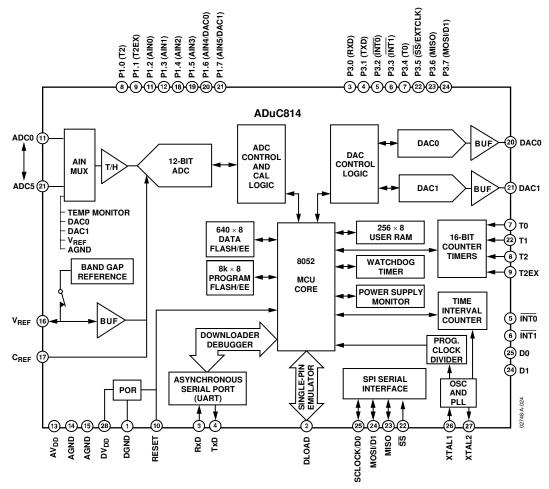

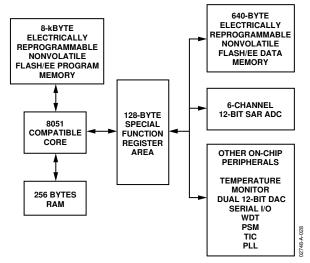

#### FUNCTIONAL BLOCK DIAGRAM

#### **APPLICATIONS**

Optical networking—laser power control Base station systems—power amplifier bias control Precision instruments, smart sensors Battery-powered systems, precision system monitors

#### Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

Figure 1.

#### **GENERAL DESCRIPTION**

The ADuC814 is a fully integrated 247 kSPS, 12-bit data acquisition system incorporating a high performance multichannel ADC, an 8-bit MCU, and program/data Flash/EE memory on a single chip.

This low power device operates from a 32 kHz crystal with an on-chip PLL generating a high frequency clock of 16.78 MHz. This clock is, in turn, routed through a programmable clock divider from which the MCU core clock operating frequency is generated.

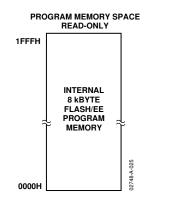

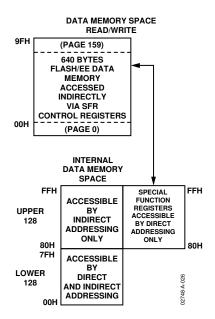

The microcontroller core is an 8052 and is compatible with an 8051 instruction. 8 kBytes of nonvolatile Flash/EE program memory are provided on-chip. 640 bytes of nonvolatile Flash/EE data memory and 256 bytes RAM are also integrated on-chip.

The ADuC814 also incorporates additional analog functionality with dual 12-bit DACs, a power supply monitor, and a band gap reference. On-chip digital peripherals include a watchdog timer, time interval counter, three timer/counters, and two serial I/O ports (SPI and UART).

On-chip factory firmware supports in-circuit serial download and debug modes (via UART), as well as single-pin emulation mode via the DLOAD pin. The ADuC814 is supported by a QuickStart<sup>™</sup> Development System.

The part operates from a single 3 V or 5 V supply over the extended temperature range  $-40^{\circ}$ C to  $+125^{\circ}$ C. When operating from 3 V supplies, the power dissipation for the part is below 10 mW. The ADuC814 is housed in a 28-lead TSSOP package.

# **ADUC814\* PRODUCT PAGE QUICK LINKS**

Last Content Update: 02/23/2017

### COMPARABLE PARTS

View a parametric search of comparable parts.

### EVALUATION KITS

ADuC814 QuickStart Development System

### **DOCUMENTATION**

#### **Application Notes**

- AN-1074: Understanding the Serial Download Protocol (Formerly uC004)

- AN-282: Fundamentals of Sampled Data Systems

- AN-660: XY-Matrix Keypad Interface to MicroConverter<sup>®</sup>

- AN-661: ADuC814 to ADM1032 via I<sup>2</sup>C<sup>®</sup> Interface

- AN-709: RTD Interfacing and Linearization Using an ADuC8xx MicroConverter<sup>®</sup>

- AN-759: Expanding the Number of DAC Outputs on the ADuC8xx and ADuC702x Families (uC012)

- UC-001: MicroConverter® I2C® Compatible Interface

- UC-006: A 4-wire UART-to-PC Interface

- UC-009: Addressing 16MB of External Data Memory

- UC-018: Uses of the Time Interval Counter

#### Data Sheet

- ADuC814: MicroConverter<sup>®</sup>, Small Package, 12-Bit ADC with Embedded Flash MCU Data Sheet

- ADuC814: Errata Sheet

#### **User Guides**

- ADuC814 Quick Reference Guide

- UG-041: ADuC8xx Evaluation Kit Getting Started User Guide

### REFERENCE MATERIALS

#### **Technical Articles**

· Integrated Route Taken to Pulse Oximetry

### DESIGN RESOURCES

- ADUC814 Material Declaration

- PCN-PDN Information

- Quality And Reliability

- Symbols and Footprints

### DISCUSSIONS

View all ADUC814 EngineerZone Discussions.

### SAMPLE AND BUY

Visit the product page to see pricing options.

### TECHNICAL SUPPORT

Submit a technical question or find your regional support number.

### DOCUMENT FEEDBACK

Submit feedback for this data sheet.

### **TABLE OF CONTENTS**

| Specifications                               |

|----------------------------------------------|

| Absolute Maximum Ratings                     |

| ESD Caution                                  |

| Pin Configuration and Function Description10 |

| Terminology12                                |

| ADC Specifications                           |

| DAC Specifications                           |

| Typical Performance Curves                   |

| ADuC814 Architecture, Main Features          |

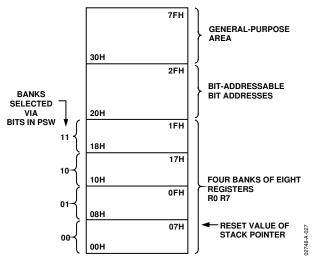

| Memory Organization17                        |

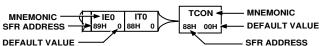

| Overview of MCU-Related SFRs18               |

| Accumulator SFR                              |

| B SFR                                        |

| Stack Pointer SFR 18                         |

| Data Pointer                                 |

| Program Status Word SFR18                    |

| Power Control SFR 19                         |

| Special Function Registers                   |

| ADC Circuit Information                      |

| General Overview                             |

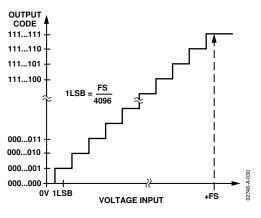

| ADC Transfer Function                        |

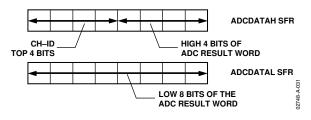

| ADC Data Output Format                       |

| SFR Interface to ADC Block                   |

| ADCCON1 (ADC Control SFR 1) 22               |

| ADCCON2 (ADC Control SFR 2)                  |

| ADCCON3 (ADC Control SFR 3)                  |

| Driving the ADC25                            |

| Voltage Reference Connections                |

| Configuring the ADC                          |

| Initiating ADC Conversions                   |

| ADC High Speed Data Capture Mode             |

| ADC Offset and Gain Calibration Overview            | 28 |

|-----------------------------------------------------|----|

| ADC Offset and Gain Calibration Coefficients        | 28 |

| Calibrating the ADC                                 | 29 |

| Initiating Calibration in Code                      | 29 |

| Nonvolitile Flash/EE Memory                         | 30 |

| Flash/EE Memory Overview                            | 30 |

| Flash/EE Memory and the ADuC814                     | 30 |

| ADuC814 Flash/EE Memory Reliability                 | 30 |

| Using Flash/EE Program Memory                       | 31 |

| Serial Downloading (In-Circuit Programming)         | 31 |

| Parallel Programming                                | 31 |

| Flash/EE Program Memory Security                    | 31 |

| Lock Mode                                           | 31 |

| Secure Mode                                         | 31 |

| Serial Safe Mode                                    | 31 |

| Using Flash/EE Data Memory                          | 32 |

| ECON—Flash/EE Memory Control SFR                    | 32 |

| Flash/EE Memory Timing                              | 33 |

| Using the Flash/EE Memory Interface                 | 33 |

| Programming a Byte                                  | 33 |

| User Interface to Other On-Chip ADuC814 Peripherals | 34 |

| DACs                                                | 34 |

| Using the DACs                                      | 35 |

| On-Chip PLL                                         | 37 |

| Time Interval Counter (TIC)                         | 38 |

| Watchdog Timer                                      | 41 |

| Power Supply Monitor                                | 42 |

| ADuC814 Configuration Register (CFG814)             | 43 |

| Serial Peripheral Interface                         | 43 |

| External Clock                                      | 43 |

|                                                     |    |

| Serial Peripheral Interface44                  |

|------------------------------------------------|

| MISO (Master In, Slave Out Data I/O Pin)44     |

| MOSI (Master Out, Slave In Pin)44              |

| SCLOCK (Serial Clock I/O Pin)44                |

| SS (Slave Select Input Pin)44                  |

| Using the SPI Interface45                      |

| SPI Interface—Master Mode45                    |

| SPI Interface—Slave Mode45                     |

| I <sup>2</sup> C Compatible Interface46        |

| 8051 Compatible On-Chip Peripherals47          |

| Parallel I/O Ports 1 and 347                   |

| Additional Digital Outputs Pins47              |

| Timers/Counters                                |

| Timer/Counter 0 and 1 Data Registers49         |

| Timer/Counter 0 and 1 Operating Modes50        |

| Mode 0 (13-Bit Timer/Counter)50                |

| Mode 1 (16-Bit Timer/Counter)50                |

| Mode 2 (8-Bit Timer/Counter with Autoreload)50 |

| Mode 3 (Two 8-Bit Timer/Counters)50            |

| Timer/Counter 2 Data Registers51               |

| Timer/Counter 2 Operating Modes                |

| 16-Bit Autoreload Mode52                       |

| 16-Bit Capture Mode52                          |

| UART Serial Interface53                        |

#### **REVISION HISTORY**

| 12/03 – Data Sheet Changed from REV. 0 to REV. A |        |

|--------------------------------------------------|--------|

| Added detailed description of productUni         | versal |

| Changes to Specifications                        | 4      |

| Updated Outline Dimensions                       | 70     |

| Changes to Ordering Guide                        | 71     |

| SBUF                                       | 53 |

|--------------------------------------------|----|

| Mode 0: 8-Bit Shift Register Mode          | 54 |

| Mode 1: 8-Bit UART, Variable Baud Rate     | 54 |

| Mode 2: 9-Bit UART with Fixed Baud Rate    | 55 |

| Mode 3: 9-Bit UART with Variable Baud Rate | 55 |

| UART Serial Port Baud Rate Generation      | 55 |

| Timer 2 Generated Baud Rates               | 56 |

| Interrupt System                           | 57 |

| Interrupt Priority                         | 59 |

| Interrupt Vectors                          | 59 |

| ADuC814 Hardware Design Considerations     | 60 |

| Clock Oscillator                           | 60 |

| Power Supplies                             | 60 |

| Power Consumption                          | 60 |

| Power-Saving Modes                         | 61 |

| Power-On Reset                             | 61 |

| Grounding and Board Layout Recommendations | 61 |

| Other Hardware Considerations              | 62 |

| In-Circuit Serial Download Access          | 62 |

| Embedded Serial Port Debugger              | 62 |

| Single-Pin Emulation Mode                  | 63 |

| Timing Specifications                      | 64 |

| Outline Dimensions                         | 70 |

| Ordering Guide                             | 71 |

## **SPECIFICATIONS**

Table 1.  $AV_{DD} = DV_{DD} = 2.7$  V to 3.3 V or 4.5 V to 5.5 V,  $V_{REF} = 2.5$  V internal reference, XTAL1/XTAL2 = 32.768 kHz crystal. All specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise specified<sup>1</sup>

| Parameter                                  | $V_{DD} = 5 V$        | $V_{DD} = 3 V$                 | Unit    | Test Conditions                        |

|--------------------------------------------|-----------------------|--------------------------------|---------|----------------------------------------|

| ADC CHANNEL SPECIFICATIONS                 |                       |                                |         |                                        |

| A GRADE                                    |                       |                                |         |                                        |

| DC ACCURACY <sup>2,3</sup>                 |                       |                                |         | f <sub>SAMPLE</sub> = 147 kHz          |

| Resolution                                 | 12                    | 12                             | Bits    |                                        |

| Integral Nonlinearity                      | 2                     | 2                              | LSB max | 2.5 V internal reference               |

|                                            | 1                     | 1                              | LSB typ |                                        |

|                                            | 2.5                   | 2.5                            | LSB typ | 1.0 V external reference               |

| Differential Nonlinearity                  | 4                     | 4                              | LSB max | 2.5 V internal reference               |

|                                            | 2                     | 2                              | LSB typ |                                        |

|                                            | 5                     | 5                              | LSB typ | 1.0 V external reference               |

| CALIBRATED ENDPOINT ERRORS <sup>4, 5</sup> |                       |                                |         |                                        |

| Offset Error                               | 5                     | 5                              | LSB max |                                        |

| Offset Error Match                         | 1                     | 1                              | LSB typ |                                        |

| Gain Error                                 | 5                     | 5                              | LSB max |                                        |

| Gain Error Match                           | 1                     | 1                              | LSB typ |                                        |

| DYNAMIC PERFORMANCE <sup>6</sup>           |                       |                                |         | $f_{IN} = 10 \text{ kHz}$ sine wave    |

|                                            |                       |                                |         | $f_{SAMPLE} = 147 \text{ kHz}$         |

| Signal to Noise Ratio (SNR) <sup>7</sup>   | 62.5                  | 62.5                           | dB typ  |                                        |

| Total Harmonic Distortion (THD)            | -65                   | -65                            | dB typ  |                                        |

| Peak Harmonic or Spurious Noise            | -65                   | -65                            | dB typ  |                                        |

| Channel-to-Channel Crosstalk <sup>8</sup>  | -80                   | -80                            | dB typ  |                                        |

| B GRADE                                    |                       |                                |         |                                        |

| DC ACCURACY <sup>2, 3</sup>                |                       |                                |         | f <sub>SAMPLE</sub> = 147 kHz          |

| Resolution                                 | 12                    | 12                             | Bits    |                                        |

| Integral Nonlinearity                      | 1                     | 1                              | LSB max | 2.5 V internal reference               |

|                                            | 0.3                   | 0.3                            | LSB typ |                                        |

|                                            | 1.5                   | 1.5                            | LSB max | 1.0 V external reference <sup>11</sup> |

| Differential Nonlinearity                  | 0.9                   | 0.9                            | LSB max | 2.5 V internal reference               |

|                                            | 0.25                  | 0.25                           | LSB typ |                                        |

|                                            | +1.5/-0.9             | 1.5/-0.9                       | LSB max | 1.0 V external reference <sup>11</sup> |

| Code Distribution                          | 1                     | 1                              | LSB typ | ADC input is a dc voltage              |

| CALIBRATED ENDPOINT ERRORS <sup>4, 5</sup> |                       |                                |         |                                        |

| Offset Error                               | 2                     | 3                              | LSB max |                                        |

| Offset Error Match                         | 1                     | 1                              | LSB typ |                                        |

| Gain Error                                 | 2                     | 3                              | LSB max |                                        |

| Gain Error Match                           | 1                     | 1                              | LSB typ |                                        |

| DYNAMIC PERFORMANCE <sup>6</sup>           |                       |                                |         | $f_{IN} = 10 \text{ kHz}$ sine wave    |

|                                            |                       |                                |         | $f_{SAMPLE} = 147 \text{ kHz}$         |

| Signal to Noise Ratio (SNR) <sup>7</sup>   | 71                    | 71                             | dB typ  |                                        |

| Total Harmonic Distortion (THD)            | -85                   | -85                            | dB typ  |                                        |

| Peak Harmonic or Spurious Noise            | -85                   | -85                            | dB typ  |                                        |

| Channel-to-Channel Crosstalk <sup>8</sup>  | -80                   | -80                            | dB typ  |                                        |

| ANALOG INPUT                               |                       |                                |         |                                        |

| Input Voltage Ranges                       | 0 to $V_{\text{REF}}$ | $0 \text{ to } V_{\text{REF}}$ | V       |                                        |

| Leakage Current                            | 1                     | 1                              | μA max  |                                        |

| Input Capacitance                          | 32                    | 32                             | pF typ  |                                        |

| Parameter                                             | $V_{DD} = 5 V$        | $V_{DD} = 3 V$  | Unit       | Test Conditions                                          |

|-------------------------------------------------------|-----------------------|-----------------|------------|----------------------------------------------------------|

| TEMPERATURE MONITOR <sup>9</sup>                      |                       |                 |            |                                                          |

| Voltage Output at 25°C                                | 650                   | 650             | mV typ     |                                                          |

| Voltage TC                                            | -2                    | -2              | mV/°C typ  |                                                          |

| Accuracy                                              | 3                     | 3               | °C typ     | 2.5 V internal reference                                 |

| Accuracy                                              | 1.5                   | 1.5             | °C typ     | 2.5 V external reference                                 |

| DAC CHANNEL SPECIFICATIONS                            |                       |                 | 0.00       | DAC Load to AGND RL = 10 k $\Omega$ , CL = 100 pF        |

| DC ACCURACY <sup>10</sup>                             |                       |                 |            |                                                          |

| Resolution                                            | 12                    | 12              | Bits       |                                                          |

| Relative Accuracy                                     | +3                    | +3              | LSB typ    |                                                          |

| Differential Nonlinearity <sup>11</sup>               | -1                    | -1              | LSB max    | Guaranteed montonic                                      |

| ,                                                     | 1/2                   | 1/2             | LSB typ    |                                                          |

| Offset Error                                          | 50                    | 50              | mV max     | V <sub>REF</sub> range                                   |

| Gain Error                                            | 1                     | 1               | % max      | V <sub>REF</sub> range                                   |

|                                                       | 1                     | 1               | % typ      | AV <sub>DD</sub> range                                   |

| Gain Error Mismatch                                   | 0.5                   | 0.5             | % typ      | Of full scale on DAC1                                    |

| ANALOG OUTPUTS                                        |                       |                 |            |                                                          |

| Voltage Range_0                                       | 0 to V <sub>REF</sub> |                 | Volts      | $DACV_{REF} = 2.5 V$                                     |

| Voltage Range_1                                       | 0 to V <sub>DD</sub>  |                 | Volts      | $DAC V_{REF} = V_{DD}$                                   |

| Output Impedance                                      | 0.5                   | 0.5             | Ωtyp       |                                                          |

| l <sub>sink</sub>                                     | 50                    | 50              | μA typ     |                                                          |

| DAC AC Specifications                                 |                       |                 | T: JF      |                                                          |

| Voltage Output Settling Time                          | 15                    | 15              | μs typ     | Full-scale settling time to within ½ LSB of final value  |

| Digital-to-Analog Glitch Energy                       | 10                    | 10              | nVs typ    | 1 LSB change at major carry                              |

| REFERENCE INPUT/OUTPUT                                |                       |                 |            |                                                          |

| REFERENCE OUTPUT                                      |                       |                 |            |                                                          |

| Output Voltage (V <sub>REF</sub> )                    | 2.5                   | 2.5             | V          |                                                          |

| Accuracy                                              | 2.5                   | 2.5             | % max      | Of V <sub>REF</sub> measured at the C <sub>REF</sub> pin |

| Power Supply Rejection                                | 47                    | 57              | dB typ     |                                                          |

| Reference Tempco                                      | 100                   | 100             | ppm/ºC typ |                                                          |

| Internal V <sub>REF</sub> Power-On Time <sup>12</sup> | 80                    | 80              | ms typ     |                                                          |

| EXTERNAL REFERENCE INPUT <sup>13</sup>                |                       |                 |            | Internal band gap reference deselected via<br>ADCCON2.6  |

| Voltage Range (V <sub>REF</sub> ) <sup>14</sup>       | 1.0                   | 1.0             | V min      |                                                          |

|                                                       | V <sub>DD</sub>       | V <sub>DD</sub> | V max      |                                                          |

| Input Impedance                                       | 20                    | 20              | kΩ typ     |                                                          |

| Input Leakage                                         | 10                    | 10              | μA max     |                                                          |

| POWER SUPPLY MONITOR (PSM)                            |                       |                 |            |                                                          |

| V <sub>DD</sub> Trip Point Selection Range            | 2.63                  | 2.63            | V          |                                                          |

|                                                       | 2.93                  | 2.93            | V          | Four trip points selectable in this range                |

|                                                       | 3.08                  | 3.08            | V          | programmed via TP1–0 in PSMCON                           |

|                                                       | 4.63                  |                 | V          |                                                          |

| V <sub>DD</sub> Power Supply Trip Point Accuracy      | 3.5                   | 3.5             | % max      |                                                          |

| WATCH DOG TIMER (WDT) <sup>14</sup>                   |                       |                 |            |                                                          |

| Timeout Period                                        | 0                     | 0               | ms min     | Nine time-out periods selectable in this range           |

|                                                       | 2000                  | 2000            | ms max     | programmed via PRE3–0 in WDCON                           |

| LOGIC INPUTS                                          |                       |                 |            |                                                          |

| INPUT VOLTAGES <sup>14</sup>                          |                       |                 |            |                                                          |

| All Inputs except SCLOCK, RESET, and<br>XTAL1         |                       |                 |            |                                                          |

| V <sub>INL</sub> , Input Low Voltage                  | 0.8                   | 0.4             | V max      |                                                          |

| V <sub>INH</sub> , Input High Voltage                 | 2.0                   | 2.0             | V min      |                                                          |

| Parameter                                        | $V_{DD} = 5 V$ | $V_{DD} = 3 V$ | Unit             | Test Conditions                                              |

|--------------------------------------------------|----------------|----------------|------------------|--------------------------------------------------------------|

| SCLOCK and RESET Only <sup>14</sup>              |                |                |                  |                                                              |

| (Schmitt-Triggered Inputs)                       |                |                |                  |                                                              |

| V <sub>T+</sub>                                  | 1.3            | 0.95           | V min            |                                                              |

|                                                  | 3.0            | 2.5            | V max            |                                                              |

| V <sub>T</sub> -                                 | 0.8            | 0.4            | V min            |                                                              |

|                                                  | 1.4            | 1.1            | V max            |                                                              |

| $V_{T+}-V_{T-}$                                  | 0.3            | 0.3            | V min            |                                                              |

|                                                  | 0.85           | 0.85           | V max            |                                                              |

| INPUT CURRENTS                                   |                |                |                  |                                                              |

| P1.2–P1.7, DLOAD                                 | ±10            | ±10            | μA max           | $V_{IN} = 0 V \text{ or } V_{DD}$                            |

| SCLOCK <sup>15</sup>                             | -10            | -3             | μA min           | $V_{IN} = 0 V$ , internal pull-up                            |

|                                                  | -40            | –15            | μA max           | $V_{IN} = 0 V$ , internal pull-up                            |

|                                                  | ±10            | ±10            | μA max           | $V_{IN} = V_{DD}$                                            |

| RESET                                            | ±10            | ±10            | μA max           | $V_{IN} = 0 V$                                               |

|                                                  | 20             | 10             | μA min           | $V_{IN} = 5 V$ , 3 V internal pull-down                      |

|                                                  | 105            | 35             | μA max           | $V_{IN} = 5 V$ , 3 V internal pull-down                      |

| P1.0, P1.1, Port 3 <sup>15</sup>                 | ±10            | ±10            | µA max           | V <sub>IN</sub> = 5 V, 3 V                                   |

| (includes MISO, MOSI/SDATA and $\overline{SS}$ ) | 1              | 1              | μA typ           |                                                              |

|                                                  | -180           | -70            | μA min           | $V_{IN} = 2 V, V_{DD} = 5 V, 3 V$                            |

|                                                  | -660           | -200           | μA max           |                                                              |

|                                                  | -360           | -100           | μA typ           |                                                              |

|                                                  | -20            | -5             | μA min           | $V_{IN} = 450 \text{ mV}, V_{DD} = 5 \text{ V}, 3 \text{ V}$ |

|                                                  | -75            | -25            | μA max           |                                                              |

|                                                  | -38            | -12            | μA typ           |                                                              |

| NPUT CAPACITANCE                                 | 5              | 5              | pF typ           | All digital inputs                                           |

| CRYSTAL OSCILLATOR<br>(XTAL1 AND XTAL2)          |                |                | T 7F             |                                                              |

| Logic Inputs, XTAL1 Only                         |                |                |                  |                                                              |

| V <sub>INL</sub> , Input Low Voltage             | 0.8            | 0.4            | V typ            |                                                              |

| V <sub>INH</sub> , Input High Voltage            | 3.5            | 2.5            | V typ            |                                                              |

| XTAL1 Input Capacitance                          | 18             | 18             | pF typ           |                                                              |

| XTAL2 Output Capacitance                         | 18             | 18             | pF typ           |                                                              |

| DIGITAL OUTPUTS                                  |                |                | P. 9P            |                                                              |

| Output High Voltage (Vон)                        | 2.4            | 2.4            | V min            | I <sub>SOURCE</sub> = 80 mA                                  |

| Output Low Voltage (VOR)                         |                |                |                  | Source of the                                                |

| Port 1.0 and Port 1.1                            | 0.4            | 0.4            | V max            | I <sub>SINK</sub> = 10 mA, T <sub>MAX</sub> = 85°C           |

| Port 1.0 and Port 1.1                            | 0.4            | 0.4            | V max            | $I_{SINK} = 10 \text{ mA}, T_{MAX} = 0.5 \text{ C}$          |

| SCLOCK, MISO/MOSI                                | 0.4            | 0.4            | V max            | $I_{SINK} = 4 \text{ mA}$                                    |

| All Other Outputs                                | 0.4            | 0.4            | V max            | $I_{SINK} = 1.6 \text{ mA}$                                  |

| MCU CORE CLOCK                                   | 0.1            |                | VIIIGA           |                                                              |

| MCU Clock Rate                                   | 131.1          | 131.1          | kHz min          | Clock rate generated via on-chip PLL,                        |

| MCO CIOCK NALE                                   | 1.1.1          | 1.1.1          |                  | programmable via CD2-0 in PLLCON                             |

|                                                  | 16.78          | 16.78          | MHz max          |                                                              |

| START UP TIME                                    |                |                |                  |                                                              |

| At Power-On                                      | 500            | 500            | ms typ           |                                                              |

| From Idle Mode                                   | 100            | 100            | μs typ           |                                                              |

| From Power-Down Mode                             |                |                | F7 F             |                                                              |

| Oscillator Running                               |                |                |                  | OSC_PD = 0 in PLLCON SFR                                     |

| Wake-Up with INTO Interrupt                      | 100            | 100            | μs typ           |                                                              |

| Wake-Up with SPI/I <sup>2</sup> C Interrupt      | 100            | 100            |                  |                                                              |

| Wake-Up with TIC Interrupt                       | 100            | 100            | μs typ           |                                                              |

| Wake-Up with External RESET                      | 3              | 3              | μs typ<br>ms typ |                                                              |

| wake-up with external Reser                      | 3              | 2              | ms typ           |                                                              |

| Parameter                                   | $V_{DD} = 5 V$ | $V_{DD} = 3 V$ | Unit             | Test Conditions                                                      |

|---------------------------------------------|----------------|----------------|------------------|----------------------------------------------------------------------|

| Oscillator Powered Down <sup>16</sup>       |                |                |                  | OSC_PD = 1 in PLLCON SFR                                             |

| Wake-Up with INTO Interrupt                 | 150            | 400            | ms typ           |                                                                      |

| Wake-Up with SPI/I <sup>2</sup> C Interrupt | 150            | 400            | ms typ           |                                                                      |

| Wake-Up with External RESET                 | 150            | 400            | ms typ           |                                                                      |

| After External RESET in Normal Mode         | 3              | 3              | ms typ           |                                                                      |

| After WDT Reset in Normal Mode              | 3              | 3              | ms typ           | Controlled via WDCON SFR                                             |

| ELASH/EE MEMORY RELIABILITY                 |                |                |                  |                                                                      |

| Endurance <sup>18</sup>                     | 100,000        | 100,000        | Cycles min       |                                                                      |

| Data Retention <sup>19</sup>                | 100            | 100            | Years min        |                                                                      |

| POWER REQUIREMENTS <sup>20, 21</sup>        |                |                |                  |                                                                      |

| Power Supply Voltages                       |                |                |                  |                                                                      |

| $AV_{DD}/DV_{DD} - AGND$                    |                | 2.7            | V min            | $AV_{DD}/DV_{DD} = 3 V nom$                                          |

|                                             |                | 3.3            | V max            |                                                                      |

|                                             | 4.5            | 2.5            | Vmin             | $AV_{DD}/DV_{DD} = 5 V nom$                                          |

|                                             | 5.5            |                | V max            |                                                                      |

| Power Supply Currents, Normal Mode          | 5.5            |                | VIIIdx           |                                                                      |

| D <sub>VDD</sub> Current <sup>14</sup>      | 5              | 2.5            | mA max           | Core CLK = 2.097 MHz                                                 |

| Dwbb Current                                | 4              | 2.5            | mA typ           | (CD bits in PLLCON = 3)                                              |

| Avdd Current <sup>14</sup>                  | 1.7            | 1.7            | mA typ<br>mA max | (CD DIts III FEECON = 3)                                             |

|                                             |                | -              | -                | Core (IK - 16.79 MHz (max))                                          |

| D <sub>VDD</sub> Current                    | 20             | 10             | mA max           | Core CLK = 16.78MHz (max)                                            |

| A Comment                                   | 16             | 8              | mA typ           | (CD bits in PLLCON = 0)                                              |

| Avdd Current                                | 1.7            | 1.7            | mA max           |                                                                      |

| D <sub>VDD</sub> Current <sup>14</sup>      | 3.5            | 1.5            | mA max           | Core CLK = $131.2$ kHz (min)                                         |

|                                             | 2.8            | 1.2            | mA typ           | (CD bits in PLLCON $=$ 7)                                            |

| Avdd Current                                | 1.7            | 1.7            | mA max           |                                                                      |

| Power Supply Currents, Idle Mode            |                |                |                  |                                                                      |

| D <sub>VDD</sub> Current <sup>14</sup>      | 1.7            | 1.2            | mA max           | Core CLK = 2.097 MHz                                                 |

|                                             | 1.5            | 1              | mA typ           | (CD Bits in PLLCON $=$ 3)                                            |

| AV <sub>DD</sub> Current <sup>14</sup>      | 0.15           | 0.15           | mA max           |                                                                      |

| DV <sub>DD</sub> Current <sup>14</sup>      | 6              | 3              | mA max           | Core CLK = 16.78 MHz (max)                                           |

|                                             | 4              | 2.5            | mA typ           | (CD bits in PLLCON $= 0$ )                                           |

| AV <sub>DD</sub> Current <sup>14</sup>      | 0.15           | 0.15           | mA max           |                                                                      |

| DV <sub>DD</sub> Current <sup>14</sup>      | 1.25           | 1              | mA max           | Core CLK = 131 kHz (min)                                             |

|                                             | 1.1            | 0.7            | mA typ           | (CD bits in PLLCON $=$ 7)                                            |

| AV <sub>DD</sub> Current <sup>14</sup>      | 0.15           | 0.15           | mA max           |                                                                      |

| Power Supply Currents, Power-Down<br>Mode   |                |                |                  | Core CLK = 2.097 MHz or 16.78 MHz (CD bits<br>PLLCON = 3 or 0)       |

| DV <sub>DD</sub> Current <sup>14</sup>      | 1              | 20             | μA max           | Oscillator on                                                        |

|                                             | 40             | 14             | μA typ           |                                                                      |

| AV <sub>DD</sub> Current                    | 1              | 1              | μA typ           |                                                                      |

| DV <sub>DD</sub> Current                    | 1              | 15             | μA max           | Oscillator off                                                       |

|                                             | 20             | 10             | μA typ           |                                                                      |

| AV <sub>DD</sub> Current                    | 1              | 1              | μA typ           |                                                                      |

| Typical Additional Power Supply<br>Currents |                |                |                  | Core CLK = 2.097 MHz, (CD bits in PLLCON = $AV_{DD} = DV_{DD} = 5 V$ |

| PSM Peripheral                              | 50             |                | μA typ           |                                                                      |

| ADC                                         | 1.5            |                | mA typ           |                                                                      |

| DAC                                         | 150            |                | μA typ           |                                                                      |

<sup>1</sup>Temperature range –40°C to +125°C.

<sup>2</sup>ADC linearity is guaranteed when operating in nonpipelined mode, i.e., ADC conversion followed sequentially by a read of the ADC result. ADC linearity is also guaranteed during normal MicroConverter core operation.

<sup>3</sup>ADC LSB size =  $V_{REF}$  /2<sup>12</sup>, i.e., for internal  $V_{REF}$  = 2.5 V, 1 LSB = 610  $\mu$ V, and for external  $V_{REF}$  = 1 V, 1 LSB = 244  $\mu$ V.

<sup>4</sup>Offset and gain error and offset and gain error match are measured after factory calibration.

<sup>5</sup>Based on external ADC system components the user may need to execute a system calibration to remove additional external channel errors

and achieve these specifications.

<sup>6</sup>Measured with coherent sampling system using external 16.77 MHz clock via P3.5 (Pin 22).

<sup>7</sup>SNR calculation includes distortion and noise components.

<sup>8</sup>Channel-to-channel crosstalk is measured on adjacent channels.

$^{

m ?}$ The temperature monitor gives a measure of the die temperature directly; air temperature can be inferred from this result.

<sup>10</sup>DAC linearity is calculated using a reduced code range of 48 to 4095, 0 V to V<sub>REF</sub> range; a reduced code range of 48 to 3950, 0 V to V<sub>DD</sub> range. DAC output load = 10 kΩ and 100 pF.

$^{11}\text{DAC}$  differential nonlinearity specified on 0 V to  $V_{\text{REF}}$  and 0 to  $V_{\text{DD}}$  ranges.

<sup>12</sup>Measured with V<sub>REF</sub> and C<sub>REF</sub> pins decoupled with 0.1 µF capacitors to ground. Power-up time for the internal reference is determined by the value of the decoupling capacitor chosen for both the V<sub>REF</sub> and C<sub>REF</sub> pins.

<sup>13</sup>When using an external reference device, the internal band gap reference input can be bypassed by setting the ADCCON1.6 bit. In this mode, the V<sub>REF</sub> and C<sub>REF</sub> pins need to be shorted together for correct operation.

<sup>14</sup>These numbers are not production tested but are guaranteed by design and/or characterization data on production release.

<sup>15</sup>Pins configured in I<sup>2</sup>C compatible mode or SPI mode; pins configured as digital inputs during this test.

<sup>16</sup>These typical specifications assume no loading on the XTAL2 pin. Any additional loading on the XTAL2 pin increases the power-on times.

<sup>17</sup>Flash/EE memory reliability characteristics apply to both the Flash/EE program memory and the Flash/EE data memory.

<sup>18</sup>Endurance is qualified to 100 kcycles as per JEDEC Std. 22, Method A117 and measured at –40°C, +25°C, and +125°C; typical endurance at +25°C is 700 kcycles.

<sup>19</sup>Retention lifetime equivalent at junction temperature (T<sub>J</sub>) = 55°C as per JEDEC Std. 22, Method A117. Retention lifetime based on an activation energy of 0.6 eV derates with junction temperature as shown in Figure 33 in the Flash/EE memory description section.

<sup>20</sup>Power supply current consumption is measured in normal, idle, and power-down modes under the following conditions:

Normal Mode: Reset and all digital I/O pins = open circuit, core Clk changed via CD bits in PLLCON, core executing internal software loop.

Idle Mode: Reset and all digital I/O pins = open circuit, core Clk changed via CD bits in PLLCON, PCON.0 = 1, core execution suspended in idle mode. Power-Down Mode: Reset and all P1.2–P1.7 pins = 0.4 V; all other digital I/O pins are open circuit, Core Clk changed via CD bits in PLLCON, PCON.1 = 1,

Core execution suspended in power-down mode, OSC turned on or off via OSC\_PD bit (PLLCON.7) in PLLCON SFR.

<sup>21</sup>DV<sub>DD</sub> power supply current increases typically by 3 mA (3 V operation) and 10 mA (5 V operation) during a Flash/EE memory program or erase cycle.

### **ABSOLUTE MAXIMUM RATINGS**

Table 2. Temperature = 25°C, unless otherwise noted

| 1 wolt 20 1 timp that all 20 0, and 50                  | 00000                              |

|---------------------------------------------------------|------------------------------------|

| Parameter                                               | Rating                             |

| AV <sub>DD</sub> to AGND                                | –0.3 V to +7 V                     |

| DV <sub>DD</sub> to AGND                                | –0.3 V to +7 V                     |

| AV <sub>DD</sub> to DV <sub>DD</sub>                    | –0.3 V to +0.3 V                   |

| AGND to DGND <sup>1</sup>                               | –0.3 V to +0.3 V                   |

| Analog Input Voltage to AGND <sup>2</sup>               | -0.3 V to AV <sub>DD</sub> + 0.3 V |

| Reference Input Voltage to AGND                         | -0.3 V to AV <sub>DD</sub> + 0.3 V |

| Analog Input Current (Indefinite)                       | 30 mA                              |

| Reference Input Current (Indefinite)                    | 30 mA                              |

| Digital Input Voltage to DGND                           | -0.3 V to DV <sub>DD</sub> + 0.3 V |

| Digital Output Voltage to DGND                          | -0.3 V to DV <sub>DD</sub> + 0.3 V |

| Operating Temperature Range                             | -40°C to +125°C                    |

| Storage Temperature Range                               | -65°C to +150°C                    |

| Junction Temperature                                    | 150°C                              |

| θ <sub>JA</sub> Thermal Impedance                       | 97.9°C/W                           |

| Lead Temperature, Soldering                             |                                    |

| Vapor Phase (60 sec)                                    | 215°C                              |

| Infrared (15 sec)                                       | 220°C                              |

| <sup>1</sup> AGND and DGND are shorted internally on th |                                    |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

<sup>2</sup> Applies to Pins P1.2 to P1.7 operating in analog or digital input mode.

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

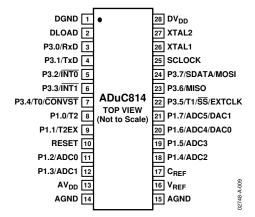

### **PIN CONFIGURATION AND FUNCTION DESCRIPTION**

Figure 2. Pin Configuration

#### Table 3. Pin Descriptions

| Pin No. | Mnemonic           | Туре | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------|--------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | DGND               | S    | Digital Ground. Ground reference point for the digital circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2       | DLOAD              | I    | Debug/Serial Download Mode. Enables when pulled high through a resistor on power-on or RESET. I this mode, DLOAD may also be used as an external emulation I/O pin, therefore the voltage level at this pin must not be changed during this mode of operation because it may cause an emulation interrupt that halts code execution. User code is executed when this pin is pulled low on power-on o RESET.                                                                                                        |

| 3–7     | P3.0 – P3.4        | I/O  | Bidirectional Port Pins with Internal Pull-Up Resistors. Port 3 pins that have 1s written to them are pulled high by the internal pull-up resistors, and in that state they can be used as inputs. As inputs, with Port 3 pins being pulled low externally, they source current because of the internal pull-up resistors. When driving a 0-to-1 output transition, a strong pull-up is active during S1 of the instruction cycle. Port 3 pins also have various secondary functions which are described next.     |

| 3       | P3.0/RxD           | I/O  | Receiver Data Input (asynchronous) or Data Input/Output (synchronous) in Serial (UART) Mode.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4       | P3.1/TxD           | I/O  | Transmitter Data Output (asynchronous) or Clock Output (synchronous) in Serial (UART) Mode.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5       | P3.2/INT0          | I/O  | Interrupt 0, programmable edge or level-triggered interrupt input, which can be programmed to one of two priority levels. This pin can also be used as agate control input to Timer 0.                                                                                                                                                                                                                                                                                                                             |

| 6       | P3.3/INT1          | I/O  | Interrupt 1, programmable edge or level-triggered interrupt input, which can be programmed to one of two priority levels. This pin can also be used as agate control input to Timer 1.                                                                                                                                                                                                                                                                                                                             |

| 7       | P3.4/T0/<br>CONVST | I/O  | Timer/Counter 0 Input and External Trigger Input for ADC Conversion Start.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 8–9     | P1.0-P1.1          | I/O  | Bidirectional Port Pins with Internal Pull-Up Resistors. Port 1 pins that have 1s written to them are pulled high by the internal pull-up resistors, and in that state they can be used as inputs. As inputs ,with Port 1 pins being pulled low externally, they source current because of the internal pull-up resistors When driving a 0-to-1 output transition a strong pull-up is active during S1 of the instruction cycle. Port 1 pins also have various secondary functions which are described as follows. |

| 8       | P1.0/T2            | I/O  | Timer 2 Digital Input. Input to Timer/Counter 2. When enabled, Counter 2 is incremented in response to a 1 to 0 transition of the T2 input.                                                                                                                                                                                                                                                                                                                                                                        |

| 9       | P1.1/T2EX          | I/O  | Digital Input. Capture/Reload trigger for Counter 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 10      | RESET              | I    | Reset Input. A high level on this pin while the oscillator is running resets the device. There is an internal weak pull-down and a Schmitt-trigger input stage on this pin.                                                                                                                                                                                                                                                                                                                                        |

| 11–12   | P1.2–P1.3          | I    | Port 1.2 to P1.3. These pins have no digital output drivers, i.e., they can only function as digital inputs for which 0 must be written to the port bit. These port pins also have the following analog functionality                                                                                                                                                                                                                                                                                              |

| 11      | P1.2/ADC0          | 1    | ADC Input Channel 0. Selected via ADCCON2 SFR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 12      | P1.3/ADC1          | 1    | ADC Input Channel 1. Selected via ADCCON2 SFR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 13      | AV <sub>DD</sub>   | S    | Analog Positive Supply Voltage, 3 V or 5 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 14–15   | AGND               | G    | Analog Ground. Ground reference point for the analog circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 16      | V <sub>REF</sub>   | I/O  | Reference Input/Output. This pin is connected to the internal reference through a switch and is the reference source for the analog to digital converter. The nominal internal reference voltage is 2.5 V and this appears at the pin. This pin can be used to connect an external reference to the analog to digital converter by setting ADCCON1.6 to 1. Connect 0.1 $\mu$ F between this pin and AGND.                                                                                                          |

| Pin No. | Mnemonic            | Туре | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|---------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17      | CREF                | 1    | Decoupling Input for On-Chip Reference. Connect 0.1 µF between this pin and AGND.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 18–21   | P1.4–P1.7           | 1    | Port 1.4 to P1.7. These pins have no digital output drivers, i.e., they can only function as digital inputs, for which 0 must be written to the port bit. These port pins also have the following analog functionality:                                                                                                                                                                                                                                                                                             |

| 18      | P1.4/ADC2           | I    | ADC Input Channel 2. Selected via ADCCON2 SFR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 19      | P1.5/ADC3           | 1    | ADC Input Channel 2. Selected via ADCCON2 SFR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 20      | P1.6/ADC4/<br>DAC0  | I/O  | ADC Input Channel 4. Selected via ADCCON2 SFR. The voltage DAC Channel 0 can also be configured to appear on P1.6.                                                                                                                                                                                                                                                                                                                                                                                                  |

| 21      | P1.7/<br>ADC5/DAC1  | I/O  | ADC Input Channel 5, selected via ADCCON2 SFR. The voltage DAC Channel 1 can also be configured to appear on P1.7.                                                                                                                                                                                                                                                                                                                                                                                                  |

| 22–24   | P3.5-P3.7           | 1/0  | Bidirectional Port Pins with Internal Pull-Up Resistors. Port 3 pins that have 1s written to them are pulled high by the internal pull-up resistors, and in that state they can be used as inputs. As inputs ,with Port 3 pins being pulled low externally, they source current because of the internal pull-up resistors. When driving a 0-to-1 output transition a strong pull-up is active during S1 of the instruction cycle. Port 3 pins also have various secondary functions which are described as follows. |

| 22      | P3.5/T1             |      | I/O Timer/Counter 1 Input. P3.5–P3.7 pins also have SPI interface functions. To enable these functions, Bit 0 of the CFG814 SFR must be set to 1.                                                                                                                                                                                                                                                                                                                                                                   |

| 22      | P3.5/SS<br>/EXTCLK  | I/O  | This pin also functions as the Slave Select input for the SPI interface when the device is operated in slave mode. P3.5 can also function as an input for an external clock. This clock effectively bypasses the PLL. This function is enabled by setting Bit 1 of the CFG814 SFR.                                                                                                                                                                                                                                  |

| 23      | P3.6/MISO           | I/O  | SPI Master Input/Slave Output Data Input/Output Pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 24      | P3.7/SDATA/<br>MOSI | I/O  | SPI Master Output/Slave Input Data Input/Output Pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 25      | SCLOCK              | I/O  | Serial Clock Pin for SPI Serial Interface Clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 26      | XTAL1               | I    | Input to the Crystal Oscillator Inverter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 27      | XTAL2               | 0    | Output from the Crystal Oscillator Inverter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 28      | DVDD                | S    | Analog Positive Supply Voltage, 3 V or 5 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

I = Input, O = Output, S = Supply, G - Ground.

The following notes apply to the entire data sheet:

- In bit designation tables, *set* implies a Logic 1 state, and *cleared* implies a Logic 0 state, unless otherwise stated.

- *Set* and *cleared* also imply that the bit is set or cleared by the ADuC814 hardware, unless otherwise stated.

- User software should not write to reserved or unimplemented bits as they may be used in future products.

### TERMINOLOGY ADC SPECIFICATIONS

#### **Integral Nonlinearity**

This is the maximum deviation of any code from a straight line passing through the endpoints of the ADC transfer function. The endpoints of the transfer function are zero scale, a point1/2 LSB below the first code transition and full scale, a point 1/2 LSB above the last code transition.

#### **Differential Nonlinearity**

This is the difference between the measured and the ideal 1 LSB change between any two adjacent codes in the ADC.

#### **Offset Error**

This is the deviation of the first code transition (0000 ... 000) to (0000 ... 001) from the ideal, i.e., +1/2 LSB.

#### **Full-Scale Error**

This is the deviation of the last code transition from the ideal AIN voltage (full-scale error has been adjusted out).

#### Signal-to-(Noise + Distortion) Ratio

This is the measured ratio of signal-to-(noise + distortion) at the output of the ADC. The signal is the rms amplitude of the fundamental. Noise is the rms sum of all nonfundamental signals up to half the sampling frequency ( $f_s/2$ ), excluding dc. The ratio is dependent upon the number of quantization levels in the digitization process; the more levels, the smaller the quantization noise. The theoretical signal-to-(noise + distortion) ratio for an ideal N-bit converter with a sine wave input is given by

Signal-to = -(Noise + Distortion) = (6.02N + 1.76)

Thus, for a 12-bit converter, this is 74 dB.

#### **Total Harmonic Distortion (THD)**

Total harmonic distortion is the ratio of the rms sum of the harmonics to the fundamental.

#### Peak Harmonic or Spurious Noise

Peak harmonic or spurious noise is defined as the ratio of the rms value of the next largest component in the ADC output spectrum (up to  $f_s/2$  and including dc) to the rms value of the fundamental. Normally, the value of this specification is determined by the largest harmonic in the spectrum, but for ADCs where the harmonics are buried in the noise floor, it is the noise peak.

#### **DAC SPECIFICATIONS**

#### **Relative Accuracy**

Relative accuracy or endpoint linearity is a measure of the maximum deviation from a straight line passing through the endpoints of the DAC transfer function. It is measured after adjusting for zero-scale error and full-scale error.

#### Voltage Output Settling Time

This is the amount of time it takes for the output to settle to a specified level for a full-scale input change.

#### Digital-to-Analog Glitch Impulse

This is the amount of charge injected into the analog output when the inputs change state. It is specified as the area of the glitch in nV-sec.

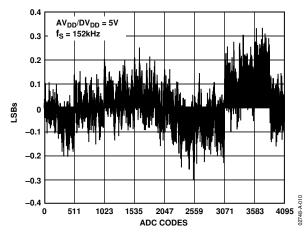

### **TYPICAL PERFORMANCE CURVES**

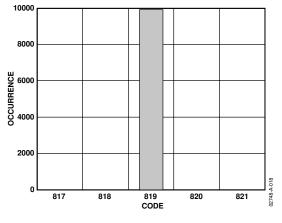

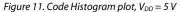

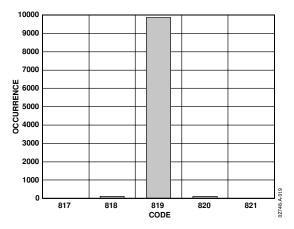

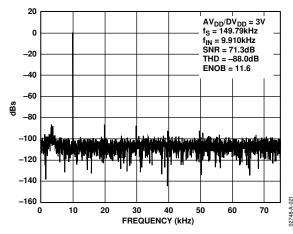

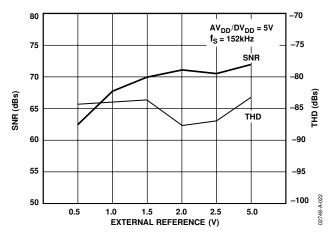

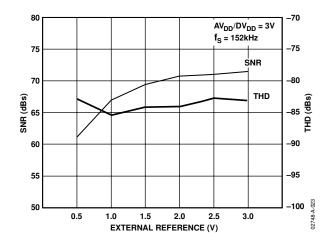

The typical performance plots presented in this section illustrate typical performance of the ADuC814 under various operating conditions. Note that all typical plots in this section were generated using the ADuC814BRU, i.e., the B-grade part.

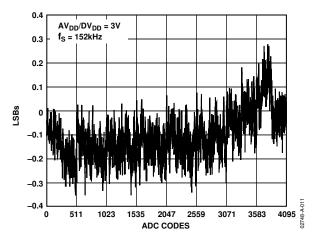

Figure 3 and Figure 4 show typical ADC integral nonlinearity (INL) errors from ADC Code 0 to Code 4095 at 5 V and 3 V supplies, respectively. The ADC is using its internal reference (2.5 V) and operating at a sampling rate of 152 kHz. The typical worst-case errors in both plots are just less than 0.3 LSBs.

Figure 3. Typical INL Error,  $V_{DD} = 5 V$

Figure 4. Typical INL Error,  $V_{DD} = 3 V$

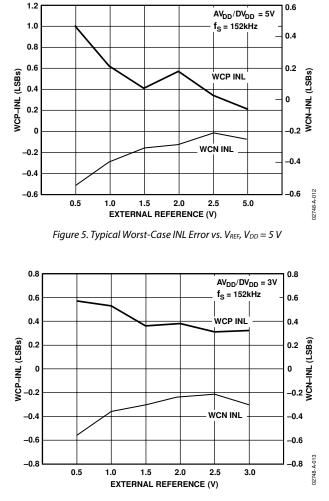

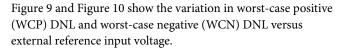

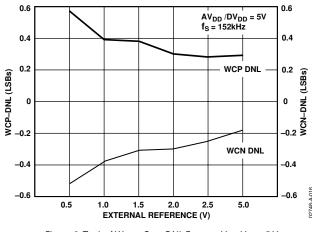

Figure 5 and Figure 6 show the variation in worst-case positive (WCP) INL and worst-case negative (WCN) INL versus external reference input voltage.

Figure 6. Typical Worst-Case INL Error vs.  $V_{REF}$ ,  $V_{DD} = 3 V$

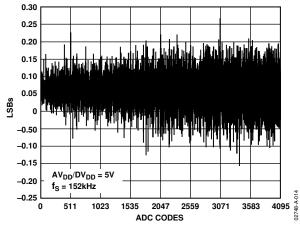

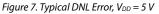

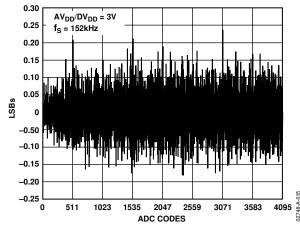

Figure 7 and Figure 8 show typical ADC differential nonlinearity (DNL) errors from ADC Code 0 to Code 4095 at 5 V and 3 V supplies, respectively. The ADC is using its internal reference (2.5 V) and operating at a sampling rate of 152 kHz. The typical worst-case errors in both plots are just less than 0.2 LSBs.

Figure 8. Typical DNL Error,  $V_{DD} = 3 V$