# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# ANALOG DEVICES

# MicroConverter 12-Bit ADCs and DACs with Embedded High Speed 62 kB Flash MCU

#### **Data Sheet**

# ADuC841/ADuC842/ADuC843

#### **FEATURES**

| LATORES                                            |

|----------------------------------------------------|

| Pin compatible upgrade of ADuC812/ADuC831/ADuC832  |

| Increased performance                              |

| Single-cycle 20 MIPS 8052 core                     |

| High speed 420 kSPS 12-bit ADC                     |

| Increased memory                                   |

| Up to 62 kBytes on-chip Flash/EE program memory    |

| 4 kBytes on-chip Flash/EE data memory              |

| In-circuit reprogrammable                          |

| Flash/EE, 100 year retention, 100 kCycle endurance |

| 2304 bytes on-chip data RAM                        |

| Smaller package                                    |

| 8 mm × 8 mm chip scale package                     |

| 52-lead PQFP—pin-compatible upgrade                |

| Analog I/O                                         |

| 8-channel, 420 kSPS high accuracy, 12-bit ADC      |

| On-chip, 15 ppm/°C voltage reference               |

| DMA controller, high speed ADC-to-RAM capture      |

| Two 12-bit voltage output DACs <sup>1</sup>        |

| Dual output PWM Σ-Δ DACs                           |

| On-chip temperature monitor function               |

| 8052 based core                                    |

| 8051 compatible instruction set (20 MHz max)       |

| High performance single-cycle core                 |

| 32 kHz external crystal, on-chip programmable PLL  |

| 12 interrupt sources, 2 priority levels            |

| Dual data pointers, extended 11-bit stack pointer  |

| On-chip peripherals                                |

| Time interval counter (TIC)                        |

| UART, I <sup>2</sup> C°, and SPI° Serial I/O       |

| Watchdog timer (WDT)                               |

| Power supply monitor (PSM)                         |

| Power                                              |

| Normal: 4.5 mA @ 3 V (core CLK = 2.098 MHz)        |

| Power-down: 10 μA @ 3 V²                           |

| Development tools                                  |

| Low cost, comprehensive development system         |

| incorporating nonintrusive single-pin emulation,   |

| IDE based assembly and C source debugging          |

| APPLICATIONS                                       |

|                                                    |

Optical networking—laser power control Base station systems Precision instrumentation, smart sensors Transient capture systems DAS and communications systems

<sup>1</sup> ADuC841/ADuC842 only. <sup>2</sup> ADuC842/ADuC843 only, ADuC841 driven directly by external crystal. Rev. A Document Fe

Rev. A Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

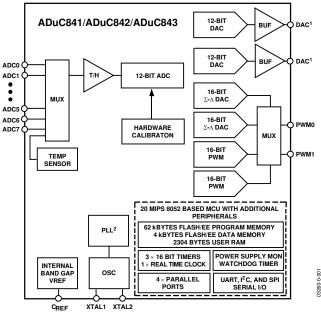

#### FUNCTIONAL BLOCK DIAGRAM

Figure 1.

#### **GENERAL DESCRIPTION**

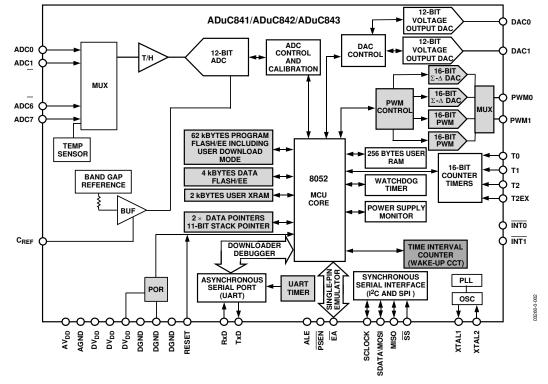

The ADuC841/ADuC842/ADuC843<sup>1</sup> are complete smart transducer front ends, that integrates a high performance self-calibrating multichannel ADC, a dual DAC, and an optimized single-cycle 20 MHz 8-bit MCU (8051 instruction set compatible) on a single chip.

The ADuC841 and ADuC842 are identical with the exception of the clock oscillator circuit; the ADuC841 is clocked directly from an external crystal up to 20 MHz whereas the ADuC842 uses a 32 kHz crystal with an on-chip PLL generating a programmable core clock up to 16.78 MHz.

The ADuC843 is identical to the ADuC842 except that the ADuC843 has no analog DAC outputs.

The microcontroller is an optimized 8052 core offering up to 20 MIPS peak performance. Three different memory options are available offering up to 62 kBytes of nonvolatile Flash/EE program memory. Four kBytes of nonvolatile Flash/EE data memory, 256 bytes RAM, and 2 kBytes of extended RAM are also integrated on-chip.

<sup>1</sup> Protected by U.S. Patent No. 5,969,657.

(continued on page 15)

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2003–2016 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

### **TABLE OF CONTENTS**

| Features                                     | 1  |

|----------------------------------------------|----|

| Applications                                 | 1  |

| Functional Block Diagram                     | 1  |

| General Description                          | 1  |

| Revision History                             | 2  |

| Specifications                               |    |

| Absolute Maximum Ratings                     |    |

| ESD Caution                                  |    |

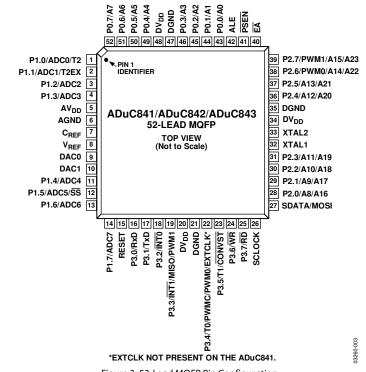

| Pin Configurations and Function Descriptions | 9  |

| Terminology                                  | 19 |

| ADC Specifications                           |    |

| DAC Specifications                           | 19 |

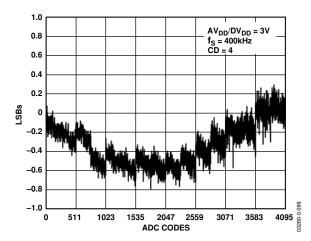

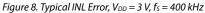

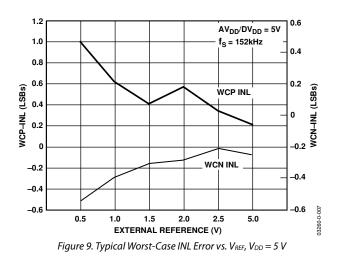

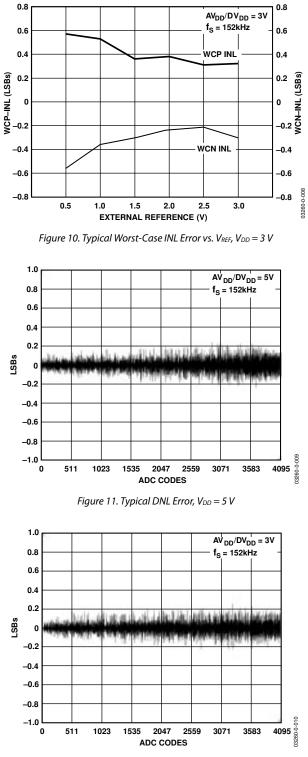

| Typical Performance Characteristics          |    |

| Functional Description                       | 24 |

| 8052 Instruction Set                         | 24 |

| Other Single-Cycle Core Features             |    |

| Memory Organization                          |    |

| Special Function Registers (SFRs)            |    |

| Accumulator SFR (ACC)                        |    |

| Special Function Register Banks              |    |

| ADC Circuit Information                      |    |

| Calibrating the ADC                          |    |

| Nonvolatile Flash/EE Memory                  |    |

| Using Flash/EE Data Memory                   |    |

|   | User Interface to On-Chip Peripherals          | . 46 |

|---|------------------------------------------------|------|

|   | On-Chip PLL                                    | . 49 |

|   | Pulse-Width Modulator (PWM)                    | . 50 |

|   | Serial Peripheral Interface (SPI)              | . 53 |

|   | I <sup>2</sup> C Compatible Interface          | . 56 |

|   | Dual Data Pointer                              | . 59 |

|   | Power Supply Monitor                           | . 60 |

|   | Watchdog Timer                                 | . 61 |

|   | Time Interval Counter (TIC)                    | . 62 |

|   | 8052 Compatible On-Chip Peripherals            | . 65 |

|   | Timer/Counter 0 and 1 Operating Modes          | . 70 |

|   | Timer/Counter Operating Modes                  | . 72 |

|   | UART Serial Interface                          | . 73 |

|   | SBUF                                           | . 73 |

|   | Interrupt System                               | . 78 |

|   | Hardware Design Considerations                 | . 80 |

|   | Other Hardware Considerations                  | . 84 |

|   | Development Tools                              | . 85 |

|   | QuickStart Development System                  | . 85 |

| Т | <sup>°</sup> iming Specifications <sup>•</sup> | . 86 |

| C | Outline Dimensions                             | . 94 |

|   | Ordering Guide                                 | . 95 |

#### **REVISION HISTORY**

| 4/16—Rev. 0 to Rev. A                  |    |

|----------------------------------------|----|

| Added Patent Note, Note 1              | 1  |

| Changes to Figure 3 and Table 3        |    |

| Changes to Figure 4                    | 14 |

| Added Table 4; Renumbered Sequentially | 14 |

| Changes to Using the DAC Section | 47 |

|----------------------------------|----|

| Updated Outline Dimensions       | 94 |

| Changes to Ordering Guide        | 95 |

11/03—Revision 0: Initial Version

### SPECIFICATIONS<sup>1</sup>

Table 1.  $AV_{DD} = DV_{DD} = 2.7 V$  to 3.6 V or 4.75 V to 5.25 V;  $V_{REF} = 2.5 V$  internal reference,  $f_{CORE} = 16.78 MHz @ 5 V 8.38 MHz @ 3 V$ ; all specifications  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted

| Parameter                                       | $V_{DD} = 5 V$                 | $V_{DD} = 3 V$        | Unit      | <b>Test Conditions/Comments</b>                    |

|-------------------------------------------------|--------------------------------|-----------------------|-----------|----------------------------------------------------|

| ADC CHANNEL SPECIFICATIONS                      |                                |                       |           |                                                    |

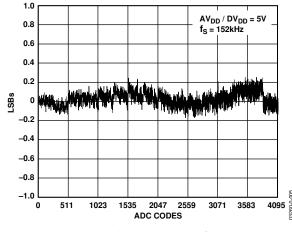

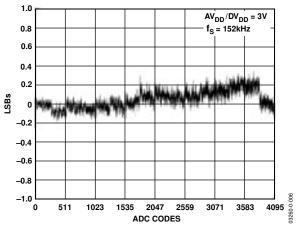

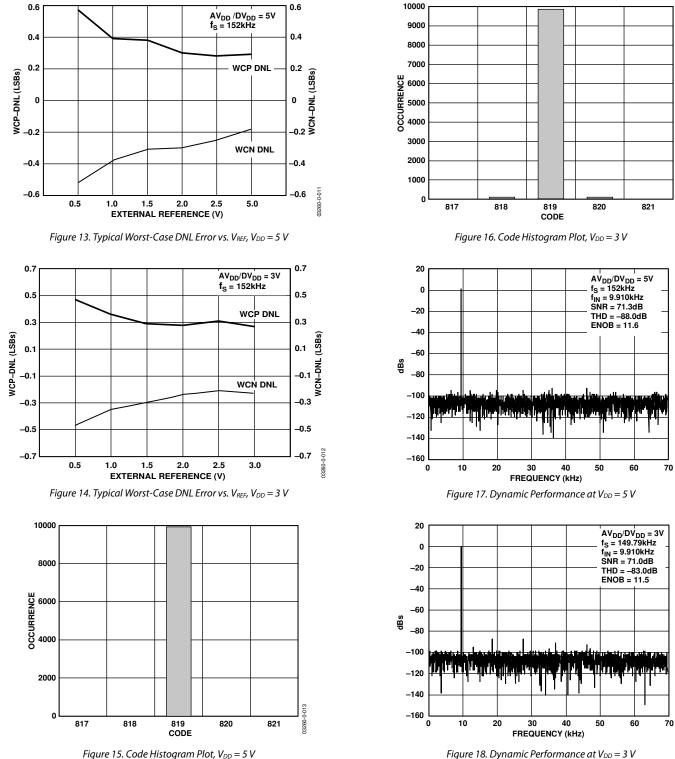

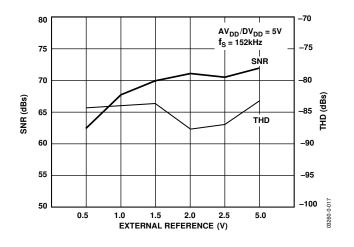

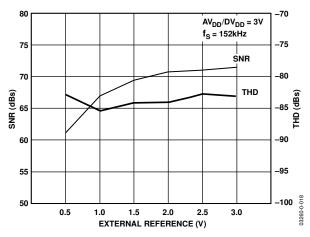

| DC ACCURACY <sup>2, 3</sup>                     |                                |                       |           | $f_{SAMPLE} = 120 \text{ kHz}$ , see the Typical   |

|                                                 |                                |                       |           | Performance Characteristics for typical            |

|                                                 |                                |                       |           | performance at other values of $f_{\text{SAMPLE}}$ |

| Resolution                                      | 12                             | 12                    | Bits      |                                                    |

| Integral Nonlinearity                           | ±1                             | ±1                    | LSB max   | 2.5 V internal reference                           |

|                                                 | ±0.3                           | ±0.3                  | LSB typ   |                                                    |

| Differential Nonlinearity                       | +1/-0.9                        | +1/-0.9               | LSB max   | 2.5 V internal reference                           |

|                                                 | ±0.3                           | ±0.3                  | LSB typ   |                                                    |

| Integral Nonlinearity <sup>4</sup>              | ±2                             | ±1.5                  | LSB max   | 1 V external reference                             |

| Differential Nonlinearity <sup>4</sup>          | +1.5/-0.9                      | +1.5/-0.9             | LSB max   | 1 V external reference                             |

| Code Distribution                               | 1                              | 1                     | LSB typ   | ADC input is a dc voltage                          |

| CALIBRATED ENDPOINT ERRORS <sup>5, 6</sup>      |                                |                       |           |                                                    |

| Offset Error                                    | ±3                             | ±2                    | LSB max   |                                                    |

| Offset Error Match                              | ±1                             | ±1                    | LSB typ   |                                                    |

| Gain Error                                      | ±3                             | ±2                    | LSB max   |                                                    |

| Gain Error Match                                | ±1                             | ±1                    | LSB typ   |                                                    |

| DYNAMIC PERFORMANCE                             |                                |                       |           | $f_{IN} = 10 \text{ kHz}$ sine wave                |

|                                                 |                                | 71                    |           | f <sub>sample</sub> = 120 kHz                      |

| Signal-to-Noise Ratio (SNR) <sup>7</sup>        | 71                             | 71                    | dB typ    |                                                    |

| Total Harmonic Distortion (THD)                 | -85                            | -85                   | dB typ    |                                                    |

| Peak Harmonic or Spurious Noise                 | -85                            | -85                   | dB typ    |                                                    |

| Channel-to-Channel Crosstalk <sup>8</sup>       | -80                            | -80                   | dB typ    |                                                    |

| ANALOG INPUT                                    | 0. V                           | 0 · V                 |           |                                                    |

| Input Voltage Range                             | 0 to V <sub>REF</sub>          | 0 to V <sub>REF</sub> | V         |                                                    |

| Leakage Current                                 | ±1                             | ±1                    | µA max    |                                                    |

|                                                 | 32                             | 32                    | pF typ    |                                                    |

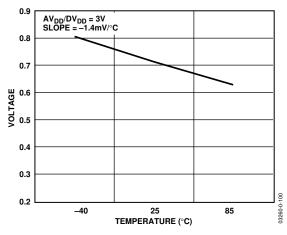

| TEMPERATURE SENSOR <sup>9</sup>                 | 700                            | 700                   |           |                                                    |

| Voltage Output at 25°C                          | 700                            | 700                   | mV typ    |                                                    |

| Voltage TC                                      | -1.4                           | -1.4                  | mV/°C typ |                                                    |

| Accuracy                                        | ±1.5                           | ±1.5                  | °C typ    | Internal/External 2.5 V V <sub>REF</sub>           |

|                                                 |                                |                       |           | DAC load to AGND                                   |

| DAC CHANNEL SPECIFICATIONS                      |                                |                       |           |                                                    |

| Internal Buffer Enabled<br>ADuC841/ADuC842 Only |                                |                       |           | $R_L = 10 \text{ k}\Omega, C_L = 100 \text{ pF}$   |

|                                                 |                                |                       |           |                                                    |

| DC ACCURACY <sup>10</sup>                       |                                |                       |           |                                                    |

| Resolution                                      | 12                             | 12                    | Bits      |                                                    |

| Relative Accuracy                               | ±3                             | ±3                    | LSB typ   |                                                    |

| Differential Nonlinearity <sup>11</sup>         | -1                             | -1                    | LSB max   | Guaranteed 12-bit monotonic                        |

|                                                 | ±1/2                           | ±1/2                  | LSB typ   |                                                    |

| Offset Error                                    | ±50                            | ±50                   | mV max    | V <sub>REF</sub> range                             |

| Gain Error                                      | ±1                             | ±1                    | % max     | AV <sub>DD</sub> range                             |

|                                                 | ±1                             | ±1                    | % typ     | V <sub>REF</sub> range                             |

| Gain Error Mismatch                             | 0.5                            | 0.5                   | % typ     | % of full-scale on DAC1                            |

| ANALOG OUTPUTS                                  |                                |                       |           |                                                    |

| Voltage Range_0                                 | $0 \text{ to } V_{\text{REF}}$ | 0 to $V_{\text{REF}}$ | V typ     | $DACV_{REF} = 2.5 V$                               |

| Voltage Range_1                                 | 0 to V <sub>DD</sub>           | 0 to V <sub>DD</sub>  | V typ     | $DAC V_{REF} = V_{DD}$                             |

| Output Impedance                                | 0.5                            | 0.5                   | Ωtyp      |                                                    |

| Parameter                                                | $V_{DD} = 5 V$          | $V_{DD} = 3 V$        | Unit             | Test Conditions/Comments                                       |

|----------------------------------------------------------|-------------------------|-----------------------|------------------|----------------------------------------------------------------|

| DAC AC CHARACTERISTICS                                   |                         |                       |                  |                                                                |

| Voltage Output Settling Time                             | 15                      | 15                    | μs typ           | Full-scale settling time to within<br>½ LSB of final value     |

| Digital-to-Analog Glitch Energy                          | 10                      | 10                    | nV-sec typ       | 1 LSB change at major carry                                    |

| DAC CHANNEL SPECIFICATIONS <sup>12, 13</sup>             |                         |                       |                  |                                                                |

| nternal Buffer Disabled ADuC841/ADuC842 Only             |                         |                       |                  |                                                                |

| DC ACCURACY <sup>10</sup>                                |                         |                       |                  |                                                                |

| Resolution                                               | 12                      | 12                    | Bits             |                                                                |

| Relative Accuracy                                        | ±3                      | ±3                    | LSB typ          |                                                                |

| Differential Nonlinearity <sup>11</sup>                  | -1                      | -1                    | LSB max          | Guaranteed 12-bit monotonic                                    |

|                                                          | ±1/2                    | ±1/2                  | LSB typ          |                                                                |

| Offset Error                                             | ±5                      | ±5                    | mV max           | V <sub>REF</sub> range                                         |

| Gain Error                                               | ±0.5                    | ±0.5                  | % typ            | V <sub>REF</sub> range                                         |

| Gain Error Mismatch <sup>4</sup>                         | 0.5                     | 0.5                   | % typ            | % of full-scale on DAC1                                        |

| ANALOG OUTPUTS                                           |                         |                       |                  |                                                                |

| Voltage Range_0                                          | $0$ to $V_{\text{REF}}$ | 0 to $V_{\text{REF}}$ | V typ            | DAC $V_{REF} = 2.5 V$                                          |

| REFERENCE INPUT/OUTPUT REFERENCE OUTPUT <sup>14</sup>    |                         |                       |                  |                                                                |

| Output Voltage (V <sub>REF</sub> )                       | 2.5                     | 2.5                   | V                |                                                                |

| Accuracy                                                 | ±10                     | ±10                   | mV Max           | Of $V_{REF}$ measured at the $C_{REF}$ pin $T_A = 25^{\circ}C$ |

| Power Supply Rejection                                   | 65                      | 67                    | dB typ           |                                                                |

| Reference Temperature Coefficient                        | ±15                     | ±15                   | ppm/°C typ       |                                                                |

| Internal V <sub>REF</sub> Power-On Time                  | 2                       | 2                     | ms typ           |                                                                |

| EXTERNAL REFERENCE INPUT <sup>15</sup>                   |                         |                       |                  |                                                                |

| Voltage Range (V <sub>REF</sub> ) <sup>4</sup>           | 1                       | 1                     | V min            |                                                                |

|                                                          | VDD                     | V <sub>DD</sub>       | V max            |                                                                |

| Input Impedance                                          | 20                      | 20                    | kΩ typ           |                                                                |

| Input Leakage                                            | 1                       | 1                     | µA max           | Internal band gap deselected via<br>ADCCON1.6                  |

| POWER SUPPLY MONITOR (PSM)                               |                         |                       |                  |                                                                |

| DV <sub>DD</sub> Trip Point Selection Range              |                         | 2.93                  | V min            | Two trip points selectable in this                             |

|                                                          |                         | 3.08                  | V max            | range programmed via TPD1–0 in<br>PSMCON, 3 V part only        |

| DV <sub>DD</sub> Power Supply Trip Point Accuracy        |                         | ±2.5                  | % max            |                                                                |

| VATCHDOG TIMER (WDT) <sup>4</sup>                        |                         |                       | 1                |                                                                |

| Timeout Period                                           | 0                       | 0                     | ms min           | Nine timeout periods selectable ir                             |

|                                                          | 2000                    | 2000                  | ms max           | this range                                                     |

| LASH/EE MEMORY RELIABILITY CHARACTERISTICS <sup>16</sup> |                         |                       |                  |                                                                |

| Endurance <sup>17</sup>                                  | 100,000                 | 100,000               | Cycles min       |                                                                |

| Data Retention <sup>18</sup>                             | 100                     | 100                   | Years min        |                                                                |

| DIGITAL INPUTS                                           |                         |                       | 1                |                                                                |

| Input Leakage Current (Port 0, EA)                       | ±10                     | ±10                   | µA max           | $V_{IN} = 0 V \text{ or } V_{DD}$                              |

|                                                          | ±1                      | ±1                    | μA typ           | $V_{\rm IN} = 0 \text{ V or } V_{\rm DD}$                      |

| Logic 1 Input Current                                    |                         |                       |                  |                                                                |

| (All Digital Inputs), SDATA, SCLOCK                      | ±10                     | ±10                   | μA max           | $V_{IN} = V_{DD}$                                              |

|                                                          | ±10                     | ±10                   | μA typ           | $V_{\rm IN} = V_{\rm DD}$<br>$V_{\rm IN} = V_{\rm DD}$         |

| Logic 0 Input Current (Ports 1, 2, 3) SDATA, SCLOCK      | -75                     | -25                   | μA typ<br>μA max |                                                                |

| Logic o input current (rons 1, 2, 3) 3DATA, 3CLOCK       | -40                     | -15                   | μA typ           | $V_{IL} = 450 \text{ mV}$                                      |

| Logic 1 to Logic 0 Transition Current (Ports 2 and 3)    | -40<br>-660             | -15                   | μΑ typ<br>μΑ max | $V_{IL} = 430 \text{ mV}$ $V_{IL} = 2 \text{ V}$               |

| Logic Fito Logic o Hansition Current (Ports 2 and 3)     | -660<br>-400            | -250                  | -                | $V_{IL} = 2 V$<br>$V_{IL} = 2 V$                               |

| DECET                                                    |                         |                       | μA typ           |                                                                |

| RESET                                                    | ±10                     | ±10                   | µA max           | $V_{\rm IN} = 0 V$                                             |

|                                                          | 10                      | 5                     | μA min           | $V_{IN} = 5 V, 3 V$ Internal Pull Down                         |

|                                                          | 105                     | 35                    | μA max           | $V_{IN} = 5 V$ , 3 V Internal Pull Down                        |

| Parameter                                            | $V_{DD} = 5 V$ | $V_{DD} = 3 V$ | Unit           | <b>Test Conditions/Comments</b>                                                      |

|------------------------------------------------------|----------------|----------------|----------------|--------------------------------------------------------------------------------------|

| LOGIC INPUTS <sup>4</sup>                            |                |                |                |                                                                                      |

| INPUT VOLTAGES                                       |                |                |                |                                                                                      |

| All Inputs Except SCLOCK, SDATA, RESET, and<br>XTAL1 |                |                |                |                                                                                      |

| VINL, Input Low Voltage                              | 0.8            | 0.4            | V max          |                                                                                      |

| VINH, Input High Voltage                             | 2.0            | 2.0            | V min          |                                                                                      |

| SDATA                                                |                |                |                |                                                                                      |

| VINL, Input Low Voltage                              | 0.8            | 0.8            | V max          |                                                                                      |

| VINH, Input High Voltage                             | 2.0            | 2.0            | V min          |                                                                                      |

| SCLOCK and RESET ONLY <sup>4</sup>                   |                |                |                |                                                                                      |

| (Schmitt-Triggered Inputs)                           |                |                |                |                                                                                      |

| V <sub>T+</sub>                                      | 1.3            | 0.95           | V min          |                                                                                      |

|                                                      | 3.0            | 0.25           | V max          |                                                                                      |

| V <sub>T-</sub>                                      | 0.8            | 0.4            | Vmin           |                                                                                      |

|                                                      | 1.4            | 1.1            | V max          |                                                                                      |

| $V_{T+} - V_{T-}$                                    | 0.3            | 0.3            | V min          |                                                                                      |

|                                                      | 0.85           | 0.85           | V max          |                                                                                      |

| CRYSTAL OSCILLATOR                                   |                |                |                |                                                                                      |

| Logic Inputs, XTAL1 Only                             |                |                |                |                                                                                      |

| V <sub>INL</sub> , Input Low Voltage                 | 0.8            | 0.4            | V typ          |                                                                                      |

| $V_{\text{INH}}$ , Input High Voltage                | 3.5            | 2.5            | V typ          |                                                                                      |

| XTAL1 Input Capacitance                              | 18             | 18             | pF typ         |                                                                                      |

| XTAL2 Output Capacitance                             | 18             | 18             | pF typ         |                                                                                      |

| MCU CLOCK RATE                                       | 16.78          | 8.38           | MHz max        | ADuC842/ADuC843 Only                                                                 |

|                                                      | 20             | 8.38           | MHz max        | ADuC841 Only                                                                         |

| DIGITAL OUTPUTS                                      | 20             | 0.50           |                |                                                                                      |

| Output High Voltage (Vон)                            | 2.4            |                | V min          | $V_{DD} = 4.5 V \text{ to } 5.5 V$                                                   |

| output high voltage (von)                            | 4              |                | V typ          | $I_{\text{SOURCE}} = 80 \mu\text{A}$                                                 |

|                                                      | •              | 2.4            | Vmin           | $V_{DD} = 2.7 \text{ V to } 3.3 \text{ V}$                                           |

|                                                      |                | 2.6            | V typ          | $I_{\text{SOURCE}} = 20 \mu\text{A}$                                                 |

| Output Low Voltage (Vol)                             |                | 2.0            | 1 UP           | 1500KCE - 20 µ/                                                                      |

| ALE, Ports 0 and 2                                   | 0.4            | 0.4            | V max          | $I_{SINK} = 1.6 \text{ mA}$                                                          |

|                                                      | 0.4            | 0.4            | V typ          | $I_{\text{SINK}} = 1.6 \text{ mA}$                                                   |

| Port 3                                               | 0.2            | 0.2            | V typ<br>V max | $I_{SINK} = 1.6 \text{ mA}$<br>$I_{SINK} = 4 \text{ mA}$                             |

| SCLOCK/SDATA                                         | 0.4            | 0.4            | V max          | $I_{SINK} = 4 \text{ mA}$<br>$I_{SINK} = 8 \text{ mA}, I^2 \text{C} \text{ Enabled}$ |

| Floating State Leakage Current <sup>4</sup>          | 0.4<br>±10     |                |                | ISINK – O ITIA, I C ENADIEU                                                          |

| Hoating State Leakage Current                        | ±10<br>±1      | ±10            | μA max         |                                                                                      |

| STARTUP TIME                                         |                | ±1             | μA typ         | At any core CLK                                                                      |

| At Power-On                                          | 500            | 500            | matur          | At any core CLK                                                                      |

|                                                      | 500            | 500            | ms typ         |                                                                                      |

| From Idle Mode                                       | 100            | 100            | µs typ         |                                                                                      |

| From Power-Down Mode                                 | 150            | 400            | us true        |                                                                                      |

| Wake-up with INTO Interrupt                          | 150            | 400            | µs typ         |                                                                                      |

| Wake-up with SPI/I <sup>2</sup> C Interrupt          | 150            | 400            | μs typ         |                                                                                      |

| Wake-up with External RESET                          | 150            | 400            | µs typ         |                                                                                      |

| After External RESET in Normal Mode                  | 30             | 30             | ms typ         |                                                                                      |

| After WDT Reset in Normal Mode                       | 3              | 3              | ms typ         | Controlled via WDCON SFR                                                             |

| Parameter                                                  | $V_{DD} = 5 V$ | $V_{DD} = 3 V$ | Unit   | Test Conditions/Comments                  |

|------------------------------------------------------------|----------------|----------------|--------|-------------------------------------------|

| POWER REQUIREMENTS <sup>19, 20</sup>                       |                |                |        |                                           |

| Power Supply Voltages                                      |                |                |        |                                           |

| $AV_{DD}/DV_{DD} - AGND$                                   |                | 2.7            | V min  | $AV_{DD}/DV_{DD} = 3 V nom$               |

|                                                            |                | 3.6            | V max  |                                           |

|                                                            | 4.75           |                | V min  | $AV_{DD}/DV_{DD} = 5 V nom$               |

|                                                            | 5.25           |                | V max  |                                           |

| Power Supply Currents <b>Normal</b> Mode <sup>21</sup>     |                |                |        |                                           |

| DV <sub>DD</sub> Current <sup>4</sup>                      | 10             | 4.5            | mA typ | Core CLK = 2.097 MHz                      |

| AV <sub>DD</sub> Current                                   | 1.7            | 1.7            | mA max | Core CLK = 2.097 MHz                      |

| DV <sub>DD</sub> Current                                   | 38             | 12             | mA max | Core CLK = 16.78MHz/8.38 MHz 5 V/3        |

|                                                            | 33             | 10             | mA typ | Core CLK = 16.78MHz/8.38 MHz 5 V/3        |

| AV <sub>DD</sub> Current                                   | 1.7            | 1.7            | mA max | Core CLK = 16.78MHz/8.38 MHz 5 V/3        |

| DV <sub>DD</sub> Current <sup>4</sup>                      | 45             | N/A            | mA max | Core CLK = 20MHz ADuC841 Only             |

| Power Supply Currents Idle Mode <sup>21</sup>              |                |                |        |                                           |

| DV <sub>DD</sub> Current                                   | 4.5            | 2.2            | mA typ | Core CLK = 2.097 MHz                      |

| AV <sub>DD</sub> Current                                   | 3              | 2              | μA typ | Core CLK = 2.097 MHz                      |

| DV <sub>DD</sub> Current <sup>4</sup>                      | 12             | 5              | mA max | Core CLK = 16.78 MHz/8.38 MHz 5 V/3       |

|                                                            | 10             | 3.5            | mA typ | Core CLK = 16.78 MHz/8.38 MHz 5 V/3       |

| AV <sub>DD</sub> Current                                   | 3              | 2              | μA typ | Core CLK = 16.78 MHz/8.38 MHz 5 V/3       |

| Power Supply Currents <b>Power-Down</b> Mode <sup>21</sup> |                |                |        | Core CLK = any frequency                  |

| DV <sub>DD</sub> Current                                   | 28             | 18             | μA max | Oscillator Off / TIMECON.1 = 0            |

|                                                            | 20             | 10             | μA typ |                                           |

| AV <sub>DD</sub> Current                                   | 2              | 1              | μA typ | Core CLK = any frequency, ADuC841<br>Only |

| DV <sub>DD</sub> Current <sup>4</sup>                      | 3              | 1              | mA max | TIMECON.1 = 1                             |

| DV <sub>DD</sub> Current <sup>4</sup>                      | 50             | 22             | μA max | Core CLK = any frequency                  |

|                                                            | 40             | 15             | μA typ | ADuC842/ADuC843 Only, oscillator of       |

| Typical Additional Power Supply Currents                   |                |                |        |                                           |

| PSM Peripheral                                             | 15             | 10             | μA typ | $AV_{DD} = DV_{DD}$                       |

| ADC <sup>4</sup>                                           | 1.0            | 1.0            | mA min | MCLK Divider = 32                         |

|                                                            | 2.8            | 1.8            | mA max | MCLK Divider = 2                          |

| DAC                                                        | 150            | 130            | μA typ |                                           |

See footnotes on the next page.

Data Sheet

<sup>1</sup> Temperature Range –40°C to +85°C.

- <sup>2</sup> ADC linearity is guaranteed during normal MicroConverter core operation.

- <sup>3</sup> ADC LSB size =  $V_{REF}/2^{12}$ , that is, for internal  $V_{REF}$  = 2.5 V, 1 LSB = 610  $\mu$ V, and for external  $V_{REF}$  = 1 V, 1 LSB = 244  $\mu$ V.

- <sup>4</sup> These numbers are not production tested but are supported by design and/or characterization data on production release.

- <sup>5</sup> Offset and gain error and offset and gain error match are measured after factory calibration.

- <sup>6</sup> Based on external ADC system components, the user may need to execute a system calibration to remove additional external channel errors to achieve these

- specifications.

- <sup>7</sup> SNR calculation includes distortion and noise components.

- <sup>8</sup> Channel-to-channel crosstalk is measured on adjacent channels.

- <sup>9</sup> The temperature monitor gives a measure of the die temperature directly; air temperature can be inferred from this result.

- <sup>10</sup> DAC linearity is calculated using:

- Reduced code range of 100 to 4095, 0 V to V<sub>REF</sub> range.

- Reduced code range of 100 to 3945, 0 V to  $V_{DD}$  range.

- DAC output load =  $10 \text{ k}\Omega$  and 100 pF.

- <sup>11</sup> DAC differential nonlinearity specified on 0 V to  $V_{REF}$  and 0 V to  $V_{DD}$  ranges.

- <sup>12</sup> DAC specification for output impedance in the unbuffered case depends on DAC code.

- <sup>13</sup> DAC specifications for I<sub>SINK</sub>, voltage output settling time, and digital-to-analog glitch energy depend on external buffer implementation in unbuffered mode. DAC in unbuffered mode tested with OP270 external buffer, which has a low input leakage current.

- <sup>14</sup> Measured with C<sub>REF</sub> pin decoupled with 0.47 μF capacitor to ground. Power-up time for the internal reference is determined by the value of the decoupling capacitor chosen for the C<sub>REF</sub> pin.

- <sup>15</sup> When using an external reference device, the internal band gap reference input can be bypassed by setting the ADCCON1.6 bit.

- <sup>16</sup> Flash/EE memory reliability characteristics apply to both the Flash/EE program memory and the Flash/EE data memory.

- <sup>17</sup> Endurance is qualified to 100,000 cycles as per JEDEC Std. 22 method A117 and measured at -40°C, +25°C, and +85°C. Typical endurance at 25°C is 700,000 cycles.

<sup>18</sup> Retention lifetime equivalent at junction temperature (T<sub>j</sub>) = 55°C as per JEDEC Std. 22 method A117. Retention lifetime based on an activation energy of 0.6 eV derates with junction temperature as shown in Figure 38 in the Flash/EE Memory Reliability section.

- <sup>19</sup> Power supply current consumption is measured in normal, idle, and power-down modes under the following conditions:

- Normal Mode: Reset = 0.4 V, digital I/O pins = open circuit, Core Clk changed via CD bits in PLLCON (ADuC842/ADuC843), core executing internal software loop.

Idle Mode: Reset = 0.4 V, digital I/O pins = open circuit, Core Clk changed via CD bits in PLLCON (ADuC842/ADuC843), PCON.0 = 1, core execution suspended in idle mode.

- Power-Down Mode: Reset = 0.4 V, all Port 0 pins = 0.4 V, All other digital I/O and Port 1 pins are open circuit, Core Clk changed via CD bits in PLLCON (ADuC842/ADuC843), PCON.0 = 1, core execution suspended in power-down mode, OSC turned on or off via OSC\_PD bit (PLLCON.7) in PLLCON SFR (ADuC842/ADuC843).

- <sup>20</sup> DV<sub>DD</sub> power supply current increases typically by 3 mA (3 V operation) and 10 mA (5 V operation) during a Flash/EE memory program or erase cycle.

- <sup>21</sup> Power supply currents are production tested at 5.25 V and 3.3 V for a 5 V and 3 V part, respectively.

#### **ABSOLUTE MAXIMUM RATINGS**

Table 2.  $T_A = 25^{\circ}$ C, unless otherwise noted

| Tuble 2. TA = 25 °C, unless other wise noted                                                                            |                                           |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|--|--|--|--|

| Parameter                                                                                                               | Rating                                    |  |  |  |  |

| AV <sub>DD</sub> to DV <sub>DD</sub>                                                                                    | –0.3 V to +0.3 V                          |  |  |  |  |

| AGND to DGND                                                                                                            | –0.3 V to +0.3 V                          |  |  |  |  |

| DV <sub>DD</sub> to DGND, AV <sub>DD</sub> to AGND                                                                      | –0.3 V to +7 V                            |  |  |  |  |

| Digital Input Voltage to DGND                                                                                           | -0.3 V to DV <sub>DD</sub> + 0.3 V        |  |  |  |  |

| Digital Output Voltage to DGND                                                                                          | –0.3 V to $\text{DV}_{\text{DD}}$ + 0.3 V |  |  |  |  |

| V <sub>REF</sub> to AGND                                                                                                | -0.3 V to AV <sub>DD</sub> + 0.3 V        |  |  |  |  |

| Analog Inputs to AGND                                                                                                   | -0.3 V to AV <sub>DD</sub> + 0.3 V        |  |  |  |  |

| Operating Temperature Range,<br>Industrial<br>ADuC841BS, ADuC842BS, ADuC843BS,<br>ADuC841BCP, ADuC842BCP,<br>ADuC843BCP | –40°C to +85°C                            |  |  |  |  |

| Storage Temperature Range                                                                                               | –65°C to +150°C                           |  |  |  |  |

| Junction Temperature                                                                                                    | 150°C                                     |  |  |  |  |

| θ <sub>JA</sub> Thermal Impedance (ADuC84xBS)                                                                           | 90°C/W                                    |  |  |  |  |

| $\theta_{JA}$ Thermal Impedance (ADuC84xBCP)                                                                            | 52°C/W                                    |  |  |  |  |

| Lead Temperature, Soldering<br>Vapor Phase (60 sec)<br>Infrared (15 sec)                                                | 215°C<br>220°C                            |  |  |  |  |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

Figure 2. ADuC841/ADuC842/ADuC843 Block Diagram (Shaded Areas are Features Not Present on the ADuC812), No DACs on ADuC843, PLL on ADuC842/ADuC843 Only.

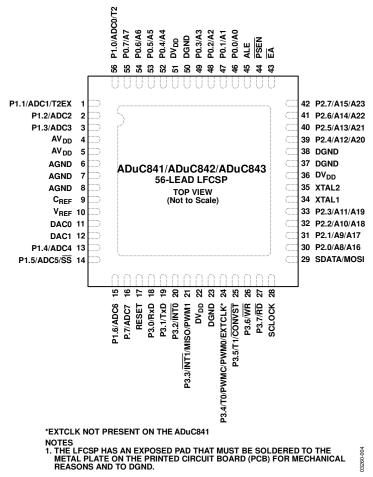

#### **PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS**

| Pin No. | Mnemonic         | Type <sup>1</sup> | Description                                                                                                                                                                                      |  |

|---------|------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1       | P1.0/ADC0/T2     | I                 | Input Port 1 (P1.0). Port 1 is an 8-bit input port only. Unlike the other ports, Port 1 defaults to analog input mode. To configure this port pin as a digital input, write a 0 to the port bit. |  |

|         |                  |                   | Single-Ended Analog Input (ADC0). Channel selection is via ADCCON2 SFR.                                                                                                                          |  |

|         |                  |                   | Timer 2 Digital Input (T2). Input to Timer/Counter 2. When enabled, Counter 2 is incremented in response to a 1 to 0 transition of the T2 input.                                                 |  |

| 2       | P1.1/ADC1/T2EX   | 1                 | Input Port 1 (P1.1). Port 1 is an 8-bit input port only. Unlike the other ports, Port 1 defaults to analog input mode. To configure this port pin as a digital input, write a 0 to the port bit. |  |

|         |                  |                   | Single-Ended Analog Input 1 (ADC1). Channel selection is via ADCCON2 SFR.                                                                                                                        |  |

|         |                  |                   | Capture/Reload Trigger for Counter 2 (T2EX). T2EX is a digital input. This pin also functions as an up/down control input for Counter 2.                                                         |  |

| 3       | P1.2/ADC2        | 1                 | Input Port 1 (P1.2). Port 1 is an 8-bit input port only. Unlike the other ports, Port 1 defaults to analog input mode. To configure this port pin as a digital input, write a 0 to the port bit. |  |

|         |                  |                   | Single-Ended Analog Input (ADC2). Channel selection is via ADCCON2 SFR.                                                                                                                          |  |

| 4       | P1.3/ADC3        | 1                 | Input Port 1 (P1.3). Port 1 is an 8-bit input port only. Unlike the other ports, Port 1 defaults to analog input mode. To configure this port pin as a digital input, write a 0 to the port bit. |  |

|         |                  |                   | Single-Ended Analog Input (ADC3). Channel selection is via ADCCON2 SFR.                                                                                                                          |  |

| 5       | AV <sub>DD</sub> | Р                 | Analog Positive Supply Voltage. 3 V or 5 V nominal.                                                                                                                                              |  |

| 6       | AGND             | G                 | Analog Ground. AGND is the ground reference point for the analog circuitry.                                                                                                                      |  |

| 7       | Cref             | I/O               | Decoupling Input for On-Chip Reference. Connect a 0.47 µF capacitor between this pin and AGND.                                                                                                   |  |

| 8       | V <sub>REF</sub> | NC                | Not Connected. This was a reference output on the ADuC812; use the CREF pin instead.                                                                                                             |  |

| 9       | DAC0             | 0                 | Voltage Output from DAC0. This pin is a no connect on the ADuC843.                                                                                                                               |  |

| 10      | DAC1             | 0                 | Voltage Output from DAC1. This pin is a no connect on the ADuC843.                                                                                                                               |  |

Data Sheet

| Pin No.    | Mnemonic            | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                                   |

|------------|---------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11         | P1.4/ADC4           |                   | Input Port 1 (P1.4). Port 1 is an 8-bit input port only. Unlike the other ports, Port 1 defaults to analog input mode. To configure this port pin as a digital input, write a 0 to the port bit.                                                                                                                                              |

| 12         | P1.5/ADC5/SS        | I                 | Single-Ended Analog Input 4 (ADC4). Channel selection is via ADCCON2 SFR.<br>Input Port 1 (P1.5). Port 1 is an 8-bit input port only. Unlike the other ports, Port 1<br>defaults to analog input mode. To configure this port pin as a digital input, write a<br>0 to the port bit.                                                           |

|            |                     |                   | Single-Ended Analog Input 5 (ADC5). Channel selection is via ADCCON2 SFR.<br>Slave Select Input for the SPI Interface (SS).                                                                                                                                                                                                                   |

| 13         | P1.6/ADC6           | I                 | Input Port 1 (P1.6). Port 1 is an 8-bit input port only. Unlike the other ports, Port 1 defaults to analog input mode. To configure this port pin as a digital input, write a 0 to the port bit.                                                                                                                                              |

| 14         | P1.7/ADC7           | I                 | Single-Ended Analog Input 6 (ADC6). Channel selection is via ADCCON2 SFR.<br>Input Port 1(P1.7). Port 1 is an 8-bit input port only. Unlike the other ports, Port 1<br>defaults to analog input mode. To configure this port pin as a digital input, write a<br>0 to the port bit.                                                            |

|            |                     |                   | Single-Ended Analog Input 7 (ADC7). Channel selection is via ADCCON2 SFR.                                                                                                                                                                                                                                                                     |

| 15         | RESET               | I                 | Reset. Digital Input. A high level on this pin for 24 master clock cycles while the oscillator is running resets the device.                                                                                                                                                                                                                  |

| 16         | P3.0/RxD            | I/O               | Input/Output Port 3 (P3.0). Port 3 is a bidirectional port with internal pull-up resistors. Port 3 pins that have 1s written to them are pulled high by the internal pull-up resistors, and in that state can be used as inputs. As inputs, Port 3 pins being pulled externally low source current because of the internal pull-up resistors. |

|            |                     |                   | Receiver Data Input (Asynchronous) or Data Input/Output (Synchronous) of the Serial (UART) Port (RxD).                                                                                                                                                                                                                                        |

| 17         | P3.1/TxD            | I/O               | Input/Output Port 3 (P3.1). Port 3 is a bidirectional port with internal pull-up resistors. Port 3 pins that have 1s written to them are pulled high by the internal pull-up resistors, and in that state can be used as inputs. As inputs, Port 3 pins being pulled externally low source current because of the internal pull-up resistors. |

|            |                     |                   | Transmitter Data Output (Asynchronous) or Clock Output (Synchronous) of the Serial (UART) Port (TxD).                                                                                                                                                                                                                                         |

| 18         | P3.2/INTO           | I/O               | Input/Output Port 3 (P3.2). Port 3 is a bidirectional port with internal pull-up resistors. Port 3 pins that have 1s written to them are pulled high by the internal pull-up resistors, and in that state can be used as inputs. As inputs, Port 3 pins being pulled externally low source current because of the internal pull-up resistors. |

|            |                     |                   | Interrupt 0 (INTO). Programmable edge or level triggered interrupt input; can be programmed to one of two priority levels. This pin can also be used as a gate control input to Timer 0.                                                                                                                                                      |

| 19         | P3.3/INT1/MISO/PWM1 | I/O               | Input/Output Port 3 (P3.3). Port 3 is a bidirectional port with internal pull-up resistors. Port 3 pins that have 1s written to them are pulled high by the internal pull-up resistors, and in that state can be used as inputs. As inputs, Port 3 pins being pulled externally low source current because of the internal pull-up resistors. |

|            |                     |                   | Interrupt 1 (INT1). Programmable edge or level triggered interrupt input; can be programmed to one of two priority levels. This pin can also be used as a gate control input to Timer 1.                                                                                                                                                      |

|            |                     |                   | SPI Master Input/Slave Output Data I/O Pin for SPI Serial Interface (MISO).<br>PWM 1 Voltage Output (PWM1). See the CFG841/CFG842 register for further<br>information.                                                                                                                                                                        |

| 20, 34, 48 | DV <sub>DD</sub>    | Р                 | Digital Positive Supply Voltage. 3 V or 5 V nominal.                                                                                                                                                                                                                                                                                          |

| 21, 35, 47 | DGND                | G                 | Digital Ground. DGND is the ground reference point for the digital circuitry.                                                                                                                                                                                                                                                                 |

| Pin No. | Mnemonic                 | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                                   |

|---------|--------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22      | P3.4/T0/PWMC/PWM0/EXTCLK | I/O               | Input/Output Port 3 (P3.4). Port 3 is a bidirectional port with internal pull-up resistors. Port 3 pins that have 1s written to them are pulled high by the internal pull-up resistors, and in that state can be used as inputs. As inputs, Port 3 pins being pulled externally low source current because of the internal pull-up resistors. |

|         |                          |                   | Timer/Counter 0 Input (T0).                                                                                                                                                                                                                                                                                                                   |

|         |                          |                   | PWM Clock Input (PWMC).                                                                                                                                                                                                                                                                                                                       |

|         |                          |                   | PWM 0 Voltage Output (PWM0). PWM outputs can be configured to use Port 2.6 and Port 2.7 or Port 3.4 and Port 3.3.                                                                                                                                                                                                                             |

|         |                          |                   | Input for External Clock Signal (EXTCLK). This pin function must be enabled via the CFG842 register.                                                                                                                                                                                                                                          |

| 23      | P3.5/T1/CONVST           | I/O               | Input/Output Port 3 (P3.5). Port 3 is a bidirectional port with internal pull-up resistors. Port 3 pins that have 1s written to them are pulled high by the internal pull-up resistors, and in that state can be used as inputs. As inputs, Port 3 pins being pulled externally low source current because of the internal pull-up resistors. |

|         |                          |                   | Timer/Counter 1 Input (T1).                                                                                                                                                                                                                                                                                                                   |

|         |                          |                   | Active Low Convert Start Logic Input for the ADC Block When the External Convert Start Function is Enabled (CONVST). A low to high transition on this input puts the track-and-hold into hold mode and starts the conversion.                                                                                                                 |

| 24      | P3.6/WR                  | I/O               | Input/Output Port 3 (P3.6). Port 3 is a bidirectional port with internal pull-up resistors. Port 3 pins that have 1s written to them are pulled high by the internal pull-up resistors, and in that state can be used as inputs. As inputs, Port 3 pins being pulled externally low source current because of the internal pull-up resistors. |

|         |                          |                   | Write Control Signal, Logic Output (WR). Latches the data byte from Port 0 into the external data memory.                                                                                                                                                                                                                                     |

| 25      | P3.7/RD                  | I/O               | Input/Output Port 3 (P3.7). Port 3 is a bidirectional port with internal pull-up resistors. Port 3 pins that have 1s written to them are pulled high by the internal pull-up resistors, and in that state can be used as inputs. As inputs, Port 3 pins being pulled externally low source current because of the internal pull-up resistors. |

|         |                          |                   | Read Control Signal, Logic Output (RD). Enables the external data memory to Port 0.                                                                                                                                                                                                                                                           |

| 26      | SCLOCK                   | I/O               | Serial Clock Pin for I <sup>2</sup> C-Compatible Clock or for SPI Serial Interface Clock.                                                                                                                                                                                                                                                     |

| 27      | SDATA/MOSI               | I/O               | User Selectable, I <sup>2</sup> C Compatible, or SPI Data Input/Output Pin (SDATA).                                                                                                                                                                                                                                                           |

|         |                          |                   | SPI Master Output/Slave Input Data I/O Pin for SPI Interface (MOSI).                                                                                                                                                                                                                                                                          |

| 28      | P2.0/A8/A16              | I/O               | Input/Output Port 2 (P2.0). Port 2 is a bidirectional port with internal pull-up resistors. Port 2 pins that have 1s written to them are pulled high by the internal pull-up resistors, and in that state can be used as inputs. As inputs, Port 2 pins being pulled externally low source current because of the internal pull-up resistors. |

|         |                          |                   | External Memory Addresses (A8). Port 2 emits the middle order address byte                                                                                                                                                                                                                                                                    |

|         |                          |                   | during accesses to the external 24-bit external data memory space.                                                                                                                                                                                                                                                                            |

|         |                          |                   | External Memory Addresses (A16). Port 2 emits the high order address byte during accesses to the external 24-bit external data memory space.                                                                                                                                                                                                  |

| 29      | P2.1/A9/A17              | I/O               | Input/Output Port 2 (P2.1). Port 2 is a bidirectional port with internal pull-up resistors. Port 2 pins that have 1s written to them are pulled high by the internal pull-up resistors, and in that state can be used as inputs. As inputs, Port 2 pins being pulled externally low source current because of the internal pull-up resistors. |

|         |                          |                   | External Memory Addresses (A9). Port 2 emits the middle order address byte                                                                                                                                                                                                                                                                    |

|         |                          |                   | during accesses to the external 24-bit external data memory space.<br>External Memory Addresses (A17). Port 2 emits the high order address byte during                                                                                                                                                                                        |

| 30      | P2.2/A10/A18             | I/O               | accesses to the external 24-bit external data memory space.<br>Input/Output Port 2 (P2.2). Port 2 is a bidirectional port with internal pull-up                                                                                                                                                                                               |

|         |                          |                   | resistors. Port 2 pins that have 1s written to them are pulled high by the internal pull-up resistors, and in that state can be used as inputs. As inputs, Port 2 pins being pulled externally low source current because of the internal pull-up resistors.                                                                                  |

|         |                          |                   | External Memory Addresses (A10). Port 2 emits the middle order address byte during accesses to the external 24-bit external data memory space.<br>External Memory Addresses (A18). Port 2 emits the high order address byte during                                                                                                            |

|         |                          |                   | accesses to the external 24-bit external data memory space.                                                                                                                                                                                                                                                                                   |

| Pin No. | Mnemonic          | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                                   |

|---------|-------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31      | P2.3/A11/A19      | I/O               | Input/Output Port 2 (P2.3). Port 2 is a bidirectional port with internal pull-up resistors. Port 2 pins that have 1s written to them are pulled high by the internal pull-up resistors, and in that state can be used as inputs. As inputs, Port 2 pins being pulled externally low source current because of the internal pull-up resistors. |

|         |                   |                   | External Memory Addresses (A11). Port 2 emits the middle order address byte during accesses to the external 24-bit external data memory space.                                                                                                                                                                                                |

|         |                   |                   | External Memory Addresses (A19). Port 2 emits the high order address byte during accesses to the external 24-bit external data memory space.                                                                                                                                                                                                  |

| 32      | XTAL1             | I                 | Input to the Inverting Oscillator Amplifier.                                                                                                                                                                                                                                                                                                  |

| 33      | XTAL2             | 0                 | Output of the Inverting Oscillator Amplifier.                                                                                                                                                                                                                                                                                                 |

| 36      | P2.4/A12/A20      | I/O               | Input/Output Port 2 (P2.4). Port 2 is a bidirectional port with internal pull-up resistors. Port 2 pins that have 1s written to them are pulled high by the internal pull-up resistors, and in that state can be used as inputs. As inputs, Port 2 pins being pulled externally low source current because of the internal pull-up resistors. |

|         |                   |                   | External Memory Addresses (A12). Port 2 emits the middle order address byte during accesses to the external 24-bit external data memory space.                                                                                                                                                                                                |