Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 10-Bit, 4× Oversampling SDTV Video Decoder

Data Sheet ADV7180

#### **FEATURES**

Qualified for automotive applications

Worldwide NTSC/PAL/SECAM color demodulation support

One 10-bit ADC, 4× oversampling for CVBS, 2× oversampling

for Y/C mode, and 2× oversampling for YPrPb (per channel)

3 video input channels with on-chip antialiasing filter

CVBS (composite), Y/C (S-Video), and YPrPb (component)

video input support

5-line adaptive comb filters and CTI/DNR video enhancement

Mini-TBC functionality provided by adaptive digital line length tracking (ADLLT), signal processing, and enhanced FIFO management

Integrated AGC with adaptive peak white mode Macrovision copy protection detection NTSC/PAL/SECAM autodetection

8-bit ITU-R BT.656 YCrCb 4:2:2 output and HS, VS, and FIELD<sup>1</sup>

1.0 V analog input signal range

Full-featured VBI data slicer with teletext support (WST)

Power-down mode and ultralow sleep mode current

2-wire serial MPU interface (I<sup>2</sup>C compatible)

Single 1.8 V supply possible

- 1.8 V analog, 1.8 V PLL, 1.8 V digital, 1.8 V to 3.3 V I/O supply

- -10°C to +70°C commercial temperature grade

- -40°C to +85°C industrial/automotive qualified temperature grade

- -40°C to +125°C temperature grade for automotive qualified 4 package types

64-lead, 10 mm × 10 mm, RoHS compliant LQFP 48-Lead, 7 mm × 7 mm, RoHS compliant LQFP 40-lead, 6 mm × 6 mm, RoHS compliant LFCSP

32-lead, 5 mm × 5 mm, RoHS compliant LFCSP

#### **GENERAL DESCRIPTION**

The ADV7180 automatically detects and converts standard analog baseband television signals compatible with worldwide NTSC, PAL, and SECAM standards into 4:2:2 component video data compatible with the 8-bit ITU-R BT.656 interface standard.

The simple digital output interface connects gluelessly to a wide range of MPEG encoders, codecs, mobile video processors, and Analog Devices, Inc., digital video encoders, such as the ADV7391. External HS, VS, and FIELD signals provide timing references for LCD controllers and other video ASICs, if required. Accurate 10-bit analog-to-digital conversion provides professional quality

#### **APPLICATIONS**

Digital camcorders and PDAs

Low cost SDTV PIP decoders for digital TVs

Multichannel DVRs for video security

AV receivers and video transcoding

PCI-/USB-based video capture and TV tuner cards

Personal media players and recorders

Smartphone/multimedia handsets

In-car/automotive infotainment units

Rearview camera/vehicle safety systems

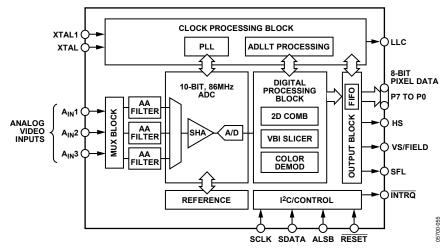

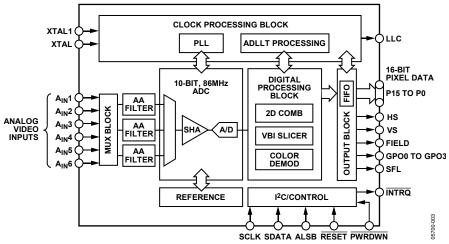

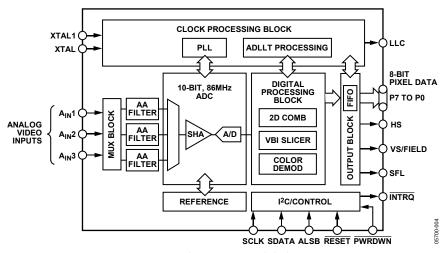

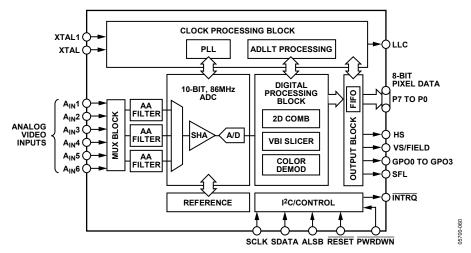

#### **FUNCTIONAL BLOCK DIAGRAM**

10NLY AVAILABLE ON 64-LEAD PACKAGE AND 48-LEAD PACKAGES.

216-BIT ONLY AVAILABLE ON 64-LEAD PACKAGE.

348-LEAD, 40-LEAD, AND 32-LEAD PACKAGE USES ONE LEAD FOR VS/FIELD.

4NOT AVAILABLE ON 32-LEAD PACKAGE.

50NLY AVAILABLE ON 4

Figure 1.

video performance for consumer applications with true 8-bit data resolution. Three analog video input channels accept standard composite, S-Video, or component video signals, supporting a wide range of consumer video sources. AGC and clamp-restore circuitry allow an input video signal peak-to-peak range to 1.0 V. Alternatively, these can be bypassed for manual settings.

The line-locked clock output allows the output data rate, timing signals, and output clock signals to be synchronous, asynchronous, or line locked even with ±5% line length variation. Output control signals allow glueless interface connections in many applications. The ADV7180 is programmed via a 2-wire, serial bidirectional port (I²C-compatible) and is fabricated in a 1.8 V CMOS process. Its monolithic CMOS construction ensures greater functionality with lower power dissipation. LFCSP package options make the decoder ideal for space-constrained portable applications. The 64-lead LQFP package is pin compatible with the ADV7181C.

Trademarks and registered trademarks are the property of their respective owners.

<sup>&</sup>lt;sup>1</sup> The 48-Lead LQFP, 40-lead LFCSP, and 32-lead LFCSP use one pin to output VS or FIELD.

# ADV7180\* PRODUCT PAGE QUICK LINKS

Last Content Update: 02/23/2017

# COMPARABLE PARTS 🖵

View a parametric search of comparable parts.

### **EVALUATION KITS**

· ADV7180 Evaluation Boards

### **DOCUMENTATION**

#### **Application Notes**

- AN-1180: Optimizing Video Platforms for Automated Post-Production Self-Tests

- AN-1240: Low Cost Video Multiplexer for Video Switching Using the ADA4853-2 Op Amp with Disable Function

- AN-1260: Crystal Design Considerations for Video Decoders, HDMI Receivers, and Transceivers

- · AN-850: Adaptive Digital Line Length Tracking

#### **Data Sheet**

ADV7180: 10-Bit, 4x Oversampling SDTV Video Decoder Data Sheet

### **TOOLS AND SIMULATIONS**

ADV7180 IBIS Models

# REFERENCE DESIGNS 🖵

- CN0060

- CN0263

### REFERENCE MATERIALS 🖳

#### Informational

Advantiv<sup>™</sup> Advanced TV Solutions

#### **Technical Articles**

- Analog Video Time Base Correction and Processing for Nonstandard TV Signals

- Optimizing standard-definition video on high-definition displays

### DESIGN RESOURCES $\Box$

- ADV7180 Material Declaration

- PCN-PDN Information

- Quality And Reliability

- · Symbols and Footprints

# **DISCUSSIONS**

View all ADV7180 EngineerZone Discussions.

# SAMPLE AND BUY

Visit the product page to see pricing options.

# **TECHNICAL SUPPORT**

Submit a technical question or find your regional support number.

# **DOCUMENT FEEDBACK**

Submit feedback for this data sheet.

# **ADV7180**

# **TABLE OF CONTENTS**

| Features                                     | 1    | Video Processor                                       | 26    |

|----------------------------------------------|------|-------------------------------------------------------|-------|

| General Description                          | 1    | SD Luma Path                                          | 26    |

| Applications                                 | 1    | SD Chroma Path                                        | 26    |

| Functional Block Diagram                     | 1    | Sync Processing                                       | 27    |

| Revision History                             | 3    | VBI Data Recovery                                     | 27    |

| Introduction                                 | 5    | General Setup                                         | 27    |

| Analog Front End                             | 5    | Color Controls                                        | 29    |

| Standard Definition Processor                | 5    | Clamp Operation                                       | 31    |

| Functional Block Diagrams                    | 6    | Luma Filter                                           | 32    |

| Specifications                               | 8    | Chroma Filter                                         | 35    |

| Electrical Characteristics                   | 8    | Gain Operation                                        | 36    |

| Video Specifications                         | 9    | Chroma Transient Improvement (CTI)                    | 40    |

| Timing Specifications                        | . 10 | Digital Noise Reduction (DNR) and Luma Peaking Filter | 41    |

| Analog Specifications                        | . 11 | Comb Filters                                          | 42    |

| Thermal Specifications                       | . 11 | IF Filter Compensation                                | 44    |

| Absolute Maximum Ratings                     | . 12 | AV Code Insertion and Controls                        | 45    |

| ESD Caution                                  | . 12 | Synchronization Output Signals                        | 47    |

| Pin Configurations and Function Descriptions | . 13 | Sync Processing                                       | 54    |

| 32-Lead LFCSP                                | . 13 | VBI Data Decode                                       | 54    |

| 40-Lead LFCSP                                | . 14 | I <sup>2</sup> C Readback Registers                   | 63    |

| 64-Lead LQFP                                 | . 15 | Pixel Port Configuration                              | 76    |

| 48-Lead LQFP                                 | . 17 | GPO Control                                           | 77    |

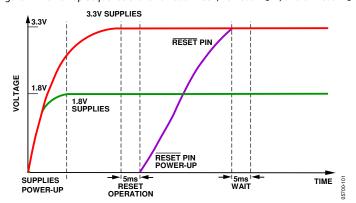

| Power Supply Sequencing                      | . 18 | MPU Port Description                                  | 78    |

| Power-Up Sequence                            | . 18 | Register Access                                       | 79    |

| Power-Down Sequence                          | . 18 | Register Programming                                  | 79    |

| Universal Power Supply                       | . 18 | I <sup>2</sup> C Sequencer                            | 79    |

| Analog Front End                             | . 19 | I <sup>2</sup> C Register Maps                        | 80    |

| Input Configuration                          | . 20 | PCB Layout Recommendations                            | . 107 |

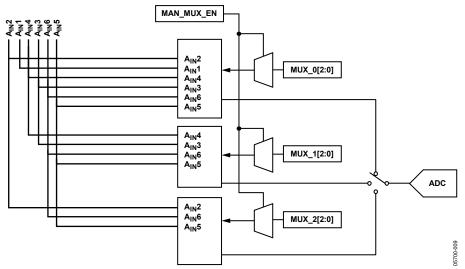

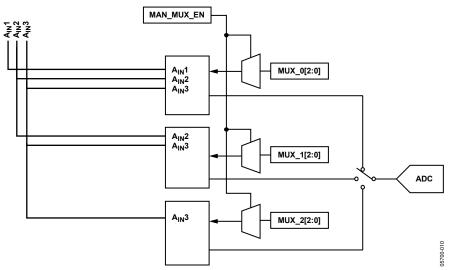

| Analog Input Muxing                          | . 21 | Analog Interface Inputs                               | . 107 |

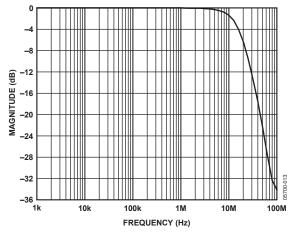

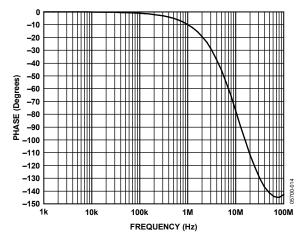

| Antialiasing Filters                         | . 22 | Power Supply Decoupling                               | . 107 |

| Global Control Registers                     | . 23 | PLL                                                   | . 107 |

| Power-Saving Modes                           | . 23 | VREFN and VREFP                                       | . 107 |

| Reset Control                                | . 23 | Digital Outputs (Both Data and Clocks)                | . 107 |

| Global Pin Control                           | . 23 | Digital Inputs                                        | . 107 |

| Global Status Register                       | . 25 | Typical Circuit Connection                            | . 108 |

| Identification                               | . 25 | Outline Dimensions                                    | . 112 |

| Status 1                                     | . 25 | Ordering Guide                                        | . 114 |

| Autodetection Result                         | . 25 | Automotive Products                                   | . 114 |

| Status 2                                     | . 25 |                                                       |       |

| Status 3                                     | . 25 |                                                       |       |

**REVISION HISTORY**

| 1/15—Rev. 1 to Rev. )                                        | //10—Rev. E to Rev. F                                                          |

|--------------------------------------------------------------|--------------------------------------------------------------------------------|

| Changes to Table 38                                          | Added 48-Lead LQFPThroughout                                                   |

| Changes to Table 16, Table 17, and Table 1824                | Changes to Features Section1                                                   |

| Changes to Table 10799                                       | Changes to Table 24                                                            |

| Updated Outline Dimensions112                                | Added Figure 5; Renumbered Sequentially6                                       |

| Changes to Ordering Guide114                                 | Added Input Current (SDA, SCLK) Parameter and Input                            |

|                                                              | Current (PWRDWN) Parameter, Table 37                                           |

| 2/14—Rev. H to Rev. I                                        | Added Figure 11 and Table 12; Renumbered Sequentially16                        |

| Changes to Figure 3 Caption and Figure 4 Caption6            | Changes to MAN_MUX_EN, Manual Input Muxing Enable,                             |

| Changes to Figure 710                                        | Address 0xC4[7] Section                                                        |

|                                                              | Added GDE_SEL_OLD_ADF Bit Description, Table 10792                             |

| 1/14—Rev. G to Rev. H                                        | Moved 32-Lead LFCSP Section                                                    |

| Changes to Figure 11                                         | Added Figure 58                                                                |

| Changes to Figure 3 and Figure 46                            | Updated Outline Dimensions115                                                  |

| Changes to Analog Supply Current Parameter, Table 38         | Changes to Ordering Guide                                                      |

| Changes to Data and Control Outputs Parameter, Table 510     | Changes to Cracking Garden                                                     |

| Added Power Supply Sequencing Section18                      | 2/10—Rev. D to Rev. E                                                          |

| Deleted Power-On RESET Section21                             | Added 32-Lead LFCSPThroughout                                                  |

| Changes to Drive Strength Selection Data Section24           | Changes to Features1                                                           |

| Changes to Luma Gain Section                                 | Changes to Figure 1                                                            |

| Changes to Comb Filters Section42                            | Changes to Introduction                                                        |

| Changes to Table 10580                                       | Added Figure 4, Renumbered Sequentially8                                       |

| Deleted Register Select (SR7 to SR0) Section81               | Added Figure 9 and Table 1114                                                  |

| Changes to Table 10784                                       | Changes to Figure 11                                                           |

| Changes to Table 108 and Table Summary Statement100          | e e                                                                            |

| Deleted I <sup>2</sup> C Programming Examples Section106     | Changes to Payer On Paset Section Apples Input Maying                          |

| Updated Outline Dimensions (Lead-to-Pad Dimension)112        | Changes to Power-On Reset Section, Analog Input Muxing Section, and Table 1417 |

| Opdated Odthlie Diffiensions (Lead-to-Fad Diffiension)112    |                                                                                |

| 3/12—Rev. F to Rev. G                                        | Changes to PDBP Section and TOD Section                                        |

| Changed ADV7179 to ADV7391 Throughout1                       | Changes to Identification Section                                              |

| Changes to Figure 1218                                       | Changes to VS and FIELD Configuration Section and SQPE                         |

| Changes to Table 14                                          | Section                                                                        |

| Changes to Power-On RESET Section and MAN_MUX_EN,            | Changes to Table 99 and Table 100                                              |

| · ·                                                          | Changes to GPO Control Section                                                 |

| Manual Input Muxing Enable, Address 0xC4[7] Section20        | Changes to Table 104                                                           |

| Changed NTSM to NTSC Throughout                              | Changes to Table 106                                                           |

| Deleted ADV7190, ADV7191, and ADV7192 Throughout27           | Added Figure 56                                                                |

| Change to DEF_C[7:0], Default Value C, Address 0x0D[7:0]     | Added Figure 59                                                                |

| Section                                                      | Changes to Ordering Guide110                                                   |

| Changes to Luma Filter Section                               | Cloop B. Cu B. B.                                                              |

| Changes to Table 39 and LAGT[1:0], Luma Automatic Gain       | 6/09—Rev. C to Rev. D                                                          |

| Timing, Address 0x2F[7:6] Section                            | Change to General Description                                                  |

| Changed Calculation of the Luma Calibration Factor Section   | Deleted Comparison with the ADV7181B Section5                                  |

| Heading to Calculation of the Chroma Calibration Factor      | Deleted Figure 2; Renumbered Sequentially5                                     |

| Section                                                      | Changes to Power Requirements Parameter, Table 26                              |

| Changes to Range, Range Selection, Address 0x04[0] Section45 | Changes to Table 29                                                            |

| Changes to PHS, Polarity HS, Address 0x37[7] Section46       | Changes to Figure 3344                                                         |

| Changes to 0x0D, 0x1D, 0x2C, 0x37, and 0x41, Table 10785     | Changes to Subaddress 0x0A Notes, Table 10481                                  |

| Changes to Power Supply Decoupling Section110                | Changes to Ordering Guide110                                                   |

| Deleted Figure 55; Renumbered Sequentially110                |                                                                                |

| Changes to Figure 55111                                      |                                                                                |

| Changes to Figure 56112                                      |                                                                                |

| Changes to Figure 57113                                      |                                                                                |

| Changes to Figure 58114                                      |                                                                                |

| Changes to Ordering Guide117                                 |                                                                                |

| 4/09—Rev. B to Rev. C                                      |    |

|------------------------------------------------------------|----|

| Changes to Features Section                                | 1  |

| Changes to Absolute Maximum Ratings, Table 7               | 11 |

| Changes to Figure 7 and Table 8, EPAD Addition             |    |

| Added Power-On RESET Section                               |    |

| Changes to MAN_MUX_EN, Manual Input Muxing Enable,         |    |

| Address 0xC4[7] Section and Table 12                       | 17 |

| Changes to Identification Section                          | 21 |

| Added Table 16; Renumbered Sequentially                    | 21 |

| Changes to Table 21                                        | 23 |

| Changes to CIL[2:0], Count Into Lock, Address 0x51[2:0]    |    |

| Section and COL[2:0], Count Out of Lock, Address 0x51[5:3] |    |

| Section                                                    | 25 |

| Changes to Table 32 and Table 33                           | 30 |

| Changes to Table 34                                        | 32 |

| Changes to Table 42                                        | 35 |

| Changes to Table 52                                        | 38 |

| Changes to Table 53 and Table 56                           | 39 |

| Changes to Table 61 and Figure 32                          | 43 |

| Added SQPE, Square Pixel Mode, Address 0x01[2] Section     | 44 |

| Changes to NEWAVMODE, New AV Mode, Address 0x31[4]         |    |

| Section                                                    | 44 |

| Changes to Figure 34                                       | 45 |

| Changes to NFTOG[4:0], NTSC Field Toggle,                  |    |

| Address 0xE7[4:0] Section                                  | 47 |

| Changes to PFTOG, PAL Field Toggle, Address 0xEA[4:0]      |    |

| Section                                                    | 49 |

| Changes to VDP Manuel Configuration Section                | 50 |

| Changes to Table 66                                        | 51 |

| Changes to Table 71                                        | 54 |

| Changes to Table 72                                        | 55 |

| Changes to VPS Section and PDC/UTC Section                 | 63 |

| Changes to Gemstar_2x Format, Half-Byte Output Mode        |    |

| Section                                                    | 66 |

| Changes to NTSC CCAP Data Section and PAL CCAP Data        |    |

| Section                                                    |    |

| Changes to Figure 48                                       |    |

| Changes to I <sup>2</sup> C Sequencer Section              | 75 |

| Changes to Table 102                                       | 76 |

| Changes to Table 104                                       | 80 |

| Changes to Table 105                                       | 97 |

| Changes to Figure 531                                      |    |

| Changes to Figure 541                                      |    |

| Added Exposed Paddle Notation to Outline Dimensions 1      | 10 |

| Changes to Ordering Guide                                  | 11 |

| 2/U/—Rev. A to Rev. B                             |        |

|---------------------------------------------------|--------|

| Changes to SFL_INV, Subcarrier Frequency Lock Inv | ersion |

| Section                                           | 24     |

| Changes to Table 103, Register 0x41               | 90     |

| Updated Outline Dimensions                        | 111    |

|                                                   |        |

| 11/06—Rev. 0 to Rev. A                            |        |

| Changes to Table 10 and Table 11                  | 16     |

| Changes to Table 30                               | 28     |

| Changes to Gain Operation Section                 | 33     |

| Changes to Table 43                               | 35     |

| Changes to Table 97                               | 72     |

| Changes to Table 99                               |        |

| Changes to Table 103                              | 80     |

| Changes to Figure 54                              |        |

| 8 8                                               |        |

### INTRODUCTION

The ADV7180 is a versatile one-chip multiformat video decoder that automatically detects and converts PAL, NTSC, and SECAM standards in the form of composite, S-Video, and component video into a digital ITU-R BT.656 format.

The simple digital output interface connects gluelessly to a wide range of MPEG encoders, codecs, mobile video processors, and Analog Devices digital video encoders, such as the ADV7391. External HS, VS, and FIELD signals provide timing references for LCD controllers and other video ASICs that do not support the ITU-R BT.656 interface standard. The different package options available for the ADV7180 are shown in Table 2.

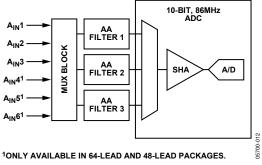

#### **ANALOG FRONT END**

The ADV7180 analog front end comprises a single high speed, 10-bit analog-to-digital converter (ADC) that digitizes the analog video signal before applying it to the standard definition processor. The analog front end employs differential channels to the ADC to ensure high performance in mixed-signal applications.

The front end also includes a 3-channel input mux that enables multiple composite video signals to be applied to the ADV7180. Current clamps are positioned in front of the ADC to ensure that the video signal remains within the range of the converter. A resistor divider network is required before each analog input channel to ensure that the input signal is kept within the range of the ADC (see Figure 29). Fine clamping of the video signal is performed downstream by digital fine clamping within the ADV7180.

Table 1 shows the three ADC clocking rates that are determined by the video input format to be processed—that is, INSEL[3:0]. These clock rates ensure 4× oversampling per channel for CVBS mode and 2× oversampling per channel for Y/C and YPrPb modes.

Table 1. ADC Clock Rates

| Input Format                        | ADC Clock Rate (MHz) <sup>1</sup> | Oversampling<br>Rate per Channel |

|-------------------------------------|-----------------------------------|----------------------------------|

| CVBS                                | 57.27                             | 4×                               |

| Y/C (S-Video) <sup>2</sup><br>YPrPb | 86                                | 2×                               |

| YPrPb                               | 86                                | 2×                               |

<sup>&</sup>lt;sup>1</sup> Based on a 28.6363 MHz crystal between the XTAL and XTAL1 pins.

#### STANDARD DEFINITION PROCESSOR

The ADV7180 is capable of decoding a large selection of baseband video signals in composite, S-Video, and component formats. The video standards supported by the video processor include PAL B/D/I/G/H, PAL 60, PAL M, PAL N, PAL Nc, NTSC M/J, NTSC 4.43, and SECAM B/D/G/K/L. The ADV7180 can automatically detect the video standard and process it accordingly.

The ADV7180 has a five-line, superadaptive, 2D comb filter that gives superior chrominance and luminance separation when decoding a composite video signal. This highly adaptive filter automatically adjusts its processing mode according to the video standard and signal quality without requiring user intervention. Video user controls such as brightness, contrast, saturation, and hue are also available with the ADV7180.

The ADV7180 implements a patented ADLLT<sup>™</sup> algorithm to track varying video line lengths from sources such as a VCR. ADLLT enables the ADV7180 to track and decode poor quality video sources such as VCRs and noisy sources from tuner outputs, VCD players, and camcorders. The ADV7180 contains a chroma transient improvement (CTI) processor that sharpens the edge rate of chroma transitions, resulting in sharper vertical transitions.

The video processor can process a variety of VBI data services, such as closed captioning (CCAP), wide screen signaling (WSS), copy generation management system (CGMS), EDTV, Gemstar\* 1×/2×, and extended data service (XDS). Teletext data slicing for world standard teletext (WST), along with program delivery control (PDC) and video programming service (VPS), are provided. Data is transmitted via the 8-bit video output port as ancillary data packets (ANC). The ADV7180 is fully Macrovision\* certified; detection circuitry enables Type I, Type II, and Type III protection levels to be identified and reported to the user. The decoder is also fully robust to all Macrovision signal inputs.

Table 2. ADV7180 Selection Guide

| Part Number <sup>1</sup>    | Package Type  | Analog Inputs | Digital Outputs | Temperature Grade |

|-----------------------------|---------------|---------------|-----------------|-------------------|

| ADV7180KCP32Z               | 32-lead LFCSP | 3             | 8-bit           | −10°C to +70°C    |

| ADV7180WBCP32Z (Automotive) | 32-lead LFCSP | 3             | 8-bit           | -40°C to +85°C    |

| ADV7180BCPZ                 | 40-lead LFCSP | 3             | 8-bit           | -40°C to +85°C    |

| ADV7180WBCPZ (Automotive)   | 40-lead LFCSP | 3             | 8-bit           | -40°C to +125°C   |

| ADV7180BSTZ                 | 64-lead LQFP  | 6             | 8-bit/16-bit    | -40°C to +85°C    |

| ADV7180WBSTZ (Automotive)   | 64-lead LQFP  | 6             | 8-bit/16-bit    | -40°C to +125°C   |

| ADV7180WBST48Z (Automotive) | 48-lead LQFP  | 6             | 8-bit           | −40°C to +85°C    |

$<sup>^{1}</sup>$  W = Automotive qualification completed.

<sup>&</sup>lt;sup>2</sup> See INSEL[3:0] in Table 107 for the mandatory write for Y/C (S-Video) mode.

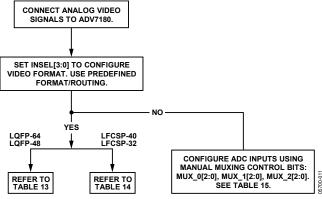

# **FUNCTIONAL BLOCK DIAGRAMS**

Figure 2. 32-Lead LFCSP Functional Diagram

Figure 3. 64-Lead LQFP Functional Block Diagram

Figure 4. 40-Lead LFCSP Functional Block Diagram

Figure 5. 48-Lead LQFP Functional Block Diagram

# **SPECIFICATIONS**

#### **ELECTRICAL CHARACTERISTICS**

A<sub>VDD</sub> = 1.71 V to 1.89 V, D<sub>VDD</sub> = 1.65 V to 2.0 V, D<sub>VDDIO</sub> = 1.62 V to 3.6 V, P<sub>VDD</sub> = 1.65 V to 2.0 V, specified at operating temperature range, unless otherwise noted.

Table 3.

| Parameter                                   | Symbol                    | Test Conditions/Comments     | Min  | Тур       | Max  | Uni  |

|---------------------------------------------|---------------------------|------------------------------|------|-----------|------|------|

| STATIC PERFORMANCE                          |                           |                              |      |           |      |      |

| Resolution (Each ADC)                       | N                         |                              |      |           | 10   | Bits |

| Integral Nonlinearity                       | INL                       | BSL in CVBS mode             |      | 2         |      | LSB  |

| Differential Nonlinearity                   | DNL                       | CVBS mode                    |      | -0.6/+0.6 |      | LSB  |

| DIGITAL INPUTS                              |                           |                              |      |           |      |      |

| Input High Voltage (DVDDIO = 3.3 V)         | V <sub>IH</sub>           |                              | 2    |           |      | ٧    |

| Input High Voltage (DVDDIO = 1.8 V)         | V <sub>IH</sub>           |                              | 1.2  |           |      | V    |

| Input Low Voltage (DVDDIO = 3.3 V)          | V <sub>IL</sub>           |                              |      |           | 0.8  | V    |

| Input Low Voltage (DVDDIO = 1.8 V)          | V <sub>IL</sub>           |                              |      |           | 0.4  | ٧    |

| Crystal Inputs                              | V <sub>IH</sub>           |                              | 1.2  |           |      | ٧    |

|                                             | VIL                       |                              |      |           | 0.4  | ٧    |

| Input Current                               | I <sub>IN</sub>           |                              | -10  |           | +10  | μΑ   |

| Input Current (SDA, SCLK) <sup>1</sup>      | I <sub>IN</sub>           |                              | -10  |           | +15  | μΑ   |

| Input Current (PWRDWN) <sup>2</sup>         | I <sub>IN</sub>           |                              | -10  |           | +48  | μΑ   |

| Input Capacitance                           | C <sub>IN</sub>           |                              |      |           | 10   | рF   |

| DIGITAL OUTPUTS                             |                           |                              |      |           |      |      |

| Output High Voltage (DVDDIO = 3.3 V)        | V <sub>OH</sub>           | I <sub>SOURCE</sub> = 0.4 mA | 2.4  |           |      | V    |

| Output High Voltage (DVDDIO = 1.8 V)        | V <sub>OH</sub>           | I <sub>SOURCE</sub> = 0.4 mA | 1.4  |           |      | V    |

| Output Low Voltage (DVDDIO = 3.3 V)         | Vol                       | I <sub>SINK</sub> = 3.2 mA   |      |           | 0.4  | V    |

| Output Low Voltage (DVDDIO = 1.8 V)         | Vol                       | I <sub>SINK</sub> = 1.6 mA   |      |           | 0.2  | V    |

| High Impedance Leakage Current              | I <sub>LEAK</sub>         |                              |      |           | 10   | μΑ   |

| Output Capacitance                          | Соит                      |                              |      |           | 20   | рF   |

| POWER REQUIREMENTS <sup>3, 4, 5</sup>       |                           |                              |      |           |      |      |

| Digital Power Supply                        | D <sub>VDD</sub>          |                              | 1.65 | 1.8       | 2    | V    |

| Digital I/O Power Supply                    | D <sub>VDDIO</sub>        |                              | 1.62 | 3.3       | 3.6  | V    |

| PLL Power Supply                            | P <sub>VDD</sub>          |                              | 1.65 | 1.8       | 2.0  | V    |

| Analog Power Supply                         | A <sub>VDD</sub>          |                              | 1.71 | 1.8       | 1.89 | V    |

| Digital Supply Current                      | I <sub>DVDD</sub>         |                              |      | 77        | 85   | mA   |

| Digital I/O Supply Current <sup>6</sup>     | I <sub>DVDDIO</sub>       |                              |      | 3         | 5    | mA   |

| PLL Supply Current                          | I <sub>PVDD</sub>         |                              |      | 12        | 15   | mA   |

| Analog Supply Current                       | l <sub>AVDD</sub>         | CVBS input <sup>7</sup>      |      | 33        | 43   | mA   |

|                                             |                           | CVBS input <sup>8</sup>      |      | 43        | 53   | mA   |

|                                             |                           | Y/C input                    |      | 59        | 75   | mA   |

|                                             |                           | YPrPb input                  |      | 77        | 94   | mA   |

| Power-Down Current                          | I <sub>DVDD</sub>         |                              |      | 6         | 10   | μΑ   |

|                                             | I <sub>DVDDIO</sub>       |                              |      | 0.1       | 1    | μΑ   |

|                                             | I <sub>PVDD</sub>         |                              |      | 1         | 5    | μΑ   |

|                                             | I <sub>AVDD</sub>         |                              |      | 1         | 5    | μΑ   |

| Total Power Dissipation in Power-Down Mode9 |                           |                              |      | 15        | 44   | μW   |

| Power-Up Time                               | <b>t</b> <sub>PWRUP</sub> |                              |      | 20        |      | ms   |

<sup>&</sup>lt;sup>1</sup> ADV7180KCP32Z, ADV7180WBCP32Z, and ADV7180WBST48Z only.

<sup>2</sup> Applies to ADV7180WBST48Z, ADV7180WBST48Z-RL, ADV7180KST48Z, ADV7180KST48Z-RL, ADV7180BST48Z, ADV7180BST48Z-RL only.

<sup>&</sup>lt;sup>3</sup> Guaranteed by characterization.

<sup>&</sup>lt;sup>4</sup> Typical current consumption values are recorded with nominal voltage supply levels and a SMPTEBAR pattern.

<sup>&</sup>lt;sup>5</sup> Maximum current consumption values are recorded with maximum rated voltage supply levels and a multiburst pattern. <sup>6</sup> Typical (Typ) number is measured with DVDDIO = 3.3 V and maximum (Max) number is measured with DVDDIO = 3.6 V.

<sup>&</sup>lt;sup>7</sup> CVBS input when CVBS\_IBIAS[3:0] (User Map, Register 0x52, Bits[3:0]) equal 0b'1011.

<sup>&</sup>lt;sup>8</sup> CVBS input when CVBS\_IBIAS[3:0] (User Map, Register 0x52, Bits [3:0]) equal 0b'1101. Recommended setting.

<sup>&</sup>lt;sup>9</sup> ADV7180 clocked.

### **VIDEO SPECIFICATIONS**

Guaranteed by characterization.  $A_{\rm VDD}$  = 1.71 V to 1.89 V,  $D_{\rm VDD}$  = 1.65 V to 2.0 V,  $D_{\rm VDDIO}$  = 1.62 V to 3.6 V,  $P_{\rm VDD}$  = 1.65 V to 2.0 V, specified at operating temperature range, unless otherwise noted.

Table 4.

| Parameter                             | Symbol | Test Conditions/Comments              | Min | Тур  | Max | Unit    |

|---------------------------------------|--------|---------------------------------------|-----|------|-----|---------|

| NONLINEAR SPECIFICATIONS              |        |                                       |     |      |     |         |

| Differential Phase                    | DP     | CVBS input, modulate five-step [NTSC] |     | 0.6  |     | Degrees |

| Differential Gain                     | DG     | CVBS input, modulate five-step [NTSC] |     | 0.5  |     | %       |

| Luma Nonlinearity                     | LNL    | CVBS input, five-step [NTSC]          |     | 2.0  |     | %       |

| NOISE SPECIFICATIONS                  |        |                                       |     |      |     |         |

| SNR Unweighted                        |        | Luma ramp                             |     | 57.1 |     | dB      |

|                                       |        | Luma flat field                       |     | 58   |     | dB      |

| Analog Front-End Crosstalk            |        |                                       |     | 60   |     | dB      |

| LOCK TIME SPECIFICATIONS              |        |                                       |     |      |     |         |

| Horizontal Lock Range                 |        |                                       | -5  |      | +5  | %       |

| Vertical Lock Range                   |        |                                       | 40  |      | 70  | Hz      |

| f <sub>SC</sub> Subcarrier Lock Range |        |                                       |     | ±1.3 |     | kHz     |

| Color Lock-In Time                    |        |                                       |     | 60   |     | Lines   |

| Sync Depth Range                      |        |                                       | 20  |      | 200 | %       |

| Color Burst Range                     |        |                                       | 5   |      | 200 | %       |

| Vertical Lock Time                    |        |                                       |     | 2    |     | Fields  |

| Autodetection Switch Speed            |        |                                       |     | 100  |     | Lines   |

| Chroma Luma Gain Delay                | CVBS   |                                       |     | 2.9  |     | ns      |

|                                       | Y/C    |                                       |     | 5.6  |     | ns      |

|                                       | YPrPb  |                                       |     | -3.0 |     | ns      |

| LUMA SPECIFICATIONS                   |        |                                       |     |      |     |         |

| Luma Brightness Accuracy              |        | CVBS, 1 V input                       |     | 1    |     | %       |

| Luma Contrast Accuracy                |        | CVBS, 1 V input                       |     | 1    |     | %       |

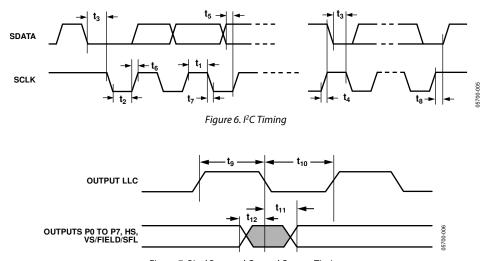

#### **TIMING SPECIFICATIONS**

Guaranteed by characterization.  $A_{VDD} = 1.71~V$  to 1.89~V,  $D_{VDD} = 1.65~V$  to 2.0~V,  $D_{VDDIO} = 1.62~V$  to 3.6~V,  $P_{VDD} = 1.65~V$  to 2.0~V, specified at operating temperature range, unless otherwise noted.

Table 5.

| Parameter                     | Symbol                | Test Conditions                                                            | Min   | Тур     | Max   | Unit         |

|-------------------------------|-----------------------|----------------------------------------------------------------------------|-------|---------|-------|--------------|

| SYSTEM CLOCK AND CRYSTAL      |                       |                                                                            |       |         |       |              |

| Nominal Frequency             |                       |                                                                            |       | 28.6363 |       | MHz          |

| Frequency Stability           |                       |                                                                            |       |         | ±50   | ppm          |

| I <sup>2</sup> C PORT         |                       |                                                                            |       |         |       |              |

| SCLK Frequency                |                       |                                                                            |       |         | 400   | kHz          |

| SCLK Minimum Pulse Width High | t <sub>1</sub>        |                                                                            | 0.6   |         |       | μs           |

| SCLK Minimum Pulse Width Low  | t <sub>2</sub>        |                                                                            | 1.3   |         |       | μs           |

| Hold Time (Start Condition)   | t <sub>3</sub>        |                                                                            | 0.6   |         |       | μs           |

| Setup Time (Start Condition)  | <b>t</b> 4            |                                                                            | 0.6   |         |       | μs           |

| SDA Setup Time                | <b>t</b> <sub>5</sub> |                                                                            | 100   |         |       | ns           |

| SCLK and SDA Rise Times       | <b>t</b> 6            |                                                                            |       |         | 300   | ns           |

| SCLK and SDA Fall Times       | <b>t</b> <sub>7</sub> |                                                                            |       |         | 300   | ns           |

| Setup Time for Stop Condition | t <sub>8</sub>        |                                                                            |       | 0.6     |       | μs           |

| RESET FEATURE                 |                       |                                                                            |       |         |       |              |

| Reset Pulse Width             |                       |                                                                            | 5     |         |       | ms           |

| CLOCK OUTPUTS                 |                       |                                                                            |       |         |       |              |

| LLC Mark Space Ratio          | t9:t10                |                                                                            | 45:55 |         | 55:45 | % duty cycle |

| DATA AND CONTROL OUTPUTS      |                       |                                                                            |       |         |       |              |

| Data Output Transitional Time | t <sub>11</sub>       | Negative clock edge to start of valid data $(t_{SETUP} = t_{10} - t_{11})$ |       |         | 3.6   | ns           |

| Data Output Transitional Time | t <sub>12</sub>       | End of valid data to negative clock edge $(t_{HOLD} = t_9 - t_{12})$       |       |         | 2.4   | ns           |

### **Timing Diagrams**

Figure 7. Pixel Port and Control Output Timing

### **ANALOG SPECIFICATIONS**

Guaranteed by characterization.  $A_{VDD} = 1.71~V$  to 1.89~V,  $D_{VDD} = 1.65~V$  to 2.0~V,  $D_{VDDIO} = 1.62~V$  to 3.6~V,  $P_{VDD} = 1.65~V$  to 2.0~V, specified at operating temperature range, unless otherwise noted.

#### Table 6.

| Parameter                  | Test Conditions     | Min | Тур | Max | Unit |

|----------------------------|---------------------|-----|-----|-----|------|

| CLAMP CIRCUITRY            |                     |     |     |     |      |

| External Clamp Capacitor   |                     |     | 0.1 |     | μF   |

| Input Impedance            | Clamps switched off |     | 10  |     | ΜΩ   |

| Large-Clamp Source Current |                     |     | 0.4 |     | mA   |

| Large-Clamp Sink Current   |                     |     | 0.4 |     | mA   |

| Fine Clamp Source Current  |                     |     | 10  |     | μΑ   |

| Fine Clamp Sink Current    |                     |     | 10  |     | μΑ   |

#### THERMAL SPECIFICATIONS

Table 7.

| Parameter                                             | Symbol        | Test Conditions                                      | Min | Тур  | Max | Unit |

|-------------------------------------------------------|---------------|------------------------------------------------------|-----|------|-----|------|

| THERMAL CHARACTERISTICS                               |               |                                                      |     |      |     |      |

| Junction-to-Ambient Thermal<br>Resistance (Still Air) | $\theta_{JA}$ | 4-layer PCB with solid ground plane, 32-lead LFCSP   |     | 32.5 |     | °C/W |

| Junction-to-Case Thermal Resistance                   | θις           | 4-layer PCB with solid ground plane, 32-lead LFCSP   |     | 2.3  |     | °C/W |

| Junction-to-Ambient Thermal<br>Resistance (Still Air) | $\theta_{JA}$ | 4-layer PCB with solid ground plane, 40-lead LFCSP   |     | 30   |     | °C/W |

| Junction-to-Case Thermal Resistance                   | θις           | 4-layer PCB with solid ground plane, 40-lead LFCSP   |     | 3    |     | °C/W |

| Junction-to-Ambient Thermal<br>Resistance (Still Air) | $\theta_{JA}$ | 4-layer PCB with solid ground plane, 64-lead LQFP 47 |     | 47   |     | °C/W |

| Junction-to-Case Thermal Resistance                   | θις           | 4-layer PCB with solid ground plane, 64-lead LQFP    |     | 11.1 |     | °C/W |

| Junction-to-Ambient Thermal<br>Resistance (Still Air) | ӨЈА           | 4-layer PCB with solid ground plane, 48-lead LQFP    |     | 50   |     | °C/W |

| Junction-to-Case Thermal Resistance                   | θις           | 4-layer PCB with solid ground plane, 48-lead LQFP    |     | 20   |     | °C/W |

# **ABSOLUTE MAXIMUM RATINGS**

#### Table 8.

| Table 6.                                          |                                            |

|---------------------------------------------------|--------------------------------------------|

| Parameter                                         | Rating                                     |

| A <sub>VDD</sub> to AGND                          | 2.2 V                                      |

| D <sub>VDD</sub> to DGND                          | 2.2 V                                      |

| P <sub>VDD</sub> to AGND                          | 2.2 V                                      |

| D <sub>VDDIO</sub> to DGND                        | 4 V                                        |

| Dyddio to Aydd                                    | −0.3 V to +4 V                             |

| P <sub>VDD</sub> to D <sub>VDD</sub>              | −0.3 V to +0.9 V                           |

| Dyddio to Pydd                                    | -0.3 V to +4 V                             |

| D <sub>VDDIO</sub> to D <sub>VDD</sub>            | −0.3 V to +4 V                             |

| A <sub>VDD</sub> to P <sub>VDD</sub>              | −0.3 V to +0.3 V                           |

| $A_{VDD}$ to $D_{VDD}$                            | −0.3 V to +0.9 V                           |

| Digital Inputs Voltage                            | DGND - 0.3 V to D <sub>VDDIO</sub> + 0.3 V |

| Digital Outputs Voltage                           | DGND – 0.3 V to D <sub>VDDIO</sub> + 0.3 V |

| Analog Inputs to AGND                             | AGND – 0.3 V to A <sub>VDD</sub> + 0.3 V   |

| Maximum Junction Temperature (T <sub>1</sub> max) | 140°C                                      |

| Storage Temperature Range                         | −65°C to +150°C                            |

| Infrared Reflow Soldering (20 sec)                | 260°C                                      |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

This device is a high performance integrated circuit with an ESD rating of <2 kV, and it is ESD sensitive. Proper precautions should be taken for handling and assembly.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

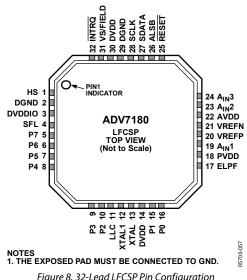

# PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS **32-LEAD LFCSP**

Figure 8. 32-Lead LFCSP Pin Configuration

Table 9. 32-Lead LFCSP Pin Function Descriptions

| Pin No.         | Mnemonic                               | Туре | Description                                                                                                                                                                                                                  |  |  |  |

|-----------------|----------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1               | HS                                     | 0    | Horizontal Synchronization Output Signal.                                                                                                                                                                                    |  |  |  |

| 2, 29           | DGND                                   | G    | Ground for Digital Supply.                                                                                                                                                                                                   |  |  |  |

| 3               | DVDDIO                                 | Р    | Digital I/O Supply Voltage (1.8 V to 3.3 V).                                                                                                                                                                                 |  |  |  |

| 4               | SFL                                    | 0    | Subcarrier Frequency Lock. This pin contains a serial output stream that can be used to lock the subcarrier frequency when this decoder is connected to any Analog Devices digital video encoder.                            |  |  |  |

| 5 to 10, 15, 16 | P7 to P2, P1, P0                       | 0    | Video Pixel Output Port.                                                                                                                                                                                                     |  |  |  |

| 11              | LLC                                    | 0    | Line-Locked Output Clock for the Output Pixel Data. Nominally 27 MHz but varies up or down according to video line length.                                                                                                   |  |  |  |

| 12              | XTAL1                                  | 0    | This pin should be connected to the 28.6363 MHz crystal or not connected if an external 1.8 V, 28.6363 MHz clock oscillator source is used to clock the ADV7180. In crystal mode, the crystal must be a fundamental crystal. |  |  |  |

| 13              | XTAL                                   | 1    | Input Pin for the 28.6363 MHz Crystal. This pin can be overdriven by an external 1.8 V, 28.6363 MHz clock oscillator source. In crystal mode, the crystal must be a fundamental crystal.                                     |  |  |  |

| 14, 30          | DVDD                                   | Р    | Digital Supply Voltage (1.8 V).                                                                                                                                                                                              |  |  |  |

| 17              | ELPF                                   | 1    | The recommended external loop filter must be connected to this ELPF pin, as shown in Figure 60                                                                                                                               |  |  |  |

| 18              | PVDD                                   | Р    | PLL Supply Voltage (1.8 V).                                                                                                                                                                                                  |  |  |  |

| 19, 23, 24      | A <sub>IN</sub> 1 to A <sub>IN</sub> 3 | 1    | Analog Video Input Channels.                                                                                                                                                                                                 |  |  |  |

| 20              | VREFP                                  | 0    | Internal Voltage Reference Output. See Figure 60 for recommended output circuitry.                                                                                                                                           |  |  |  |

| 21              | VREFN                                  | 0    | Internal Voltage Reference Output. See Figure 60 for recommended output circuitry.                                                                                                                                           |  |  |  |

| 22              | AVDD                                   | Р    | Analog Supply Voltage (1.8 V).                                                                                                                                                                                               |  |  |  |

| 25              | RESET                                  | 1    | System Reset Input. Active low. A minimum low reset pulse width of 5 ms is required to reset the ADV7180 circuitry.                                                                                                          |  |  |  |

| 26              | ALSB                                   | 1    | This pin selects the I <sup>2</sup> C address for the ADV7180. For ALSB set to Logic 0, the address selected for a write is Address 0x40; for ALSB set to Logic 1, the address selected is Address 0x42.                     |  |  |  |

| 27              | SDATA                                  | I/O  | I <sup>2</sup> C Port Serial Data Input/Output Pin.                                                                                                                                                                          |  |  |  |

| 28              | SCLK                                   | 1    | I <sup>2</sup> C Port Serial Clock Input. The maximum clock rate is 400 kHz.                                                                                                                                                 |  |  |  |

| 31              | VS/FIELD                               | 0    | Vertical Synchronization Output Signal/Field Synchronization Output Signal.                                                                                                                                                  |  |  |  |

| 32              | ĪNTRQ                                  | 0    | Interrupt Request Output. Interrupt occurs when certain signals are detected on the input video (see Table 108).                                                                                                             |  |  |  |

|                 | EPAD (EP)                              |      | The exposed pad must be connected to GND.                                                                                                                                                                                    |  |  |  |

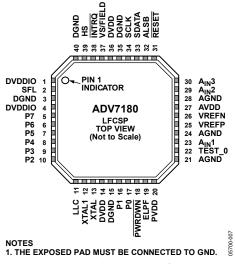

#### **40-LEAD LFCSP**

Figure 9. 40-Lead LFCSP Pin Configuration

**Table 10. 40-Lead LFCSP Pin Function Descriptions**

| Pin No.         | Mnemonic                               | Type | Description                                                                                                                                                                                                                  |  |  |  |

|-----------------|----------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1, 4            | DVDDIO                                 | Р    | Digital I/O Supply Voltage (1.8 V to 3.3 V).                                                                                                                                                                                 |  |  |  |

| 2               | SFL                                    | 0    | Subcarrier Frequency Lock. This pin contains a serial output stream that can be used to lock the subcarrier frequency when this decoder is connected to any Analog Devices digital video encoder.                            |  |  |  |

| 3, 15, 35, 40   | DGND                                   | G    | Ground for Digital Supply.                                                                                                                                                                                                   |  |  |  |

| 5 to 10, 16, 17 | P7 to P2, P1, P0                       | 0    | Video Pixel Output Port.                                                                                                                                                                                                     |  |  |  |

| 11              | LLC                                    | 0    | Line-Locked Output Clock for the Output Pixel Data. Nominally 27 MHz but varies up or down according to video line length.                                                                                                   |  |  |  |

| 12              | XTAL1                                  | 0    | This pin should be connected to the 28.6363 MHz crystal or not connected if an external 1.8 V, 28.6363 MHz clock oscillator source is used to clock the ADV7180. In crystal mode, the crystal must be a fundamental crystal. |  |  |  |

| 13              | XTAL                                   | I    | Input Pin for the 28.6363 MHz Crystal. This pin can be overdriven by an external 1.8 V, 28.6363 MHz clock oscillator source. In crystal mode, the crystal must be a fundamental crystal.                                     |  |  |  |

| 14, 36          | DVDD                                   | Р    | Digital Supply Voltage (1.8 V).                                                                                                                                                                                              |  |  |  |

| 18              | PWRDWN                                 | I    | A logic low on this pin places the ADV7180 into power-down mode.                                                                                                                                                             |  |  |  |

| 19              | ELPF                                   | 1    | The recommended external loop filter must be connected to this ELPF pin, as shown in Figure 5                                                                                                                                |  |  |  |

| 20              | PVDD                                   | Р    | PLL Supply Voltage (1.8 V).                                                                                                                                                                                                  |  |  |  |

| 21, 24, 28      | AGND                                   | G    | Ground for Analog Supply.                                                                                                                                                                                                    |  |  |  |

| 22              | TEST_0                                 | 1    | This pin must be tied to DGND.                                                                                                                                                                                               |  |  |  |

| 23, 29, 30      | A <sub>IN</sub> 1 to A <sub>IN</sub> 3 | 1    | Analog Video Input Channels.                                                                                                                                                                                                 |  |  |  |

| 25              | VREFP                                  | 0    | Internal Voltage Reference Output. See Figure 57 for recommended output circuitry.                                                                                                                                           |  |  |  |

| 26              | VREFN                                  | 0    | Internal Voltage Reference Output. See Figure 57 for recommended output circuitry.                                                                                                                                           |  |  |  |

| 27              | AVDD                                   | Р    | Analog Supply Voltage (1.8 V).                                                                                                                                                                                               |  |  |  |

| 31              | RESET                                  | I    | System Reset Input. Active low. A minimum low reset pulse width of 5 ms is required to reset the ADV7180 circuitry.                                                                                                          |  |  |  |

| 32              | ALSB                                   | I    | This pin selects the I <sup>2</sup> C address for the ADV7180. For ALSB set to Logic 0, the address selected for a write is Address 0x40; for ALSB set to Logic 1, the address selected is Address 0x42.                     |  |  |  |

| 33              | SDATA                                  | I/O  | I <sup>2</sup> C Port Serial Data Input/Output Pin.                                                                                                                                                                          |  |  |  |

| 34              | SCLK                                   | I    | l <sup>2</sup> C Port Serial Clock Input. The maximum clock rate is 400 kHz.                                                                                                                                                 |  |  |  |

| 37              | VS/FIELD                               | 0    | Vertical Synchronization Output Signal/Field Synchronization Output Signal.                                                                                                                                                  |  |  |  |

| 38              | ĪNTRQ                                  | 0    | Interrupt Request Output. Interrupt occurs when certain signals are detected on the input video (see Table 108).                                                                                                             |  |  |  |

| 39              | HS                                     | 0    | Horizontal Synchronization Output Signal.                                                                                                                                                                                    |  |  |  |

|                 | EPAD (EP)                              |      | The exposed pad must be connected to GND.                                                                                                                                                                                    |  |  |  |

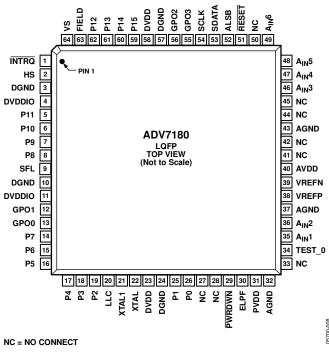

#### **64-LEAD LQFP**

Figure 10. 64-Lead LQFP Pin Configuration

Table 11. 64-Lead LQFP Pin Function Description

| Pin No.                               | Mnemonic                                      | Type | Description                                                                                                                                                                                                                         |  |  |  |

|---------------------------------------|-----------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1                                     | INTRQ                                         | 0    | Interrupt Request Output. Interrupt occurs when certain signals are detected on the input video (see Table 108).                                                                                                                    |  |  |  |

| 2                                     | HS                                            | 0    | Horizontal Synchronization Output Signal.                                                                                                                                                                                           |  |  |  |

| 3, 10, 24, 57                         | DGND                                          | G    | Digital Ground.                                                                                                                                                                                                                     |  |  |  |

| 4, 11                                 | DVDDIO                                        | Р    | Digital I/O Supply Voltage (1.8 V to 3.3 V).                                                                                                                                                                                        |  |  |  |

| 5 to 8, 14 to 19,<br>25, 26, 59 to 62 | P11 to P8,<br>P7 to P2, P1,<br>P0, P15 to P12 | 0    | Video Pixel Output Port. See Table 100 for output configuration for 8-bit and 16-bit modes.                                                                                                                                         |  |  |  |

| 9                                     | SFL                                           | 0    | Subcarrier Frequency Lock. This pin contains a serial output stream that can be used to lock the subcarrier frequency when this decoder is connected to any Analog Devices digital video encoder.                                   |  |  |  |

| 12, 13, 55, 56                        | GPO0 to GPO3                                  | 0    | General-Purpose Outputs. These pins can be configured via I <sup>2</sup> C to allow control of external device                                                                                                                      |  |  |  |

| 20                                    | LLC                                           | 0    | This is a line-locked output clock for the pixel data output by the ADV7180. It is nominally 27 MHz but varies up or down according to video line length.                                                                           |  |  |  |

| 21                                    | XTAL1                                         | 0    | This pin should be connected to the 28.6363 MHz crystal or left as a no connect if an external 1.8 V, 28.6363 MHz clock oscillator source is used to clock the ADV7180. In crystal mode, the crystal must be a fundamental crystal. |  |  |  |

| 22                                    | XTAL                                          | I    | This is the input pin for the 28.6363 MHz crystal, or this pin can be overdriven by an externa 1.8 V, 28.6363 MHz clock oscillator source. In crystal mode, the crystal must be a fundament crystal.                                |  |  |  |

| 23, 58                                | DVDD                                          | Р    | Digital Supply Voltage (1.8 V).                                                                                                                                                                                                     |  |  |  |

| 27, 28, 33, 41, 42,<br>44, 45, 50     | NC                                            |      | No Connect. These pins are not connected internally.                                                                                                                                                                                |  |  |  |

| 29                                    | PWRDWN                                        | 1    | A logic low on this pin places the ADV7180 in power-down mode.                                                                                                                                                                      |  |  |  |

| 30                                    | ELPF                                          | 1    | The recommended external loop filter must be connected to the ELPF pin, as shown in Figure 58.                                                                                                                                      |  |  |  |

| 31                                    | PVDD                                          | Р    | PLL Supply Voltage (1.8 V).                                                                                                                                                                                                         |  |  |  |

| 32, 37, 43                            | AGND                                          | G    | Analog Ground.                                                                                                                                                                                                                      |  |  |  |

| 34                                    | TEST_0                                        | 1    | This pin must be tied to DGND.                                                                                                                                                                                                      |  |  |  |

| 35, 36, 46 to 49                      | A <sub>IN</sub> 1 to A <sub>IN</sub> 6        | 1    | Analog Video Input Channels.                                                                                                                                                                                                        |  |  |  |

| 38                                    | VREFP                                         | 0    | Internal Voltage Reference Output. See Figure 58 for recommended output circuitry.                                                                                                                                                  |  |  |  |

| Pin No. | Mnemonic | Туре | Description                                                                                                                                                                                              |

|---------|----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 39      | VREFN    | 0    | Internal Voltage Reference Output. See Figure 58 for recommended output circuitry.                                                                                                                       |

| 40      | AVDD     | Р    | Analog Supply Voltage (1.8 V).                                                                                                                                                                           |

| 51      | RESET    | 1    | System Reset Input. Active low. A minimum low reset pulse width of 5 ms is required to reset the ADV7180 circuitry.                                                                                      |

| 52      | ALSB     | 1    | This pin selects the I <sup>2</sup> C address for the ADV7180. For ALSB set to Logic 0, the address selected for a write is Address 0x40; for ALSB set to Logic 1, the address selected is Address 0x42. |

| 53      | SDATA    | I/O  | I <sup>2</sup> C Port Serial Data Input/Output Pin.                                                                                                                                                      |

| 54      | SCLK     | 1    | I <sup>2</sup> C Port Serial Clock Input. The maximum clock rate is 400 kHz.                                                                                                                             |

| 63      | FIELD    | 0    | Field Synchronization Output Signal.                                                                                                                                                                     |

| 64      | VS       | 0    | Vertical Synchronization Output Signal.                                                                                                                                                                  |

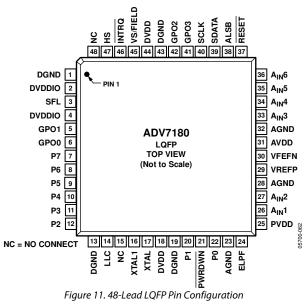

### **48-LEAD LQFP**

Table 12. 48-Lead LQFP Pin Function Descriptions

| Pin No.          | Mnemonic                               | Туре | Description                                                                                                                                                                                                                         |  |  |  |

|------------------|----------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1, 13, 19, 43    | DGND                                   | G    | Digital Ground.                                                                                                                                                                                                                     |  |  |  |

| 2, 4             | DVDDIO                                 | Р    | Digital I/O Supply Voltage (1.8 V to 3.3 V).                                                                                                                                                                                        |  |  |  |

| 3                | SFL                                    | 0    | Subcarrier Frequency Lock. This pin contains a serial output stream that can be used to lock the subcarrier frequency when this decoder is connected to any Analog Devices digital video encoder.                                   |  |  |  |

| 5, 6, 41, 42     | GPO0 to GPO3                           | 0    | General-Purpose Outputs. These pins can be configured via I <sup>2</sup> C to allow control of external devices.                                                                                                                    |  |  |  |