# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Multiformat SDTV Video Decoder with Fast Switch Overlay Support

# ADV7188

#### FEATURES

Multiformat video decoder supports NTSC (J/M/4.43), PAL (B/D/G/H/I/M/N), SECAM Integrates four 54 MHz, Noise Shaped Video (NSV®), 12-bit ADCs SCART fast blank support Clocked from a single 28.63636 MHz crystal Line-locked clock-compatible (LLC) Adaptive Digital Line Length Tracking (ADLLT™), signal processing, and enhanced FIFO management give mini-TBC functionality 5-line adaptive comb filters Proprietary architecture for locking to weak, noisy, and unstable video sources such as VCRs and tuners Subcarrier frequency lock and status information output Integrated automatic gain control (AGC) with adaptive peak white mode Macrovision<sup>®</sup> copy protection detection Chroma transient improvement (CTI) **Digital noise reduction (DNR)** Multiple programmable analog input formats CVBS (composite video) Y/C (S-video) YPrPb (component) (VESA, MII, SMPTE, and BETACAM) 12 analog video input channels Integrated antialiasing filters Programmable interrupt request output pin

#### **GENERAL DESCRIPTION**

The ADV7188 integrated video decoder automatically detects and converts standard analog baseband television signals compatible with worldwide NTSC, PAL, and SECAM standards into 4:2:2 component video data compatible with 20-/16-/10-/8-bit CCIR 601/CCIR 656.

The advanced, highly flexible digital output interface enables performance video decoding and conversion in line-locked, clock-based systems. This makes the device ideally suited for a broad range of applications with diverse analog video characteristics, including tape-based sources, broadcast sources, security and surveillance cameras, and professional systems.

The accurate 12-bit ADC provides professional quality video performance and is unmatched. This allows true 10-bit resolution in the 10-bit output mode.

The 12 analog input channels accept standard composite, S-video, and component video signals in an extensive number of combinations.

Automatic NTSC/PAL/SECAM identification Digital output formats (8-bit, 10-bit, 16-bit, or 20-bit) ITU-R BT.656 YCrCb 4:2:2 output + HS, VS, and FIELD 0.5 V to 1.6 V analog signal input range Differential gain: 0.4% typical Differential phase: 0.4° typical **Programmable video controls** Peak white/hue/brightness/saturation/contrast Integrated on-chip video timing generator Free-run mode (generates stable video output with no input) VBI decode support for close captioning (including Gemstar® 1×/2× (XDS)), WSS, CGMS, teletext, VITC, VPS Power-down mode 2-wire serial MPU interface (I<sup>2</sup>C<sup>®</sup> compatible) 3.3 V analog, 1.8 V digital core, 3.3 V input/output supply Industrial temperature grade: -40°C to +85°C 80-lead, Pb-free LQFP

#### **APPLICATIONS**

High end DVD recorders Video projectors HDD-based PVRs/DVDRs LCD TVs Set-top boxes Professional video products AVR receiver

AGC and clamp-restore circuitry allow an input video signal peak-to-peak range of 0.5 V to 1.6 V. Alternatively, these can be bypassed for manual settings.

The fixed 54 MHz clocking of the ADCs and datapath for all modes allows very precise, accurate sampling and digital filtering. The line-locked clock output allows the output data rate, timing signals, and output clock signals to be synchronous, asynchronous, or line locked even with  $\pm$ 5% variation in line length. The output control signals allow glueless interface connections in most applications. The ADV7188 modes are set up over a 2-wire, serial, bidirectional port (I<sup>2</sup>C compatible).

SCART and overlay functionality are enabled by the ability of the ADV7188 to process CVBS and standard definition RGB signals simultaneously. Signal mixing is controlled by the fast blank pin. The ADV7188 is fabricated in a 3.3 V CMOS process. Its monolithic CMOS construction ensures greater functionality with lower power dissipation. It is packaged in a small, Pb-free, 80-lead LQFP.

Rev. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700

www.analog.com

Fax: 781.461.3113

©2007 Analog Devices, Inc. All rights reserved.

# **ADV7188\* PRODUCT PAGE QUICK LINKS**

Last Content Update: 02/23/2017

### COMPARABLE PARTS

View a parametric search of comparable parts.

### DOCUMENTATION

#### **Application Notes**

- AN-1180: Optimizing Video Platforms for Automated Post-Production Self-Tests

- AN-1260: Crystal Design Considerations for Video Decoders, HDMI Receivers, and Transceivers

- AN-850: Adaptive Digital Line Length Tracking

#### **Data Sheet**

ADV7188: Multiformat SDTV Video Decoder with Fast Switch Overlay Support Data Sheet

#### **User Guides**

ADV7188 Design Support Files

### REFERENCE MATERIALS

#### Informational

Advantiv<sup>™</sup> Advanced TV Solutions

#### **Technical Articles**

- Analog Video Time Base Correction and Processing for Nonstandard TV Signals

- Optimizing standard-definition video on high-definition displays

### DESIGN RESOURCES

- ADV7188 Material Declaration

- PCN-PDN Information

- Quality And Reliability

- Symbols and Footprints

### DISCUSSIONS

View all ADV7188 EngineerZone Discussions.

### SAMPLE AND BUY

Visit the product page to see pricing options.

### TECHNICAL SUPPORT

Submit a technical question or find your regional support number.

### DOCUMENT FEEDBACK

Submit feedback for this data sheet.

# TABLE OF CONTENTS

| Features                                      |  |  |  |  |  |  |  |

|-----------------------------------------------|--|--|--|--|--|--|--|

| Applications1                                 |  |  |  |  |  |  |  |

| General Description 1                         |  |  |  |  |  |  |  |

| Revision History                              |  |  |  |  |  |  |  |

| Introduction                                  |  |  |  |  |  |  |  |

| Analog Front End 4                            |  |  |  |  |  |  |  |

| Standard Definition Processor (SDP) 4         |  |  |  |  |  |  |  |

| Functional Block Diagram                      |  |  |  |  |  |  |  |

| Specifications                                |  |  |  |  |  |  |  |

| Electrical Characteristics                    |  |  |  |  |  |  |  |

| Video Specifications                          |  |  |  |  |  |  |  |

| Analog Specifications                         |  |  |  |  |  |  |  |

| Thermal Specifications7                       |  |  |  |  |  |  |  |

| Timing Specifications7                        |  |  |  |  |  |  |  |

| Timing Diagrams                               |  |  |  |  |  |  |  |

| Absolute Maximum Ratings9                     |  |  |  |  |  |  |  |

| Package Thermal Performance9                  |  |  |  |  |  |  |  |

| ESD Caution9                                  |  |  |  |  |  |  |  |

| Pin Configuration and Function Descriptions10 |  |  |  |  |  |  |  |

| Analog Front End 12                           |  |  |  |  |  |  |  |

| Analog Input Muxing13                         |  |  |  |  |  |  |  |

| Manual Input Muxing15                         |  |  |  |  |  |  |  |

| XTAL Clock Input Pin Functionality16          |  |  |  |  |  |  |  |

| 28.63636 MHz Crystal Operation16              |  |  |  |  |  |  |  |

| Antialiasing Filters16                        |  |  |  |  |  |  |  |

| SCART and Fast Blanking16                     |  |  |  |  |  |  |  |

| Fast Blank Control17                          |  |  |  |  |  |  |  |

| Global Control Registers                      |  |  |  |  |  |  |  |

| Power-Saving Modes21                          |  |  |  |  |  |  |  |

| Reset Control                                 |  |  |  |  |  |  |  |

| Global Pin Control                            |  |  |  |  |  |  |  |

| Global Status Registers                                  |

|----------------------------------------------------------|

| Standard Definition Processor (SDP)                      |

| SD Luma Path                                             |

| SD Chroma Path                                           |

| Sync Processing                                          |

| VBI Data Recovery                                        |

| General Setup                                            |

| Color Controls                                           |

| Clamp Operation                                          |

| Luma Filter                                              |

| Chroma Filter                                            |

| Gain Operation                                           |

| Chroma Transient Improvement (CTI)                       |

| Digital Noise Reduction (DNR) and Luma Peaking Filter 39 |

| Comb Filters                                             |

| AV Code Insertion and Controls                           |

| Synchronization Output Signals 4                         |

| Sync Processing                                          |

| VBI Data Decode                                          |

| I <sup>2</sup> C Interface                               |

| Standard Detection and Identification                    |

| I²C Readback Registers                                   |

| Pixel Port Configuration                                 |

| Pixel Port-Related Controls                              |

| MPU Port Description                                     |

| Register Accesses                                        |

| Register Programming                                     |

| I <sup>2</sup> C Sequencer                               |

| I <sup>2</sup> C Programming Examples                    |

| I <sup>2</sup> C Register Maps                           |

| User Map 82                                              |

|                                                          |

| 99 | User Sub Map                           |

|----|----------------------------------------|

|    | PCB Layout Recommendations             |

|    | Analog Interface Inputs                |

|    | Power Supply Decoupling                |

|    | PLL                                    |

|    | Digital Outputs (Both Data and Clocks) |

### **REVISION HISTORY**

7/05—Revision 0: Initial Version

| Digital Inputs                           | 110 |

|------------------------------------------|-----|

| XTAL and Load Capacitor Values Selection | 110 |

| Typical Circuit Connection               | 111 |

| Outline Dimensions                       | 112 |

| Ordering Guide                           | 112 |

|                                          |     |

## INTRODUCTION

The ADV7188 is a high quality, single chip, multiformat video decoder that automatically detects and converts PAL, NTSC, and SECAM standards in the form of composite, S-video, and component video into a digital ITU-R BT.656 format.

The advanced, highly flexible digital output interface enables performance video decoding and conversion in line-locked, clockbased systems. This makes the device ideally suited for a broad range of applications with diverse analog video characteristics, including tape-based sources, broadcast sources, security and surveillance cameras, and professional systems.

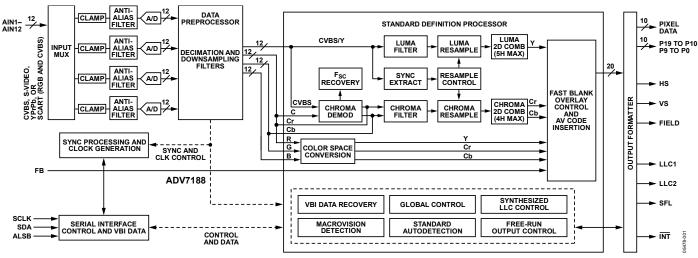

#### **ANALOG FRONT END**

The ADV7188 analog front end includes four 12-bit NSV ADCs that digitize the analog video signal before applying it to the standard definition processor (SDP). The analog front end uses differential channels for each ADC to ensure high performance in mixed-signal applications.

The front end also includes a 12-channel input mux that enables multiple video signals to be applied to the ADV7188. Current and voltage clamps are positioned in front of each ADC to ensure that the video signal remains within the range of the converter. Fine clamping of the video signals is performed downstream by digital fine clamping within the ADV7188. The ADCs are configured to run in 4× oversampling mode.

The ADV7188 has optional antialiasing filters on each of the four input channels. The filters are designed for standard definition (SD) video with approximately 6 MHz bandwidth.

SCART and overlay functionality are enabled by the ability of the ADV7188 to process CVBS and standard definition RGB signals simultaneously. Signal mixing is controlled by the fast blank (FB) pin.

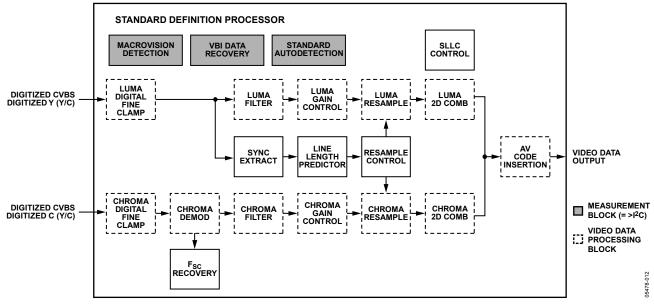

#### STANDARD DEFINITION PROCESSOR (SDP)

The ADV7188 is capable of decoding a large selection of baseband video signals in composite, S-video, and component formats. The video standards that are supported include PAL B/D/I/G/H, PAL 60, PAL M, PAL N, PAL NC, NTSC M/J, NTSC 4.43, and SECAM B/D/G/K/L. The ADV7188 can automatically detect the video standard and process it accordingly.

The ADV7188 has a 5-line, superadaptive, 2D comb filter that provides superior chrominance and luminance separation when decoding a composite video signal. This highly adaptive filter automatically adjusts its processing mode according to the video standard and signal quality without requiring user intervention. Video user controls such as brightness, contrast, saturation, and hue are also available within the ADV7188.

The ADV7188 implements the patented ADLLT algorithm to track varying video line lengths from sources such as a VCR. ADLLT enables the ADV7188 to track and decode poor quality video sources such as VCRs and noisy sources from tuner outputs, VCD players, and camcorders. The ADV7188 contains a CTI processor that sharpens the edge rate of chroma transitions, resulting in sharper vertical transitions.

The ADV7188 can process a variety of VBI data services, such as closed captioning (CC), wide-screen signaling (WSS), copy generation management system (CGMS), Gemstar<sup>®</sup> 1×/2×, extended data service (XDS), and teletext. The ADV7188 is fully Macrovision certified; detection circuitry enables Type I, Type II, and Type III protection levels to be identified and reported to the user. The decoder is also fully robust to all Macrovision signal inputs.

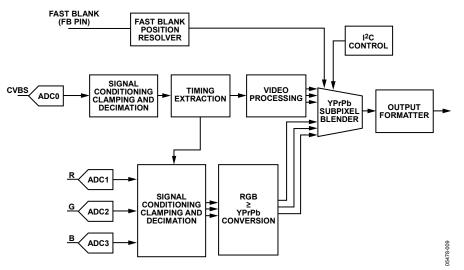

#### FUNCTIONAL BLOCK DIAGRAM

### **SPECIFICATIONS**

#### **ELECTRICAL CHARACTERISTICS**

A<sub>VDD</sub> = 3.15 V to 3.45 V, D<sub>VDD</sub> = 1.65 V to 2.0 V, D<sub>VDDIO</sub> = 3.0 V to 3.6 V, P<sub>VDD</sub> = 1.71 V to 1.89 V, nominal input range 1.6 V. Operating temperature range, unless otherwise noted.

| Table 1.                              |                           |                                  |      |           |            |      |

|---------------------------------------|---------------------------|----------------------------------|------|-----------|------------|------|

| Parameter                             | Symbol                    | Test Conditions                  | Min  | Тур       | Max        | Unit |

| STATIC PERFORMANCE <sup>1, 2, 3</sup> |                           |                                  |      |           |            |      |

| Resolution (Each ADC)                 | N                         |                                  |      |           | 12         | Bits |

| Integral Nonlinearity                 | INL                       | BSL at 54 MHz                    |      | -1.5/+2.5 | ±8         | LSB  |

| Differential Nonlinearity             | DNL                       | BSL at 54 MHz                    |      | -0.7/+0.7 | -0.99/+2.5 | LSB  |

| DIGITAL INPUTS                        |                           |                                  |      |           |            |      |

| Input High Voltage⁴                   | VIH                       |                                  | 2    |           |            | V    |

| Input Low Voltage⁵                    | VIL                       |                                  |      |           | 0.8        | V    |

| Input Current <sup>6, 7</sup>         | l <sub>IN</sub>           |                                  | -50  |           | +50        | μΑ   |

|                                       |                           |                                  | -10  |           | +10        | μA   |

| Input Capacitance <sup>8</sup>        | CIN                       |                                  |      |           | 10         | pF   |

| DIGITAL OUTPUTS                       |                           |                                  |      |           |            |      |

| Output High Voltage <sup>9</sup>      | Vон                       | I <sub>SOURCE</sub> = 0.4 mA     | 2.4  |           |            | V    |

| Output Low Voltage <sup>9</sup>       | Vol                       | $I_{SINK} = 3.2 \text{ mA}$      |      |           | 0.4        | V    |

| High Impedance Leakage Current        | ILEAK                     |                                  |      |           | 10         | μΑ   |

| Output Capacitance <sup>8</sup>       | Cout                      |                                  |      |           | 20         | pF   |

| POWER REQUIREMENTS <sup>8</sup>       |                           |                                  |      |           |            |      |

| Digital Core Power Supply             | D <sub>VDD</sub>          |                                  | 1.65 | 1.8       | 2.0        | V    |

| Digital Input/Output Power Supply     | Dvddio                    |                                  | 3.0  | 3.3       | 3.6        | V    |

| PLL Power Supply                      | P <sub>VDD</sub>          |                                  | 1.71 | 1.8       | 1.89       | V    |

| Analog Power Supply                   | Avdd                      |                                  | 3.15 | 3.3       | 3.45       | V    |

| Digital Core Supply Current           | IDVDD                     |                                  |      | 105       |            | mA   |

| Digital Input/Output Supply Current   |                           |                                  |      | 4         |            | mA   |

| PLL Supply Current                    | IPVDD                     |                                  |      | 11        |            | mA   |

| Analog Supply Current                 | IAVDD                     | CVBS input <sup>10</sup>         |      | 99        |            | mA   |

|                                       |                           | SCART RGB FB input <sup>11</sup> |      | 269       |            | mA   |

| Power-Down Current                    | IPWRDN                    |                                  |      | 0.65      |            | mA   |

| Power-Up Time                         | <b>t</b> <sub>PWRUP</sub> |                                  |      | 20        |            | ms   |

<sup>1</sup> All ADC linearity tests performed with the input range at full scale – 12.5% and at zero scale + 12.5%.

<sup>2</sup> Maximum INL and DNL specifications obtained with the part configured for component video input.

<sup>3</sup> Temperature range T<sub>MIN</sub> to T<sub>MAX</sub>, -40°C to +85°C. The minimum/maximum specifications are guaranteed over this range.

<sup>4</sup> To obtain specified V<sub>IH</sub> level on Pin 29, Register 0x13 (write only) must be programmed with Value 0x04. If Register 0x13 is programmed with Value 0x00, then V<sub>IH</sub> on Pin 29 is 1.2 V. <sup>5</sup> To obtain specified V<sub>IL</sub> level on Pin 29, Register 0x13 (write only) must be programmed with Value 0x04. If Register 0x13 is programmed with Value 0x00, then V<sub>IL</sub> on Pin 29 is 1.2 V. <sup>6</sup> Pins 36, 64, 79.

<sup>7</sup> Excluding all TEST pins (TEST0 to TEST8)

$^{8}$  V<sub>OH</sub> and  $V_{OL}$  levels obtained using default drive strength value (0xD5) in Register 0xF4.

<sup>9</sup> Guaranteed by characterization.

<sup>10</sup> Only ADC0 is powered on.

<sup>11</sup> All four ADCs powered on.

#### **VIDEO SPECIFICATIONS**

At  $A_{VDD} = 3.15$  V to 3.45 V,  $D_{VDD} = 1.65$  V to 2.0 V,  $D_{VDDIO} = 3.0$  V to 3.6 V,  $P_{VDD} = 1.71$  V to 1.89 V (operating temperature range, unless otherwise noted).

#### Table 2.

| Parameter <sup>1, 2</sup>     | Symbol | Test Conditions                 | Min | Тур  | Max | Unit   |

|-------------------------------|--------|---------------------------------|-----|------|-----|--------|

| NONLINEAR SPECIFICATIONS      |        |                                 |     |      |     |        |

| Differential Phase            | DP     | CVBS input, modulate five steps |     | 0.4  | 0.6 | Degree |

| Differential Gain             | DG     | CVBS input, modulate five steps |     | 0.4  | 0.6 | %      |

| Luma Nonlinearity             | LNL    | CVBS input, five steps          |     | 0.4  | 0.7 | %      |

| NOISE SPECIFICATIONS          |        |                                 |     |      |     |        |

| SNR Unweighted                |        | Luma ramp                       | 61  | 63   |     | dB     |

|                               |        | Luma flat field                 | 63  | 65   |     | dB     |

| Analog Front End Crosstalk    |        |                                 |     | 60   |     | dB     |

| LOCK TIME SPECIFICATIONS      |        |                                 |     |      |     |        |

| Horizontal Lock Range         |        |                                 | -5  |      | +5  | %      |

| Vertical Lock Range           |        |                                 | 40  |      | 70  | Hz     |

| Fsc Subcarrier Lock Range     |        |                                 |     | ±1.3 |     | Hz     |

| Color Lock-In Time            |        |                                 |     | 60   |     | Lines  |

| Sync Depth Range <sup>3</sup> |        |                                 | 20  |      | 200 | %      |

| Color Burst Range             |        |                                 | 5   |      | 200 | %      |

| Vertical Lock Time            |        |                                 |     | 2    |     | Fields |

| Autodetection Switch Speed    |        |                                 |     | 100  |     | Lines  |

| CHROMA SPECIFICATIONS         |        |                                 |     |      |     |        |

| Hue Accuracy                  | HUE    |                                 |     | 1    |     | Degree |

| Color Saturation Accuracy     | CL_AC  |                                 |     | 1    |     | %      |

| Color AGC Range               |        |                                 | 5   |      | 400 | %      |

| Chroma Amplitude Error        |        |                                 |     | 0.4  |     | %      |

| Chroma Phase Error            |        |                                 |     | 0.3  |     | Degree |

| Chroma Luma Intermodulation   |        |                                 |     | 0.1  |     | %      |

| LUMA SPECIFICATIONS           |        |                                 |     |      |     |        |

| Luma Brightness Accuracy      |        | CVBS, 1 V input                 |     | 1    |     | %      |

| Luma Contrast Accuracy        |        | CVBS, 1 V input                 |     | 1    |     | %      |

<sup>1</sup> Temperature range T<sub>MIN</sub> to T<sub>MAX</sub> is -40°C to +85°C. The minimum/maximum specifications are guaranteed over this range.

<sup>2</sup> Guaranteed by characterization.

<sup>3</sup> Nominal sync depth is 300 mV at 100% sync depth range.

#### ANALOG SPECIFICATIONS

At  $A_{VDD} = 3.15$  V to 3.45 V,  $D_{VDD} = 1.65$  V to 2.0 V,  $D_{VDDIO} = 3.0$  V to 3.6 V,  $P_{VDD} = 1.71$  V to 1.89 V (operating temperature range, unless otherwise noted). Recommended analog input video signal range is 0.5 V to 1.6 V, typically 1 V p-p.

#### Table 3.

| Parameter <sup>1, 2</sup>      | Symbol | Test Condition      | Min | Тур  | Max | Unit |

|--------------------------------|--------|---------------------|-----|------|-----|------|

| CLAMP CIRCUITRY                |        |                     |     |      |     |      |

| External Clamp Capacitor       |        |                     |     | 0.1  |     | μF   |

| Input Impedance <sup>3</sup>   |        | Clamps switched off |     | 10   |     | MΩ   |

| Input Impedance of Pin 40 (FB) |        |                     |     | 20   |     | kΩ   |

| Large-Clamp Source Current     |        |                     |     | 0.75 |     | mA   |

| Large-Clamp Sink Current       |        |                     |     | 0.75 |     | mA   |

| Fine-Clamp Source Current      |        |                     |     | 60   |     | μΑ   |

| Fine-Clamp Sink Current        |        |                     |     | 60   |     | μΑ   |

<sup>1</sup> Temperature range T<sub>MIN</sub> to T<sub>MAX</sub> is -40°C to +85°C. The minimum/maximum specifications are guaranteed over this range.

<sup>2</sup> Guaranteed by characterization.

<sup>3</sup> Except Pin 40 (FB).

#### **THERMAL SPECIFICATIONS**

| Table 4.                                           |        |                                     |     |      |     |      |

|----------------------------------------------------|--------|-------------------------------------|-----|------|-----|------|

| Parameter                                          | Symbol | Test Conditions                     | Min | Тур  | Max | Unit |

| Junction-to-Case Thermal Resistance                | θ」     | 4-layer PCB with solid ground plane |     | 7.6  |     | °C/W |

| Junction-to-Ambient Thermal Resistance (Still Air) | θ」Α    | 4-layer PCB with solid ground plane |     | 38.1 |     | °C/W |

#### **TIMING SPECIFICATIONS**

$A_{VDD} = 3.15$  V to 3.45 V,  $D_{VDD} = 1.65$  V to 2.0 V,  $D_{VDDIO} = 3.0$  V to 3.6 V,  $P_{VDD} = 1.71$  V to 1.89 V (operating temperature range, unless otherwise noted).

Table 5.

| Parameter <sup>1, 2</sup>                  | Symbol                 | Test Conditions                                                             | Min   | Тур      | Max   | Unit         |

|--------------------------------------------|------------------------|-----------------------------------------------------------------------------|-------|----------|-------|--------------|

| SYSTEM CLOCK AND CRYSTAL                   |                        |                                                                             |       |          |       |              |

| Nominal Frequency                          |                        |                                                                             |       | 28.63636 |       | MHz          |

| Frequency Stability                        |                        |                                                                             |       |          | ±50   | ppm          |

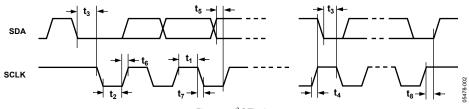

| I <sup>2</sup> C PORT <sup>3</sup>         |                        |                                                                             |       |          |       |              |

| SCLK Frequency                             |                        |                                                                             |       |          | 400   | kHz          |

| SCLK Minimum Pulse Width High              | t1                     |                                                                             | 0.6   |          |       | μs           |

| SCLK Minimum Pulse Width Low               | t <sub>2</sub>         |                                                                             | 1.3   |          |       | μs           |

| Hold Time (Start Condition)                | t <sub>3</sub>         |                                                                             | 0.6   |          |       | μs           |

| Setup Time (Start Condition)               | t4                     |                                                                             | 0.6   |          |       | μs           |

| SDA Setup Time                             | t₅                     |                                                                             | 100   |          |       | ns           |

| SCLK and SDA Rise Time                     | t <sub>6</sub>         |                                                                             |       |          | 300   | ns           |

| SCLK and SDA Fall Time                     | t <sub>7</sub>         |                                                                             |       |          | 300   | ns           |

| Setup Time for Stop Condition              | t <sub>8</sub>         |                                                                             |       | 0.6      |       | μs           |

| RESET FEATURE                              |                        |                                                                             |       |          |       |              |

| Reset Pulse Width                          |                        |                                                                             | 5     |          |       | ms           |

| CLOCK OUTPUTS                              |                        |                                                                             |       |          |       |              |

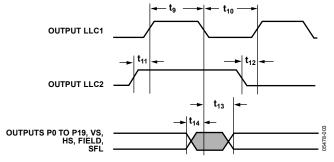

| LLC1 Mark-Space Ratio                      | t9:t10                 |                                                                             | 45:55 |          | 55:45 | % duty cycle |

| LLC1 Rising to LLC2 Rising                 | <b>t</b> 11            |                                                                             |       | 1        |       | ns           |

| LLC1 Rising to LLC2 Falling                | <b>t</b> <sub>12</sub> |                                                                             |       | 1        |       | ns           |

| DATA AND CONTROL OUTPUTS                   |                        |                                                                             |       |          |       |              |

| Data Output Transitional Time <sup>4</sup> | <b>t</b> <sub>13</sub> | Negative clock edge to start of valid data $(t_{ACCESS} = t_{10} - t_{13})$ |       |          | 3.6   | ns           |

| Data Output Transitional Time <sup>4</sup> | t <sub>14</sub>        | End of valid data to negative clock edge $(t_{HOLD} = t_9 + t_{14})$        |       |          | 2.4   | ns           |

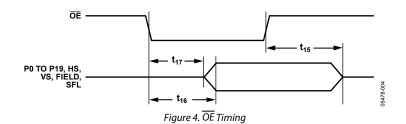

| Propagation Delay to Hi-Z                  | t15                    |                                                                             |       | 6        |       | ns           |

| Max Output Enable Access Time              | t <sub>16</sub>        |                                                                             |       | 7        |       | ns           |

| Min Output Enable Access Time              | <b>t</b> <sub>17</sub> |                                                                             |       | 4        |       | ns           |

<sup>1</sup> Temperature range T<sub>MIN</sub> to T<sub>MAX</sub> is –40°C to +85°C. The minimum/maximum specifications are guaranteed over this range. <sup>2</sup> Guaranteed by characterization.

<sup>3</sup> TTL input values are 0 V to 3 V, with rise/fall times  $\leq$ 3 ns, measured between the 10% and 90% points.

<sup>4</sup> SDP timing figures obtained using default drive strength value (0xD5) in Register 0xF4.

#### **TIMING DIAGRAMS**

Figure 3. Pixel Port and Control Output Timing

### **ABSOLUTE MAXIMUM RATINGS**

#### Table 6.

| Parameter                                | Rating                                       |

|------------------------------------------|----------------------------------------------|

| Avdd to AGND                             | 4 V                                          |

| D <sub>VDD</sub> to DGND                 | 2.2 V                                        |

| PVDD to AGND                             | 2.2 V                                        |

| DVDDIO to DGND                           | 4 V                                          |

| DVDDIO to AVDD                           | –0.3 V to +0.3 V                             |

| P <sub>VDD</sub> to D <sub>VDD</sub>     | –0.3 V to +0.3 V                             |

| Dvddio to Pvdd                           | –0.3 V to +2 V                               |

| D <sub>VDDIO</sub> to D <sub>VDD</sub>   | –0.3 V to +2 V                               |

| Avdd to Pvdd                             | –0.3 V to +2 V                               |

| A <sub>VDD</sub> to D <sub>VDD</sub>     | –0.3 V to +2 V                               |

| Digital Inputs Voltage to DGND           | -0.3 V to D <sub>VDDIO</sub> + 0.3 V         |

| Digital Output Voltage to DGND           | -0.3 V to D <sub>VDDIO</sub> + 0.3 V         |

| Analog Inputs to AGND                    | AGND $- 0.3$ V to A <sub>VDD</sub> $+ 0.3$ V |

| Maximum Junction Temperature<br>(TJ max) | 125℃                                         |

| Storage Temperature Range                | –65°C to +150°C                              |

| Infrared Reflow Soldering (20 sec)       | 260°C                                        |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### PACKAGE THERMAL PERFORMANCE

To reduce power consumption the user is advised to turn off any unused ADCs when using the part.

The junction temperature must always stay below the maximum junction temperature (T<sub>1</sub> max) of 125°C. Use the following equation to calculate the junction temperature:

$$T_J = T_{A \max} + (\theta_{JA} \times W_{\max})$$

where:  $T_{A max} = 85^{\circ}\text{C}.$   $\theta_{JA} = 30^{\circ}\text{C/W}.$  $W_{max} = ((A_{VDD} \times I_{AVDD}) + (D_{VDD} \times I_{DVDD}) + (D_{VDDIO} \times I_{DVDDIO}) + (P_{VDD} \times I_{PVDD})).$

#### ESD CAUTION

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

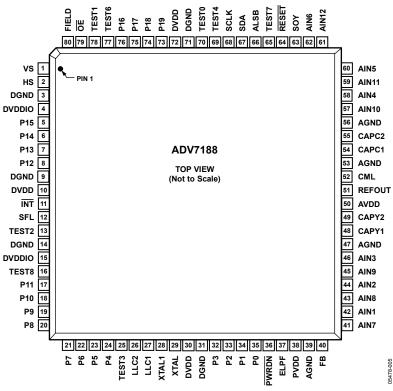

### PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 5. 80-Lead LQFP Pin Configuration

#### Table 7. Pin Function Descriptions

| Pin No.               | Mnemonic          | Туре | Description                                                                                                                                             |

|-----------------------|-------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       |                   | G    |                                                                                                                                                         |

| 3, 9, 14, 31, 71      | DGND              |      | Digital Ground.                                                                                                                                         |

| 39, 47, 53, 56        | AGND              | G    | Analog Ground.                                                                                                                                          |

| 4, 15                 | DVDDIO            | Р    | Digital I/O Supply Voltage (3.3 V).                                                                                                                     |

| 10, 30, 72            | DVDD              | Р    | Digital Core Supply Voltage (1.8 V).                                                                                                                    |

| 50                    | AVDD              | Р    | Analog Supply Voltage (3.3 V).                                                                                                                          |

| 38                    | PVDD              | Р    | PLL Supply Voltage (1.8 V).                                                                                                                             |

| 42, 44, 46, 58,       | AIN1 to           | I    | Analog Video Input Channels.                                                                                                                            |

| 60, 62, 41, 43,       | AIN12             |      |                                                                                                                                                         |

| 45, 57, 59, 61        |                   |      |                                                                                                                                                         |

| 11                    | INT               | 0    | Interrupt Request Output. An interrupt occurs when certain signals are detected on the input video. See the User Sub Map register details in Table 107. |

| 40                    | FB                | I    | Fast Blank. FB is a fast switch overlay input that switches between CVBS and RGB analog signals.                                                        |

| 70, 78, 13, 25,<br>69 | TEST0 to<br>TEST4 |      | Leave these pins unconnected.                                                                                                                           |

| 77, 65                | TEST6 to<br>TEST7 |      | Tie to AGND.                                                                                                                                            |

| 16                    | TEST8             |      | Tie to DVDDIO.                                                                                                                                          |

| 35 to 32,             | P0 to P19         | 0    | Video Pixel Output Ports.                                                                                                                               |

| 24 to 17, 8 to 5,     |                   |      |                                                                                                                                                         |

| 76 to 73              |                   |      |                                                                                                                                                         |

| 2                     | HS                | 0    | Horizontal Synchronization Output Signal.                                                                                                               |

| 1                     | VS                | 0    | Vertical Synchronization Output Signal.                                                                                                                 |

| 80                    | FIELD             | 0    | Field Synchronization Output Signal.                                                                                                                    |

| 67                    | SDA               | I/O  | I <sup>2</sup> C Port Serial Data Input/Output.                                                                                                         |

| Pin No. | Mnemonic        | Туре | Description                                                                                                                                                                                                                                                            |

|---------|-----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 68      | SCLK            | I    | I <sup>2</sup> C Port Serial Clock Input. Maximum clock rate of 400 kHz.                                                                                                                                                                                               |

| 66      | ALSB            | I    | This pin selects the I <sup>2</sup> C address for the ADV7188. ALSB set to Logic 0 sets the address for a write to 0x40; set to Logic 1 sets the address to 0x42.                                                                                                      |

| 64      | RESET           | I    | System Reset Input (active low). A minimum low reset pulse width of 5 ms is required to reset the ADV7188 circuitry.                                                                                                                                                   |

| 27      | LLC1            | 0    | Line-Locked Clock 1. This is a line-locked output clock for the pixel data output by the ADV7188.<br>Nominally 27 MHz, but varies according to video line length.                                                                                                      |

| 26      | LLC2            | 0    | Line-Locked Clock 2. This is a divide-by-2 version of the LLC1 output clock for the pixel data output by the ADV7188. Nominally 13.5 MHz, but varies according to video line length.                                                                                   |

| 29      | XTAL            | I    | Crystal Input. This is the input pin for the 28.63636 MHz crystal, or it can be overdriven by an external 3.3 V, 28.63636 MHz clock oscillator source. In crystal mode, the crystal must be a fundamental crystal.                                                     |

| 28      | XTAL1           | 0    | This pin should be connected to the 28.63636 MHz crystal or left as a no connect if an external 3.3 V, 28.63636 MHz clock oscillator source is used to clock the ADV7188. In crystal mode, the crystal must be a fundamental crystal.                                  |

| 36      | PWRDN           | I    | Logic 0 on this pin places the ADV7188 in a power-down mode. Refer to the I <sup>2</sup> C Register Maps section for more options on power-down modes for the ADV7188.                                                                                                 |

| 79      | ŌĒ              | I    | When set to Logic 0, $\overline{\text{OE}}$ enables the pixel output bus, P19 to P0 of the ADV7188. Logic 1 on the $\overline{\text{OE}}$ pin places P19 to P0, HS, VS, and SFL into a high impedance state.                                                           |

| 37      | ELPF            | 1    | The recommended external loop filter must be connected to this ELPF pin, as shown in Figure 52.                                                                                                                                                                        |

| 12      | SFL             | 0    | Subcarrier Frequency Lock. This pin contains a serial output stream that can be used to lock the subcarrier frequency when this decoder is connected to any Analog Devices, Inc., digital video encoder.                                                               |

| 63      | SOY             | I    | SYNC on Y. This input pin should only be used with the standard detection and identification function (see the Standard Detection and Identification section). This pin should be connected to the Y signal of a component input for standard identification function. |

| 51      | REFOUT          | 0    | Internal Voltage Reference Output. Refer to Figure 52 for a recommended capacitor network for this pin.                                                                                                                                                                |

| 52      | CML             | 0    | Common-Mode Level. The CML pin is a common-mode level for the internal ADCs. Refer to Figure 52 for a recommended capacitor network for this pin.                                                                                                                      |

| 48, 49  | CAPY1,<br>CAPY2 | I    | ADC Capacitor Network. Refer to Figure 52 for a recommended capacitor network for this pin.                                                                                                                                                                            |

| 54, 55  | CAPC1,<br>CAPC2 | I    | ADC Capacitor Network. Refer to Figure 52 for a recommended capacitor network for this pin.                                                                                                                                                                            |

### ANALOG FRONT END

Figure 6. Internal Pin Connections

#### ANALOG INPUT MUXING

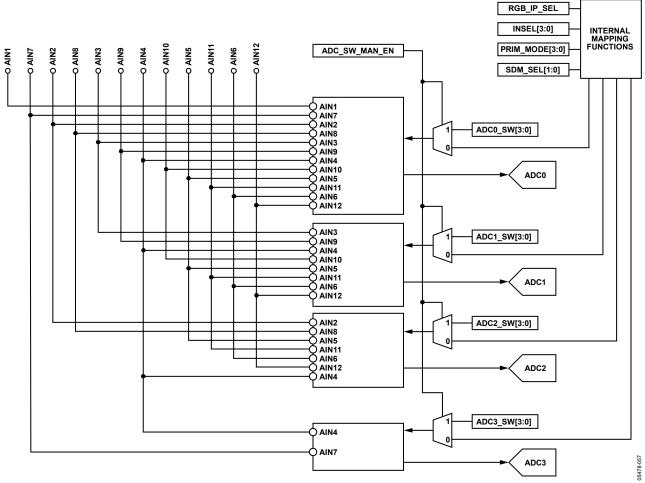

The ADV7188 has an integrated analog muxing section that allows connecting more than one source of video signal to the decoder. Figure 6 outlines the overall structure of the input muxing provided in the ADV7188.

As can be seen in Figure 6, the analog input muxes can be controlled in two ways:

- By the functional register (INSEL). Using INSEL [3:0] simplifies the setup of the muxes and minimizes crosstalk between channels by preassigning the input channels. This is referred to as the recommended input muxing.

- By an I<sup>2</sup>C manual override (ADC\_SW\_MAN\_EN, ADC0\_SW, ADC1\_SW, ADC2\_SW, and ADC3\_SW). This is provided for applications with special requirements, such as number/combinations of signals that are not served by the preassigned input connections. This is referred to as manual input muxing.

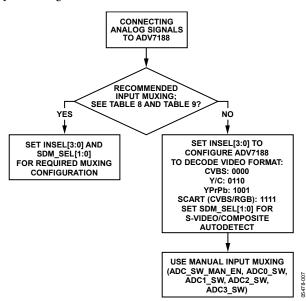

Figure 7 shows an overview of the two methods of controlling input muxing.

Figure 7. Input Muxing Overview

#### **Recommended Input Muxing**

A maximum of 12 CVBS inputs can be connected and decoded by the ADV7188, meaning that the sources must be connected to adjacent pins on the IC, as seen in Figure 5. This calls for a careful design of the PCB layout, for example, placing ground shielding between all signals routed through tracks that are physically close together.

#### SDM\_SEL [1:0], Y/C and CVBS Autodetect Mode Select, Address 0x69 [1:0]

The SDM\_SEL bits decide on input routing and whether INSEL [3:0] is used to govern input routing decisions.

The S-video/composite autodetection feature is enabled using SDM\_SEL = 11.

| Table 8. SDM | SEL | [1:0] |

|--------------|-----|-------|

|--------------|-----|-------|

| SDM_SEL [1:0] | Mode                               | Analog Video Inputs                    |

|---------------|------------------------------------|----------------------------------------|

| 00            | As per INSEL [3:0]                 | As per INSEL [3:0]                     |

| 01            | CVBS                               | AIN11                                  |

| 10            | Y/C                                | Y = AIN10<br>C = AIN12                 |

| 11            | S-video/composite<br>autodetection | CVBS = AIN11<br>Y = AIN11<br>C = AIN12 |

#### INSEL [3:0], Input Selection, Address 0x00 [3:0]

The INSEL bits allow the user to select the input channel and format. Depending on the PCB connections, only a subset of the INSEL modes is valid. INSEL [3:0] not only switches the analog input muxing, but also configures the ADV7188 to process composite (CVBS), S-video (Y/C), or component (YPbPr) format signals.

The recommended input muxing is designed to minimize crosstalk between signal channels and to obtain the highest level of signal integrity. Table 10 summarizes how the PCB layout should connect analog video signals to the ADV7188.

It is strongly recommended that users connect any unused analog input pins to AGND to act as a shield.

Connect the AIN7 to AIN11 inputs to AGND when only six input channels are used. This improves the quality of the sampling due to better isolation between the channels.

AIN12 is not controlled by INSEL [3:0]. It can be routed to ADC0/ADC1/ADC2 only by manual muxing. See Table 11 for details.

| -         |                                 | <b>v</b>                 |

|-----------|---------------------------------|--------------------------|

| INSEL     |                                 | ription                  |

| [3:0]     | Analog Input Pins               | Video Format             |

| 0000      | CVBS1 = AIN1                    | SCART (CVBS and R, G, B) |

| (default) | $B = AIN4 \text{ or } AIN7^{1}$ |                          |

|           | $R = AIN5 \text{ or } AIN8^1$   |                          |

|           | $G = AIN6 \text{ or } AIN9^1$   |                          |

| 0001      | CVBS2 = AIN2                    | SCART (CVBS and R, G, B) |

|           | $B = AIN4 \text{ or } AIN7^1$   |                          |

|           | $R = AIN5 \text{ or } AIN8^1$   |                          |

|           | $G = AIN6 \text{ or } AIN9^1$   |                          |

| 0010      | CVBS3 = AIN3                    | SCART (CVBS and R, G, B) |

|           | $B = AIN4 \text{ or } AIN7^1$   |                          |

|           | $R = AIN5 \text{ or } AIN8^1$   |                          |

|           | $G = AIN6 \text{ or } AIN9^1$   |                          |

| 0011      | CVBS4 = AIN4                    | SCART (CVBS and R, G, B) |

|           | B = AIN7                        |                          |

|           | R = AIN8                        |                          |

|           | G = AIN9                        |                          |

| 0100      | CVBS1 = AIN5                    | SCART (CVBS and R, G, B) |

| 0100      | B = AIN4                        |                          |

|           | R = AIN5                        |                          |

|           | G = AIN6                        |                          |

| 0101      | CVBS1 = AIN1                    | SCART (CVBS and R, G, B) |

| 0101      | B = AIN4                        |                          |

|           | R = AIN5                        |                          |

|           | G = AIN6                        |                          |

| 0110      | Y1 = AIN1                       | Y/C                      |

| 0.10      | C1 = AIN4                       | ., -                     |

| 0111      | $Y_2 = AIN_2$                   | Y/C                      |

|           | C2 = AIN5                       |                          |

| 1000      | Y3 = AIN3                       | Y/C                      |

|           | C3 = AIN6                       |                          |

| 1001      | Y1 = AIN1                       | YPrPb                    |

|           | PB1 = AIN4                      |                          |

|           | PR1 = AIN5                      |                          |

| 1010      | Y2 = AIN2                       | YPrPb                    |

|           | PB2 = AIN3                      |                          |

|           | PR2 = AIN6                      |                          |

| 1011      | CVBS7 = AIN7                    | SCART (CVBS and R, G, B) |

|           | B = AIN4                        |                          |

|           | R = AIN5                        |                          |

|           | G = AIN6                        |                          |

| 1100      | CVBS8 = AIN8                    | SCART (CVBS and R, G, B) |

|           | B = AIN4                        |                          |

|           | R = AIN5                        |                          |

|           | G = AIN6                        |                          |

| 1101      | CVBS9 = AIN9                    | SCART (CVBS and R, G, B) |

|           | B = AIN4                        |                          |

|           | R = AIN5                        |                          |

|           | G = AIN6                        |                          |

| 1110      | CVBS10 = AIN10                  | SCART (CVBS and R, G, B) |

|           | $B = AIN4 \text{ or } AIN7^{1}$ |                          |

|           | $R = AIN5 \text{ or } AIN8^1$   |                          |

|           | $G = AIN6 \text{ or } AIN9^1$   |                          |

| 1111      | CVBS11 = AIN11                  | SCART (CVBS and R, G, B) |

|           | $B = AIN4 \text{ or } AIN7^{1}$ |                          |

|           | $R = AIN5 \text{ or } AIN8^{1}$ |                          |

|           | $G = AIN6 \text{ or } AIN9^1$   |                          |

|           |                                 |                          |

<sup>1</sup> Selectable via RGB\_IP\_SEL.

| Input Channel | Pin | Recommended Input Muxing Control—INSEL [3:0] |       |           |             |  |

|---------------|-----|----------------------------------------------|-------|-----------|-------------|--|

| AIN7          | 41  | CVBS7                                        |       |           | SCART1-B    |  |

| AIN1          | 42  | CVBS1                                        | YC1-Y | YPrPb1-Y  | SCART2-CVBS |  |

| AIN8          | 43  | CVBS8                                        |       |           | SCART1-R    |  |

| AIN2          | 44  | CVBS2                                        | YC2-Y | YPrPb2-Y  |             |  |

| AIN9          | 45  | CVBS9                                        |       |           | SCART1-G    |  |

| AIN3          | 46  | CVBS3                                        | YC3-Y | YPrPb2-Pb |             |  |

| AIN10         | 57  | CVBS10                                       |       |           |             |  |

| AIN4          | 58  | CVBS4                                        | YC1-C | YPrPb1-Pb | SCART2-B    |  |

| AIN11         | 59  | CVBS11                                       |       |           | SCART1-CVBS |  |

| AIN5          | 60  | CVBS5                                        | YC2-C | YPrPb1-Pr | SCART2-R    |  |

| AIN12         | 61  | Not available                                |       |           |             |  |

| AIN6          | 62  | CVBS6                                        | YC3-C | YPrPb2-Pr | SCART2-G    |  |

Table 10. Input Channel Assignments

Table 11. Manual Mux Settings for All ADCs (Set ADC\_SW\_MAN\_EN to 1)

|               | ADC0          |               | ADC1          |               | ADC2          |               | ADC3          |

|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|

| ADC0_SW [3:0] | Connected To  | ADC1_SW [3:0] | Connected To  | ADC2_SW [3:0] | Connected To  | ADC3_SW [3:0] | Connected To  |

| 0000          | No connection |

| 0001          | AIN1          | 0001          | No connection | 0001          | No connection | 0001          | No connection |

| 0010          | AIN2          | 0010          | No connection | 0010          | AIN2          | 0010          | No connection |

| 0011          | AIN3          | 0011          | AIN3          | 0011          | No connection | 0011          | No connection |

| 0100          | AIN4          | 0100          | AIN4          | 0100          | No connection | 0100          | AIN4          |

| 0101          | AIN5          | 0101          | AIN5          | 0101          | AIN5          | 0101          | No connection |

| 0110          | AIN6          | 0110          | AIN6          | 0110          | AIN6          | 0110          | No connection |

| 0111          | No connection |

| 1000          | No connection |

| 1001          | AIN7          | 1001          | No connection | 1001          | No connection | 1001          | AIN7          |

| 1010          | AIN8          | 1010          | No connection | 1010          | AIN8          | 1010          | No connection |

| 1011          | AIN9          | 1011          | AIN9          | 1011          | No connection | 1011          | No connection |

| 1100          | AIN10         | 1100          | AIN10         | 1100          | No connection | 1100          | No connection |

| 1101          | AIN11         | 1101          | AIN11         | 1101          | AIN11         | 1101          | No connection |

| 1110          | AIN12         | 1110          | AIN12         | 1110          | AIN12         | 1110          | No connection |

| 1111          | No connection |

#### RGB\_IP\_SEL, Address 0xF1 [0]

For SCART input, R, G, and B signals can be input either on AIN4, AIN5, and AIN6 or on AIN7, AIN8, and AIN9.

0 (default)—B is input on AIN4, R is input on AIN5, and G is input on AIN6.

1—B is input on AIN7, R is input on AIN8, and G is input on AIN9.

#### MANUAL INPUT MUXING

By accessing a set of manual override muxing registers, the analog input muxes of the ADV7188 can be controlled directly. This is referred to as manual input muxing. Manual input muxing overrides other input muxing control bits, including INSEL and SDM\_SEL.

Manual muxing is activated by setting the ADC\_SW\_MAN\_EN bit. It only affects the analog switches in front of the ADCs.

Therefore, if the settings of INSEL and the manual input muxing bits (ADC0\_SW/ADC1\_SW/ADC2\_SW/ADC3\_SW) contradict each other, the ADC0\_SW/ADC1\_SW/ADC2\_SW/ ADC3\_SW settings apply and INSEL and SDM\_SEL are ignored.

Manual input muxing controls only the analog input muxes. For the follow-on blocks to process video data in the correct format, however, INSEL must still be used to indicate whether the input signal is of YPbPr, Y/C, or CVBS format.

Restrictions in the channel routing are imposed by the analog signal routing inside the IC; each input pin cannot be routed to each ADC. Refer to Figure 6 for an overview on the routing capabilities inside the chip. The four mux sections can be controlled by the reserved control signal buses, ADC0\_SW [3:0], ADC1\_SW [3:0], ADC2\_SW [3:0], and ADC3\_SW [3:0]. Table 11 explains the control words used.

ADC\_SW\_MAN\_EN, Manual Input Muxing Enable, Address 0xC4 [7]

ADC0\_SW [3:0], ADC0 Mux Configuration, Address 0xC3 [3:0]

ADC1\_SW [3:0], ADC1 Mux Configuration, Address 0xC3 [7:4]

ADC2\_SW [3:0], ADC2 Mux Configuration, Address 0xC4 [3:0]

ADC3\_SW [3:0], ADC3 Mux Configuration, Address 0xF3 [7:4]

See Table 11.

### XTAL CLOCK INPUT PIN FUNCTIONALITY XTAL\_TTL\_SEL, Address 0x13 [2]

The crystal pad is normally part of the crystal oscillator circuit, powered from a 1.8 V supply. For optimal clock generation, the slice level of the input buffer of this circuit is at approximately half the supply voltage, making it incompatible with TLL level signals.

0 (default)—A crystal is used to generate the ADV7188 clock.

1—An external TTL level clock is supplied. A different input buffer can be selected that slices at TTL-compatible levels. This inhibits operation of the crystal oscillator and therefore can only be used when a clock signal is applied.

# 28.63636 MHz CRYSTAL OPERATION *EN28XTAL, Address 0x1D* [6]

The ADV7188 can operate on two different base crystal frequencies. Selecting one over the other may be desirable in systems in which board crosstalk between different components leads to undesirable interference between video signals. It is recommended to use a crystal of frequency 28.63636 MHz to clock the ADV7188.

0 (default)—The crystal frequency is 27 MHz.

1—The crystal frequency is 28.63636 MHz.

#### **ANTIALIASING FILTERS**

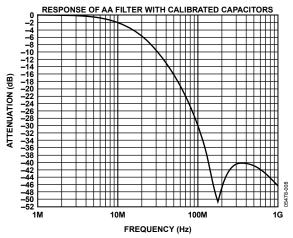

The ADV7188 has optional antialiasing filters on each of the four input channels. The filters are designed for SD video with approximately 6 MHz bandwidth.

A plot of the filter response is shown in Figure 8. The filters can be individually enabled via I<sup>2</sup>C under the control of AA\_FILT\_EN [3:0].

#### AA\_FILT\_EN [0], Address 0xF3 [0]

0 (default)—The filter on Channel 0 is disabled.

1—The filter on Channel 0 is enabled.

#### AA\_FILT\_EN [1], Address 0xF3 [1]

0 (default)—The filter on Channel 1 is disabled.

1—The filter on Channel 1 is enabled.

#### AA\_FILT\_EN [2], Address 0xF3 [2]

0 (default)—The filter on Channel 2 is disabled.

1—The filter on Channel 2 is enabled.

#### AA\_FILT\_EN [3], Address 0xF3 [3]

0 (default)—The filter on Channel 3 is disabled.

1—The filter on Channel 3 is enabled.

Figure 8. Frequency Response of Internal ADV7188 Antialiasing Filters

### SCART AND FAST BLANKING

The ADV7188 can support simultaneous processing of CVBS and RGB standard definition signals to enable SCART compatibility and overlay functionality.

This function is available when INSEL [3:0] is set appropriately (see Table 9). Timing extraction is always performed by the ADV7188 on the CVBS signal. However, a combination of the CVBS and RGB inputs can be mixed and output under the control of the I<sup>2</sup>C registers and the FB pin.

Four basic modes are supported:

- Static Switch Mode. The FB pin is not used. The timing is extracted from the CVBS signal, and either the CVBS content or RGB content can be output under the control of CVBS\_RGB\_SEL. This mode allows the selection of a full-screen picture from either source. Overlay is not possible in static switch mode.

- Fixed Alpha Blending. The FB pin is not used. The timing is extracted from the CVBS signal, and an alpha blended combination of the video from the CVBS and RGB sources is output. This alpha blending is applied to the full screen. The alpha blend factor is selected with the I<sup>2</sup>C signal

MAN\_ALPHA\_VAL [6:0]. Overlay is not possible in fixed alpha blending mode.

- Dynamic Switching (Fast Mux). The FB pin can be used to select the source. This enables dynamic multiplexing between the CVBS and RGB sources. With default settings, when Logic 1 is applied to the FB pin, the RGB source is selected; when Logic 0 is applied to the FB pin, the CVBS source is selected. This mode is suitable for the overlay of subtitles, teletext, or other material. Typically, the CVBS source carries the main picture, and the RGB source has the overlay data.

- Dynamic Switching with Edge Enhancement. This provides the same functionality as the dynamic switching mode, but with the benefit of Analog Devices' proprietary edgeenhancement algorithms, which improve the visual appearance of transitions for signals from a wide variety of sources.

#### System Diagram

A block diagram of the ADV7188 fast blanking configuration is shown in Figure 9.

The CVBS signal is processed by the ADV7188 and converted to YPrPb. The RGB signals are processed by a color space converter (CSC), and samples are converted to YPrPb. Both sets of YPrPb signals are input to the subpixel blender, which can be configured to operate in any of the four modes previously outlined in this section.

The fast blank position resolver determines the time position of the FB pin accurately (<1 ns). This position information is then used by the subpixel blender in dynamic switching modes, enabling the ADV7188 to implement high performance multiplexing between the CVBS and RGB sources even when the RGB data source is completely asynchronous to the sampling crystal reference.

An antialiasing filter is required on all four data channels (R, G, B, and CVBS). The order of this filter is reduced because all signals are sampled at 54 MHz.

The switched or blended data is output from the ADV7188 in the standard output formats (see Table 102).

#### **FAST BLANK CONTROL**

#### FB\_MODE [1:0], Address 0xED [1:0]

FB\_MODE controls which fast blank mode is selected.

| Table 12. FB_MODE [1:0] Function |                                         |  |  |

|----------------------------------|-----------------------------------------|--|--|

| FB_MODE [1:0]                    | Description                             |  |  |

| 00 (default)                     | Static switch mode                      |  |  |

| 01                               | Fixed alpha blending                    |  |  |

| 10                               | Dynamic switching (fast mux)            |  |  |

| 11                               | Dynamic switching with edge enhancement |  |  |

### Static Mux Selection Control

#### CVBS\_RGB\_SEL, Address 0xED [2]

CVBS\_RGB\_SEL controls whether the video from the CVBS or RGB source is selected for output from the ADV7188.

0 (default)—Data from the CVBS source is selected for output.

1-Data from the RGB source is selected for output.

#### Alpha Blend Coefficient

#### MAN\_ALPHA\_VAL [6:0], Address 0xEE [6:0]

When fixed alpha blending is selected (FB\_MODE [1:0] = 01), MAN\_ALPHA\_VAL [6:0] determines the proportion in which the video from the CVBS and RGB sources are blended. Equation 1 shows how these bits affect the video output.

$$Video_{out} = Video_{CVBS} \times \left(1 - \frac{MAN\_ALPHA\_VAL [6:0]}{64}\right) + Video_{RGB} \times \frac{MAN\_ALPHA\_VAL [6:0]}{64}$$

(1)

The maximum valid value for MAN\_ALPHA\_VAL [6:0] is 1000000, such that the alpha blender coefficients remain between 0 and 1. The default value for MAN\_ALPHA\_VAL [6:0] is 0000000.

Figure 9. Fast Blanking Configuration

#### Fast Blank Edge Shaping FB\_EDGE\_SHAPE [2:0], Address 0xEF [2:0]

To improve the picture transition for high speed fast blank switching, an edge-shaping mode is available on the ADV7188. Depending on the format of the RGB inputs, it may be advantageous to apply different levels of edge shaping. The levels are selected via the FB\_EDGE\_SHAPE [2:0] bits. Users are advised to try each of the settings and select the setting that is most visually pleasing on their system.

#### Table 13. FB\_EDGE\_SHAPE [2:0] Function

| Description          |

|----------------------|

| No edge shaping      |

| Level 1 edge shaping |

| Level 2 edge shaping |

| Level 3 edge shaping |

| Level 4 edge shaping |

| Not valid            |

|                      |

#### **Contrast Reduction**

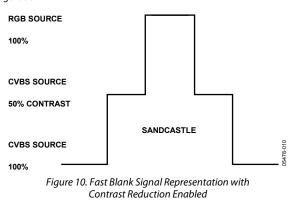

For overlay applications, text can be more readable if the contrast of the video directly behind the text is reduced. To enable the definition of a window of reduced contrast behind inserted text, the signal applied to the FB pin can be interpreted as a trilevel signal, as shown in Figure 10.

#### **Contrast Reduction Enable**

#### CNTR\_ENABLE, Address 0xEF [3]

This bit enables the contrast reduction feature and changes the meaning of the signal applied to the FB pin.

0 (default)—The contrast reduction feature is disabled, and the fast blank signal is interpreted as a bilevel signal.

1—The contrast reduction feature is enabled, and the fast blank signal is interpreted as a trilevel signal.

#### **Contrast Mode**

#### CNTR\_MODE [1:0], Address 0xF1 [3:2]

The contrast level in the selected contrast reduction box is selected using the CNTR\_MODE [1:0] bits.

| Table 14. CNTR | _MODE [1:0] | Function |

|----------------|-------------|----------|

|----------------|-------------|----------|

| CNTR_MODE [1:0] | Description |  |  |

|-----------------|-------------|--|--|

| 00 (default)    | 25%         |  |  |

| 01              | 50%         |  |  |

| 10              | 75%         |  |  |

| 11              | 100%        |  |  |

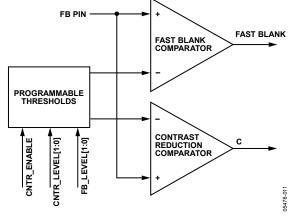

#### Fast Blank and Contrast Reduction Programmable Thresholds

The internal fast blank and contrast reduction signals are resolved from the trilevel FB signal using two comparators, as shown in Figure 11. To facilitate compliance with different input level standards, the reference level to these comparators is programmable via FB\_LEVEL [1:0] and CNTR\_LEVEL [1:0]. The resulting thresholds are given in Table 15.

#### FB\_LEVEL [1:0], Address 0xF1 [5:4]

These bits control the reference level for the fast blank comparator.

#### CNTR\_LEVEL [1:0], Address 0xF1 [7:6]

These bits control the reference level for the contrast reduction comparator.

Figure 11. Fast Blank and Contrast Reduction Programmable Threshold

| FB_LEVEL [1:0] | CNTR_LEVEL [1:0]                     | Fast Blanking Threshold (V)                                                                                                                               | Contrast Reduction Threshold (V)                                                                                                                                                                                                                                      |

|----------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00 (default)   | XX                                   | 1.4                                                                                                                                                       | n/a                                                                                                                                                                                                                                                                   |

| 01             | XX                                   | 1.6                                                                                                                                                       | n/a                                                                                                                                                                                                                                                                   |

| 10             | XX                                   | 1.8                                                                                                                                                       | n/a                                                                                                                                                                                                                                                                   |

| 11             | XX                                   | 2.0                                                                                                                                                       | n/a                                                                                                                                                                                                                                                                   |

| 00 (default)   | 00                                   | 1.6                                                                                                                                                       | 0.4                                                                                                                                                                                                                                                                   |

| 01             | 01                                   | 1.8                                                                                                                                                       | 0.6                                                                                                                                                                                                                                                                   |

| 10             | 10                                   | 2.0                                                                                                                                                       | 0.8                                                                                                                                                                                                                                                                   |

| 11             | 11                                   | 2.2                                                                                                                                                       | 2.0                                                                                                                                                                                                                                                                   |

|                | 01<br>10<br>11<br>00 (default)<br>01 | 00 (default)         XX           01         XX           10         XX           11         XX           00 (default)         00           01         01 | 00 (default)         XX         1.4           01         XX         1.6           10         XX         1.8           11         XX         2.0           00 (default)         00         1.6           01         01         1.8           10         10         2.0 |

#### Table 15. Fast Blank and Contrast Reduction Programmable Threshold I<sup>2</sup>C Controls

#### FB\_INV, Address 0xED [3], Write Only

The interpretation of the polarity of the signal applied to the FB pin can be changed using FB\_INV.

0 (default)—The fast blank pin is active high.

1—The fast blank pin is active low.

#### Readback of FB Pin Status

#### FB\_STATUS [3:0], Address 0xED [7:4]

FB\_STATUS [3:0] is a readback value that provides the system information on the status of the FB pins, as shown in Table 16.

#### FB Timing

#### FB\_SP\_ADJUST [3:0], Address 0xEF [7:4]

The critical information extracted from the FB signal is the time at which it switches relative to the input video. Due to small timing inequalities either on the IC or on the PCB, it may be necessary to adjust the result by a fraction of one clock cycle. This is controlled by FB\_SP\_ADJUST [3:0].

Each LSB of FB\_SP\_ADJUST [3:0] corresponds to <sup>1</sup>/s<sup>th</sup> of an ADC clock cycle. Increasing the value is equivalent to adding delay to the FB signal. The reset value is chosen to produce equalized channels when the ADV7188 internal antialiasing filters are enabled and there are only intentional delays on the PCB.

The default value of FB\_SP\_ADJUST [3:0] is 0100.

#### Alignment of FB Signal

#### FB\_DELAY [3:0], Address 0xF0 [3:0]

In the event of misalignment between the FB input signal and the other input signals (CVBS and RGB) or unequalized delays in their processing, it is possible to alter the delay of the FB signal in 28.63636 MHz clock cycles. (For a finer granularity delay of the FB signal, refer to the FB\_SP\_ADJUST [3:0], Address 0xEF [7:4] section.)

The default value of FB\_DELAY [3:0] is 0100.