Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# AFCT-701SDZ

10Gb Ethernet, 1310 nm, 10GBASE-LR, SFP+ Transceiver for SMF 10km links

# AVAGO

# **Data Sheet**

#### **Description**

The Avago AFCT-701SDZ transceiver is part of a family of SFP+ products. This transceiver utilizes Avago's 1310nm DFB and PIN Detector technology to provide an IEEE 10Gb Ethernet design compliant with the 10GBASE-LR standard. The AFCT-701SDZ transceiver is designed to enable 10Gb Ethernet equipment designs with very high port density based on the new electrical and mechanical specification enhancements to the well known SFP specifications developed by the SFF Committee. These specifications are referred to as SFP+ to recognize these enhancements to previous SFP specifications used for lower speed products. Avago Technologies is an active participant in the SFF Committee specification development activities.

#### **Related Products**

- AFCT-701ASDZ SFP+ 10 Gigabit Ethernet 10GBASE-LR transceiver with case temperature operated at 0-85 °C for operation in SMF link applications to 10 km

- AFBR-707SDZ SFP+ 10 Gigabit Ethernet 10GBASE-LRM transceiver for 220 meter operation in all MMF link applications including OM1 and OM2 legacy fiber cables and new high bandwidth OM3 fiber cables.

- The AFBR-703SDZ (AFBR-703ASDZ) with case temperature 0-70 (0-85) °C is an SFP+ 10 Gigabit Ethernet 10GBASE-SR transceiver for use on multimode fiber cables. It is best suited for OM3 high bandwidth MMF link applications with link lengths up to 300 meters.

- AFCT-5016Z SFP+ Evaluation Board The purpose of this SFP+ evaluation board is to provide the designer with a convenient means for evaluating SFP+ fiber optic transceivers.

#### **Features**

- Avago 1310nm DFB source and Transmitter Optical Subassembly technology

- Avago PIN detector and Receiver Optical Subassembly technology

- Typical power dissipation 850mW

- Full digital diagnostic management interface

- Avago SFP+ package design enables equipment EMI performance in high port density applications with margin to Class B limits

#### **Specifications**

- Optical interface specifications per IEEE 802.3ae 10GBASE-LR

- Electrical interface specifications per SFF Committee SFF 8431 Specifications for Enhanced 8.5 and 10 Gigabit Small Form Factor Pluggable Module "SFP+"

- Management interface specifications per SFF Committee SFF 8431 and SFF 8472 Diagnostic Monitoring Interface for Optical Transceivers

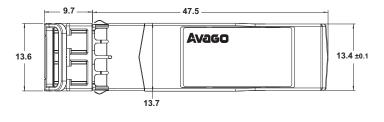

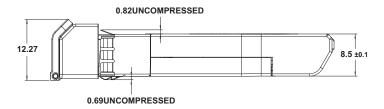

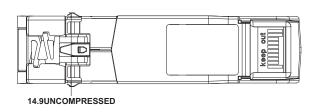

- Mechanical specifications per SFF Committee SFF 8432 Improved Pluggable Formfactor "IPF"

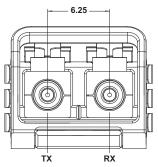

- LC Duplex optical connector interface confirming to ANSITIA/EA 604-10 (FOCIS 10A)

- Compliant to Restriction on Hazardous Substances (RoHS) per EU and China requirements

- Class 1 Eye safe per requirements of IEC 60825-1 / CDRH

# **Description**, continued

#### Installation

The AFCT-701SDZ transceiver package is compliant with the SFF 8432 Improved Pluggable Formfactor housing specification for the SFP+. It can be installed in any INF-8074 or SFF-8431/2 compliant Small Form Pluggable (SFP) port regardless of host equipment operating status The AFCT-701SDZ is hot-pluggable, allowing the module to be installed while the host system is operating and on-line. Upon insertion, the transceiver housing makes initial contact with the host board SFP cage, mitigating potential damage due to Electro-Static Discharge (ESD).

# **Digital Diagnostic Interface and Serial Identification**

The two-wire interface protocol and signaling detail are based on SFF-8431. Conventional EEPROM memory, bytes 0-255 at memory address 0xA0, is organized in compliance with SFF-8431. New digital diagnostic information, bytes 0-255 at memory address 0xA2, is compliant to SFF-8472. The new diagnostic information provides the opportunity for Predictive Failure Identification, Compliance Prediction, Fault Isolation and Component Monitoring.

#### **Predictive Failure Identification**

The AFCT-701SDZ predictive failure feature allows a host to identify potential link problems before system performance is impacted. Prior identification of link problems enables a host to service an application via "fail over" to a redundant link or replace a suspect device, maintaining system uptime in the process. For applications where ultra-high system uptime is required, a digital SFP provides a means to monitor two real-time laser metrics associated with observing laser degradation and predicting failure: average laser bias current (Tx\_Bias) and average laser optical power (Tx\_Power).

#### **Compliance Prediction**

Compliance prediction is the ability to determine if an optical transceiver is operating within its operating and environmental requirements. AFCT-701SDZ devices provide real-time access to transceiver internal supply voltage and temperature, allowing a host to identify potential component compliance issues. Received optical power is also available to assess compliance of a cable plant and remote transmitter. When operating out of requirements, the link cannot guarantee error free transmission.

#### Fault Isolation

The fault isolation feature allows a host to quickly pinpoint the location of a link failure, minimizing downtime. For optical links, the ability to identify a fault at a local device, remote device or cable plant is crucial to speeding service of an installation. AFCT-701SDZ real-time monitors of Tx\_Bias, Tx\_Power, Vcc, Temperature and Rx\_Power can be used to assess local transceiver current operating conditions. In addition, status flags TX\_DISABLE and Rx Loss of Signal (LOS) are mirrored in memory and available via the two-wire serial interface.

#### **Component Monitoring**

Component evaluation is a more casual use of the AFCT-701SDZ real-time monitors of Tx\_Bias, Tx\_Power, Vcc, Temperature and Rx\_Power. Potential uses are as debugging aids for system installation and design, and transceiver parametric evaluation for factory or field qualification. For example, temperature per module can be observed in high density applications to facilitate thermal evaluation of blades, PCI cards and systems.

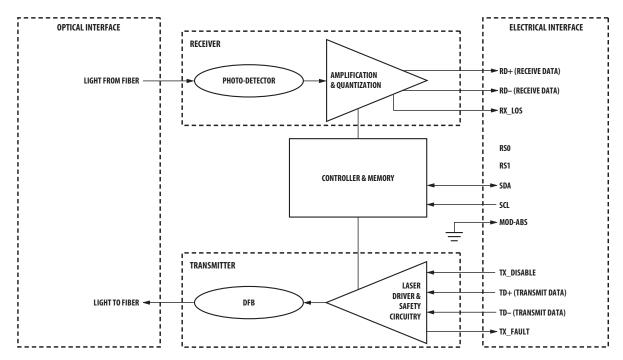

Figure 1. Transceiver functional diagram

# **Transmitter Section**

The transmitter section includes the Transmitter Optical Sub-Assembly (TOSA) and laser driver circuitry. The TOSA, containing an Avago designed and manufactured 1310 nm DFB light source, is located at the optical interface and mates with the LC optical connector. The TOSA is driven by an IC which uses the incoming differential high speed logic signal to modulate the laser diode driver current. This Tx laser driver circuit regulates the optical power at a level within the specified range.

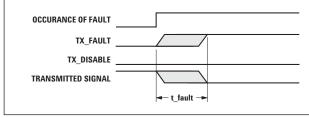

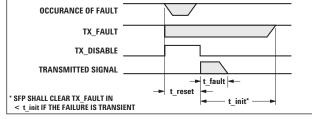

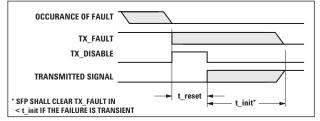

#### Transmit Disable (TX\_DISABLE)

The AFCT-701SDZ accepts an LVTTL compatible transmit disable control signal input which shuts down the transmitter optical output. A high signal implements this function while a low signal allows normal transceiver operation. In the event of a fault (e.g. eye safety circuit activated), cycling this control signal resets the module as depicted in Figure 5. An internal pull up resistor disables the transceiver transmitter until the host pulls the input low. TX\_DISABLE can also be asserted via the two-wire interface (address A2h, byte 110, bit 6) and monitored (address A2h, byte 110, bit 7).

The contents of A2h, byte 110, bit 6 are logic OR'd with hardware TX\_DISABLE (contact 3) to control transmitter operation. The normal behavior of this feature is to reset a TX disabled transceiver to TX enabled when it is power cycled or hot-plugged.

# Transmit Fault (TX\_FAULT)

A catastrophic laser fault will activate the transmitter signal, TX\_FAULT, and disable the laser. This signal is an open collector output (pull-up required on the host board). A low signal indicates normal laser operation and a high signal indicates a fault. A fault is defined as laser power below or above the specified IEEE 802.3ae specified min/max range. The TX\_FAULT will be latched high when a laser fault occurs and is cleared by toggling the TX\_DISABLE input or power cycling the transceiver. The transmitter fault condition can also be monitored via the two-wire serial interface (address A2, byte 110, bit 2).

#### **Receiver Section**

The receiver section includes the Receiver Optical Sub-Assembly (ROSA) and the amplification/quantization circuitry. The ROSA, containing a PIN photodiode and custom transimpedance amplifier, is located at the optical interface and mates with the LC optical connector. The ROSA output is fed to a custom IC that provides postamplification and quantization.

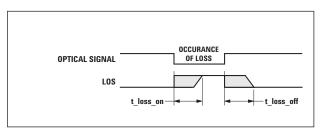

# Receiver Loss of Signal (Rx\_LOS)

The post-amp IC also includes transition detection circuitry which monitors the AC level of incoming optical signals and provides a LVTTL/CMOS compatible status signal to the host. A high status signal indicates loss of modulated signal, indicating link failures such as broken fiber or failed transmitter. Rx\_LOS can also be monitored via the two-wire serial interface (address A2h, byte 110, bit 1).

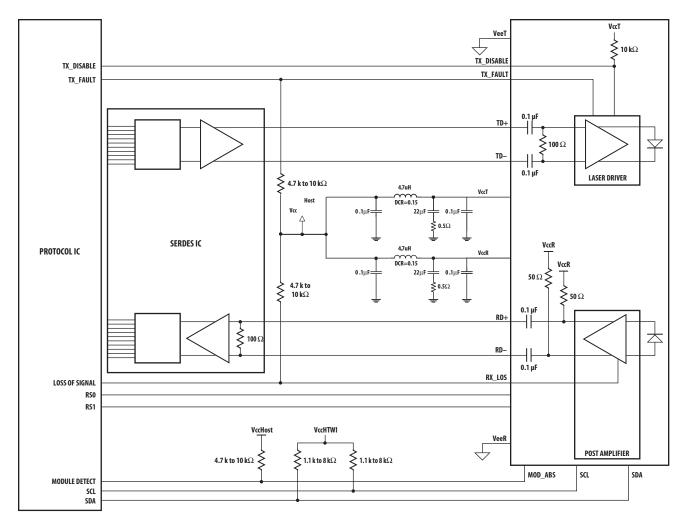

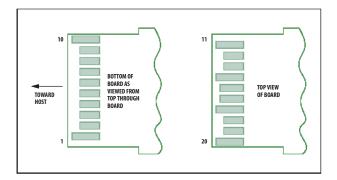

#### Functional Data I/O

The AFCT-701SDZ interfaces with the host circuit board through the twenty contact SFP+ electrical connector. See Table 2 for contact descriptions. The module edge connector is shown in Figure 3. The host board layout for this interface is depicted in Figure 6.

The AFCT-701SDZ high speed transmit and receive interfaces require SFF-8431 compliant signal lines on the host board. To simplify board requirements, biasing resistors and AC coupling capacitors are incorporated into the SFP+ transceiver module (per SFF-8431) and hence are not required on the host board. The TX\_DISABLE, TX\_FAULT and RX\_LOS signals require LVTTL signals on the host board (per SFF-8431) if used. If an application does not take advantage of these functions, care must be taken to ground TX\_DISABLE to enable normal operation.

Figure 2 depicts the recommended interface circuit to link the AFCT-701SDZ to supporting physical layer ICs. Timing for the dedicated SFP+ control signals implemented in the transceiver are listed in Figure 5.

# **Application Support**

An Evaluation Kit and Reference Designs are available to assist in evaluation of the AFCT-701SDZ. Please contact your local Field Sales representative for availability and ordering details.

#### Caution

There are no user serviceable parts nor maintenance requirements for the AFCT-701SDZ, All mechanical adjustments are made at the factory prior to shipment. Tampering with, modifying, misusing or improperly handling the AFCT-701SDZ will void the product warranty. It may also result in improper operation and possibly overstress the laser source. Performance degradation or device failure may result. Connection of the AFCT-701SDZ to a light source not compliant with IEEE Std. 802.3ae Clause 52 and SFF-8341 specifications, operating above maximum operating conditions or in a manner inconsistent with it's design and function may result in exposure to hazardous light radiation and may constitute an act of modifying or manufacturing a laser product. Persons performing such an act are required by law to recertify and re-identify the laser product under the provisions of U.S. 21 CFR (Subchapter J) and TUV.

# **Customer Manufacturing Processes**

This module is pluggable and is not designed for aqueous wash, IR reflow, or wave soldering processes.

# **Ordering Information**

Please contact your local field sales engineer or one of Avago Technologies franchised distributors for ordering information. For technical information, please visit Avago Technologies' WEB page at www.avagotech.com. For information related to SFF Committee documentation visit www.sffcommittee.org.

#### **Regulatory Compliance**

The AFCT-701SDZ complies with all applicable laws and regulations as detailed in Table 1. Certification level is dependent on the overall configuration of the host equipment. The transceiver performance is offered as a figure of merit to assist the designer.

### Electrostatic Discharge (ESD)

The AFCT-701SDZ is compatible with ESD levels found in typical manufacturing and operating environments as described in Table 1. In the normal handling and operation of optical transceivers, ESD is of concern in two circumstances.

The first case is during handling of the transceiver prior to insertion into an SFP compliant cage. To protect the device, it's important to use normal ESD handling precautions. These include use of grounded wrist straps, work-benches and floor wherever a transceiver is handled.

The second case to consider is static discharges to the exterior of the host equipment chassis after installation. If the optical interface is exposed to the exterior of host equipment cabinet, the transceiver may be subject to system level ESD requirements.

#### Electromagnetic Interference (EMI)

Equipment incorporating 10 gigabit transceivers is typically subject to regulation by the FCC in the United States, CENELEC EN55022 (CISPR 22) in Europe and VCCI in Japan. The AFCT-701SDZ enables equipment compliance to these standards detailed in Table 1. The metal housing and shielded design of the AFCT-701SDZ minimizes the EMI challenge facing the equipment designer. For superior EMI performance it is recommended that equipment designs utilize SFP+ cages per SFF 8432.

#### RF Immunity (Susceptibility)

Due to its shielded design, the EMI immunity of the AFCT-701SDZ exceeds typical industry standards.

#### **Eye Safety**

The AFCT-701SDZ provides Class 1 (single fault tolerant) eye safety by design and has been tested for compliance with the requirements listed in Table 1. The eye safety circuit continuously monitors the optical output power level and will disable the transmitter upon detecting a condition beyond the scope of Class 1 certification Such conditions can be due to inputs from the host board (Vcc fluctuation, unbalanced code) or a fault within the transceiver. US CDRH and EU TUV certificates are listed in table 1.

### **Flammability**

The AFCT-701SDZ optical transceiver is made of metal and high strength, heat resistant, chemical resistant and UL 94V-0 flame retardant plastic.

**Table 1. Regulatory Compliance**

| Feature                                                      | Test Method                                                                                                                                                                       | Performance                                                                                                              |  |  |

|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|

| Electrostatic Discharge (ESD) to the Electrical Contacts     | MIL-STD883C Method 3015.4<br>JEDEC DESD22-A11-4-B                                                                                                                                 | Class 1 (> 1KV) for high speed I/O pins<br>Class 1 (> 2KV) for all other pins                                            |  |  |

| Electrostatic Discharge (ESD)<br>to the Duplex LC Receptacle | IEC 61000-4-2                                                                                                                                                                     | Typically, no damage occurs with 25 kV when the duplex LC connector receptacle is contacted by a Human Body Model probe. |  |  |

| Life Traffic ESD Immunity                                    | IEC 61000-4-2                                                                                                                                                                     | 10 contacts of 8 kV on the electrical faceplate with device inserted into a panel.                                       |  |  |

| Life Traffic ESD Immunity                                    | IEC 61000-4-2                                                                                                                                                                     | Air discharge of 15 kV (min.) contact to connector without damage.                                                       |  |  |

| Electromagnetic<br>Interference (EMI)                        | FCC Class B<br>CENELEC EN55022 Class B<br>(CISPR 22A)<br>VCCI Class 1                                                                                                             | System margins are dependent on customer board and chassis design.                                                       |  |  |

| RF Immunity                                                  | IEC 61000-4-3                                                                                                                                                                     | Typically shows no measurable effect from a 10 V/m field swept from 80MHz to 1 GHz                                       |  |  |

| Laser Eye Safety and Equipment Type Testing                  | US FDA CDRH AEL Class 1<br>US21 CFR, Subchapter J per<br>Paragraphs 1002.10 and 1002.12                                                                                           | CDRH Accession No. 9521220-158<br>Pending Completion                                                                     |  |  |

| TÜV Rheinland Product Safety  RAMPROVED                      | (IEC) EN60825-1: 1994 + A11 + A2<br>(IEC) EN60825-2: 1994 + A1<br>(IEC) EN60950: 1992 + A1 + A2 + A3<br>+ A4 + A11                                                                |                                                                                                                          |  |  |

| Component Recognition                                        | Underwriters Laboratories and Canadian<br>Standards Association Joint Component<br>Recognition for Information Technology<br>Equipment including Electrical Business<br>Equipment | UL file E173874                                                                                                          |  |  |

| RoHS Compliance                                              | RoHS Directive 2002/95/EC and it's amendment directives 6/6                                                                                                                       | SGS Test Report No. LPC1/00895/08<br>CTS ref. CTS/08-0238/Avago                                                          |  |  |

Figure 2. Typical application configuration

**Table 2. Contact Description**

| Contact | Symbol     | Function/Description                                                               | Notes  |

|---------|------------|------------------------------------------------------------------------------------|--------|

| 1       | VeeT       | Transmitter Signal Ground                                                          | Note 1 |

| 2       | TX_FAULT   | Transmitter Fault (LVTTL-O) – High indicates a fault condition                     | Note 2 |

| 3       | TX_DISABLE | Transmitter Disable (LVTTL-I) – High or open disables the transmitter              | Note 3 |

| 4       | SDA        | Two Wire Serial Interface Data Line (LVCMOS – I/O) (same as MOD-DEF2 in INF-8074)  | Note 4 |

| 5       | SCL        | Two Wire Serial Interface Clock Line (LVCMOS – I/O) (same as MOD-DEF1 in INF-8074) | Note 4 |

| 6       | MOD_ABS    | Module Absent (Output), connected to VeeT or VeeR in the module                    | Note 5 |

| 7       | RS0        | Rate Select 0 - Not used, Presents high input impedance.                           |        |

| 8       | RX_LOS     | Receiver Loss of Signal (LVTTL-O)                                                  | Note 2 |

| 9       | RS1        | Rate Select 1 - Not used, Presents high input impedance.                           |        |

| 10      | VeeR       | Receiver Signal Ground                                                             | Note 1 |

| 11      | VeeR       | Receiver Signal Ground                                                             | Note 1 |

| 12      | RD-        | Receiver Data Out Inverted (CML-O)                                                 |        |

| 13      | RD+        | Receiver Data Out (CML-O)                                                          |        |

| 14      | VeeR       | Receiver Signal Ground                                                             |        |

| 15      | VccR       | Receiver Power + 3.3 V                                                             |        |

| 16      | VccT       | Transmitter Power + 3.3 V                                                          |        |

| 17      | VeeT       | Transmitter Signal Ground                                                          | Note 1 |

| 18      | TD+        | Transmitter Data In (CML-I)                                                        |        |

| 19      | TD-        | Transmitter Data In Inverted (CML-I)                                               |        |

| 20      | VeeT       | Transmitter Signal Ground                                                          | Note 1 |

|         |            |                                                                                    |        |

- 1. The module signal grounds are isolated from the module case.

- 2. This is an open collector/drain output that on the host board requires a 4.7 k $\Omega$  to 10 k $\Omega$  pullup resistor to VccHost. See Figure 2.

- 3. This input is internally biased high with a 4.7 k $\Omega$  to 10 k $\Omega$  pullup resistor to VccT.

- 4. Two-Wire Serial interface clock and data lines require an external pullup resistor dependent on the capacitance load.

- 5. This is a ground return that on the host board requires a 4.7 k $\Omega$  to 10 k $\Omega$  pullup resistor to VccHost.

Figure 3. Module edge connector contacts

#### **Table 3. Absolute Maximum Ratings**

Stress in excess of any of the individual Absolute Maximum Ratings can cause immediate catastrophic damage to the module even if all other parameters are within Recommended Operating Conditions. It should not be assumed that limiting values of more than one parameter can be applied concurrently. Exposure to any of the Absolute Maximum Ratings for extended periods can adversely affect reliability.

| Parameter                              | Symbol         | Minimum | Maximum | Unit | Notes  |

|----------------------------------------|----------------|---------|---------|------|--------|

| Storage Temperature                    | T <sub>S</sub> | -40     | 100     | С    |        |

| Case Operating Temperature             | T <sub>C</sub> | -40     | 100     | С    |        |

| Relative Humidity                      | RH             | 5       | 95      | %    |        |

| Supply Voltage                         | VccT, VccR     | -0.3    | 3.8     | V    | Note 1 |

| Low Speed Input Voltage                |                | -0.5    | Vcc+0.5 | V    |        |

| Two-Wire Interface Input Voltage       |                | -0.5    | Vcc+0.5 | V    |        |

| High Speed Input Voltage, Single Ended |                | -0.3    | Vcc+0.5 | V    |        |

| High Speed Input Voltage, Differential |                |         | 2.5     | V    |        |

| Low Speed Output Current               |                | -20     | 20      | mA   |        |

| Optical Receiver Input Average Power   |                |         | 1.5     | dBm  |        |

#### Note:

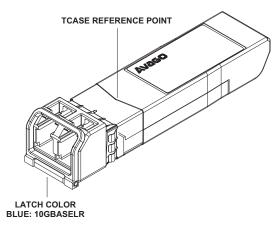

#### **Table 4. Recommended Operating Conditions**

Recommended Operating Conditions specify parameters for which the electrical and optical characteristics hold unless otherwise noted. Optical and electrical charactristics are not defined for operation outside the Recommended Operating Conditions, reliability is not implied and damage to the module may occur for such operation over an extended period of time. The SFP+ Module Power Supply Requirements are specified in the latest revision of SFF 8431 MSA.

| Parameter                                                | Symbol         | Minimum | Maximum | Unit  | Notes  |

|----------------------------------------------------------|----------------|---------|---------|-------|--------|

| Case Operating Temperature                               | T <sub>C</sub> | 0       | 70      | °C    | Note 1 |

| Module Supply Voltage                                    | VccT, VccR     | 3.135   | 3.465   | V     |        |

| Signal Rate                                              |                | 10.311  | 10.313  | GBd   |        |

| Power Supply Noise Tolerance including Ripple            |                |         | 66      | mVp-p | Note 2 |

| Tx Input Single Ended DC<br>Voltage Tolerance (Ref VeeT) | V              | -0.3    | 4.0     | V     |        |

| Rx Output Single Ended Voltage Tolerance                 | V              | -0.3    | 4.0     | V     |        |

<sup>1.</sup> The module supply voltages, VccT and VccR must not differ by more than 0.5 V or damage to the device may occur.

<sup>1.</sup> Ambient operating temperature limits are based on the Case Operating Temperature limits and are subject to the host system thermal design. See Figure 6 for the module Tc reference point.

<sup>2.</sup> The Power Supply Filter (PSF) and resulting Power Supply Noise Tolerance (PSNT) are specified in the SFF 8431 MSA. The PSNT value applies over the range from 10Hz to 10MHz.

# **Table 5. Low Speed Signal Electrical Characteristics**

The following characteristics are defined over the Recommended Operating Conditions unless otherwise noted. Typical values are for  $Tc = 40^{\circ}C$ . VccT and VccR = 3.3 V.

| Parameter             | Symbol            | Minimum | Typical | Maximum    | Unit | Notes  |

|-----------------------|-------------------|---------|---------|------------|------|--------|

| Module Supply Current | I <sub>CC</sub>   |         | 258     | 289        | mA   | Note 1 |

| Power Dissipation     | P <sub>DISS</sub> |         | 850     | 1000       | mW   |        |

| TX_FAULT, RX_LOS      | I <sub>OH</sub>   | - 50    |         | + 37.5     | μΑ   | Note 2 |

|                       | $V_{OL}$          | - 0.3   |         | 0.4        | V    |        |

| TX_DISABLE            | V <sub>IH</sub>   | 2.0     |         | VccT + 0.3 | V    | Note 3 |

|                       | $V_{IL}$          | -0.3    |         | 0.8        | V    |        |

#### Notes:

- 1. Supply current includes both VccT and VccR connections.

- 2. Measured with a 4.7 k  $\Omega$  load to VccHost.

- 3. TX\_DISABLE has an internal 4.7 k $\Omega$  to 10 k $\Omega$  pull-up to VccT

# **Table 6. High Speed Signal Electrical Characteristics**

The following characteristics are defined over the Recommended Operating Conditions unless otherwise noted.

| Parameter                                                                    | Symbol                | Minimum | Typical | Maximum | Unit    | Notes         |

|------------------------------------------------------------------------------|-----------------------|---------|---------|---------|---------|---------------|

| Tx Input Differential Voltage,  (TD +) - (TD-)                               | VI                    | 180     |         | 700     | mV      | Note 1        |

| Tx Input AC Common Mode Voltage Tolerance                                    |                       |         |         | 15      | mV(RMS) |               |

| Tx Input Differential S-parameter (100 $\Omega$ Ref.)                        | SDD11                 |         |         | -12     | dB      | 0.01-1.0 GHz  |

|                                                                              |                       |         |         | Note 3  | dB      | 1.0-11.1 GHz  |

| Tx Input Reflected Differential to Common Mode Conversion (25 $\Omega$ Ref.) | SCD11                 |         |         | -10     | dB      | 0.01-11.1 GHz |

| Rx Output Differential Voltage,  (RD +) - (RD-)                              | Vo                    | 300     |         | 850     | mV      | Note 2        |

| Rx Output Termination Mismatch @ 1MHz                                        | $\Delta Z_{\text{m}}$ |         |         | 5       | %       |               |

| Rx Output AC Common Mode Voltage                                             |                       |         |         | 7.5     | mV(RMS) | Note 5        |

| Rx Output Output Rise and Fall Time (20% to 80%)                             | tr, tf                | 28      |         |         | ps      |               |

| Rx Output Total Jitter                                                       | ŢJ                    |         |         | 0.70    | Ulp-p   |               |

| Rx Output Deterministic Jitter                                               | DJ                    |         |         | 0.42    | Ulp-p   |               |

| Rx Output Differential S-parameter                                           | SDD22                 |         |         | -12     | dB      | 0.01-1.0 GHz  |

| (100 Ω Ref.)                                                                 |                       |         |         | Note 4  | dB      | 1.0-11.1 GHz  |

| Rx Output Common Mode Reflection                                             | SCC22                 |         |         | -6      | dB      | 0.01-2.5 GHz  |

| Coefficient (25 Ω Ref.)                                                      |                       |         |         | -3      | dB      | 2.5-11.1 GHz  |

| Receiver Output Eye Mask                                                     |                       |         |         |         |         | See Figure 4a |

- 1. Internally AC coupled and terminated (100 Ohm differential).

- 2. Internally AC coupled but requires an external load termination (100 Ohm differential).

- 3. Reflection Coefficient given by equation SDD11(dB)=Max(-12 + 2\*SQRT(f) -6.3+13Log10(f/5.5)), with f in GHz.

- $4. \ \ Differential\ Output\ S-parameter\ given\ by\ equation\ SDD22(dB) = Max(-12 + 2*SQRT(f)\ -6.3 + 13Log10(f/5.5)),\ with\ f\ in\ GHz.$

- 5. The RMS value is measured by calculating the standard deviation of the histogram for one UI of the common mode signal.

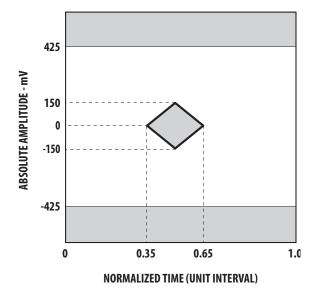

Figure 4a. Receiver Electrical Optical Eye Mask Definition

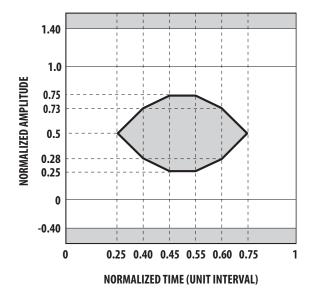

Figure 4b. Transmitter Optical Eye Mask Definition

**Table 7. Two-Wire Interface Electrical Characteristics**

| Parameter                                 | Symbol                        | Min.          | Max.          | Unit | Conditions                                               |

|-------------------------------------------|-------------------------------|---------------|---------------|------|----------------------------------------------------------|

| Host Vcc Range                            | VccHTWI                       | 3.135         | 3.465         | V    |                                                          |

| SCL and SDA                               | V <sub>OL</sub>               | 0.0           | 0.40          | V    | Rp <sup>[1]</sup> pulled to VccHTWI,                     |

|                                           | V <sub>OH</sub>               | VccHTWI - 0.5 | VccHTWI + 0.3 | V    | measured at host side of connector                       |

| SCL and SDA                               | V <sub>IL</sub>               | -0.3          | VccT*0.3      | V    |                                                          |

|                                           | V <sub>IH</sub>               | VccT*0.7      | VccT + 0.5    | V    |                                                          |

| Input Current on the SCL and SDA Contacts | II                            | -10           | 10            | μΑ   |                                                          |

| Capacitance on SCL and SDA Contacts       | C <sub>i</sub> <sup>[2]</sup> |               | 14            | рF   |                                                          |

| Total bus capacitance for SCL and for SDA | C <sup>p</sup> [3]            |               | 100           | pF   | At 400 kHz, 3.0 kΩ Rp, max<br>At 100 kHz, 8.0 kΩ Rp, max |

|                                           |                               |               | 290           | pF   | At 400 kHz, 1.1 kΩRp, max<br>At 100 kHz, 2.75 kΩ Rp, max |

<sup>1.</sup> Rp is the pull up resistor. Active bus termination may be used by the host in place of a pullup resistor. Pull ups can be connected to various power supplies, however the host board design shall ensure that no module contact has voltage exceeding VccT or VccR by 0.5 V nor requires the module to sink more than 3.0 mA current.

<sup>2.</sup>  $C_i$  is the capacitance looking into the module SCL and SDA contacts

<sup>3.</sup> C<sub>b</sub> is the total bus capacitance on the SCL or SDA bus.

**Table 8. Optical Specifications**

The following characteristics are defined over the Recommended Operating Conditions unless otherwise noted.

| Parameter                                | Minimum | Typical | Maximum | Units  | Notes            |

|------------------------------------------|---------|---------|---------|--------|------------------|

| Transmitter                              |         |         |         |        |                  |

| Laser OMA output power                   | -5.2    |         |         | dBm    | 1                |

| Laser mean output power                  | -8.2    |         | 0.5     | dBm    | 1                |

| Laser off power                          |         |         | -30     | dBm    | 1                |

| Extinction ratio                         | 3.5     |         |         | dB     | 1                |

| Transmitter and dispersion penalty (TDP) |         |         | 3.2     | dB     | 1                |

| Center Wavelength                        | 1260    |         | 1355    | nm     |                  |

| Side Mode Suppression Ratio - SMSR       | 30      |         |         | dB     |                  |

| RIN12OMA                                 |         |         | -128    | dB/Hz  | 1                |

| Optical Return Loss Tolerance            |         |         | 12      | dB     | 1                |

| Transmitter Output Eye Mask              |         |         |         |        | 1, See Figure 4b |

| Receiver                                 |         |         |         |        |                  |

| Stressed sensitivity (OMA)               |         |         | -10.3   | dBm    | 1                |

| Receive sensitivity (OMA)                |         |         | -12.6   | dBm    |                  |

| Receive Power (Pave) Overload            | 0.5     |         |         | dBm    | 1                |

| Reflectance                              |         |         | -12     | dB     | 1                |

| Center Wavelength                        | 1260    |         | 1355    | nm     | 1                |

| RX_LOS (OMA) De-Assert                   |         |         | -17     | dBm    | 3                |

| RX_LOS (OMA) Assert                      | -30     |         |         | dBm    | 3                |

| RX_LOS (OMA) Hysteresis                  | 0.5     |         |         | dB     |                  |

| Vertical eye closure penalty             | 2.2     |         |         | dB     | 2                |

| Stressed eye jitter                      | 0.3     |         |         | UI p-p | 2                |

|                                          |         |         |         |        |                  |

# **General Specification Considerations (Notes):**

- 1. IEEE 802.3ae Clause 52 compliant.

- Vertical eye closure and stressed eye jitter are test conditions for stressed sensitivity (OMA) measurements

Loss of Signal (LOS) detection responds only to OMA and the indicator will respond unpredictably with the application of unmodulated optical power.

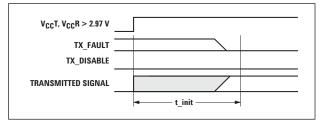

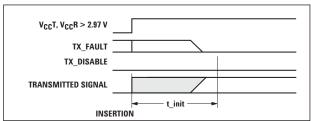

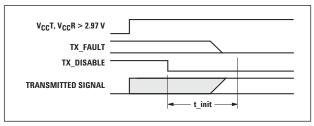

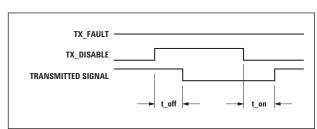

Table 9. Control Functions: Low Speed Signals Timing Characteristics

The following characteristics are defined over the Recommended Operating Conditions unless otherwise noted.

| Parameter                                       | Symbol    | Minimum | Maximum | Unit | Notes           |

|-------------------------------------------------|-----------|---------|---------|------|-----------------|

| TX_DISABLE Assert Time                          | t_off     |         | 100     | μs   | Note 1 , Fig. 5 |

| TX_DISABLE Negate Time                          | t_on      |         | 2       | ms   | Note 2 , Fig. 5 |

| Time to initialize, including reset of TX_FAULT | t_init    |         | 300     | ms   | Note 3 , Fig. 5 |

| TX_FAULT Assert Time                            | t_fault   |         | 1000    | μs   | Note 4 , Fig. 5 |

| TX_DISABLE to Reset                             | t_reset   | 10      |         | μs   | Note 5 , Fig. 5 |

| RX_LOS Assert Time                              | t_los_on  |         | 100     | μs   | Note 6 , Fig. 5 |

| RX_LOS Deassert Time                            | t_los_off |         | 100     | μs   | Note 7 , Fig. 5 |

#### Notes:

- 1. Time from rising edge of TX\_DISABLE to when the optical output falls below 10% of nominal. A 10 ms interval between assertions of TX\_DISABLE is required.

- 2. Time from falling edge of TX\_DISABLE to when the modulated optical output rises above 90% of nominal.

- 3. Time from power on or falling edge of TX\_DISABLE to when the modulated optical output rises above 90% of nominal and the Two-Wire interface is available.

- 4. From power on or negation of TX\_FAULT using TX\_DISABLE.

- 5. Time TX\_DISABLE must be held high to reset the laser fault shutdown circuitry.

- 6. Time from loss of optical signal to Rx\_LOS Assertion.

- 7. Time from valid optical signal to Rx\_LOS De-Assertion.

#### **Table 10. Control Functions: Two-Wire Interface Timing Characteristics**

The following characteristics are defined over the Recommended Operating Conditions unless otherwise noted.

| _                                                |                |         |         |      |        |

|--------------------------------------------------|----------------|---------|---------|------|--------|

| Parameter                                        | Symbol         | Minimum | Maximum | Unit | Notes  |

| TX_DISABLE Assert Time                           | t_off_twi      |         | 100     | ms   | Note 1 |

| TX_DISABLE Negate Time                           | t_on_twi       |         | 100     | ms   | Note 2 |

| TX_FAULT Assert Time                             | t_fault_twi    |         | 100     | ms   | Note 3 |

| Rx_LOS Assert Time                               | t_loss_on_twi  |         | 100     | ms   | Note 4 |

| Rx_LOS Deassert Time                             | t_loss_off_twi |         | 100     | ms   | Note 5 |

| Analog parameter data ready                      | t_data         |         | 1000    | ms   | Note 6 |

| Two-Wire Interface Ready                         | t_serial       |         | 300     | ms   | Note 7 |

| Complete Single or Sequential Write up to 4 Byte | t_write        |         | 40      | ms   | Note 8 |

| Complete Sequential Write of 5-8 Byte            | t_write        |         | 80      | ms   | Note 8 |

| Two-Wire Interface Clock Rate                    | f_serial_clock |         | 400     | kHz  | Note 8 |

| Time bus free before new transmission can start  | t_BUF          | 20      |         | μs   | Note 9 |

<sup>1.</sup> Time from two-wire interface assertion of TX\_DISABLE (A2h, byte 110, bit 6) to when the optical output falls below 10% of nominal. Measured from falling clock edge after stop bit of write transaction.

- 3. Time from fault to two-wire interface TX\_FAULT (A2h, byte 110, bit 2) asserted.

- 4. Time for two-wire interface assertion of Rx\_LOS (A2h, byte 110, bit 1) from loss of optical signal.

- 5. Time for two-wire interface de-assertion of Rx\_LOS (A2h, byte 110, bit 1) from presence of valid optical signal.

- 6. From power on to data ready bit asserted (A2h, byte 110, bit 0). Data ready indicates analog monitoring circuitry is functional.

- 7. Time from power on until module is ready for data transmission over the two-wire interface (reads or writes over A0h and A2h).

- 8. Operation of the Two Wire Serial Interface at rtes beyond 100kHz requires the use of clock stretching techniques.

- 9. Between STOP and START. See SFF 8431 Section 4.3

<sup>2.</sup> Time from two-wire interface de-assertion of TX\_DISABLE (A2h, byte 110, bit 6) to when the modulated optical output rises above 90% of nominal

Table 11. Transceiver Digital Diagnostic Monitor (Real Time Sense) Characteristics

The following characteristics are defined over the Recommended Operating Conditions unless otherwise noted.

| Parameter                                                      | Symbol           | Min.                  | Units                                                                                                                                                        | Notes                                                                                              |  |  |

|----------------------------------------------------------------|------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--|--|

| Transceiver Internal Temperature                               | T <sub>INT</sub> | T <sub>INT</sub> ±3.0 |                                                                                                                                                              | Temperature is measured internal to the transceiver Valid from = -10°C to 85°C case temperature.   |  |  |

| Transceiver Internal Supply V <sub>INT</sub> ±0.1 V<br>Voltage |                  | V                     | Supply voltage is measured internal to the transceive and can, with less accuracy, be correlated to voltage at the VccT contact. Valid over 3.3 V $\pm$ 10%. |                                                                                                    |  |  |

| Transmitter Laser DC Bias Current                              | I <sub>INT</sub> | ±10                   | %                                                                                                                                                            | $I_{\text{INT}}$ accuracy is better than $\pm 10\%$ of the nominal value.                          |  |  |

| Transmitted Average Optical<br>Output Power                    | P <sub>T</sub>   | ±3.0                  | dB                                                                                                                                                           | Average Power coupled into 9/125 μm single-mode fiber. Valid from151 μW to 1120 μW.                |  |  |

| Received Average Optical Input<br>Power                        | P <sub>R</sub>   | ±3.0                  | dB                                                                                                                                                           | Average Power coupled from 9/125 $\mu$ m single-mode fiber. Valid from 25 $\mu$ W to 1120 $\mu$ W. |  |  |

t-init: TX DISABLE NEGATED

t-init: TX DISABLE NEGATED, MODULE HOT PLUGGED

t-fault: TX FAULT OCCURED

t-fault: TX DISABLE ASSERTED THEN NEGATED, TX SIGNAL NOT RECOVERED

t-init: TX DISABLE ASSERTED

t-off & t-on: TX DISABLE ASSERTED THEN NEGATED

t-reset: TX DISABLE ASSERTED THEN NEGATED, TX SIGNAL RECOVERED

t-los-on & t-los-off

Figure 5. Transceiver timing diagrams (module installed and power applied except where noted)

Table 12. EEPROM Serial ID Memory Contents – Conventional SFP Memory (Address A0h)

| Byte #<br>Decimal | Data<br>Hex | Notes                                              | Byte #<br>Decimal | Data<br>Hex | Notes                                                |

|-------------------|-------------|----------------------------------------------------|-------------------|-------------|------------------------------------------------------|

| 0                 | 03          | SFP physical device                                | 37                | 00          | Hex Byte of Vendor OUI <sup>[1]</sup>                |

| 1                 | 04          | SFP function defined by serial ID only             | 38                | 17          | Hex Byte of Vendor OUI <sup>[1]</sup>                |

| 2                 | 07          | LC optical connector                               | 39                | 6A          | Hex Byte of Vendor OUI <sup>[1]</sup>                |

| 3                 | 20          | 10G Base-LR                                        | 40                | 41          | "A" - Vendor Part Number ASCII character             |

| 4                 | 00          |                                                    | 41                | 46          | "F" - Vendor Part Number ASCII character             |

| 5                 | 00          |                                                    | 42                | 43          | "C" - Vendor Part Number ASCII character             |

| 6                 | 00          |                                                    | 43                | 54          | "T" - Vendor Part Number ASCII character             |

| 7                 | 00          |                                                    | 44                | 2D          | "-" - Vendor Part Number ASCII character             |

| 8                 | 00          |                                                    | 45                | 37          | "7" - Vendor Part Number ASCII character             |

| 9                 | 00          |                                                    | 46                | 30          | "0" - Vendor Part Number ASCII character             |

| 10                | 00          |                                                    | 47                | 31          | "1" - Vendor Part Number ASCII character             |

| 11                | 06          | 64B/66B                                            | 48                | 53          | "S" - Vendor Part Number ASCII character             |

| 12                | 67          | 10312.5 Mbit/sec nominal bit rate (10.3125 Gbit/s) | 49                | 44          | "D" - Vendor Part Number ASCII character             |

| 13                | 00          | Unspecified                                        | 50                | 5A          | "Z" - Vendor Part Number ASCII character             |

| 14                | 0A          | 10GBASE-LR 10km                                    | 51                | 20          | " " - Vendor Part Number ASCII character             |

| 15                | 64          | 10GBASE-LR 10km                                    | 52                | 20          | " " - Vendor Part Number ASCII character             |

| 16                | 00          |                                                    | 53                | 20          | " " - Vendor Part Number ASCII character             |

| 17                | 00          |                                                    | 54                | 20          | " " - Vendor Part Number ASCII character             |

| 18                | 00          |                                                    | 55                | 20          | " " - Vendor Part Number ASCII character             |

| 19                | 00          |                                                    | 56                | 20          | " " - Vendor Part Number ASCII character             |

| 20                | 41          | "A" - Vendor Name ASCII character                  | 57                | 20          | " " - Vendor Part Number ASCII character             |

| 21                | 56          | "V" - Vendor Name ASCII character                  | 58                | 20          | " " - Vendor Part Number ASCII character             |

| 22                | 41          | "A" - Vendor Name ASCII character                  | 59                | 20          | " " - Vendor Part Number ASCII character             |

| 23                | 47          | "G" - Vendor Name ASCII character                  | 60                | 05          | Hex Byte of Laser Wavelength <sup>[2]</sup>          |

| 24                | 4F          | "0" - Vendor Name ASCII character                  | 61                | 1E          | Hex Byte of Laser Wavelength <sup>[2]</sup>          |

| 25                | 20          | " " - Vendor Name ASCII character                  | 62                | 00          |                                                      |

| 26                | 20          | " " - Vendor Name ASCII character                  | 63                |             | Checksum for Bytes 0-62 <sup>[3]</sup>               |

| 27                | 20          | " " - Vendor Name ASCII character                  | 64                | 00          | Receiver limiting output. 1 Watt power class.        |

| 28                | 20          | " " - Vendor Name ASCII character                  | 65                | 1A          | Hardware SFP TX_DISABLE, TX_FAULT, & RX_LOS          |

| 29                | 20          | " " - Vendor Name ASCII character                  | 66                | 00          |                                                      |

| 30                | 20          | " " - Vendor Name ASCII character                  | 67                | 00          |                                                      |

| 31                | 20          | " " - Vendor Name ASCII character                  | 68-83             |             | Vendor Serial Number ASCII characters <sup>[4]</sup> |

| 32                | 20          | " " - Vendor Name ASCII character                  | 84-91             |             | Vendor Date Code ASCII characters <sup>[5]</sup>     |

| 33                | 20          | " " - Vendor Name ASCII character                  | 92                | 68          | Digital Diagnostics, Internal Cal, Rx Pwr Avg        |

| 34                | 20          | " " - Vendor Name ASCII character                  | 93                | F0          | A/W, Soft SFP TX_DISABLE, TX_FAULT,<br>& RX_LOS      |

| 35                | 20          | " " - Vendor Name ASCII character                  | 94                | 03          | SFF-8472 Compliance to revision 10.2                 |

| 36                | 00          |                                                    | 95                |             | Checksum for Bytes 64-94 <sup>[3]</sup>              |

|                   |             |                                                    | 96 - 255          | 00          |                                                      |

- 1. The IEEE Organizationally Unique Identifier (OUI) assigned to Avago Technologies is 00-17-6A (3 bytes of hex).

- 2. Laser wavelength is represented in 16 unsigned bits.

- 3. Addresses 63 and 95 are checksums calculated (per SFF-8472) and stored prior to product shipment.

- 4. Addresses 68-83 specify the AFCT-701SDZ ASCII serial number and will vary on a per unit basis.

- 5. Addresses 84-91 specify the AFCT-701SDZ ASCII date code and will vary on a per date code basis.

Table 13. EEPROM Serial ID Memory Contents – Enhanced Feature Set Memory (Address A2h)

| Byte#<br>Decimal | Notes                                | Byte #<br>Decimal | Notes                                         | Byte #<br>Decimal | Notes                               |

|------------------|--------------------------------------|-------------------|-----------------------------------------------|-------------------|-------------------------------------|

| 0                | Temp H Alarm MSB <sup>[1]</sup>      | 26                | Tx Pwr L Alarm MSB <sup>[4]</sup>             | 104               | Real Time Rx Pwr MSB <sup>[5]</sup> |

| 1                | Temp H Alarm LSB <sup>[1]</sup>      | 27                | Tx Pwr L Alarm LSB <sup>[4]</sup>             | 105               | Real Time Rx Pwr LSB <sup>[5]</sup> |

| 2                | Temp L Alarm MSB <sup>[1]</sup>      | 28                | Tx Pwr H Warning MSB <sup>[4]</sup>           | 106               | Reserved                            |

| 3                | Temp L Alarm LSB <sup>[1]</sup>      | 29                | Tx Pwr H Warning LSB <sup>[4]</sup>           | 107               | Reserved                            |

| 4                | Temp H Warning MSB <sup>[1]</sup>    | 30                | Tx Pwr L Warning MSB <sup>[4]</sup>           | 108               | Reserved                            |

| 5                | Temp H Warning LSB <sup>[1]</sup>    | 31                | Tx Pwr L Warning LSB <sup>[4]</sup>           | 109               | Reserved                            |

| 6                | Temp L Warning MSB <sup>[1]</sup>    | 32                | Rx Pwr H Alarm MSB <sup>[5]</sup>             | 110               | Status/Control<br>- See Table 15    |

| 7                | Temp L Warning LSB <sup>[1]</sup>    | 33                | Rx Pwr H Alarm LSB <sup>[5]</sup>             | 111               | Reserved                            |

| 8                | Vcc H Alarm MSB <sup>[2]</sup>       | 34                | Rx Pwr L Alarm MSB <sup>[5]</sup>             | 112               | Flag Bits - See Table 16            |

| 9                | Vcc H Alarm LSB <sup>[2]</sup>       | 35                | Rx Pwr L Alarm LSB <sup>[5]</sup>             | 113               | Flag Bits - See Table 16            |

| 10               | Vcc L Alarm MSB <sup>[2]</sup>       | 36                | Rx Pwr H Warning MSB <sup>[5]</sup>           | 114               | Reserved                            |

| 11               | Vcc L Alarm LSB <sup>[2]</sup>       | 37                | Rx Pwr H Warning LSB <sup>[5]</sup>           | 115               | Reserved                            |

| 12               | Vcc H Warning MSB <sup>[2]</sup>     | 38                | Rx Pwr L Warning MSB <sup>[5]</sup>           | 116               | Flag Bits - See Table 16            |

| 13               | Vcc H Warning LSB <sup>[2]</sup>     | 39                | Rx Pwr L Warning LSB <sup>[5]</sup>           | 117               | Flag Bits - See Table 16            |

| 14               | Vcc L Warning MSB <sup>[2]</sup>     | 40-55             | Reserved                                      | 118-127           | Reserved                            |

| 15               | Vcc L Warning LSB <sup>[2]</sup>     | 56-94             | External Calibration Constants <sup>[6]</sup> | 128-247           | Customer Writeable                  |

| 16               | Tx Bias H Alarm MSB <sup>[3]</sup>   | 95                | Checksum for Bytes 0-94 <sup>[7]</sup>        | 248-255           | Vendor Specific                     |

| 17               | Tx Bias H Alarm LSB <sup>[3]</sup>   | 96                | Real Time Temperature MSB <sup>[1]</sup>      |                   |                                     |

| 18               | Tx Bias L Alarm MSB <sup>[3]</sup>   | 97                | Real Time Temperature LSB <sup>[1]</sup>      |                   |                                     |

| 19               | Tx Bias L Alarm LSB <sup>[3]</sup>   | 98                | Real Time Vcc MSB <sup>[2]</sup>              |                   |                                     |

| 20               | Tx Bias H Warning MSB <sup>[3]</sup> | 99                | Real Time Vcc LS <sup>[2]</sup>               |                   |                                     |

| 21               | Tx Bias H Warning LSB <sup>[3]</sup> | 100               | Real Time Tx Bias MSB <sup>[3]</sup>          |                   |                                     |

| 22               | Tx Bias L Warning MSB <sup>[3]</sup> | 101               | Real Time Tx Bias LSB <sup>[3]</sup>          |                   |                                     |

| 23               | Tx Bias L Warning LSB <sup>[3]</sup> | 102               | Real Time Tx Power MSB <sup>[4]</sup>         |                   |                                     |

| 24               | Tx Pwr H Alarm MSB <sup>[4]</sup>    | 103               | Real Time Tx Power LSB <sup>[4]</sup>         |                   |                                     |

| 25               | Tx Pwr H Alarm LSB <sup>[4]</sup>    |                   |                                               |                   |                                     |

- $1. \ \ Temperature \ (Temp) \ is \ decoded \ as \ a \ 16 \ bit \ signed \ twos \ compliment \ integer \ in \ increments \ of \ 1/256 ^{\circ}C.$

- 2. Supply Voltage (Vcc) is decoded as a 16 bit unsigned integer in increments of 100  $\mu$ V.

- 3. Laser bias current (Tx Bias) is decoded as a 16 bit unsigned integer in increments of 2  $\mu$ A.

- 4. Transmitted average optical power (Tx Pwr) is decoded as a 16 bit unsigned integer in increments of 0.1  $\mu$ W.

- 5. Received average optical power (Rx Pwr) is decoded as a 16 bit unsigned integer in increments of 0.1  $\mu$ W.

- 6. Bytes 56-94 are not intended for use with AFCT-701SDZ, but have been set to default values per SFF-8472.

- 7. Byte 95 is a checksum calculated (per SFF-8472) and stored prior to product shipment.

Table 14. EEPROM Serial ID Memory Contents – Soft Commands (Address A2h, Byte 110)

| Status/           |                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------|---------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Control Name      | Description                                                                                                   | Notes                                                                                                                                                                                                                                                                                                                                                                                          |

| TX_ DISABLE State | Digital state of SFP TX_ DISABLE Input (1 = TX_DISABLE asserted)                                              | Note 1                                                                                                                                                                                                                                                                                                                                                                                         |

| Soft TX_ DISABLE  | Read/write bit for changing digital state of TX_DISABLE function                                              | Note 1, 2                                                                                                                                                                                                                                                                                                                                                                                      |

| Reserved          |                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                |

| Reserved          |                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                |

| Reserved          |                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                |

| TX_FAULT State    | Digital state of the SFP TX_FAULT Output (1 = TX_FAULT asserted)                                              | Note 1                                                                                                                                                                                                                                                                                                                                                                                         |

| RX_LOS State      | Digital state of the SFP RX_LOS Output (1 = RX_LOS asserted)                                                  | Note 1                                                                                                                                                                                                                                                                                                                                                                                         |

| Data Ready (Bar)  | Indicates transceiver is powered and real time sense data is ready. (0 = Ready)                               |                                                                                                                                                                                                                                                                                                                                                                                                |

|                   | Control Name  TX_ DISABLE State  Soft TX_ DISABLE  Reserved  Reserved  Reserved  TX_FAULT State  RX_LOS State | Control Name  Description  TX_ DISABLE State  Digital state of SFP TX_ DISABLE Input (1 = TX_DISABLE asserted)  Soft TX_ DISABLE  Read/write bit for changing digital state of TX_DISABLE function  Reserved  Reserved  Reserved  TX_FAULT State  Digital state of the SFP TX_FAULT Output (1 = TX_FAULT asserted)  RX_LOS State  Digital state of the SFP RX_LOS Output (1 = RX_LOS asserted) |

- 1. The response time for soft commands of the AFCT-701SDZ is 100 msec as specified by SFF-8472.

- 2. Bit 6 is logic OR'd with the SFP TX\_DISABLE input on contact 3; either asserted will disable the SFP+ transmitter.

Table 15. EEPROM Serial ID Memory Contents – Alarms and Warnings (Address A2h, Bytes 112, 113, 116, 117)

| Byte | Bit | Flag Bit Name Description |                                                                             |

|------|-----|---------------------------|-----------------------------------------------------------------------------|

| 112  | 7   | Temp High Alarm           | Set when transceiver internal temperature exceeds high alarm threshold      |

|      | 6   | Temp Low Alarm            | Set when transceiver internal temperature exceeds low alarm threshold       |

|      | 5   | Vcc High Alarm            | Set when transceiver internal supply voltage exceeds high alarm threshold   |

|      | 4   | Vcc Low Alarm             | Set when transceiver internal supply voltage exceeds low alarm threshold    |

|      | 3   | Tx Bias High Alarm        | Set when transceiver laser bias current exceeds high alarm threshold        |

|      | 2   | Tx Bias Low Alarm         | Set when transceiver laser bias current exceeds low alarm threshold         |

|      | 1   | Tx Power High Alarm       | Set when transmitted average optical power exceeds high alarm threshold     |

|      | 0   | Tx Power Low Alarm        | Set when transmitted average optical power exceeds low alarm threshold      |

| 113  | 7   | Rx Power High Alarm       | Set when received average optical power exceeds high alarm threshold        |

|      | 6   | Rx Power Low Alarm        | Set when received average optical power exceeds low alarm threshold         |

|      | 0-5 | Reserved                  |                                                                             |

| 116  | 7   | Temp High Warning         | Set when transceiver internal temperature exceeds high warning threshold    |

|      | 6   | Temp Low Warning          | Set when transceiver internal temperature exceeds low warning threshold     |

|      | 5   | Vcc High Warning          | Set when transceiver internal supply voltage exceeds high warning threshold |

|      | 4   | Vcc Low Warning           | Set when transceiver internal supply voltage exceeds low warning threshold  |

|      | 3   | Tx Bias High Warning      | Set when transceiver laser bias current exceeds high warning threshold      |

|      | 2   | Tx Bias Low Warning       | Set when transceiver laser bias current exceeds low warning threshold       |

|      | 1   | Tx Power High Warning     | Set when transmitted average optical power exceeds high warning threshold   |

|      | 0   | Tx Power Low Warning      | Set when transmitted average optical power exceeds low warning threshold    |

| 117  | 7   | Rx Power High Warning     | Set when received average optical power exceeds high warning threshold      |

|      | 6   | Rx Power Low Warning      | Set when received average optical power exceeds low warning threshold       |

|      | 0-5 | Reserved                  |                                                                             |

|      |     |                           |                                                                             |

Figure 6. Module drawing

# **Label format**

Figure 7. Module label

AVAGO