# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### AGB2N0CS-GEVK Evaluation Board User's Manual

#### **Adapter Board Overview**

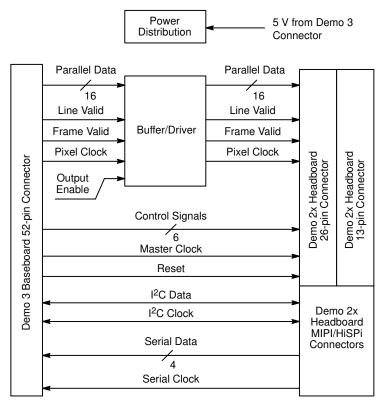

The AGB2N0CS Adapter Board helps connect Demo 2× headboards to the Demo 3 Baseboard, the AGB1N0CS–GEVK. The Demo 3 uses a high-bandwidth USB 3.0 interface and HDMI<sup>®</sup> connector to send sensor image data to the host computer. It supports single/double/quad MIPI interface, dual/quad lanes of HiSPi interface, CCP, and parallel interface. Since the Demo 2× Headboards do not use the same connector as the Demo 3, the AGB2N0CS provides communication between the headboard parallel and serial connectors to communicate with the Demo 3 Baseboard interface connection.

#### Features

- Demo 2× Headboard Connectors

- Parallel Data Buffer Option

- MIPI/HiSPi Connectors

- Demo 3 Baseboard Connector

#### **Block Diagram**

#### **ON Semiconductor®**

www.onsemi.com

#### **EVAL BOARD USER'S MANUAL**

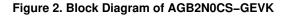

Top View

Bottom View

Figure 1. AGB2N0CS Evaluation Board

Top View

Figure 3. Top View of Adapter Board with Default Jumpers, Test Pins and Connectors

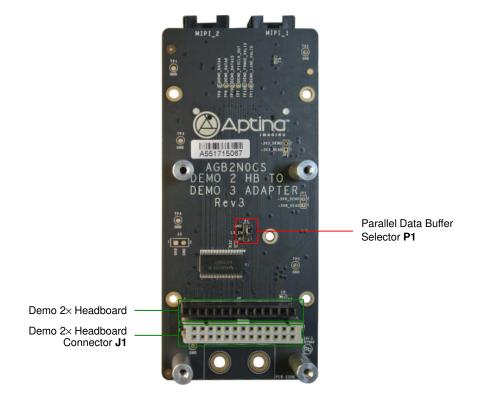

Bottom View

Figure 4. Bottom View of Adapter Board with Connectors

#### Jumper Pin Location

The jumpers on headboards start with Pin 1 on the leftmost side of the pin. Grouped jumpers increase in pin size with each jumper added.

Figure 5. Pin Locations for a Single Jumper. Pin 1 is Located at the Leftmost Side

#### Jumper/Header Functions & Default Positions

The P1 jumper/header configuration allows configuration of parallel data. Its default position shorts pins 2-3, which enables the parallel data buffer to pass parallel data signals. When pins 1-2 are shorted, the parallel data buffer is disabled.

#### AGB2N0CS-GEVK Connectors

The evaluation board supports has various different connectors on-board, including a Demo 3 connector, two MIPI/HiSPi connectors for the Demo  $2\times$  headboard, the 14-pin Demo  $2\times$  headboard connector, and 26-pin Demo  $2\times$  headboard connector.

#### Headboard Connectors

The Demo 2× headboard connectors are described in the pinouts in Tables 1 and 2. The headboard connector has a 14-pin and 26-pin connector, as well as two MIPI/HiSPi connectors.

#### Baseboard Connector

The Demo 3 Baseboard connector is shown in the pinout in Table 3. The Demo 3 connector has a serial sensor data input, I<sup>2</sup>C control interface, headboard power, and parallel image data interface.

#### Table 1. 26-PIN DEMO 2X HEADBOARD CONNECTOR FUNCTION DESCRIPTION (J1)

| Pin | Name          | Description                      | DIR | Comment                       |

|-----|---------------|----------------------------------|-----|-------------------------------|

| 1   | S_DATA8       | Parallel Data8                   | I/O | Parallel Data Bit             |

| 2   | S_DATA9       | Parallel Data9                   | I/O | Parallel Data Bit             |

| 3   | S_DATA10      | Parallel Data10                  | I/O | Parallel Data Bit             |

| 4   | S_DATA11      | Parallel Data11                  | I/O | Parallel Data Bit             |

| 5   | S_DATA12      | Parallel Data12                  | I/O | Parallel Data Bit             |

| 6   | S_DATA13      | Parallel Data13                  | I/O | Parallel Data Bit             |

| 7   | S_DATA14      | Parallel Data14                  | I/O | Parallel Data Bit             |

| 8   | S_DATA15      | Parallel Data15                  | I/O | Parallel Data Bit             |

| 9   | S_DATA6       | Parallel Data6                   | I/O | Parallel Data Bit             |

| 10  | S_DATA7       | Parallel Data7                   | I/O | Parallel Data Bit             |

| 11  | GND           | Ground                           | PWR |                               |

| 12  | GND           | Ground                           | PWR |                               |

| 13  | S_LINE_VALID  | Parallel Line Valid              | Out | Check Line Valid Signal       |

| 14  | S_SP5         | General Control Signal 5         | Out | Signal @ +3.3 V Level         |

| 15  | NOT USED      | Not Used                         | NA  |                               |

| 16  | HEAD_RESET_L  | Reset Signal to Sensor           | In  | Reset to Headboard Sensor     |

| 17  | S_FRAME_VALID | Parallel Frame Valid             | Out | Check Frame Valid Signal      |

| 18  | HEAD_SDA      | I <sup>2</sup> C Data to Sensor  | I/O | Signal @ +3.3 V Level         |

| 19  | HEAD_SCL      | I <sup>2</sup> C Clock to Sensor | I/O | Signal @ +3.3 V Level         |

| 20  | NOT USED      | Not Used                         | NA  |                               |

| 21  | +5V0_HEAD     | +5V0 Power Input                 | PWR | For Powering Up the Headboard |

| 22  | +5V0_HEAD     | +5V0 Power Input                 | PWR | For Powering Up the Headboard |

| 23  | S_PIXCLK      | Parallel Pixel Clock             | In  | Parallel Data Pixel Clock     |

| 24  | GND           | Ground                           | PWR |                               |

#### Table 1. 26-PIN DEMO 2X HEADBOARD CONNECTOR FUNCTION DESCRIPTION (J1) (continued)

| Pin | Name | Description  | DIR | Comment                        |

|-----|------|--------------|-----|--------------------------------|

| 25  | GND  | Ground       | PWR |                                |

| 26  | MCLK | Master Clock | In  | Master Clock from Demo 3 Board |

| Pin | Name      | Description              | DIR | Comment                       |

|-----|-----------|--------------------------|-----|-------------------------------|

| 1   | GND       | Ground                   | PWR |                               |

| 2   | S_DATA4   | Parallel Data4           | I/O | Parallel Data Bit             |

| 3   | S_DATA5   | Parallel Data5           | I/O | Parallel Data Bit             |

| 4   | S_DATA2   | Parallel Data2           | I/O | Parallel Data Bit             |

| 5   | S_DATA3   | Parallel Data3           | I/O | Parallel Data Bit             |

| 6   | S_DATA0   | Parallel Data0           | I/O | Parallel Data Bit             |

| 7   | S_DATA1   | Parallel Data1           | I/O | Parallel Data Bit             |

| 8   | S_SP0     | General Control Signal 0 | Out | Signal @ +3.3 V Level         |

| 9   | S_SP1     | General Control Signal 1 | Out | Signal @ +3.3 V Level         |

| 10  | S_SP2     | General Control Signal 2 | Out | Signal @ +3.3 V Level         |

| 11  | S_SP3     | General Control Signal 3 | Out | Signal @ +3.3 V Level         |

| 12  | S_SP4     | General Control Signal 4 | Out | Signal @ +3.3 V Level         |

| 13  | +3V3_HEAD | +3.3 V to Headboard      | PWR | For Powering Up the Headboard |

| 14  | GND       | Ground                   | PWR |                               |

#### Table 2. 14-PIN DEMO 2X HEADBOARD CONNECTOR FUNCTION DESCRIPTION (J2)

#### Shorted Jumper for Power Measurement

Different supplies to the headboard are provided by trace shorted jumper, for any voltage and power measurements. To conduct current for current measurement on a given power rail, cut the trace between the two pins of their respective JP, and insert an ammeter prior to powering up the system. The figure below shows where the trace to cut is located.

#### Table 3. SHORTED JUMPERS FOR POWER MEASUREMENT

| Jumper          | Voltage (V) |

|-----------------|-------------|

| JP1 (+5V0 HEAD) | 5.0         |

| JP2 (+3V3 HEAD) | 3.3         |

# Figure 6. Top and Bottom View of Shorted Jumper. The Bottom View Shows the Trace Location to Cut for Current Measurement

#### HDMI is a registered trademark of HDMI Licensing, LLC.

ON Semiconductor and the 💷 are registered trademarks of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries. SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdt/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC for any such unintended or unauthorized application, barrness against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC products for any such unintended or copyright taws and is not for reas

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81–3–5817–1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative