Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Lowest Power, Proven Security, and Exceptional Reliability

Flash FPGAs

Flash SoC FPGAs

Military FPGAs

Automotive FPGAs

Ecosystem

Design Hardware

Intellectual Property

**Technology Solutions**

Delivering More Resources in Low-Density Devices with the Lowest Power, Proven Security, and Exceptional Reliability

# Microsemi FPGAs and SoC FPGAs

Whether you're designing at the board or system level, Microsemi's SoC FPGAs and low-power FPGAs are your best choice. The unique, flash-based technology of Microsemi FPGAs and their history of reliability sets them apart from traditional FPGAs.

Design with Microsemi's FPGAs and SoC FPGAs for today's rapidly-growing markets of consumer and portable medical devices, or tomorrow's environmentally friendly data centers, industrial controls, and military and commercial aircraft. Only Microsemi can meet the power, size, cost, and reliability targets that reduce time-to-market and enable long-term profitability.

# **Product Highlights**

| SmartFusion®2 SoC FPGA                                            | <ul> <li>166 MHz ARM® Cortex®-M3 processor</li> <li>5K to 150K logic elements</li> <li>PCle Gen2 hard IP and complete microcontroller subsystem</li> </ul>                                                                                                                   | 4  |

|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| IGLOO®2 FPGA                                                      | <ul><li>The most feature-rich low-density FPGA</li><li>5K to 150K logic elements</li><li>High-performance memory subsystem</li></ul>                                                                                                                                         | 5  |

| IGLOO FPGA Family<br>IGLOO/e<br>IGLOO nano<br>IGLOO PLUS          | <ul> <li>100 to 35K logic elements</li> <li>Ideal for CPLD replacement</li> <li>Smallest package options</li> <li>High I/O-to-logic ratio</li> </ul>                                                                                                                         | 6  |

| ProASIC®3 FPGA Family<br>ProASIC3/E<br>ProASIC3 nano<br>ProASIC3L | <ul><li>100 to 35K logic elements</li><li>Ideal for CPLD replacement</li><li>Smallest package options</li></ul>                                                                                                                                                              | 9  |

| SmartFusion SoC FPGA                                              | <ul><li>100 MHz ARM Cortex-M3 processor</li><li>Up to 6K logic elements, analog processing</li></ul>                                                                                                                                                                         | 12 |

| Military SmartFusion2, IGLOO2                                     | <ul> <li>Military FPGA with up to 150K logic elements</li> <li>Best-in-class security</li> <li>Industry's most reliable FPGAs</li> </ul>                                                                                                                                     | 13 |

| Military SmartFusion, Fusion®, and ProASIC3/EL                    | <ul> <li>Mixed signal integration down to -55 °C</li> <li>Reprogrammable digital logic, configurable analog, embedded flash memory</li> <li>Low power consumption across the full military temperature range</li> <li>High-density fine-pitch ball grid packaging</li> </ul> | 14 |

| Automotive-Grade Products                                         | <ul><li>AEC-Q 100 T1 and T2 devices</li><li>1K to 90K logic elements</li></ul>                                                                                                                                                                                               | 15 |

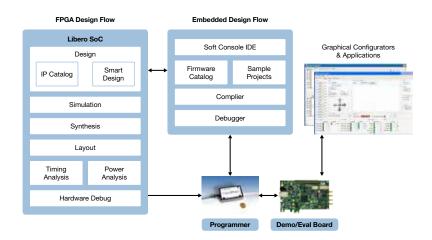

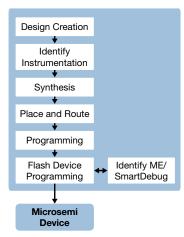

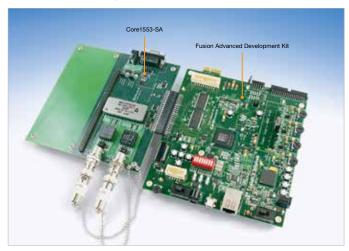

| Ecosystem                                                         | Design software and hardware tools for Microsemi<br>FPGAs and SoC FPGAs                                                                                                                                                                                                      | 18 |

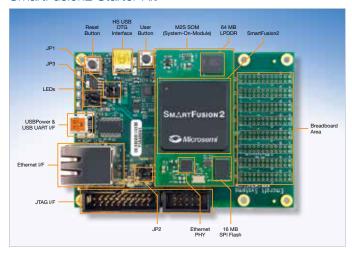

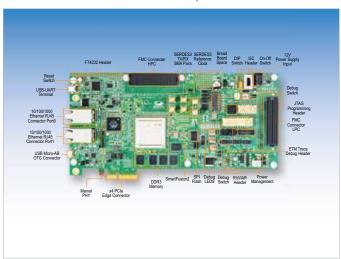

| Development Kits                                                  | Starter, evaluation, and development kits                                                                                                                                                                                                                                    | 20 |

| Intellectual Property Cores                                       | Microsemi intellectual property designed and optimized<br>for use with Microsemi FPGAs                                                                                                                                                                                       | 26 |

For the latest device information, valid ordering codes, and details regarding previous-generations of flash FPGAs, visit www.microsemi.com/fpga-soc or consult the corresponding product datasheets.

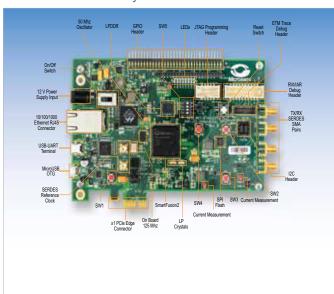

# SmartFusion2 SoC FPGAs

# More Resources in Low-Density Devices with ARM Cortex-M3 Processor

SmartFusion2 SoC FPGAs deliver more resources in low-density devices with the lowest power, proven security, and exceptional reliability. These devices are ideal for general purpose functions such as Gigabit Ethernet or dual-PCI Express control planes, bridging functions, input/output (I/O) expansion and conversion, video/image processing, system management, and secure connectivity. Microsemi SoC FPGAs are used by customers in Communications, Industrial, Medical, Defense, and Aviation markets.

- Embedded ARM Cortex-M3 microcontroller subsystem (MSS)

- PCIe Gen2 endpoints starting at 10K logic elements

- Embedded DDR3 memory controllers

- · Small packages

- 1 mW in Flash\*Freeze mode

- Instant-on

- Zero FIT FPGA configuration cells

- SECDED memory protection

- NRBG, AES-256, SHA-256, ECC cryptographic engine

- User physically unclonable function (PUF)

- CRI DPA pass-through license

## SmartFusion2 Devices

| SmartFusion2 Devices | Features                                      | M2S005 | M2S010     | M2S025     | M2S050 | M2S060 | M2S090        | M2S150       |

|----------------------|-----------------------------------------------|--------|------------|------------|--------|--------|---------------|--------------|

|                      | Maximum logic elements (4LUT + DFF)           | 6,060  | 12,084     | 27,696     | 56,340 | 56,520 | 86,184        | 146,124      |

|                      | Mathblocks (18 × 18)                          | 11     | 22         | 34         | 72     | 72     | 84            | 240          |

| Logic/DSP            | Fabric interface controllers (FICs)           |        | 1          |            | 2      |        | 1             | 2            |

|                      | PLLs and CCCs                                 |        | 2          |            | (      | 3      |               | 8            |

|                      | Security                                      |        | AES256, SH | HA256, RNG |        | AES256 | 6, SHA256, RN | IG, ECC, PUF |

|                      | Cortex-M3 + instruction cache                 |        |            |            | Yes    |        |               |              |

|                      | eNVM (KB)                                     | 128    |            | 256 512    |        |        |               |              |

| MSS                  | eSRAM (KB)                                    |        |            |            | 64     |        |               |              |

| M99                  | eSRAM (KB) non-SECDED                         |        |            |            | 80     |        |               |              |

|                      | CAN, 10/100/1000 Ethernet, HS USB             |        |            |            |        |        |               |              |

|                      | Multi-mode UART, SPI, I <sup>2</sup> C, timer |        |            |            | 2 each |        |               |              |

|                      | LSRAM 18K blocks                              | 10     | 21         | 31         | 6      | 9      | 109           | 236          |

| Fabric memory        | uSRAM 1K blocks                               | 11     | 22         | 34         | 7      | 2      | 112           | 240          |

|                      | Total RAM (kbits)                             | 191    | 400        | 592        | 1,3    | 314    | 2,074         | 4,488        |

|                      | DDR controllers (count × width)               |        | 1 × 18     |            | 2 × 36 | 1 ×    | : 18          | 2 x 36       |

| High-speed           | SERDES lanes                                  | 0      | 4          | 4          | 8      | 4      | 4             | 16           |

|                      | PCIe endpoints                                | 0      |            | 1          |        | 2      |               | 4            |

|                      | MSIO (3.3 V)                                  | 115    | 123        | 157        | 139    | 271    | 309           | 292          |

|                      | MSIOD (2.5 V)                                 | 28     | 4          | .0         | 62     | 4      | 10            | 106          |

| User I/O             | DDRIO (2.5 V)                                 | 66     | 7          | 0          | 176    | 7      | '6            | 176          |

|                      | Total user I/Os                               | 209    | 233        | 267        | 377    | 387    | 425           | 574          |

# I/Os per Package

|                     |     |        |     |       |     |        |     |       |     | Pacl   | kage ( | Options |     |       |     |       |     |        |     |           |

|---------------------|-----|--------|-----|-------|-----|--------|-----|-------|-----|--------|--------|---------|-----|-------|-----|-------|-----|--------|-----|-----------|

| Package type        | FCS | (G)325 | VF( | G)256 | FCS | (G)536 | VF( | G)400 | FCV | (G)484 | TQ(    | G)144   | FG( | G)484 | FG( | G)676 | FG  | (G)896 | ı   | FC(G)1152 |

| Pitch (mm)          | (   | 0.5    | (   | D.8   |     | 0.5    |     | 0     | .8  |        |        | 0.5     |     | 1.0   |     | 1.0   |     | 1.0    |     | 1.0       |

| Length × width (mm) | 11  | × 11   | 14  | × 14  | 16  | × 16   | 17  | × 17  | 19  | × 19   | 20     | × 20    | 23  | × 23  | 27  | × 27  | 31  | × 31   |     | 35 × 35   |

| Device              | I/O | Lanes  | I/O | Lanes | I/O | Lanes  | I/O | Lanes | I/O | Lanes  | I/O    | Lanes   | I/O | Lanes | 1/0 | Lanes | I/O | Lanes  | I/O | Lanes     |

| M2S005 (S)          |     |        | 161 |       |     |        | 171 |       |     |        | 84     |         | 209 |       |     |       |     |        |     |           |

| M2S010 (S/T/TS)     |     |        | 138 | 2     |     |        | 195 | 4     |     |        | 84     |         | 233 | 4     |     |       |     |        |     |           |

| M2S025 (T/TS)       | 180 | 2      | 138 | 2     |     |        | 207 | 4     |     |        |        |         | 267 | 4     |     |       |     |        |     |           |

| M2S050 (T/TS)       | 200 | 2      |     |       |     |        | 207 | 4     |     |        |        |         | 267 | 4     |     |       | 377 | 8      |     |           |

| M2S060 (T/TS)       | 200 | 2      |     |       |     |        | 207 | 4     |     |        |        |         | 267 | 4     | 387 | 4     |     |        |     |           |

| M2S090 (T/TS)       | 180 | 4      |     |       |     |        |     |       |     |        |        |         | 267 | 4     | 425 | 4     |     |        |     |           |

| M2S150 (T/TS)       |     |        |     |       | 293 | 4      |     |       | 248 | 4      |        |         |     |       |     |       |     |        | 574 | 16        |

Notes:

1. M2S090 FCSG325 package dimension are 11 × 13.5.

2. Highlighted devices can migrate vertically in the same package.

3. (G) indicates that the package is RoHS 6/6 compliant/Pb-free.

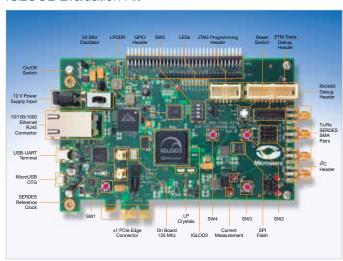

# IGLOO2 FPGAs

# More Resources in Low-Density Devices with High-Performance Memory Subsystem

IGLOO2 FPGAs deliver more resources in low-density devices with the lowest power, proven security, and exceptional reliability. These devices are ideal for general purpose functions such as Gigabit Ethernet or dual-PCI Express control planes, bridging functions, input/output (I/O) expansion and conversion, video/image processing, system management, and secure connectivity. Microsemi FPGAs are used by customers in Communications, Industrial, Medical, Defense, and Aviation markets.

- High-performance memory subsystem

- PCle Gen2 endpoints starting at 10K logic elements

- Embedded DDR3 memory controllers

- SECDED memory protection

- 1 mW in Flash\*Freeze mode

- Instant-on

- Zero FIT FPGA configuration cells

- CRI DPA pass-through license

- Small packages

- NRBG, AES-256, SHA-256, ECC cryptographic engine

- User physically unclonable function (PUF)

## IGLOO<sub>2</sub> Devices

| IGLOO2 Devices | Features                                     | M2GL005 | M2GL010    | M2GL025    | M2GL050 | M2GL060 | M2GL090      | M2GL150      |

|----------------|----------------------------------------------|---------|------------|------------|---------|---------|--------------|--------------|

|                | Maximum logic elements (4LUT + DFF)          | 6,060   | 12,084     | 27,696     | 56,340  | 56,520  | 86,184       | 146,124      |

|                | Mathblocks (18 × 18)                         | 11      | 22         | 34         | 72      | 72      | 84           | 240          |

|                | PLLs and CCCs                                | 2       | 2          |            |         | 6       |              | 8            |

| Logic/DSP      | SPI/HPDMA/PDMA                               |         |            |            | 1 eac   | n       |              |              |

|                | Fabric interface controllers (FICs)          |         | 1          |            | 2       | -       | I            | 2            |

|                | Data security                                |         | AES256, SH | IA256, RNG |         | AES256  | 6, SHA256, R | NG, ECC, PUF |

|                | eNVM (KB)                                    | 128     |            | 2          | 56      |         |              | 512          |

|                | LSRAM 18K blocks                             | 10      | 21         | 31         | (       | 69      | 109          | 236          |

| Memory         | uSRAM 1K blocks                              | 11      | 21         | 34         | 7       | 72      | 112          | 240          |

|                | eSRAM (KB)                                   |         |            |            | 64      |         |              |              |

|                | Total RAM (kbits)                            | 703     | 912        | 1104       | 18      | 326     | 2586         | 5000         |

|                | DDR controllers (count × width)              |         | 1 × 18     |            | 2 × 36  | 1 ×     | 18           | 2 × 36       |

| High-speed     | SERDES lanes                                 | 0       |            | 4          | 8       | 4       | 1            | 16           |

|                | PCIe endpoints                               | 0       |            | 1          |         | 2       |              | 4            |

|                | MSIO (3.3 V)                                 | 115     | 123        | 157        | 139     | 271     | 309          | 292          |

|                | MSIOD (2.5 V)                                | 28      | 4          | 10         | 62      | 4       | 0            | 106          |

| User I/O       | DDRIO (2.5 V)                                | 66      | 7          | 70         | 176     | 7       | 6            | 176          |

|                | Total user I/Os                              |         | 233        | 267        | 377     | 387     | 425          | 574          |

| Grades         | Commercial (C), Industrial (I), Military (M) | C, I    |            |            |         | C, I, M |              |              |

Notes:

## I/Os per Package

|                     |     |        |     |       |     |        |     |       |     | Pac    | kage | Options |     |       |     |        |     |        |     |          |

|---------------------|-----|--------|-----|-------|-----|--------|-----|-------|-----|--------|------|---------|-----|-------|-----|--------|-----|--------|-----|----------|

| Package type        | FCS | (G)325 | VF( | G)256 | FCS | (G)536 | VF( | G)400 | FCV | (G)484 | TQ   | (G)144  | FG( | G)484 | FG  | (G)676 | FG  | (G)896 | F   | C(G)1152 |

| Pitch (mm)          | (   | 0.5    | (   | 0.8   | (   | 0.5    |     | 0     | .8  |        |      | 0.5     |     | 1.0   |     | 1.0    |     | 1.0    |     | 1.0      |

| Length × width (mm) | 11  | 1x11   | 14  | 1x14  | 16  | 6x16   | 17  | 7x17  | 19  | 9x19   | 2    | 0x20    | 23  | 3x23  | 2   | 7x27   | 3   | 1x31   |     | 35x35    |

| Device              | I/O | Lanes  | I/O | Lanes | I/O | Lanes  | I/O | Lanes | I/O | Lanes  | I/O  | Lanes   | I/O | Lanes | I/O | Lanes  | I/O | Lanes  | I/O | Lanes    |

| M2GL005 (S)         |     |        | 161 |       |     |        | 171 |       |     |        | 84   |         | 209 |       |     |        |     |        |     |          |

| M2GL010 (S/T/TS)    |     |        | 138 | 2     |     |        | 195 | 4     |     |        | 84   |         | 233 | 4     |     |        |     |        |     |          |

| M2GL025 (T/TS)      | 180 | 2      | 138 | 2     |     |        | 207 | 4     |     |        |      |         | 267 | 4     |     |        |     |        |     |          |

| M2GL050 (T/TS)      | 200 | 2      |     |       |     |        | 207 | 4     |     |        |      |         | 267 | 4     |     |        | 377 | 8      |     |          |

| M2GL060 (T/TS)      | 200 | 2      |     |       |     |        | 207 | 4     |     |        |      |         | 267 | 4     | 387 | 4      |     |        |     |          |

| M2GL090 (T/TS)      | 180 | 4      |     |       |     |        |     |       |     |        |      |         | 267 | 4     | 425 | 4      |     |        |     |          |

| M2GL150 (T/TS)      |     |        |     |       | 293 | 4      |     |       | 248 | 4      |      |         |     |       |     |        |     |        | 574 | 16       |

<sup>1.</sup> Total logic may vary based on utilization of DSP and memories in your design. Please see the IGLOO2 and SmartFusion2 Fabric User Guide for details. 2. Feature availability is package dependent.

M2GL090 FCS325 package dimension are 11 x 13.5.

<sup>2.</sup> Highlighted devices can migrate vertically in the same package.

<sup>3. (</sup>G) indicates that the package is RoHS 6/6 compliant/Pb-free

# IGLOO Family: IGLOO/e FPGAs

# The Ideal Low-Power, Programmable Solution for CPLD Replacement

• Instant-on

The IGLOO family of reprogrammable and full-featured flash FPGAs is designed to meet the low-power and area requirements of today's portable electronics. Based on nonvolatile flash technology, the 1.2 V to 1.5 V operating voltage family offers the industry's lowest power consumption—as low as 5 µW. The IGLOO family supports up to 35K logic elements with up to 504 kbits of true dualport SRAM, up to six embedded PLLs, and up to 620 user I/Os. Low-power applications that require 32-bit processing can use the ARM Cortex-M1 processor without license fees or royalties in M1 IGLOO devices. Developed specifically for implementation in FPGAs, Cortex-M1 devices offer an optimal balance between performance and size to minimize power consumption.

- Low-power FPGAs

- 1.2 V core and I/O voltage

- AES-protected in-system programming (ISP)

- User nonvolatile FlashROM

- Flash\*Freeze technology for low power consumption

## IGLOO/e Devices

| IGLOO devices                 |                                 | AGL030 | AGL060 | AGL125  | AGL250   | AGL400  | AGL600   | AGL1000   | AGLE600 | AGLE3000   |

|-------------------------------|---------------------------------|--------|--------|---------|----------|---------|----------|-----------|---------|------------|

| ARM-Enabled<br>IGLOO¹ devices | Features                        |        |        |         | M1AGL250 |         | M1AGL600 | M1AGL1000 |         | M1AGLE3000 |

|                               | Logic elements (approximate)    | 330    | 700    | 1,500   | 3,000    | 5,000   | 7,000    | 11,000    | 7,000   | 35,000     |

|                               | System gates                    | 30,000 | 60,000 | 125,000 | 250,000  | 400,000 | 600,000  | 1,000,000 | 600,000 | 3,000,000  |

| Logic                         | VersaNet globals <sup>3</sup>   | 6      | 18     | 18      | 18       | 18      | 18       | 18        | 18      | 18         |

| Logic                         | Flash*Freeze mode (typical, µW) | 5      | 10     | 16      | 24       | 32      | 36       | 53        | 49      | 137        |

|                               | AES-protected ISP1              |        | Yes    | Yes     | Yes      | Yes     | Yes      | Yes       | Yes     | Yes        |

|                               | Integrated PLLs with CCC2       |        | 1      | 1       | 1        | 1       | 1        | 1         | 6       | 6          |

|                               | RAM (1,024 bits)                |        | 18     | 36      | 36       | 54      | 108      | 144       | 108     | 504        |

| Fabric memory                 | RAM blocks (4,608 bits)         |        | 4      | 8       | 8        | 12      | 24       | 32        | 24      | 112        |

|                               | FlashROM kbits (1,024 bits)     | 1      | 1      | 1       | 1        | 1       | 1        | 1         | 1       | 1          |

| User I/O                      | I/O banks                       | 2      | 2      | 2       | 4        | 4       | 4        | 4         | 8       | 8          |

| User I/U                      | Maximum user I/Os               | 81     | 96     | 133     | 143      | 194     | 235      | 300       | 270     | 620        |

1. AES is not available for Cortex-M1 IGLOO devices.

2. AGL060 in CS121 does not support the PLL.

3. Six chip (main) and twelve quadrant global networks are available for AGL060 devices and above.

# I/Os per Package

|            | I/O Package                 | QNG48 | QNG68 | UCG81 | CSG81 | CS(G)121 | VQ(G)100 | CS(G)196 | FG(G)144 | FG(G)256 <sup>3</sup> | CS(G)281 | FG(G)484 <sup>3</sup> | FG(G)896 |

|------------|-----------------------------|-------|-------|-------|-------|----------|----------|----------|----------|-----------------------|----------|-----------------------|----------|

| IGLOO/e    | Pitch (mm)                  | 0.4   | 0.4   | 0.4   | 0.5   | 0.5      | 0.5      | 0.5      | 1.0      | 1.0                   | 0.5      | 1.0                   | 1.0      |

| Devices    | Length × Width (mm)         | 6 × 6 | 8 × 8 | 4 × 4 | 5 × 5 | 6 × 6    | 16 × 16  | 8 × 8    | 13 × 13  | 17 × 17               | 10 × 10  | 23 × 23               | 31 × 31  |

| AGL030     | Single-end I/O              | 34    | 49    | 66    | 66    |          | 77       |          |          |                       |          |                       |          |

| AGL060     | Single-end I/O              |       |       |       |       | 96       | 71       |          |          |                       |          |                       |          |

| AGL125     | Single-end I/O              |       |       |       |       | 96       | 71       | 133      | 97       |                       |          |                       |          |

| AGL250/    | Single-end I/O <sup>2</sup> |       |       |       |       |          | 68       | 143¹     | 97       |                       |          |                       |          |

| M1AGL250   | Differential I/O            |       |       |       |       |          | 13       | 35¹      | 24       |                       |          |                       |          |

|            | Single-end I/O <sup>2</sup> |       |       |       |       |          |          | 143      | 97       | 178                   |          | 194                   |          |

| AGL400     | Differential I/O            |       |       |       |       |          |          | 35       | 25       | 38                    |          | 38                    |          |

| AGL600/    | Single-end I/O <sup>2</sup> |       |       |       |       |          |          |          | 97       | 177                   | 215      | 235                   |          |

| M1AGL600   | Differential I/O            |       |       |       |       |          |          |          | 25       | 43                    | 53       | 60                    |          |

| AGL1000/   | Single-end I/O <sup>2</sup> |       |       |       |       |          |          |          | 97       | 177                   | 215      | 300                   |          |

| M1AGL1000  | Differential I/O            |       |       |       |       |          |          |          | 25       | 44                    | 53       | 74                    |          |

| AGLE600    | Single-end I/O <sup>2</sup> |       |       |       |       |          |          |          |          | 165                   |          | 270                   |          |

| AGEEOOO    | Differential I/O            |       |       |       |       |          |          |          |          | 79                    |          | 135                   |          |

| AGLE3000/  | Single-end I/O <sup>2</sup> |       |       |       |       |          |          |          |          |                       |          | 341                   | 620      |

| M1AGLE3000 | Differential I/O            |       |       |       |       |          |          |          |          |                       |          | 168                   | 310      |

1. The M1AGL250 device does not support CS196 package.

3. FG256 and FG484 are footprint-compatible packages.

<sup>2.</sup> Each used differential pair reduces the number of single-end I/Os available by two

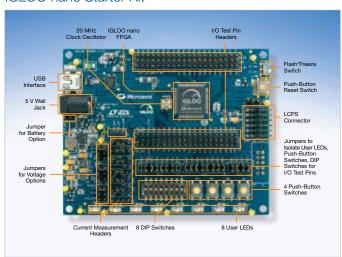

# IGLOO Family: IGLOO nano FPGAs

# The Industry's Lowest-Power, Smallest-Size Solution

IGLOO nano products offer groundbreaking possibilities in power, size, lead-times, operating temperature, and cost. Available in logic densities from 100–3K logic elements, the 1.2 V to 1.5 V IGLOO nano devices have been designed for high-volume applications where power and size are the key decision criteria. IGLOO nano devices are perfect ASIC or ASSP replacements, yet retain the historical FPGA advantages of flexibility and quick time-to-market in low-power and small footprint profiles.

- Ultra low power in Flash\*Freeze mode, as low as 2 μW

- Small footprint packages from 14 mm × 14 mm to 3 mm × 3 mm

- Enhanced commercial temperature

- 1.2 V to 1.5 V single voltage operation

- Enhanced I/O features

- Embedded SRAM and non-volatile memory (NVM)

- ISP and security

- Instant-on

## IGLOO nano Devices

| IGLOO nano Devices | Features                            | AGLN010 | AGLN020 | AGLN060 | AGLN125 | AGLN250 |

|--------------------|-------------------------------------|---------|---------|---------|---------|---------|

|                    | Logic elements (approximate)        | 100     | 200     | 700     | 1,500   | 3,000   |

|                    | System gates                        | 10,000  | 20,000  | 60,000  | 125,000 | 250,000 |

| Logio              | VersaNet globals                    | 4       | 4       | 18      | 18      | 18      |

| Logic              | Flash*Freeze mode (typical, μW)     | 2       | 4       | 10      | 16      | 24      |

|                    | AES-protected ISP                   |         |         | Yes     | Yes     | Yes     |

|                    | Integrated PLL in CCCs1             |         |         | 1       | 1       | 1       |

|                    | RAM kbits (1,024 bits)              |         |         | 18      | 36      | 36      |

| Fabric memory      | 4,608-bit blocks                    |         |         | 4       | 8       | 8       |

|                    | FlashROM kbits (1,024 bits)         | 1       | 1       | 1       | 1       | 1       |

| User I/O           | I/O banks                           | 2       | 3       | 2       | 2       | 4       |

| Oser 1/O           | Maximum user I/Os (packaged device) | 34      | 52      | 71      | 71      | 68      |

### Notes:

# I/Os per Package

| I/O Packages        | UCG36 | QNG48 | QNG68 | UCG81 | CSG81 | VQ(G)100 <sup>2</sup> |

|---------------------|-------|-------|-------|-------|-------|-----------------------|

| Pitch (mm)          | 0.4   | 0.4   | 0.4   | 0.4   | 0.5   | 0.5                   |

| Length × width (mm) | 3 × 3 | 6 × 6 | 8 × 8 | 4 × 4 | 5 × 5 | 16 × 16               |

| AGLN010             | 23    | 34    |       |       |       |                       |

| AGLN020             |       |       | 49    | 52    | 52    |                       |

| AGLN060             |       |       |       |       | 60    | 71                    |

| AGLN125             |       |       |       |       | 60    | 71                    |

| AGLN250             |       |       |       |       | 60    | 68                    |

<sup>1.</sup> AGLN060, AGLN125 and AGLN250 in the CS(G)81 package do not support PLLs.

IGLOO nano devices do not support differential I/Os.

<sup>2. (</sup>G) indicates that the package is RoHS 6/6 compliant/Pb-free.

# IGLOO Family: IGLOO PLUS FPGAs

# The Low-Power FPGA with Enhanced I/O Capabilities

IGLOO PLUS products deliver low power and enhanced I/Os in a feature-rich programmable device, offering more I/Os per logic element than the IGLOO devices, and supporting independent Schmitt trigger inputs, hot-swapping, and Flash\*Freeze bus hold. Ranging from 330–1.5K logic elements, the 1.2V to 1.5V IGLOO PLUS devices have been optimized to meet the needs of I/O-intensive, power-conscious applications that require exceptional features.

- I/O-optimized FPGA

- Low power in Flash\*Freeze mode, as low as 5 μW

- Small footprint and low-cost packages

- Reprogrammable flash technology

- 1.2 V to 1.5 V single voltage operation

- Embedded SRAM NVM

- AES-protected ISP

- Instant-on

# IGLOO PLUS Devices

| IGLOO PLUS Devices | Features                            | AGLP030 | AGLP060 | AGLP125 |

|--------------------|-------------------------------------|---------|---------|---------|

|                    | Logic elements (approximate)        | 330     | 7,000   | 1,500   |

|                    | System gates                        | 30,000  | 60,000  | 125,000 |

| Lorio              | VersaNet globals                    | 6       | 18      | 18      |

| Logic              | Flash*Freeze mode (typical, μW)     | 5       | 10      | 16      |

|                    | AES-protected ISP                   |         | Yes     | Yes     |

|                    | Integrated PLL in CCCs1             |         | 1       | 1       |

|                    | RAM (1,024 bits)                    |         | 18      | 36      |

| Fabric memory      | 4,608-bit blocks                    |         | 4       | 8       |

|                    | FlashROM kbits (1,024 bits)         | 1       | 1       | 1       |

| User I/O           | I/O banks                           | 4       | 4       | 4       |

| User I/O           | Maximum user I/Os (packaged device) | 120     | 157     | 212     |

### Notes:

## I/Os per Package

|                    | I/O Package         | CS(G)201 | CS(G)281 | CS(G)289 | VQ(G)176 |

|--------------------|---------------------|----------|----------|----------|----------|

| IGLOO PLUS Devices | Pitch (mm)          | 0.5      | 0.5      | 0.8      | 0.4      |

|                    | Length × width (mm) | 8 × 8    | 10 × 10  | 14 × 14  | 22 × 22  |

| AGLP030            | Single-end I/O      | 120      |          | 120      |          |

| AGLP060            | Single-end I/O      | 157      |          | 157      | 137      |

| AGLP125            | Single-end I/O      |          | 212      | 212      |          |

<sup>1.</sup> AGLP060 in CS(G)201 does not support the PLL.

<sup>1.</sup> IGLOO Plus devices do not support differential I/Os.

<sup>2. (</sup>G) indicates that the package is RoHS 6/6 compliant/Pb-free.

# ProASIC3 Family: ProASIC3/E FPGAs

# Low-Density CPLD Replacement FPGA

The ProASIC3 series of flash FPGAs offers a breakthrough in power, performance, density, and features for today's most demanding high-volume applications. The ProASIC3 devices support the ARM Cortex-M1 processor, offering the benefits of programmability and time-to-market at low cost. The ProASIC3 devices are based on nonvolatile flash technology and support 330–35K logic elements and up to 620 high-performance I/Os. For automotive applications, selected ProASIC3 devices are qualified to AEC-Q100 and are available with AEC T1 screening and PPAP documentation.

- 1.5 V single voltage operation

- Instant-on

• Advanced I/O standards

- 350 MHz system performance

- Configuration memory error immune

- Secure ISP

## ProASIC3/E Devices

| ProASIC3/E<br>Devices    | Features                        | A3P030 | A3P060 <sup>2</sup> | A3P125 <sup>2</sup> | A3P250 <sup>2</sup> | A3P400   | A3P600   | A3P1000 <sup>2</sup> | A3PE600 | A3PE1500   | A3PE3000   |

|--------------------------|---------------------------------|--------|---------------------|---------------------|---------------------|----------|----------|----------------------|---------|------------|------------|

| ARM Cortex-M1<br>Devices | reatures                        |        |                     |                     | M1A3P250            | M1A3P400 | M1A3P600 | M1A3P1000            |         | M1A3PE1500 | M1A3PE3000 |

|                          | Logic elements<br>(approximate) | 330    | 700                 | 1,500               | 3,000               | 5,000    | 7,000    | 11,000               | 7,000   | 16,000     | 35,000     |

|                          | System gates                    | 30,000 | 60,000              | 125,000             | 250,000             | 400,000  | 600,000  | 1,000,000            | 600,000 | 1,500,000  | 3,000,000  |

| Logic                    | VersaNet globals <sup>3</sup>   | 6      | 18                  | 18                  | 18                  | 18       | 18       | 18                   | 18      | 18         | 18         |

|                          | AES-protected ISP1              |        | Yes                 | Yes                 | Yes                 | Yes      | Yes      | Yes                  | Yes     | Yes        | Yes        |

|                          | Integrated PLL in CCCs          |        | 1                   | 1                   | 1                   | 1        | 1        | 1                    | 6       | 6          | 6          |

|                          | RAM (1,024 bits)                |        | 18                  | 36                  | 36                  | 54       | 108      | 144                  | 108     | 270        | 504        |

| Fabric memory            | 4,608-bit blocks                |        | 4                   | 8                   | 8                   | 12       | 24       | 32                   | 24      | 60         | 112        |

| ,                        | FlashROM kbits<br>(1,024 bits)  | 1      | 1                   | 1                   | 1                   | 1        | 1        | 1                    | 1       | 1          | 1          |

| User I/O                 | I/O banks                       | 2      | 2                   | 2                   | 4                   | 4        | 4        | 4                    | 8       | 8          | 8          |

| USEL 1/O                 | Maximum user I/Os               | 81     | 96                  | 133                 | 157                 | 194      | 235      | 300                  | 270     | 444        | 620        |

Notes:

# I/Os per Package

|            | I/O Type            | QNG48 | QNG68 | CS(G)121 | VQ(G)100 | TQ(G)144 | PQ(G)208    | FG(G)144 | FG(G)256 | FG(G)324 | FG(G)484 | FG(G)676 | FG(G)896 |

|------------|---------------------|-------|-------|----------|----------|----------|-------------|----------|----------|----------|----------|----------|----------|

| ProASIC3   | Pitch (mm)          | 0.4   | 0.4   | 0.5      | 0.5      | 0.5      | 0.5         | 1.0      | 1.0      | 1.0      | 1.0      | 1.0      | 1.0      |

|            | Length × width (mm) | 6 × 6 | 8 × 8 | 6 × 6    | 16 × 16  | 20 × 20  | 30.6 × 30.6 | 13 × 13  | 17 × 17  | 19 × 19  | 23 × 23  | 27 × 27  | 31 × 31  |

| A3P030     | Single-end I/O      | 34    | 49    |          | 77       |          |             |          |          |          |          |          |          |

| A3P060     | Single-end I/O      |       |       | 96       | 71       | 91       |             | 96       |          |          |          |          |          |

| A3P125     | Single-end I/O      |       |       |          | 71       | 100      | 133         | 97       |          |          |          |          |          |

| A3P250/    | Single-end I/O      |       |       |          | 68       |          | 151         | 97       | 157      |          |          |          |          |

| M1A3P250   | Differential I/O    |       |       |          | 13       |          | 34          | 24       | 38       |          |          |          |          |

| A3P400/    | Single-end I/O      |       |       |          |          |          | 151         | 97       | 178      |          | 194      |          |          |

| M1A3P400   | Differential I/O    |       |       |          |          |          | 34          | 25       | 38       |          | 38       |          |          |

| A3P600/    | Single-end I/O      |       |       |          |          |          | 154         | 97       | 177      |          | 235      |          |          |

| M1A3P600   | Differential I/O    |       |       |          |          |          | 35          | 25       | 43       |          | 60       |          |          |

| A3P1000/   | Single-end I/O      |       |       |          |          |          | 154         | 97       | 177      |          | 300      |          |          |

| M1A3P1000  | Differential I/O    |       |       |          |          |          | 35          | 25       | 44       |          | 74       |          |          |

| A3PE600    | Single-end I/O      |       |       |          |          |          | 147         |          | 165      |          | 270      |          |          |

| ASPEDUU    | Differential I/O    |       |       |          |          |          | 65          |          | 79       |          | 135      |          |          |

| A3PE1500/  | Single-end I/O      |       |       |          |          |          | 147         |          |          |          | 280      | 444      |          |

| M1A3PE1500 | Differential I/O    |       |       |          |          |          | 65          |          |          |          | 139      | 222      |          |

| A3PE3000/  | Single-end I/O      |       |       |          |          |          | 147         |          |          | 221      | 341      |          | 620      |

| M1A3PE3000 | Differential I/O    |       |       |          |          |          | 65          |          |          | 110      | 168      |          | 310      |

AES is not available for ARM Cortex-M1 ProASIC3 devices.

<sup>2.</sup> Available as automotive "T" grade

<sup>3.</sup> Six chip (main) and three quadrant global networks are available for A3P060 and above.

<sup>1. (</sup>G) indicates that the package is RoHS 6/6 compliant/Pb-free.

# ProASIC3 Family: ProASIC3 nano FPGAs

# Low-Density CPLD Replacement FPGA with Small Package Footprint

Microsemi's innovative ProASIC3 nano devices bring a new level of value and flexibility to high-volume markets. When measured against the typical project metrics of performance, cost, flexibility, and time-to-market, the ProASIC3 nano devices provide an attractive alternative to ASICs and ASSPs in fast-moving or highly competitive markets. Customer-driven total-system cost reduction was a key design criteria for the ProASIC3 nano program. A single-chip implementation and a broad selection of small footprint packages, contribute to lower total system costs.

- 1.5 V core for low power

- Configuration memory error immune

- Enhanced I/O features

- 350 MHz system performance

- Enhanced commercial temperature

- ISP and security

## ProASIC3 nano Devices

| ProASIC3 nano Devices | Features                            | A3PN010 | A3PN020 | A3PN060 | A3PN125 | A3PN250 |

|-----------------------|-------------------------------------|---------|---------|---------|---------|---------|

|                       | Logic elements (approximate)        | 100     | 200     | 700     | 1,500   | 3,000   |

|                       | System gates                        | 10,000  | 20,000  | 60,000  | 125,000 | 250,000 |

| Logic                 | VersaNet globals                    | 4       | 4       | 18      | 18      | 18      |

|                       | AES-protected ISP                   |         |         | Yes     | Yes     | Yes     |

|                       | Integrated PLL in CCCs              |         |         | 1       | 1       | 1       |

|                       | RAM (1,024 bits)                    |         |         | 18      | 36      | 36      |

| Fabric memory         | 4,608-bit blocks                    |         |         | 4       | 8       | 8       |

|                       | FlashROM kbits (1,024 bits)         | 1       | 1       | 1       | 1       | 1       |

| User I/O              | I/O banks                           | 2       | 3       | 2       | 2       | 4       |

| User I/O              | Maximum user I/Os (packaged device) | 34      | 49      | 71      | 71      | 68      |

# I/Os per Package

| I/O Packages        | QNG48 | QNG68 | VQ(G)100 <sup>1</sup> |

|---------------------|-------|-------|-----------------------|

| Pitch (mm)          | 0.4   | 0.4   | 0.5                   |

| Length × width (mm) | 6 × 6 | 8 × 8 | 16 × 16               |

| A3PN010             | 34    |       |                       |

| A3PN020             |       | 49    |                       |

| A3PN060             |       |       | 71                    |

| A3PN125             |       |       | 71                    |

| A3PN250             |       |       | 68                    |

<sup>1. (</sup>G) indicates that the package is RoHS 6/6 compliant/Pb-free.

<sup>2.</sup> ProASIC3 nano devices do not support differential I/Os.

# ProASIC3 Family: ProASIC3L FPGAs

# Low-Density, Low-Power CPLD Replacement FPGA

ProASIC3L FPGAs feature lower dynamic power and lower static power than the previous generation of ProASIC3 FPGAs, and orders of magnitude lower power than SRAM competitors, combining dramatically reduced power consumption with up to 350 MHz operation. The ProASIC3L family also supports the free implementation of an FPGA-optimized 32-bit ARM Cortex-M1 processor, enabling system designers to select the Microsemi flash FPGA solution that best meets their speed and power requirements, regardless of application or volume. Optimized software tools using power-driven layout (PDL) provide instant power reduction capabilities.

- Low power 1.2 V to 1.5 V core operation

- 700 Mbps DDR, LVDS capable I/Os

- Up to 350 MHz system performance

- Configuration memory error immune

- ISP and security

- Flash\*Freeze technology for low power

# ProASIC3L Low-Power Devices

| ProASIC3L Devices                  | Footing.                            | A3P250L | A3P600L   | A3P1000L   | A3PE3000L   |

|------------------------------------|-------------------------------------|---------|-----------|------------|-------------|

| ARM Cortex-M1 Devices <sup>1</sup> | Features                            |         | M1A3P600L | M1A3P1000L | M1A3PE3000L |

|                                    | Logic elements (approximate)        | 3,000   | 7,000     | 11,000     | 35,000      |

| Logic                              | System gates                        | 250,000 | 600,000   | 1,000,000  | 3,000,000   |

|                                    | VersaNet globals                    | 18      | 18        | 18         | 18          |

|                                    | AES-protected ISP <sup>2</sup>      | Yes     | Yes       | Yes        | Yes         |

|                                    | Integrated PLL in CCCs <sup>3</sup> | 1       | 1         | 1          | 6           |

|                                    | RAM (1,024 bits)                    | 36      | 108       | 144        | 504         |

| Fabric memory                      | 4,608-bit blocks                    | 8       | 24        | 32         | 112         |

|                                    | FlashROM kbits (1,024 bits)         | 1       | 1         | 1          | 1           |

| User I/O                           | I/O banks                           | 4       | 4         | 4          | 8           |

| User I/O                           | Maximum user I/Os (packaged device) | 157     | 235       | 300        | 620         |

### Notes:

# I/Os per Package

|                   | I/O Type            | VQ(G)100 | PQ(G)208    | FG(G)144 | FG(G)256 | FG(G)324 | FG(G)484 | FG(G)896 |

|-------------------|---------------------|----------|-------------|----------|----------|----------|----------|----------|

| ProASIC3L Devices | Pitch (mm)          | 0.5      | 0.5         | 1.0      | 1.0      | 1.0      | 1.0      | 1.0      |

|                   | Length × width (mm) | 16 × 16  | 30.6 × 30.6 | 13 × 13  | 17 × 17  | 19 × 19  | 23 × 23  | 31 × 31  |

| A3P250L           | Single-end I/O      | 68       | 151         | 97       | 157      |          |          |          |

| A3P250L           | Differential I/O    | 13       | 34          | 24       | 38       |          |          |          |

| A3P600L/          | Single-end I/O      |          | 154         | 97       | 177      |          | 235      |          |

| M1A3P600L         | Differential I/O    |          | 35          | 25       | 43       |          | 60       |          |

| A3P1000L/         | Single-end I/O      |          | 154         | 97       | 177      |          | 300      |          |

| M1A3P1000L        | Differential I/O    |          | 35          | 25       | 44       |          | 74       |          |

| A3PE3000L/        | Single-end I/O      |          | 147         |          |          | 221      | 341      | 620      |

| M1A3PE3000L       | Differential I/O    |          | 65          |          |          | 110      | 168      | 310      |

<sup>1.</sup> Refer to the Cortex-M1 product brief for more information. 2. AES is not available for Cortex-M1 ProASIC3L devices.

<sup>3.</sup> For the A3PE3000L, the PQ208 package has six CCCs and two PLLs.

<sup>(</sup>G) indicates that the package is RoHS 6/6 compliant/Pb-free.

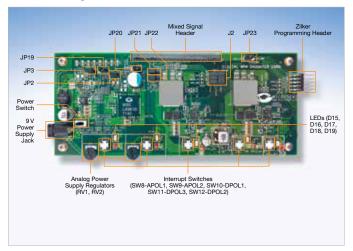

# SmartFusion SoC FPGAs

SmartFusion SoCs integrate an FPGA fabric, an ARM Cortex-M3 processor, and a programmable analog, offering full customization, IP protection, and ease-of-use. Based on Microsemi's proprietary flash process, SmartFusion SoCs are ideal for hardware and embedded designers who need a true system-on-chip that gives more flexibility than traditional fixed-function microcontrollers without the excessive cost of soft processor cores on traditional FPGAs.

- · Available in commercial, industrial, and military grades

- Hard 100 MHz 32-bit ARM Cortex-M3 CPU

- Multi-layer AHB communications matrix with up to 16 Gbps throughput

- 10/100 Ethernet MAC

- Two peripherals of each type: SPI, I2C, UART, and 32-bit timers

- Up to 512 KB flash and 64 KB SRAM

- External memory controller (EMC)

- 8-channel DMA controller

- Integrated analog-to-digital converters (ADCs) and digitalto-analog converters (DACs) with 1 % accuracy

- · On-chip voltage, current, and temperature monitors

- Up to ten 15 ns high-speed comparators

- Analog compute engine (ACE) offloads CPU from analog processing

- Up to 35 analog I/Os and 169 digital GPIOs

## **SmartFusion Devices**

| SmartFusion Devices | Features                                    | A2F060                                   | A2F200                      | A2F500                                   |

|---------------------|---------------------------------------------|------------------------------------------|-----------------------------|------------------------------------------|

|                     | Logic elements (approximate)                | 700                                      | 2,000                       | 6,000                                    |

| Logic               | System gates                                | 60,000                                   | 200,000                     | 500,000                                  |

|                     | RAM blocks (4,608 bits)                     | 8                                        | 8                           | 24                                       |

|                     | Flash (KB)                                  | 128                                      | 256                         | 512                                      |

|                     | SRAM (KB)                                   | 16                                       | 64                          | 64                                       |

|                     | Cortex-M3 with memory protection unit (MPU) | Yes                                      | Yes                         | Yes                                      |

|                     | 10/100 Ethernet MAC                         | No                                       | Yes                         | Yes                                      |

|                     | External memory controller (EMC)            | 26-bit address, 16-bit data <sup>1</sup> | 26-bit address, 16-bit data | 26-bit address, 16-bit data <sup>1</sup> |

| Microcontroller     | DMA                                         | 8 Ch                                     | 8 Ch                        | 8 Ch                                     |

| subsystem (MSS)     | I2C                                         | 2                                        | 2                           | 2                                        |

| Subsystem (MOO)     | SPI                                         | 2                                        | 2                           | 2                                        |

|                     | 16550 UART                                  | 2                                        | 2                           | 2                                        |

|                     | 32-bit timer                                | 2                                        | 2                           | 2                                        |

|                     | PLL                                         | 1                                        | 1                           | 22                                       |

|                     | 32 kHz low power oscillator                 | 1                                        | 1                           | 1                                        |

|                     | 100 MHz on-chip RC oscillator               | 1                                        | 1                           | 1                                        |

|                     | Main oscillator (32 KHz to 20 MHz)          | 1                                        | 1                           | 1                                        |

|                     | ADCs (8-/10-/12-bit SAR)                    | 1                                        | 2                           | 34                                       |

|                     | DACs (12-bit sigma-delta)                   | 1                                        | 2                           | 34                                       |

|                     | Signal conditioning blocks (SCBs)           | 1                                        | 4                           | 5 <sup>4</sup>                           |

| Programmable        | Comparators <sup>3</sup>                    | 2                                        | 8                           | 104                                      |

| analog              | Current monitors <sup>3</sup>               | 1                                        | 4                           | 5 <sup>4</sup>                           |

|                     | Temperature monitors <sup>3</sup>           | 1                                        | 4                           | 5 <sup>4</sup>                           |

|                     | Bipolar high voltage monitors <sup>3</sup>  | 2                                        | 8                           | 104                                      |

- 1. Not available on A2F500 for the PQ208 package and A2F060 for the TQ144 package.

- 2. Two PLLs are available in CS288 and FG484, one PLL in FG256 and PQ208.

- 3. These functions share I/O pins and may not all be available at the same time. See the "Analog Front-End Overview" section in the SmartFusion Programmable Analog User's Guide for details. 4. Available on FG484 only. PQ208, FG256 and CS288 packages offer the same programmable analog capabilities as A2F200.

# Package I/Os: MSS + FPGA I/Os

| Device                            |                 | A2F060 <sup>1</sup> |                 | A2F200 <sup>2</sup> |          |          |          |             | А        | 2F500 <sup>2</sup> |          |

|-----------------------------------|-----------------|---------------------|-----------------|---------------------|----------|----------|----------|-------------|----------|--------------------|----------|

| Device                            | TQ(G)144        | CS(G)288            | FG(G)256        | PQ(G)208            | CS(G)288 | FG(G)256 | FG(G)484 | PQ(G)208    | CS(G)288 | FG(G)256           | FG(G)484 |

| Pitch (mm)                        | 0.5             | 0.5                 | 1.0             | 0.5                 | 0.5      | 1.0      | 1.0      | 0.5         | 0.5      | 1.0                | 1.0      |

| Length × width (mm)               | 20 × 20         | 11 × 11             | 17 × 17         | 30.6 × 30.6         | 11 × 11  | 17 × 17  | 23 × 23  | 30.6 × 30.6 | 11 × 11  | 17 × 17            | 23 × 23  |

| Direct analog inputs              | 11              | 11                  | 11              | 8                   | 8        | 8        | 8        | 8           | 8        | 8                  | 12       |

| Shared analog inputs <sup>1</sup> | 4               | 4                   | 4               | 16                  | 16       | 16       | 16       | 16          | 16       | 16                 | 20       |

| Total analog input                | 15              | 15                  | 15              | 24                  | 24       | 24       | 24       | 24          | 24       | 24                 | 32       |

| Total analog output               | 1               | 1                   | 1               | 1                   | 2        | 2        | 2        | 1           | 2        | 2                  | 3        |

| MSS I/Os <sup>5</sup>             | 21 <sup>4</sup> | 28 <sup>4</sup>     | 26 <sup>4</sup> | 22                  | 31       | 25       | 41       | 22          | 31       | 25                 | 41       |

| FPGA I/Os                         | 33³             | 68                  | 66              | 66                  | 78       | 66       | 94       | 66³         | 78       | 66                 | 128      |

| Total I/Os                        | 70              | 112                 | 108             | 113                 | 135      | 117      | 161      | 113         | 135      | 117                | 204      |

- There are no LVTTL-capable direct inputs available on A2F060 devices.

EMC is not available on the A2F500, PQ208, and A2F060 TQ144 package.

- These pins are shared between direct analog inputs to the ADCs and voltage/current/temperature monitors.

10/100 Ethernet MAC is not available for A2F060.

- 5. 16 MSS I/Os are multiplexed and can be used as FPGA I/Os, if not required for MSS. These I/Os support Schmitt triggers, and support only LVTTL and LVCMOS (1.5 V/1.8 V/2.5 V/3.3 V) standards.

- 6. (G) indicates that the package is RoHS 6/6 compliant/Pb-free.

# Military SmartFusion2, IGLOO2 Devices

# FPGAs for Military Applications

For over 25 years, Microsemi has been the leader for high reliability defense applications. Microsemi FPGAs are qualified to Mil Std 883 Class B and QML class Q. Based on flash architecture, Microsemi offers the industry's most reliable and low-power FPGAs and SoC FPGAs. Military grade FPGAs are available in IGLOO2, ProASICPlus, and ProASIC3/EL device families, and SoC FPGAs are available in SmartFusion2, SmartFusion, and Fusion device families. In addition to the advantages of the mainstream FPGAs, SoC FPGAs have an embedded ARM Cortex-M3 microcontroller on-chip. SmartFusion and Fusion devices integrate configurable analog peripherals to yield a true system-on-chip solution.

- Tested for high reliability at temperature range of -55° C to 125° C

- Product longevity

- ISO-9001 and AS-9100-certified quality management system

- PCI Express Gen1 endpoints

- Instant-on

- · Small packages

- Zero FIT FPGA configuration cells

- SECDED memory protection

- · Built-in tamper detection and zeroization capability

- NRBG, AES-256, SHA-256, and ECC cryptographic engine

- User physically unclonable function (PUF)

- CRI DPA pass-through license

- Lowest-power operation

- Embedded ARM Cortex-M3 microcontroller subsystem

# Military SmartFusion2 and IGLOO2 Devices

| SmartFusion2/<br>IGLOO2 | Features                            | M2GL010<br>M2S010 | M2GL025<br>M2S025 | M2GL050<br>M2S050 | M2GL060<br>M2S060 | M2GL090<br>M2S090  | M2GL150<br>M2S150 |

|-------------------------|-------------------------------------|-------------------|-------------------|-------------------|-------------------|--------------------|-------------------|

|                         | Maximum logic elements (4LUT+DFF)   | 12,084            | 27,696            | 56,340            | 56,520            | 86,184             | 146,124           |

|                         | Mathblocks (18 × 18)                | 22                | 34                | 72                | 72                | 84                 | 240               |

| Logic/DSP               | PLLs and CCCs                       | 2                 |                   |                   | 6                 |                    | 8                 |

|                         | MSS (SmartFusion2) or HPMS (IGLOO2) |                   |                   |                   | 1                 |                    |                   |

|                         | Security                            | A                 | ES256, SHA256, RN | IG                | AES256            | 6, SHA256, RNG, EC | CC, PUF           |

|                         | eNVM (KB)                           |                   | 28                | 512               |                   |                    |                   |

|                         | eSRAM (KB)                          |                   |                   |                   | 64                |                    |                   |

| Memory                  | LSRAM 18K blocks                    | 21                | 31                | 69                | 69                | 109                | 236               |

| Wellioty                | uSRAM 1K blocks                     | 22                | 34                | 72                | 72                | 112                | 240               |

|                         | Total fabric RAM (kbits)            | 400               | 592               | 1314              | 1314              | 2074               | 4488              |

|                         | Total RAM (kbits)                   | 912               | 1104              | 1826              | 1826              | 2586               | 5000              |

|                         | DDR controllers                     |                   |                   | 1x18              |                   |                    | 2x36              |

| High-speed              | SERDES lanes                        |                   |                   | 4                 |                   |                    | 16                |

|                         | PCIe endpoints                      |                   | 1                 |                   | 2                 | 2                  | 4                 |

|                         | MSIO (3.3 V)                        | 123               | 157               | 105               | 157               | 157                | 292               |

| User I/O                | MSIOD (2.5 V)                       | 40                | 40                | 40                | 40                | 40                 | 106               |

| 0301 1/0                | DDRIO (2.5 V)                       | 70                | 70                | 122               | 70                | 70                 | 176               |

|                         | Total user I/O                      | 233               | 267               | 267               | 267               | 267                | 574               |

| Package                 |                                     | FG(G)484M         | FG(G)484M         | FG(G)484M         | FG(G)484M         | FG(G)484M          | FC(G)1152M        |

## I/Os per Package

|                       |       | Packa | age Options |          |

|-----------------------|-------|-------|-------------|----------|

| Package Type          | FG(G  | 3)484 | FC          | G(G)1152 |

| Pitch (mm)            |       | .0    |             | 1.0      |

| Length × width (mm)   | 23 :  | × 23  | 3           | 15 × 35  |

| Device                | I/O   | Lanes | I/O         | Lanes    |

| M2S010/M2GL010 (T/TS) | 233   | 4     |             |          |

| M2S025/M2GL025 (T/TS) | 267   | 4     |             |          |

| M2S050/M2GL050 (T/TS) | 267   | 4     |             |          |

| M2S060/M2GL060 (T/TS) | 267   | 4     |             |          |

| M2S090/M2GL090 (T/TS) | 267 4 |       |             |          |

| M2S150/M2GL150 (T/TS) |       |       | 574         | 16       |

- 1. Can migrate vertically in the same package

- 2. Gold wire bonds are available for the FG484 package by appending X399 to the part number when ordering (for example, M2S090 (T/TS)-1FG484MX399).

- 3. All the packages are available with lead and lead free. (G) indicates that the package is RoHS 6/6 compliant/Pb-free

# Military Smart Fusion, Fusion, and ProASIC3 Devices

# Military SmartFusion, ProASIC3, and Fusion Devices

| Devices                               | Features                        | A3P250  | A3PE600L | A3P1000   | A3PE3000L   | AFS600   | AFS1500   | A2F060                       | A2F500                       |

|---------------------------------------|---------------------------------|---------|----------|-----------|-------------|----------|-----------|------------------------------|------------------------------|

| ARM Cortex-M1<br>devices <sup>1</sup> |                                 |         |          | M1A3P1000 | M1A3PE3000L | M1AFS600 | M1AFS1500 | Hard 32-bit ARM<br>Cortex-M3 | Hard 32-bit ARM<br>Cortex-M3 |

|                                       | Logic elements<br>(approximate) | 3,000   | 7,000    | 11,000    | 35,000      | 7,000    | 16,000    | 700                          | 6,000                        |

|                                       | System gates                    | 250,000 | 600,000  | 1,000,000 | 3,000,000   | 600,000  | 1,500,000 | 60,000                       | 500,000                      |

| Logic                                 | PLL                             | 1       | 6        | 1         | 6           | 2        | 2         | 1                            | 2                            |

|                                       | ADCs (8-,10-,12-bit SAR)        |         |          |           |             | 1        | 1         | 1                            | 3                            |

|                                       | AES-protected ISP1              | Yes     | Yes      | Yes       | Yes         | Yes      | Yes       | Yes                          | Yes                          |

| Fabric memory                         | RAM (1,024 bits)                | 36      | 108      | 144       | 504         | 108      | 270       | 16                           | 64                           |

| Fabric memory                         | RAM blocks (4,608 bits)         | 8       | 24       | 32        | 112         | 24       | 60        | 8                            | 24                           |

|                                       | Maximum user I/Os               | 68      | 270      | 300       | 620         | 212      | 263       | 108                          | 204                          |

| User I/O                              | Digital I/Os                    | 68      | 270      | 300       | 620         | 172      | 223       | 92                           | 169                          |

|                                       | Analog I/Os                     |         |          |           |             | 40       | 40        | 16                           | 35                           |

# I/Os per Package

|                       | I/O Type            | VQ(G)100 | PQ(G)208    | FG(G)144 | FG(G)256 | FG(G)484 | FG(G)896 |

|-----------------------|---------------------|----------|-------------|----------|----------|----------|----------|

| Devices               | Pitch (mm)          | 0.5      | 0.5         | 1.0      | 1.0      | 1.0      | 1.0      |

|                       | Length × width (mm) | 16 × 16  | 30.6 × 30.6 | 13 × 13  | 17 × 17  | 23 × 23  | 31 × 31  |

| A3P250                | Single-end I/O      | 68       |             |          |          |          |          |

| A3F250                | Differential I/O    | 13       |             |          |          |          |          |

| A3PE600L              | Single-end I/O      |          |             |          |          | 270      |          |

| ASPEGUUL              | Differential I/O    |          |             |          |          | 135      |          |

| A3P1000/M1A3P1000     | Single-end I/O      |          | 154         | 97       | 177      | 300      |          |

| ASP1000/WITASP1000    | Differential I/O    |          | 35          | 25       | 44       | 74       |          |

| A3PE3000L/M1A3PE3000L | Single-end I/O      |          |             |          |          | 341      | 620      |

| ASPESUUUL/WIASPESUUUL | Differential I/O    |          |             |          |          | 168      | 310      |

| AFS600                | Single-end I/O      |          |             |          | 119      | 172      |          |

| AF5000                | Differential I/O    |          |             |          | 58       | 86       |          |

| AFS1500               | Single-end I/O      |          |             |          | 119      | 223      |          |

| AF51500               | Differential I/O    |          |             |          | 58       | 109      |          |

|                       | Analog I/O          |          |             |          | 16       |          |          |

| A2F060                | FPGA I/O            |          |             |          | 66       |          |          |

|                       | MSS I/O             |          |             |          | 26       |          |          |

|                       | Analog I/O          |          |             |          | 26       | 35       |          |

| A2F500                | FPGA I/O            |          |             |          | 66       | 128      |          |

|                       | MSS I/O             |          |             |          | 25       | 41       |          |

<sup>1.</sup> Refer to ARM Cortex-M1 product brief for more information.

<sup>2.</sup> AES is not available for ARM-enabled devices.

<sup>(</sup>G) indicates that the package is RoHS 6/6 compliant/Pb-free.

# **Automotive-Grade Products**

Microsemi offers dedicated automotive-grade devices with various densities, features, footprints, and temperature grades. All devices and packages are AEC-Q100-qualified and tested at extended temperatures. PPAP documentation is available for ProASIC3 devices on request.

# SmartFusion2 SoC FPGA Product Family

|            | Features                             | M2S005S | M2S010TS         | M2S025TS | M2S060TS     | M2S090TS           |  |  |  |

|------------|--------------------------------------|---------|------------------|----------|--------------|--------------------|--|--|--|

|            | Maximum logic elements (4LUT + DFF)1 | 6,060   | 12,084           | 27,696   | 56,520       | 86,184             |  |  |  |

|            | Math blocks (18 × 18)                | 11      | 22               | 34       | 72           | 84                 |  |  |  |

| Logic/DSP  | Fabric interface controllers (FICs)  |         | '                | 1        |              |                    |  |  |  |

|            | PLLs and CCCs                        | :       | 2                |          | 6            |                    |  |  |  |

|            | Data security                        | AE      | ES256, SHA256, F | RNG      | AES256, SHA2 | 256, RNG, ECC, PUF |  |  |  |

|            | Cortex-M3 + instruction cache        |         |                  | Yes      |              |                    |  |  |  |

|            | eNVM (KB)                            | 128     |                  | 256      | 512          |                    |  |  |  |

| Maa        | eSRAM (KB)                           | 64      |                  |          |              |                    |  |  |  |

| MSS        | eSRAM (KB) non-SECDED                | 80      |                  |          |              |                    |  |  |  |

|            | CAN, 10/100/1000 Ethernet, HS USB    | 1 each  |                  |          |              |                    |  |  |  |

|            | Multi-mode UART, SPI, I2C, timer     |         |                  | 1 eacl   | า            |                    |  |  |  |

|            | DDR controllers (count x width)      |         |                  | 1 × 18   | 1 × 18       |                    |  |  |  |

| High-speed | SERDES lanes (T)                     | 0       |                  |          | 4            |                    |  |  |  |

|            | PCIe endpoints                       | 0       |                  | 1        |              | 2                  |  |  |  |

|            | MSIO (3.3 V)                         | 115     | 123              | 157      | 271          | 309                |  |  |  |

| 111/0-     | MSIOD (2.5 V)                        | 28      | 40               | 40       | 40           | 40                 |  |  |  |

| User I/Os  | DDRIO (2.5 V)                        | 66      | 70               | 70       | 76           | 76                 |  |  |  |

|            | Total user I/O                       | 209     | 233              | 267      | 387          | 425                |  |  |  |

Notes :

# Package Options

| Туре                | VFG256 <sup>1</sup> |       | VFG400¹ |       | FGG484 <sup>1</sup> |       | FGG676 <sup>1</sup> |       |

|---------------------|---------------------|-------|---------|-------|---------------------|-------|---------------------|-------|

| Pitch (mm)          | 0.8                 |       | 0.8     |       | 1                   |       | 1                   |       |

| Length × width (mm) | 14 × 14             |       | 17 × 17 |       | 23 × 23             |       | 27 × 27             |       |

| Device              | I/O                 | Lanes | I/O     | Lanes | I/O                 | Lanes | I/O                 | Lanes |

| M2S005S             | 161                 |       | 171     |       | 209                 |       |                     |       |

| M2S010TS            | 138                 | 2     | 195     | 4     | 233                 | 4     |                     |       |

| M2S025TS            | 138                 | 2     | 207     | 4     | 267                 | 4     |                     |       |

| M2S060TS            |                     |       | 207     | 4     | 267                 | 4     | 387                 | 4     |

| M2S090TS            |                     |       |         |       | 267                 | 4     | 425                 | 4     |

<sup>1.</sup> Total logic may vary based on utilization of DSP and memories in the design.

<sup>2.</sup> Feature availability is package dependent.

All Automotive packages are RoHS compliant and available in lead-free options only.

$<sup>2. \ \</sup> Shadeing \ indicates \ that \ device \ packages \ have \ vertical \ migration \ capability.$

# Automotive-Grade Products

# IGLOO2 FPGA Product Family

|            | Features                             | M2GL005S | M2GL010TS        | M2GL025TS | M2GL060TS    | M2GL090TS          |  |

|------------|--------------------------------------|----------|------------------|-----------|--------------|--------------------|--|

|            | Maximum logic elements (4LUT + DFF)1 | 6,060    | 12,084           | 27,696    | 56,520       | 86,184             |  |

|            | Math blocks (18 x 18)                | 11       | 22               | 34        | 72           | 84                 |  |

|            | PLLs and CCCs                        |          | 2                |           | 6            |                    |  |

| Logic/DSP  | SPI/HPDMA/PDMA                       |          |                  | 1 eac     | h            |                    |  |

|            | Fabric interface controllers (FICs)  |          |                  | 1         |              |                    |  |

|            | Data security                        | А        | ES256, SHA256, R | NG        | AES256, SHA2 | 256, RNG, ECC, PUF |  |