Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### **ASAHI KASEI EMD**

## AK2300 3.3V Single channel PCM CODEC LSI

#### **GENERAL DESCRIPTION**

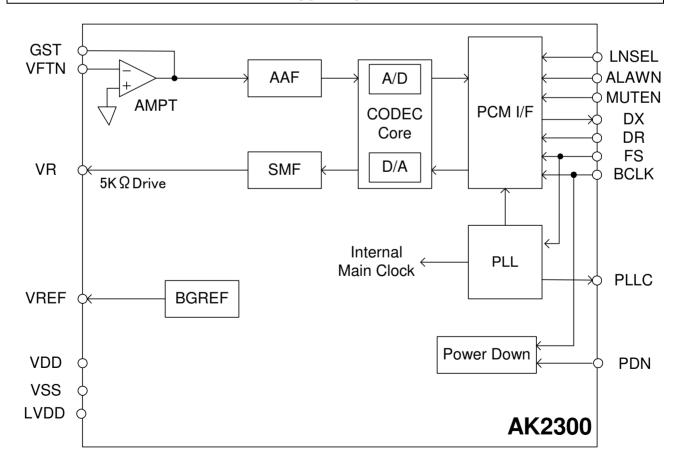

The AK2300 is a single channel PCM CODEC for various applications for example, AFE. It includes the selectable linear PCM interface, A/ $\mu$ -law function, mute and power down. All of these functions are controlled by the pin.

It includes Band limiting filter, A/D and D/A converter, and A-law/ $\mu$ -law converter. All functions are provided in very small QFN(16pins) package and it is good for reducing the mounting space.

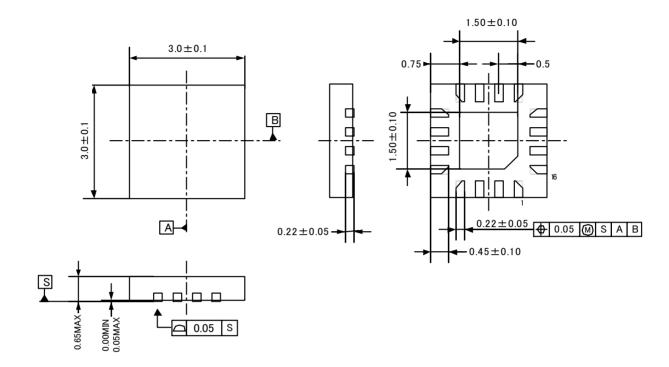

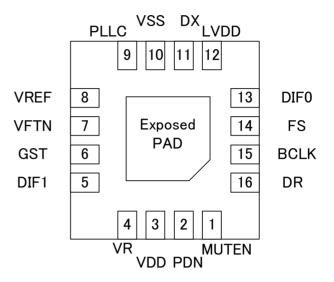

#### **PACKAGE**

♦ 16pin QFN Body 3.0\*3.0mm Pin pitch 0.5mm

#### **FEATURE**

[AK2300]

- ◆Single PCM CODEC and filtering system

- ◆ Selectable functions

- Mute

- Power down (PDN='L' or BCLK='L')

- A-law / µ-law / linear PCM

- ◆Long Frame / Short Frame are selected by pin

- ◆PCM data rate (64k\*N)Hz (N=1~32)

- ♦ Op-amp for the external gain adjustment

- ◆ Single power supply voltage: +2.6~+3.6V(VDD)

- ◆ Digital I/F power supply voltage: +1.7~3.6V(LVDD)

- ♦ Low power consumption

- Power on : 5.3mA(typ)Power down : 0.1uA(typ)

#### **BLOCK DIAGRAM**

## CONTENT

|   | ITEMS                           | PAGE     |   |

|---|---------------------------------|----------|---|

|   |                                 | <u>.</u> |   |

| _ | BLOCK DIAGRAM                   | 1        |   |

| _ | PIN CONDITION                   | 3        |   |

| _ | PIN FUNCTION                    | 4        |   |

| _ | ABSOLUTE MAXIMUM RATINGS        | 5        |   |

| _ | RECOMMENDED OPERATING CONDITION | N 5      |   |

| _ | ELECTRICAL CHARACTERESTICS      | 5        |   |

| _ | PACKAGE INFORMATION             | 1        | 1 |

| _ | PIN ASSIGNMENT                  | 1        | 2 |

| _ | MARKINGS                        | 12       | 2 |

| _ | CIRCUIT DESCRIPTIONS            | 1        | 3 |

| _ | FUNCTIONAL DESCLIPTIONS         | 1        | 4 |

| _ | PCM CODEC                       | 10       | 4 |

| _ | PCM INTERFACE                   | 1        | 4 |

| _ | MUTE, Power Down                | 10       | 6 |

| _ | START UP PROCEDURE              | 1        | 7 |

| _ | APPLICATION CIRCUIT EXAMPLE     | 1        | 8 |

## PIN CONDITIONS

| Pin# | Name  | I/O | Pin type | AC load<br>(MAX.) | DC load<br>(MIN.)         | Output<br>status<br>(mute) | Output<br>status<br>(PD) | Remarks                                                                  |

|------|-------|-----|----------|-------------------|---------------------------|----------------------------|--------------------------|--------------------------------------------------------------------------|

| 7    | VFTN  | I   | Analog   |                   |                           |                            |                          |                                                                          |

| 6    | GST   | 0   | Analog   | 50pF              | AC load(*1)<br>10k Ω (*2) |                            | Hi-Z                     |                                                                          |

| 4    | VR    | 0   | Analog   | 40pF              | AC load(*1)<br>5k Ω       | Analog<br>ground           | Hi-Z                     |                                                                          |

| 14   | FS    | I   | CMOS     |                   |                           |                            |                          | Pull down<br>100K±50Kohm                                                 |

| 15   | BCLK  | I   | CMOS     |                   |                           |                            |                          | Pull down<br>100K±50Kohm                                                 |

| 11   | DX    | 0   | CMOS     | 50pF              |                           | 0 code                     | VSS                      |                                                                          |

| 16   | DR    | I   | CMOS     |                   |                           |                            |                          | Pull down<br>100K±50Kohm                                                 |

| 1    | MUTEN | ı   | CMOS     |                   |                           |                            |                          | Do not open                                                              |

| 2    | PDN   | 1   | CMOS     |                   |                           |                            |                          | Do not open                                                              |

| 13   | DIF0  | I   | CMOS     |                   |                           |                            |                          | Do not open                                                              |

| 5    | DIF1  | -   | CMOS     |                   |                           |                            |                          | Do not open(*3)                                                          |

| 3    | VDD   | -   | PWR      |                   |                           |                            | -                        |                                                                          |

| 12   | LVDD  | -   | PWR      |                   |                           |                            | -                        |                                                                          |

| 10   | VSS   | -   | GND      |                   |                           |                            |                          |                                                                          |

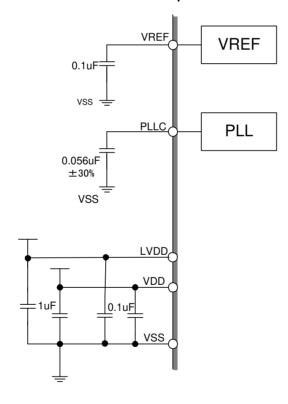

| 8    | VREF  | 0   | Analog   |                   |                           |                            | VSS                      | - External capacitance 0.1uF                                             |

| 9    | PLLC  | 0   | Analog   |                   |                           |                            | VSS                      | - External capacitance 0.056uF±30% (Includes temperature characteristic) |

<sup>\*1)</sup> AC load is feedback resistance to VFTN.

\*2) This value includes a feedback resistance of input/output op-amps.

\*3) Please connect it with VDD when DIF1 is "H".

## PIN FUNCTION

Pin types DIN: D Digital input Analog input DOUT: Digital output AOUT: Analog output PWR: Power / Ground AIN:

| IIN: Ana | alog input     |      | AOUT: Analog output                                                                                                                                                                                                                                             |

|----------|----------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin#     | Name           | Type | Function                                                                                                                                                                                                                                                        |

| 7        | VFTN           | AIN  | Negative analog onput of analog input OP amp. Signgle-end amplifire is composed the exernal registers. Transmit gain is defined by the ratio of the external registers.                                                                                         |

| 6        | GST            | AOUT | Output of the transmit OP amp.  The external feedback resister is connected between this pin and VFTN.                                                                                                                                                          |

| 4        | VR             | AOUT | Analog output of the D/A converter equivalent to the received PCM code.                                                                                                                                                                                         |

| 14       | FS             | DIN  | Frame sync input This clock is input for the internal PLL which generates the internal system clocks. FS must be 8kHz clock which synchronized with BCLK.                                                                                                       |

| 5        | BCLK           | DIN  | Bit clock of PCM data interface This clock defines the input/output timing of DX and RX. The frequency of BCLK should be 64kHz × N (N=1~32) and duty should be 40~60%. When this pin is taken low, power down the device. *Please don't stop BCLK at "H" level. |

| 11       | DX             | DOUT | Serial output of PCM data  The PCM data is synchronized with BCLK. This output remains in the low level except for the period in which PCM data is transmitted.                                                                                                 |

| 16       | DR             | DIN  | Serial input of PCM data The PCM data is synchronized with BCLK.                                                                                                                                                                                                |

| 1        | MUTEN          | DIN  | Mute setting pin "L" level forces both A/D, D/A output to mute state.                                                                                                                                                                                           |

| 2        | PDN            | DIN  | Power down setting pin "L" level forces power down mode.                                                                                                                                                                                                        |

| 13       | DIF0           | DIN  | Audio data interface select pin "L"=A-law,"H"=μ-law,"FS"=Linear PCM (Please connect DIF0 with FS(#14) at a Linear PCM mode.)                                                                                                                                    |

| 5        | DIF1           | DIN  | Audio data interface timing select pin  "H": MSB of DX/DR are input/output by rising edge of FS.(Connect to VDD)  "L": MSB of DX/DR are input/output by next rising edge of BCLK after the rising edge of FS.  (Please connect it with VDD when DIF1 is "H".)   |

| 3        | VDD            | PWR  | Positive supply voltage                                                                                                                                                                                                                                         |

| 12       | LVDD           |      | Positive supply voltage for digital interface                                                                                                                                                                                                                   |

| 10       | VSS            | PWR  | Ground (0V)                                                                                                                                                                                                                                                     |

| 8        | VREF           | AOUT | Analog reference voltage output External capacitance $(0.1\mu F)$ should be connected between this pin and VSS. Please do not connect external load to this pin.                                                                                                |

| 9        | PLLC           | AOUT | PLL loop filter output External capacitance (0.056μF±30%: Includes temperature characteristic) should be connected between this pin and VSS.                                                                                                                    |

|          | Exposed<br>Pad | -    | Flip side PAD<br>VSS or Open                                                                                                                                                                                                                                    |

## **ABSOLUTE MAXIMUM RATINGS**

| Parameter                                | Symbol | min  | max      | Units        |

|------------------------------------------|--------|------|----------|--------------|

| Power supply voltage                     |        |      |          |              |

| Analog/Digital power supply              | VDD    | -0.3 | 4.6      | V            |

| Digital interface power supply           | LVDD   | -0.3 | 4.6      | V            |

| Digital input voltage                    | VTD    | -0.3 | LVDD+0.3 | V            |

| Analog input voltage                     | VTA    | -0.3 | VDD+0.3  | V            |

| Input current (except power supply pins) | lin    | -10  | 10       | uA           |

| Storage temperature                      | Tstg   | -55  | 125      | $^{\circ}$ C |

Warning: Exceeding absolute maximum ratings may cause permanent damage.

Normal operation is not guaranteed at these extremes.

## **RECOMMENDED OPERATING CONDITIONS**

| Parameter                          | Symbol | min   | typ | max   | Units                  |

|------------------------------------|--------|-------|-----|-------|------------------------|

| Power supply voltage               |        |       |     |       |                        |

| Analog/Digital power supply        | VDD    | 2.6   | 3.3 | 3.6   | V                      |

| Digital interface power supply *1) | LVDD   | 1.7   | 3.3 | 3.6   | V                      |

| Ambient operating temperature      | Ta     | -30   |     | 85    | $^{\circ}\!\mathbb{C}$ |

| Frame sync frequency *2)           | FS     | -1.0% | 8   | +1.0% | kHz                    |

Note) All voltages reference to ground: VSS = 0V

## **ELECTRICAL CHARACTERISTICS**

Unless otherwise noted, guaranteed for VDD = +2.6V~3.6V, LVDD=+1.7V~+3.6V (VDD $\ge$ LVDD), Ta = -30~+85°C, FS=8kHz, VSS=0V

## **DC Characteristics**

| Parameter             | Symbol  | Conditions                    | min     | typ | Max     | Unit |

|-----------------------|---------|-------------------------------|---------|-----|---------|------|

| Power Consumption     | PDD1*1) | *1)BCLK=2.048                 |         | 5.3 | 9.0     | mA   |

| (All output unloaded) | PDD2    | Power down                    |         | 0.1 | 5.0     | uA   |

| Output high voltage   | Vон     | IOH=-200uA                    | 0.8VDD  |     |         | ٧    |

| Output low voltage    | Vol     | IoL=200uA                     |         |     | 0.4     | ٧    |

| Input high voltage1   | VIH1    | FS,BCLK,DR,MUTEN,<br>PDN,DIF0 | 0.7LVDD |     |         | V    |

| Input low voltage1    | VIL1    | FS,BCLK,DR,MUTEN,<br>PDN,DIF0 |         |     | 0.3LVDD | ٧    |

| Input high voltage2   | VIH2    | DIF1                          | 0.7VDD  |     |         | V    |

| Input low voltage2    | VIL2    | DIF1                          |         |     | 0.3VDD  | ٧    |

| Input leakage current | ILL     | Except pull down pins         | -10     |     | +10     | uA   |

| Analog ground output  | VRG     | VREF pin                      | 1.2     | 1.3 | 1.4     | ٧    |

<sup>\*1)</sup> VFTN=1020Hz@0dBm0 input, DR=1020Hz@0dBm0 Code input.

<sup>\*1)</sup>VDD≧LVDD

<sup>\*2)</sup> All the characteristics of the CODEC are defined by 8kHz FS.

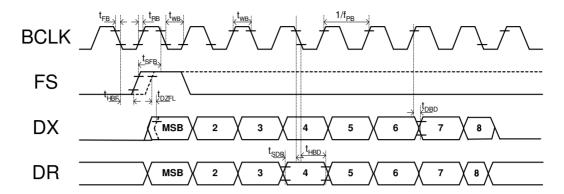

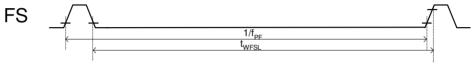

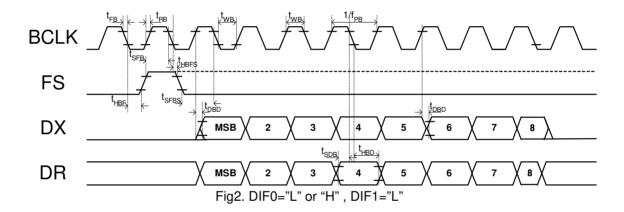

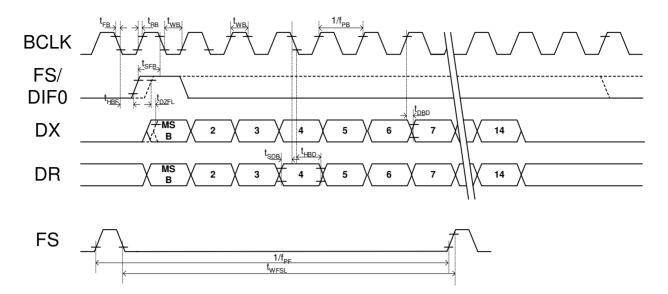

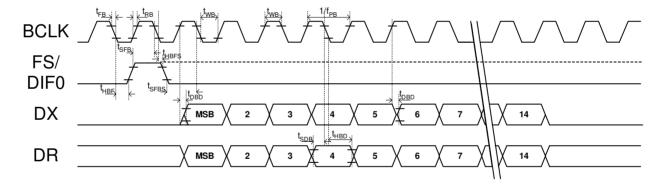

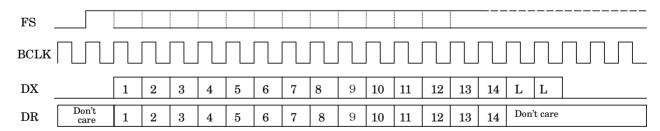

## **PCM INTERFACE** (Long Frame, Short Frame)

All timing parameters of the output pins are measured at VOH = 0.8LVDD and VOL = 0.4V. Input pins are measured at VIH = 0.7LVDD and VIL = 0.3LVDD.

## **AC Characteristics**

| Parameter                                                          | Symbol                             | Min   | Тур                             | Max   | Unit | Ref Fig        |

|--------------------------------------------------------------------|------------------------------------|-------|---------------------------------|-------|------|----------------|

| FS Frequency                                                       | f <sub>PF</sub>                    | -1.0% | 8                               | +1.0% | kHz  |                |

| BCLK Frequency                                                     | f <sub>PB</sub>                    | -     | f <sub>PF</sub> ×8N<br>(N=1~32) | -     | kHz  |                |

| BCLK Duty Cycle                                                    | t <sub>WB</sub>                    | 40    |                                 | 60    | %    |                |

| Rising/Falling Time: (BCLK,FS, DX,DR)                              | t <sub>RB</sub><br>t <sub>FB</sub> |       |                                 | 40    | ns   |                |

| Hold Time: BCLK Low to FS High                                     | t <sub>HBF</sub>                   | 60    |                                 |       | ns   |                |

| Setup Time: FS High to BCLK Low                                    | t <sub>SFB</sub>                   | 20    |                                 |       | ns   |                |

| Setup Time: DR to BCLK Low                                         | t <sub>SDB</sub>                   | 20    |                                 |       | ns   | Fig1,2,<br>3,4 |

| Hold Time: BCLK Low to DR                                          | t <sub>HBD</sub>                   | 60    |                                 |       | ns   |                |

| FS Pulse Width Low                                                 | t <sub>WFSL</sub>                  | 1     |                                 |       | BCLK |                |

| Delay time: FS or BCLK High, whichever is later,to DX valid Note1) | T <sub>DZFL</sub>                  |       |                                 | 60    | ns   |                |

| Hold time: BCLK Low to FS Low                                      | T <sub>HBFS</sub>                  | 60    |                                 |       | ns   |                |

| Setup time: FS Low to BCLK Low                                     | T <sub>SFBS</sub>                  | 20    |                                 |       | ns   |                |

| Delay Time: BCLK High to DX valid Note1)                           | t <sub>DBD</sub>                   | 0     |                                 | 60    | ns   |                |

Note1) Measured with 50pF load capacitance and 0.2mA drive.

## **Interface Timing**

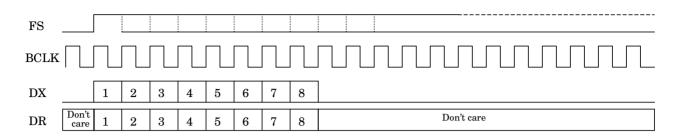

Fig1. DIF0="L" or "H", DIF1="H"

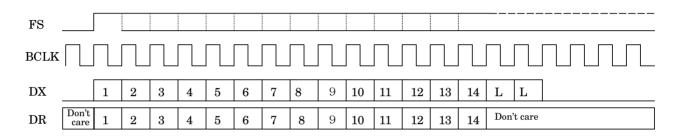

Fig3. DIF0="FS", DIF1="H"

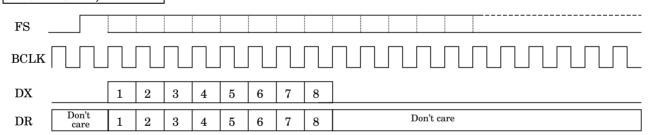

Fig4. DIF0="FS", DIF1="L"

## CODEC

\* The AMPT characteristics is measured at the 0dB gain.

The frequency specifications when FS deviation from 8kHz are as follows:

$\frac{UsedFS}{S}$  × noted frequency specification = Effective frequency specification 8k[Hz]

#### **Absolute Gain**

| Parameter              |               | Conditions         | min  | typ   | max | Unit |

|------------------------|---------------|--------------------|------|-------|-----|------|

| Analog input level     | VFTN          | 0dBm0@1020Hz input |      | 0.460 |     | Vrms |

| Absolute transmit gain | $\rightarrow$ |                    | -0.6 | _     | 0.6 | dB   |

| Maximum overload level | DX            | 3.14dBm0           |      | 0.660 |     | Vrms |

| Analog output level    | DR            | 0dBm0@1020Hz input |      | 0.460 |     | Vrms |

| Absolute receive gain  | $\rightarrow$ |                    | -0.6 | _     | 0.6 | dB   |

| Maximum overload level | VR            | 3.14dBm0           |      | 0.660 |     | Vrms |

Frequency response

| Parameter                   |              | Conditions      |      | Тур | max | Unit |

|-----------------------------|--------------|-----------------|------|-----|-----|------|

| Transmit frequency response | Relative to: | -55dBm0∼-50dBm0 | -1.2 | _   | 1.2 |      |

| $(A \rightarrow D)$         | -10dBm0      | -50dBm0∼-40dBm0 | -0.4 | _   | 0.4 | dB   |

| VFTN → DX                   | 1020Hz Tone  | -40dBm0∼ 3dBm0  | -0.2 | _   | 0.2 |      |

| Receive frequency response  | Relative to: | -55dBm0∼-50dBm0 | -1.2 | _   | 1.2 |      |

| $(D \rightarrow A)$         | -10dBm0      | -50dBm0∼-40dBm0 | -0.4 | _   | 0.4 | dB   |

| $DR \rightarrow VR$         | 1020Hz Tone  | -40dBm0∼ 3dBm0  | -0.2 | _   | 0.2 |      |

Frequency response

| Parameter                   | Co           | nditions   | min   | typ | max  | Unit |

|-----------------------------|--------------|------------|-------|-----|------|------|

| Transmit Frequency response | Relative to: | 0.05kHz    | _     | _   | -30  |      |

| $(A \rightarrow D)$         | 0dBm0@1020Hz | 0.06kHz    | _     | _   | -26  |      |

|                             |              | 0.2kHz     | -1.8  | _   | 0    |      |

| VFTN → DX                   |              | 0.3∼3.0kHz | -0.15 | _   | 0.15 | dB   |

|                             |              | 3.4kHz     | -0.8  | _   | 0    |      |

|                             |              | 4.0kHz     | _     | _   | -14  |      |

| Receive Frequency response  | Relative to: | 0∼3.0kHz   | -0.15 | _   | 0.15 |      |

| $(D \rightarrow A)$         | 0dBm0@1020Hz | 3.4kHz     | -0.8  | _   | 0    | dB   |

| DR → VR                     |              | 4.0kHz     | _     | _   | -14  |      |

Distortion (A-law, u-law)

| Σιστοιτίστι (ετ ιατι, μ ιατι, |             |                 |    |     |     |      |

|-------------------------------|-------------|-----------------|----|-----|-----|------|

| Parameter                     | Co          | Conditions      |    | typ | max | Unit |

| Transmit signal to Distortion | 1020Hz Tone | -40dBm0∼-45dBm0 | 25 | _   | _   |      |

| $(A \rightarrow D)$           |             | -30dBm0∼-40dBm0 | 30 | _   | _   | dB   |

| VFTN → DX                     |             | 0dBm0∼-30dBm0   | 36 | _   | _   |      |

| Receive signal to Distortion  | 1020Hz Tone | -40dBm0∼-45dBm0 | 25 | _   | _   |      |

| $(D \rightarrow A)$           |             | -30dBm0∼-40dBm0 | 30 | _   |     | dB   |

| $DR \rightarrow VR$           |             | 0dBm0∼-30dBm0   | 36 | _   | _   |      |

**Distortion (Liear PCM)**

| Parameter                                                               | Conditions  |                   | min | typ | max | Unit |

|-------------------------------------------------------------------------|-------------|-------------------|-----|-----|-----|------|

| Transmit signal to Distortion $(A \rightarrow D)$ VFTN $\rightarrow$ DX | 1020Hz Tone | 0dBm0 (C-massage) |     | 78  |     | dB   |

| Receive signal to Distortion $(D\rightarrow A)$ DR $\rightarrow$ VR     | 1020Hz Tone | 0dBm0 (C-massage) |     | 81  |     | dB   |

## Noise

| Parameter                   | Conditions                                 | min | typ | max | Units  |

|-----------------------------|--------------------------------------------|-----|-----|-----|--------|

| Idle channel noise A→D (*1) | →D (*1) u-law, C-message                   |     | 12  | 17  | dBrnC0 |

| VFTN → DX                   | A-law, Psophometric                        |     | -78 | -73 | dBm0p  |

|                             | Linear, C-message                          | _   | 12  | 17  | dBrnC0 |

| Idle channel noise D→A(*2)  | u-law, C-message                           | _   | 9   | 14  | dBrnC0 |

| DR → VR                     | A-law, Psophometric                        | _   | -81 | -76 | dBm0p  |

|                             | Linear, C-message                          | _   | 9   | 14  | dBrnC0 |

| PSRR<br>Transmit path       | VDD= $3.3V/\pm66$ mVop<br>f= $0\sim10$ kHz | _   | 55  | _   | dB     |

| PSRR<br>Receiver path       | VDD= $3.3V/\pm66mVop$<br>f= $0\sim10kHz$   | _   | 55  | _   | dB     |

<sup>(\*1)</sup> Analog input is set to the analog ground level (\*2) Digital input is set to the +0 CODE

## Crosstalk

| Parameter | Conditions                                  |   | Тур | max | Units |

|-----------|---------------------------------------------|---|-----|-----|-------|

|           | VFTN 0dBm0@1020Hz<br>DR = 0-Code            | _ | _   | -75 | dB    |

|           | DR=0dBm0@1020Hz code level<br>VFTN = 0 Vrms | _ | _   | -75 | dB    |

Analog input op-amp characteristics :AMPT

| The state of the s |                                        |     |     |     |       |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-----|-----|-----|-------|--|

| Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Conditions                             | min | Тур | max | Units |  |

| Load resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | AC load, Including feedback resistance | 10  | _   | _   | kΩ    |  |

| Load capacitance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                        | _   |     | 50  | рF    |  |

| Gain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Inverting amplifiers                   | -6  |     | 20  | dB    |  |

Receive signal output characteristics :VR

| Parameter                  | Conditions                   |   | typ | max | Units |

|----------------------------|------------------------------|---|-----|-----|-------|

| Output voltage(AGND level) | GND level) PCM +0 code input |   | 1.3 | _   | ٧     |

| Load resistance AC load    |                              | 5 | _   | _   | kΩ    |

| Load capacitance           |                              | _ | _   | 40  | рF    |

## PACKAGE INFORMATION

16pin QFN (3mm x 3mm)

M [AK2300]

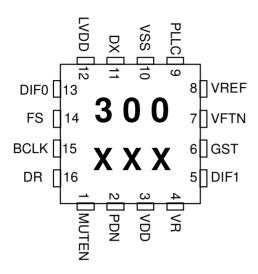

PIN ASSIGNMENT

## 16pin QFN

## **Top View**

## **Bottom View**

## **MARKING**

(1) 1pin sign

(2) Marketing Code: 300(3) Date Code: 3digit XXX

## CIRCUIT DESCRIPTION

| BLOCK        | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

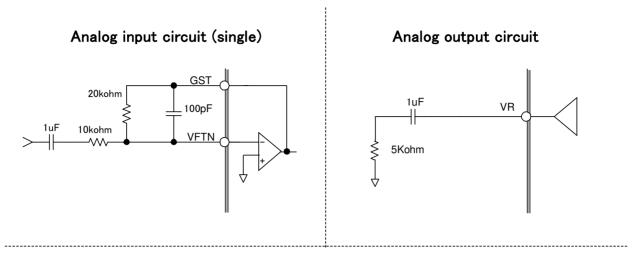

| AMPT         | Op-amp for input gain adjustment. This op-amp is used as an inverting amplifier. Adjusting the gain with external resistors. The resistor should be larger than 10kohm for the feedback resistor. VFTN: Negative op-amp input. GST: Op-amp output.                                                                                                                                                |  |  |  |  |  |

| AAF          | Integrated anti-aliasing filter which prevents signals around the sampling rate from folding back into the voice band. AAF is a 2nd order RC active low-pass filter.                                                                                                                                                                                                                              |  |  |  |  |  |

| CODEC<br>A/D | Converting the analog signal to 14bits linear data. And it is PCM data according to the companding schemes of ITU recommendation G.711; A-law or u-law. The band limiting filter is also integrated.  The selection of companding schemes(A-law/ and interface timing are set by DIF0/1pins.                                                                                                      |  |  |  |  |  |

| CODEC<br>D/A | Converting the 14bits linear PCM data or 8bits PCM data accroding to A-law / u-law.  The selection of expanding schemes and interface timing are set by DIF0/1pins.                                                                                                                                                                                                                               |  |  |  |  |  |

| SMF          | Extracts the inband signal from D/A output. It also corrects the sinx/x effect of the D/A output.                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| BGREF        | Provide the stable analog reference voltage using an on-chip band-gap reference circuit which is temperature compensated. The output voltage is 1.3V for 3.3V An external capacitor of 0.1uF should be connected between VREF and VSS to stabilize analog ground (VREF).  Please do not connect external load to this pin.                                                                        |  |  |  |  |  |

| PCM I/F      | For the PCM data rate, 64kHz × N (N=1~32) are available. The 8bit PCM data is input/output by A/u-law data. The 14bit PCM data is input/output by the 2's compliment 16bit serial data format. PCM data is input to DR pin and output from DX pin. The selection of interface timing is selected by DIF0/1 pins.  DIF0  DIF1  "L" : A-law "H": MSB of DX/DR are input/output by rising edge of FS |  |  |  |  |  |

|              | "H": u-law "L": MSB of DX/DR are input/output by next rising edge "FS": Linear of BCLK after the rising edge of FS.                                                                                                                                                                                                                                                                               |  |  |  |  |  |

#### FUNCTIONAL DESCRIPTIONS

#### **PCM CODEC**

#### - Δ/D

Analog input signal is converted to 14bit PCM data. The analog signal is fed to the anti-aliasing filter (AAF) before the converting PCM data, to prevent signals around the sampling rate from folding back into the voice band. The converted PCM data passes through the band limiting filter which Frequency response is designated in page8, and output from the DX pin with MSB first format. It is synchronized with rising edge of the BCLK. This PCM data is 8bit A/u-law or 14bit linear. And full scale is defined as 3.14dBm0. The analog input of 0.660Vrms is converted to a digital code of 3.14dBm0.

#### - D/A

Input PCM data from the DR pin is through the digital filter which Frequency response is designated in page8, and converted analog signal. This analog signal is removed the high frequency element with SMF (fc=30kHz typ) and output from the VR pin. The input PCM data is 8bit A/u-law data or 14bit linear. And full scale is defined as 3.14dBm0. When the input signal is 3.14dBm0, the level of the analog output signal becomes 0.660Vrms.

#### - 14bit linear PCM digital code

The relation ship between the analog signal and the 14bit linear code.

| Signal level                      | 14bit linear CODE (MSB First) |

|-----------------------------------|-------------------------------|

| +Full code                        | 01 1111 1111 1111             |

| Peak value of the PCM 0dBm0 CODEC | 01 0110 0100 1010             |

| PCM 0-CODE                        | 00 0000 0000 0000             |

| -Full scale                       | 10 0000 0000 0000             |

## **PCM Data Interface**

AK2300 supports the following PCM data formats

- DIF0="L" : A-Law - DIF0="H": u-Law

- DIF0="FS": Linear PCM

- DIF1="H": MSB of DX/DR are input/output by rising edge of FS

- DIF1="L": MSB of DX/DR are input/output by next rising edge of BCLK after the rising edge of FS.

PCM data is interfaced through the pin (DX, DR).

In each case, PCM data is interfaced by A/u-law data with 8bit format and 2's compliment 2digit data with 16bit MSB first format. However, internal CODEC is 14bit format operation, then the lowest 2bits output become to "L" level. For the input, the lowest 2bits are ignored.

#### - Frame sync signal (FS)

8kHz reference signal. This signal indicated the timing and the frame position of 8kHz PCM interface. All the internal clock of the LSI is generated based on this FS signal.

#### -Bit clock (BCLK)

BCLK defines the PCM data rate. BCLK rate is  $64kHz \times N$  (N=1~32). This clock must be synchronized with FS.

## DIF0="L or H", DIF1="H"

## DIF0="FS", DIF1="H"

## DIF0="L or H", DIF1="L"

## DIF0="FS", DIF1="L"

[AK2300] **MUTE**

The output of the PCM CODEC can be muted by pin control.

MUTEN pin

| MUTEN pin | Operation | DX pin          | VR pin              |

|-----------|-----------|-----------------|---------------------|

| L         | Mute      | 0 Code          | VREF level(1.3V)    |

| Н         | Normal    | PCM data output | CODEC analog output |

When the MUTEN pin turns to "L" during the data output, the mute function becomes available at the top of the next FS.

#### [VR pin]

When the MUTEN pin turns to "L", 0 code is fed to the D/A converter and VR becomes at analog reference level (VREF level=1.3V).

#### **POWER DOWN MODE**

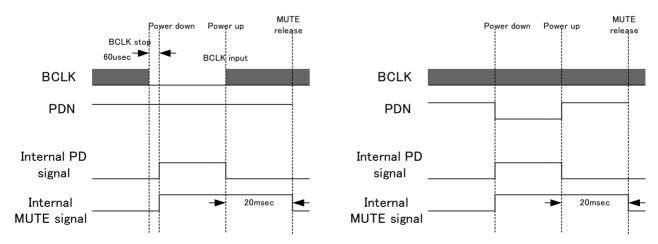

PDN pin "L" or to hold the BCLK pin "L", the AK2300 is powered down. (\*Please don't stop BCLK at "H" level.)

#### Power up/down sequence

#### 1) Power down

60usec(typ) passed after the PDN pin turns "L" or the BCLK pin hold "L", internal PDN signal turn to L and the AK2300 is powered down.

When power down mode the output pins are as follows.

| PIN Name     | GST  | VR   | DX  | VREF | PLLC |

|--------------|------|------|-----|------|------|

| Output state | Hi-Z | Hi-Z | vss | vss  | vss  |

## 2) Power up

FS and BCLK pins are clocked and PDN pin ="H", internal PDN signal is turn to "H" and power down mode is

During power down mode and 20msec (typ) after the power up, the voice path is muted for not to output abnormal noise.

Power Down by BCLK="L"

Power Down by PDN="L"

AKM [AK2300]

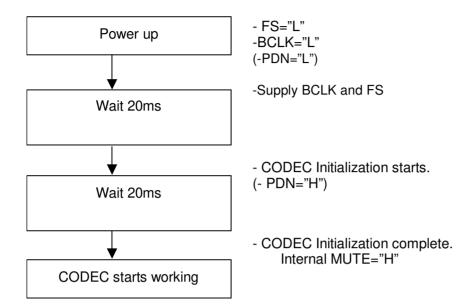

## Recommended start up procedure

The following start up procedure is recommended when AK2300 is going to power up. Power up is 5ms or less, internal Power On Reset is working, because () in the following sequence can be omitted.

## **APPLICATION CIRCUIT EXAMPLES**

# Power supply, PLL loop filter capacitor and analog ground stabillization capacitor

#### IMPORTANT NOTICE

These products and their specifications are subject to change without notice. When you consider any use or application of these products, please make inquiries the sales office of Asahi Kasei EMD Corporation (AKEMD) or authorized distributors as to current status of the products.

AKEMD assumes no liability for infringement of any patent, intellectual property, or other rights in the application or use of any information contained herein.

Any export of these products, or devices or systems containing them, may require an export license or other official approval under the law and regulations of the country of export pertaining to customs and

the law and registrations of the country of export pertaining to customs and tariffs, currency exchange, or strategic materials. AKEMD products are neither intended nor authorized for use as critical components<sub>Note1)</sub> in any safety, life support, or other hazard related device or system<sub>Note2)</sub>, and AKEMD assumes no responsibility for such use, except for the use approved with the express written consent by Representative Director of AKEMD.

Note1) A critical component is one whose failure to function or perform may reasonably be expected to result, whether directly or indirectly, in the loss of the safety or effectiveness of the device or system containing it, and which must therefore meet very high standards of performance and

Note2) A hazard related device or system is one designed or intended for life support or maintenance of safety or for applications in medicine, aerospace, nuclear energy, or other fields, in which its failure to function or perform may reasonably be expected to result in loss of life or in significant injury or

damage to person or property.

It is the responsibility of the buyer or distributor of AKEMD products, who distributes, disposes of, or otherwise places the product with a third party, to notify such third party in advance of the above content and conditions, and the buyer or distributor agrees to assume any and all responsibility and liability for and hold AKEMD harmless from any and all claims arising from the use of said product in the absence of such notification.