Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

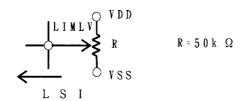

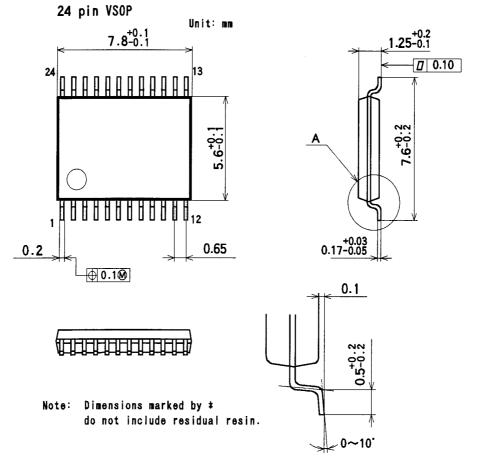

☐ Package: 24 pin VSOP

# AK2361

# Base-band LSI for Cordless Telephones

| Features                                                                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------|

| Built-in voice filter for cordless telephone, MSK MODEM (2400bps) and COMPANDOR Low / wide operation voltage range (1.9 V to 5.5V) |

| Built-in COMPANDOR output transient response circuit and time constant circuit No external component is needed for COMPANDOR       |

| Built-in buffer amplifier for ceramic receiver driving.                                                                            |

| Built-in electronic volume for microphone sensitivity and modulator/demodulator                                                    |

| sensitivity                                                                                                                        |

| Receiving level switchable in 8 steps (-12 to +9dB)                                                                                |

| Built-in muting function for voice transmitting and receiving                                                                      |

| External adjustment for the limiter level                                                                                          |

| Built-in amplifier for transmission and reception gain adjustment                                                                  |

| Low power CMOS and power-down function                                                                                             |

| Built-in 3.58MHz oscillator circuit                                                                                                |

| Built-in frame detection function for the MSK demodulator                                                                          |

| Control register and MSK MODEM data buffer controlled by serial interface                                                          |

| Few external component is necessary resulting cost reduction and small set size.                                                   |

| AK2358/58A pin compatible                                                                                                          |

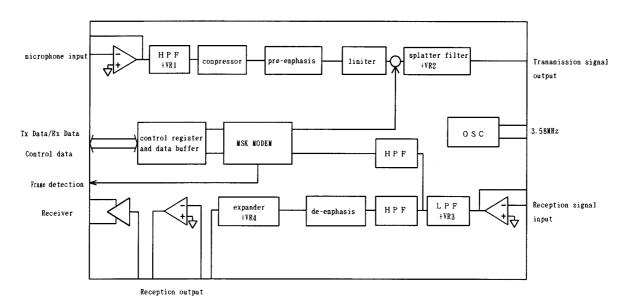

#### Block Diagram

## Description

The AK2361, a base-band LSI for cordless telephone, has built-in voice filters, a 2400bps MSK MODEM for data communication, a frame detection circuit and a COMPANDOR for noise reduction.

The CMOS process provides low power operation. Application of 24 pin VSOP package with the feature of significant reduction of external component provides minimum mounting area. The time constant circuit for the COMPANDOR output transient response is built into the LSI.

Using a 2400bps MSK MODEM for data communication has realized high data reliability and high speed communication at the same time.

This LSI is suitable for cordless system telephones etc. which requires complicated protocol control.

An oscillation circuit with a 3.58MHz crystal oscillator is built in, and no other frequency source is required for the MSK MODEM. The oscillator also can be used for the other DTMF generator etc.

Built-in electronic volumes provided for transmission and reception part realize automatic adjustment of the microphone sensitivity and the modulator/demodulator sensitivity by external EEPROM and microprocessor.

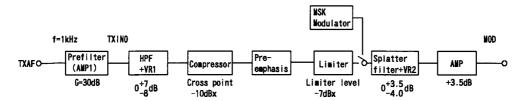

The transmission part is composed of high-pass filter, compressor, pre-emphasis circuit, limiter, MSK modulator, splatter filter, electronic volume control, etc.

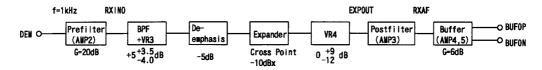

The reception part is composed of band pass filter, de-emphasis circuit, buffer amplifier, expander, MSK demodulator, frame detection circuit, electronic volume control, etc.

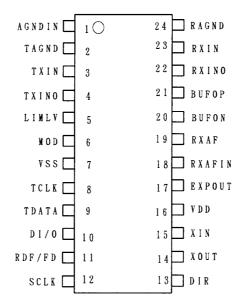

#### Pin Arrangement

24 pin VSOP

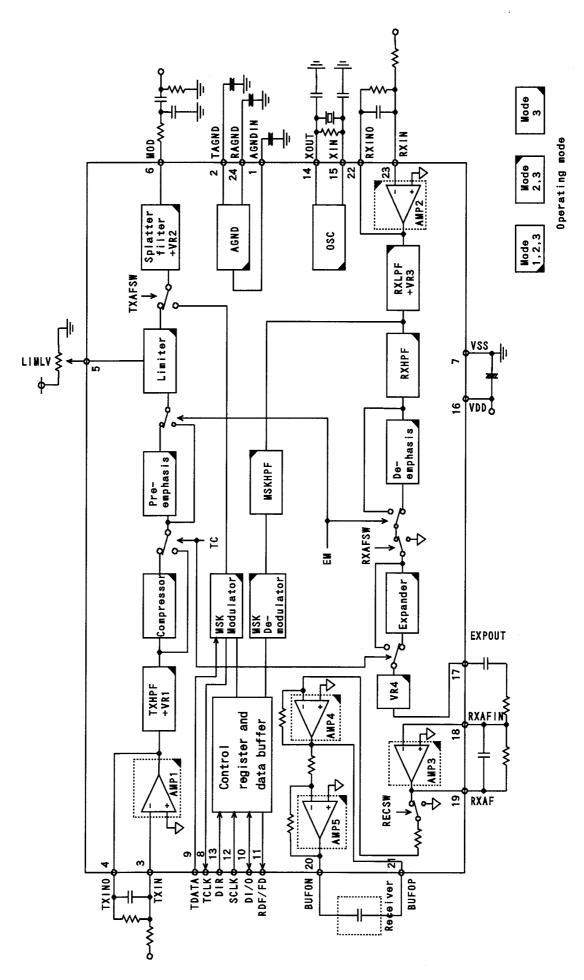

# Circuit Configuration

| Block           | Function                                                           |

|-----------------|--------------------------------------------------------------------|

| AMP1            | The operational amplifier for voice signal transmission gain       |

|                 | adjustment and for the filter to eliminate aliasing noise by the   |

|                 | SCF(switched capacitor filter) in the following stage. Use an      |

|                 | external resistor and capacitor to set the gain less than 30dB and |

|                 | the cut-off frequency to about 10kHz.                              |

| TXHPF           | The SCF circuit to eliminate the low frequency component less      |

|                 | than 300Hz from the transmission voice signal.                     |

| Compressor      | The circuit to compress the amplitude of the transmission voice    |

|                 | signal.                                                            |

| Pre-emphasis    | The circuit to emphasis the high-frequency component of the        |

|                 | transmission voice signal to improve the S/N of the modulation     |

|                 | signal.                                                            |

| Limiter         | The amplitude-limiting circuit to suppress the frequency deviation |

|                 | of the modulation signal. The limitation level can be adjusted by  |

|                 | applying a DC voltage to the LIMLV pin. If the LIMLV pin is open,  |

|                 | the default limitation level is applied.                           |

| Splatter filter | The SCF circuit to eliminate the high frequency component higher   |

|                 | than 3.0kHz from the limiter output signal or the MSK modulator    |

|                 | signal.                                                            |

| MSK modulator   | The circuit to generate a 2400bps MSK signal according to the      |

|                 | received digital signal logic from the TDATA pin.                  |

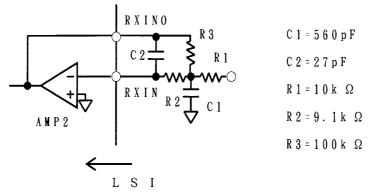

| AMP2            | The operational amplifier to adjust the reception demodulation     |

|                 | signal gain and for the filter to eliminate the aliasing noise of  |

|                 | the SCF in the following stage. Set the gain to less than 30dB     |

|                 | and the cut-off frequency to about 10kHz by external resister and  |

|                 | capacitor.                                                         |

| RXLPF           | The SCF circuit to eliminate the high frequency component higher   |

|                 | than 3.0kHz from the limiter output signal or the MSK modulator    |

|                 | signal.                                                            |

| RXHPF           | The SCF circuit to eliminate the low frequency component lower     |

|                 | than 300Hz from the reception voice signal.                        |

| De-emphasis     | The circuit to de-emphasis the emphasized signal by pre-emphasis   |

|                 | circuit.                                                           |

| Expander        | The circuit to expand the signal amplitude compressed by the       |

|                 | compressor.                                                        |

| Block            | Function                                                          |

|------------------|-------------------------------------------------------------------|

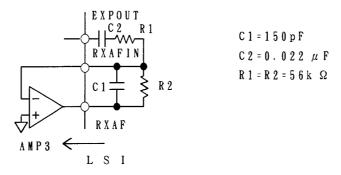

| AMP3             | The operational amplifier used on the smoothing filter of the     |

|                  | reception SCF output. Set the gain to OdB and the cut-off         |

|                  | frequency to about 20kHz by external resister and capacitor.      |

| MSKHPF           | The SCF circuit to eliminate the low frequency component lower    |

|                  | than 100Hz from the reception MSK signal.                         |

| MSK demodulator  | The circuit to reproduce the 2400bps receiving data and the clock |

| ,                | from the received MSK signal in the RXIN pin.                     |

| AMP4             | The inverting and the non-inverting buffer amplifier to drive the |

| AMP5             | ceramic receiver.                                                 |

| AGND             | The circuit to generate the reference voltage for the internal    |

|                  | analog signal.                                                    |

| Oscillation      | The circuit to oscillate the 3.58 MHz reference clock using an    |

| circuit          | external crystal oscillator and resistor.                         |

| VR1              | The volume to control the input amplitude of the transmission     |

|                  | voice signal. The adjustment range is -8dB to +7dB by 1dB step.   |

| VR2              | The volume to control the MOD output amplitude. The adjustment    |

|                  | range is -4dB to +3.5dB by 0.5dB step.                            |

| VR3              | The volume to control the input amplitude of the reception        |

|                  | demodulation signal. The adjustment range is -4dB to +3.5dB by    |

|                  | 0.5dB step.                                                       |

| VR4              | The volume to control the receiving voice amplitude. The          |

|                  | adjustment range is -12dB to +9dB by 3dB step.                    |

| Control register | The control register controls the status of internal switches and |

| and data buffer  | internal volumes of the LSI by serial data consists of 2 address  |

|                  | bits and 8 data bits. At the start up a power-on-reset circuit    |

|                  | works and the default values are set to the control register.     |

|                  | (see control register map.)                                       |

|                  | The data buffer stores 8 bits of the MSK receiving data to smooth |

|                  | the signal interface with CPU.                                    |

# Pin/Function

| Pin No. | Pin name | I/O | Function                                              |

|---------|----------|-----|-------------------------------------------------------|

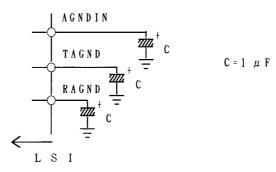

| 1       | AGNDIN   | I   | Analog ground input pin.                              |

|         |          |     | Connect the capacitor to stabilize the analog ground. |

| 2       | TAGND    | 0   | Analog ground pin for the transmission system.        |

|         | INUND    |     |                                                       |

|         |          |     | Connect the capacitor to stabilize the analog         |

|         |          |     | ground.                                               |

| 3       | TXIN     | I   | Transmission voice input pin.                         |

|         |          |     | This is the inverting input pin for AMP1. It          |

|         |          |     | composes a microphone amplifier with a external       |

|         |          |     | resister and a capacitor.                             |

| 4       | TXINO    | 0   | AMP1 output pin.                                      |

| 5       | LIMLV    | I   | Limitation level adjustment pin.                      |

|         |          |     | The limitation level can be adjusted by applying a    |

|         |          |     | DC voltage to this pin. The default limitation level  |

|         |          |     | is adopted if no voltage is applied.                  |

| Pin No.         | Pin name        | I / O | Function                                                        |

|-----------------|-----------------|-------|-----------------------------------------------------------------|

| 6               | MOD             | 0     | Output pin of the modulated transmission signal.                |

| LIMITE          |                 |       | A load impedance larger than $10k\Omega$ can be driven.         |

| . 7             | VSS             |       | Negative power supply pin.                                      |

| 8               | TCLK            | 0     | Clock output pin for the MSK data transmission.                 |

|                 |                 |       | A 2.4kHz clock is put out by setting the internal               |

|                 |                 |       | register TDE to "0". If the register is set to "1",             |

|                 |                 |       | it goes "H" level.                                              |

| 9               | TDATA           | I     | MSK transmission data input pin.                                |

|                 |                 |       | Data are latched synchronizing with the TCLK rising             |

|                 |                 |       | edge.                                                           |

| 1 0             | DI/O            | I / O | Serial data input and output pin.                               |

| 1 1             | RFD/FD          | 0     | MSK signal reception flag output and Frame detection            |

|                 |                 |       | signal output pin.                                              |

|                 |                 |       | This pin puts out two types of information,                     |

|                 |                 |       | depending on the status of the internal register                |

|                 |                 |       | FSL. If FSL is "1", it is MSK signal reception mode,            |

|                 |                 |       | so the pin reaches low after 8 bits of the MSK                  |

|                 |                 |       | reception signal have been written to the data                  |

|                 |                 |       | register. If FSL is "0", it is the frame detection              |

|                 |                 |       | signal output mode, so the low pulse is put out                 |

| 1.0             | OCLV            | T     | after a frame pattern is detected.                              |

| 1 2             | SCLK            | I     | Clock input pin for serial data I/O.                            |

| $\frac{13}{14}$ | DIR<br>XOUT     | I     | Serial data I/O control pin. Crystal oscillator connection pin. |

| 1 4             | A001            | 1     | The reference clock IC is generated by connecting a             |

|                 |                 |       | 3.58MHz crystal oscillator parallel to a $1M\Omega$             |

|                 |                 |       | resistor between this pin and XIN pin. In case of               |

|                 |                 |       | external clock operation, connect XOUT pin to VSS               |

|                 |                 |       | and apply the clock to XIN.                                     |

| 1 5             | XIN             | 0     | Crystal oscillator connection pin.                              |

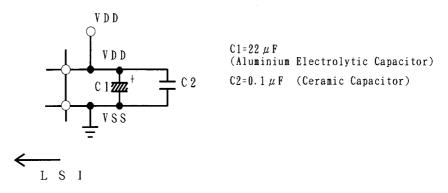

| 1 6             | VDD             | _     | Positive power supply pin.                                      |

| 1 7             | EXP <b>O</b> UT | 0     | Expander output pin.                                            |

| 1 8             | RXAFIN          | I     | Reception voice input pin.                                      |

|                 |                 |       | This is the inverting input of AMP3. It composes a              |

|                 |                 |       | smoothing filter by external resistor and capacitor.            |

| 1 9             | RXAF            | 0     | Reception voice output pin.                                     |

|                 |                 |       | This is the output pin of AMP3. A load impedance                |

|                 |                 |       | more than $10k\Omega$ can be driven.                            |

| 2 0             | BUF <b>O</b> N  | О     | Receiver amplifier output pins.                                 |

| 2 1             | BUFOP           | 0     | Connect the ceramic receiver between these two pins.            |

| 2 2             | RXINO           | 0     | AMP2 output pin.                                                |

| 2 3             | RXIN            | I     | Demodulated receiving signal input pin.                         |

|                 |                 |       | This is the inverting input of AMP2. It composes a              |

|                 |                 |       | prefilter with external resistor and capacitor.                 |

| 2 4             | RAGND           | 0     | Analog ground pin for the reception system.                     |

|                 |                 |       | Connect the capacitor to stabilize analog ground.               |

# Absolute Maximum Ratings

VSS=0V; Note 1)

| Parameter                                    | Symbol | min  | max       | Unit         |

|----------------------------------------------|--------|------|-----------|--------------|

| Power supply voltage: (VDD)                  | VA+    | -0.3 | 6.5       | V            |

| Input current (except the power supply pins) | IIN    | -    | ± 10      | mA           |

| Analog input voltage                         | VINA   | -0.3 | (VA+)+0.3 | V            |

| Digital input voltage                        | VIND   | -0.3 | (VA+)+0.3 | V            |

| Storage temperature                          | Tstg   | -55  | 130       | $^{\circ}$ C |

Note 1): All voltages with respect to the VSS pin.

Warning: Operation at or beyond these limits may result in permanent damage to the device.

Normal operation is not guaranteed at these extremes.

#### Recommended Operating Conditions

VSS=0V; Note 1)

| Parameter             |        | Symbol | min  | typ    | max  | Unit |

|-----------------------|--------|--------|------|--------|------|------|

| Operation temperature |        | Ta     | -10  |        | 70   | °C   |

| Power supply voltage: | (VDD)  | VD+    | 1. 9 | 2. 0   | 5. 5 | V    |

| Analog reference volt | age    | AGND   |      | 1/2VD+ |      | V    |

| Current consumption   | Mode 0 | Idd0   |      | 0.1    | 0.8  | mA   |

|                       | Mode 1 | Idd1   |      | 0.9    | 1.9  |      |

|                       | Mode 2 | Idd2   |      | 1.5    | 2.9  |      |

|                       | Mode 3 | I dd3  |      | 5.0    | 10   |      |

Note 1): All voltages with respect to the VSS pin.

# Analog Characteristics

f=1kHz, TC="1", EM="1", VR1 to VR4=0dB:unless otherwise specified,

0dBm=0.775Vrms

0dBx=-5dBm at AVDD=2V Note 8)

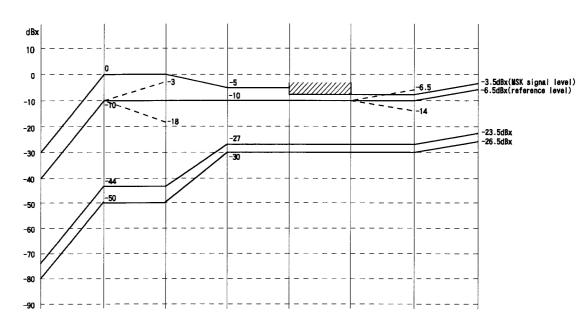

## 1) TX system

| Para                  | meter                | min   | typ   | max    | Unit  |

|-----------------------|----------------------|-------|-------|--------|-------|

| Standard input level  | @TX INO              |       | -10   |        | dBx   |

| Absolute gain         | TXINO→MOD Note 1)    | 2. 0  | 3. 5  | 5.0    | dB    |

| Limiter level         | MOD 1kHz Note 1)     |       |       |        |       |

|                       | No external R        | -4.5  | -3.5  | -2.5   | יימף. |

|                       | Adjustment range by  |       |       | -2.5   | dBx   |

|                       | external R           |       |       |        |       |

| Compressor linearity  | TXINO→MOD Note 1) 2) |       |       |        |       |

|                       | TXINO=-44dBx         | -20   | -17.0 | -14    | dB    |

|                       | TXIN0=-50dBx         | -24   | -20.0 | -16    |       |

| Noise without input   | TXINO→MOD Note 1) 3) |       |       | -36.5  | dBm   |

| Compressor distortion | TXINO→MOD            |       |       | -35    | dB    |

|                       | TXIN0=-10dBx         |       |       | - 50   | uБ    |

| Transmission MSK      | @MOD Note 1)         | -4.5  | -3.5  | -2.5   | dBx   |

| signal level          | 1.2kHz signal output | -4. J | ე. ე  | - 4. 0 | UDX   |

| Transmission MSK      | @MOD Note 1)         |       |       | -32    | dB    |

| signal distortion     | 1.2kHz signal output |       |       | J.L    | uр    |

#### 2) RX system

| Para                          | ameter                             | min            | typ              | max              | Unit |

|-------------------------------|------------------------------------|----------------|------------------|------------------|------|

| Standard input level          | @RX INO                            |                | -10              |                  | dBx  |

| Absolute gain                 | RXINO→BUFON, BUFOP<br>Note 1)      | -1.5           | 0                | +1.5             | dB   |

| Expander linearity            | RXINO→BUFON, BUFOP<br>Note 1) 4)   |                |                  |                  |      |

|                               | RX I NO=-25 dBx<br>RX I NO=-30 dBx | -33.0<br>-45.0 | -30. 0<br>-40. 0 | -27. 0<br>-35. 0 | dB   |

| Noise with no input           | RXINO→BUFON, BUFOP<br>Note 1) 3)   |                |                  | -70              | dBm  |

| Expander distortion           | RXINO→RXAF<br>RXINO=-5dBx          |                |                  | -35              | dB   |

| Reception MSK<br>signal level | @RXINO<br>1.2kHz signal output     | -14            | -7               | -1               | dBx  |

#### 3) Overall characteristics

|              | Parameter              |            | min  | typ | max   | Unit |

|--------------|------------------------|------------|------|-----|-------|------|

| Absolute gai | n TXINO→BUFON, BUFOP   | Note 5)    | -0.5 | 0   | +2.5  | dB   |

|              | TXINO = -10dBx         |            |      |     |       |      |

| Distortion   | TXINO→BUFON, BUFOP     | Note 3) 5) |      | -50 | -43   | dB   |

|              | TX I N 0 = - 1 0 d B x |            |      |     |       |      |

| Crosstalk    | @BUFON, BUFOP          | Note 1) 6) |      |     |       |      |

| Transmission | n → Reception          |            |      |     | -60   | dBx  |

|              | TXINO=0dBx TC=         | 0"         |      |     |       |      |

| Crosstalk    | @MOD                   | Note 1) 6) | ·    |     |       |      |

| Reception →  | · Transmission         |            |      |     | -56.5 | dBx  |

|              | RXINO=0dBx $TC=$       | 0"         |      |     |       |      |

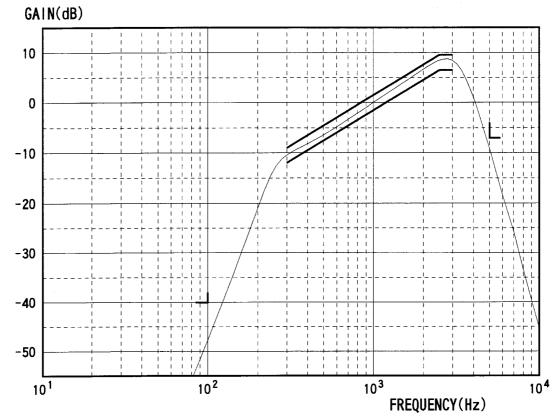

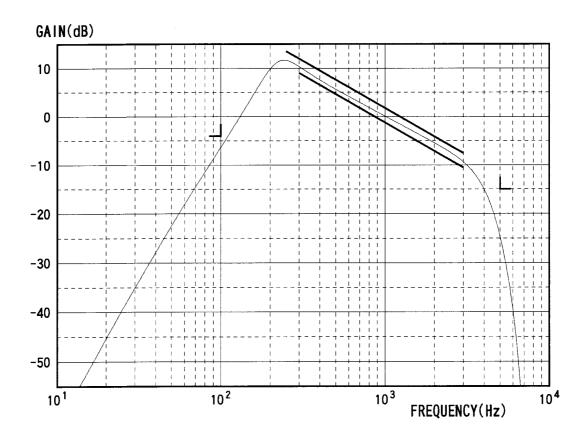

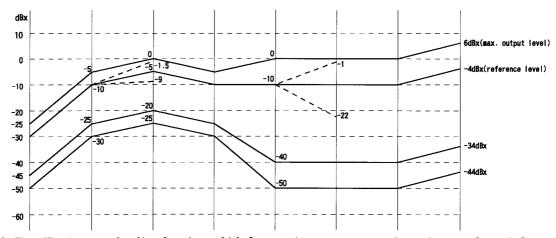

#### 4) Filter characteristics

| Parameter                               |            | min   | typ   | max  | Unit |

|-----------------------------------------|------------|-------|-------|------|------|

| Transmission overall characteristics (S | ee Fig. 1) |       |       |      |      |

| TXINO → MOD                             | 100Hz      |       | •     | -40  |      |

| TC="0" EM="1"                           | 300Hz      | -12   | -10.5 | -9   |      |

| Relative value with OdB gain            | 2.5kHz     | 6.5   | 8     | 9.5  | dB   |

| at 1kHz                                 | 3kHz       | 6.5   | 8     | 9. 5 |      |

|                                         | 5kHz       |       |       | -7   |      |

| Reception overall characteristics (See  | Fig. 2)    |       |       |      |      |

| RXINO → EXPOUT                          | 100Hz      |       |       | -4   |      |

| TC="0" EM="1"                           | 250Hz      |       | 12    | 13.5 |      |

| Relative value with OdB gain            | 300Hz      | 9     | 10.5  |      | dB   |

| at lkHz                                 | 3kHz       | -10.5 | -9    | -7.5 |      |

|                                         | 5kHz       |       |       | -15  |      |

- Note 1) With the external circuit shown in the application circuit example.

- Note 2) Relative value with OdB as the MOD output level at the time of input of standard input level (-10dBx) to TXINO.

- Note 3) With the C-message filter.

- Note 4) Relative value with OdB as the BUFON, BUFOP output level at the time of input of standard input level (-10dBx) to RXINO.

- Note 5) With the external circuit shown in the application circuit example. Further, the AMP2 gain should be -3.5dB, and MOD and RXIN should be in loop connection.

- Note 6) TC="0"

- Note 7) The dBx is standardized unit valid for various power supply voltages from 1.9 to 5.5V. If the voltage is 2V, 0dBx should be -5dBm. With the other voltage as X [V],  $0dBx = -5 + 20 \log (X/2) [dBm]$ .

ASAHI KASEI

#### ☐ Filter characteristics

Fig. 1 Transmission overall characteristics

Fig. 2 Reception overall characteristics

#### Level Diagram

#### 1) TX system

#### 2) RX system

Note) The dBx is standardized unit valid for various power supply voltages from 1.9 to 5.5V. If the voltage is 2V, 0dBx should be -5dBm. With the other voltage as X [V],  $0dBx = -5 + 20 \log (X/2) [dBm]$ .

1997/12

ASAHI KASEI

# Digital Characteristics

## 1. DC Characteristics

| Parameter                                     | Pin    | Symbol           | min    | typ | max    | Unit |

|-----------------------------------------------|--------|------------------|--------|-----|--------|------|

| High-level input voltage 1                    | (1)    | V <sub>IH1</sub> | 70%VD+ |     |        | V    |

| Low-level input voltage 1                     | (1)    | V 1 L 1          |        |     | 30%VD+ | V    |

| High-level input voltage 2                    | (2)    | V 1 H 2          | 80%VD+ |     |        | V    |

| Low-level input voltage 2                     | (2)    | V 1 L 2          |        |     | 20%VD+ | V    |

| High-level input current V <sub>IH</sub> =VD+ | (1)(2) | IIH              |        |     | 10     | μΑ   |

| Low-level input current V <sub>1L</sub> =0V   | (1)(2) | IIL              | -10    |     |        | μΑ   |

| High-level output voltage IoH=0.1mA           | (3)    | V <sub>он</sub>  | 90%VD+ |     |        | V    |

| Low-level output voltage Iol=0.6mA            | (3)    | Vol              |        |     | 0.3    | V    |

- (1) TDATA, DI/0

- (2) SCLK, DIR

- (3) TCLK, RDF, DI/O

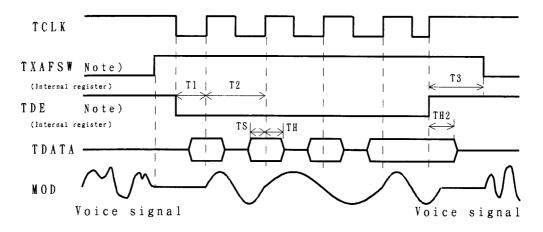

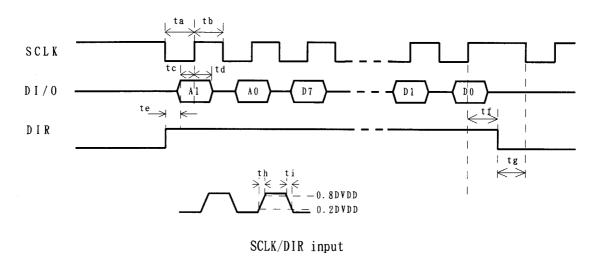

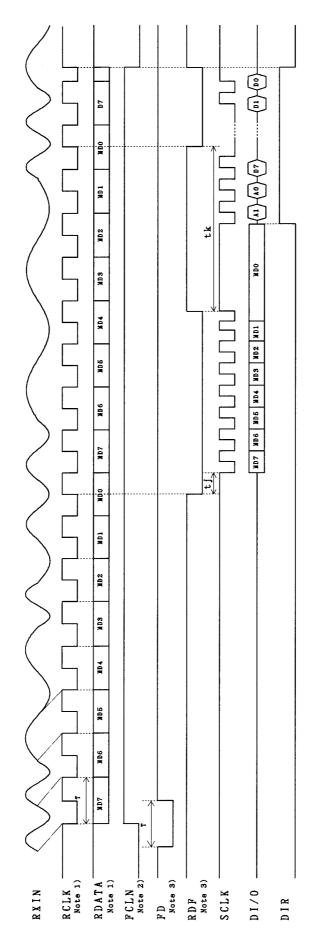

## 2. AC Characteristics

| Parameter                        | Symbol | min   | typ      | max | Unit |

|----------------------------------|--------|-------|----------|-----|------|

| Master clock frequency           | fclk   | •**   | 3.579545 | :   | MHz  |

| MSK Modulator timing             |        |       |          |     |      |

| TDE Falling to TCLK Rising       | T1     |       | 208. 3   |     | μs   |

| TCLK period                      | T2     |       | 416.7    |     | μs   |

| TDE Rising to TXAFSW Falling     | Т3     | 2     |          |     | ms   |

| TDATA Set up time                | TS     | 1     |          |     | μs   |

| TDATA Hold time                  | TH     | 1     |          |     | μs   |

| TDATA Hold time2                 | TH2    | 2     |          |     | μs   |

| MSK Demodulator timing           |        |       |          |     |      |

| RCLK Period & FD pules width     | T      | 402.2 | 416. 7   |     | μs   |

| Serial data input timing         |        |       |          |     |      |

| Clock pulse width 1              | ta     | 500   |          |     | ns   |

| Clock pulse width 2              | tb     | 500   |          |     | ns   |

| SDATA Set Up time                | tc     | 100   |          |     | ns   |

| SDATA Hold time                  | td     | 100   |          |     | ns   |

| DIR Set up time                  | te     | 100   |          |     | ns   |

| DIR Hold time                    | tf     | 100   |          |     | ns   |

| DIR falling to SCLK falling time | tg     | 100   |          |     | ns   |

| SCLK/DIR input rising time       | th     |       |          | 1   | μs   |

| SCLK/DIR input falling time      | ti     |       |          | 1   | μs   |

| RDF falling to SCLK falling time | tj     | 100   |          |     | ns   |

| SCLK rising to RDF falling time  | tk     | 600   |          |     | ns   |

ASAHI KASEI

MSK modulator

Note) The timing to rewrite the internal registers TXAFSW and TDE is synchronized with the falling edge of DIR.

Note 1) Internal node Note 2) Internal register Note 3) If the internal register FSL is "O", the status of "FD" is put out to the RFD/FD pin. If the FCL is "1", the status of "RFD" is put out.

MSK demodulator

## Control Register Map

#### ■ Register composition

|                                      | Addr | ess |                          | Data             |     |      |       |     |             |             |

|--------------------------------------|------|-----|--------------------------|------------------|-----|------|-------|-----|-------------|-------------|

|                                      | A 1  | A 0 | D 7                      | D 6              | D 5 | D 4  | D 3   | D 2 | D 1         | D 0         |

| Control register 1                   | 0    | 0   | FSL                      | BS2              | BS1 | FCLN | -     | TDE | TXAF<br>-SW | RXAF<br>-SW |

| Volume register                      | 0    | 1   | 1                        | 1                | 1   | 1    | RECSW |     | V R 4       |             |

| Volume register                      | 1    | 0   |                          | V ]              | R 2 | **** |       | V R | 1           |             |

| Control register 2 + volume register | 1    | 1   | TC                       | TC EM FRPT - VR3 |     |      |       |     |             |             |

| Reception data register              |      |     | MSK MODEM reception data |                  |     |      |       |     |             |             |

The reception data register is a read only register, and the others are write only registers.

The reception data register has no address information proceeding to the Data. Set the bits D4 to D7 of volume register address "01" to all "1". If they are set to except all "1", it is changed to test mode. Do not use this test mode. If the bit D3 of address "00" and D4 of address "11" is written either "0" or "1", setting of AK2361 is not changed.

#### Register map

#### 1) Control register 1

| Addr  | ess  | Data |     |     |      |     |     |        |        |

|-------|------|------|-----|-----|------|-----|-----|--------|--------|

| A 1   | A 0  | D 7  | D 6 | D 5 | D 4  | D 3 | D 2 | D 1    | D 0    |

| 0     | 0    | FSL  | BS2 | BS1 | FCLN | -   | TDE | TXAFSW | RXAFSW |

| (Defa | ult) | 1    | 1   | 0   | 0    | _   | 1   | 0      | 0      |

#### a) Transmission signal control

| TDE | TXAFSW | Transmission output |

|-----|--------|---------------------|

| 1   | 0      | Voice signal        |

| 1   | 1      | Mute                |

| 0   | 1      | MSK signal          |

#### b) Reception signal control

| RXAFSW | RECSW | RXAF | BUFOP/BUFON |

|--------|-------|------|-------------|

| 1      |       | Mute | Mute        |

| 0      | 1     | ON   | Mute        |

| 0      | 0     | ON   | ON          |

## c ) Frame detection circuit 0N/0FF

| FCLN |                                                 |

|------|-------------------------------------------------|

| 1    | The frame detection function is not used (OFF). |

| 0    | The frame detection function is used (ON).      |

Note) FCLN automatically changes from 0 to 1 when a synchronized frame is detected.

## d) Power-down mode

| BS2 | BS1 | Mode name | Voice system +<br>transmission MSK | Reception MSK | 0scillator |

|-----|-----|-----------|------------------------------------|---------------|------------|

| 1   | 1   | mode0     | OFF                                | OFF           | OFF        |

| 0   | 1   | mode1     | OFF                                | OFF           | O N        |

| 1   | 0   | mode2     | OFF                                | O N           | O N        |

| 0   | 0   | mode3     | O N                                | O N           | O N        |

#### e ) RDF/FD selection

| FSL |                                                                     |

|-----|---------------------------------------------------------------------|

| 1   | The MSK signal reception flag (RDF) is put out from the RDF/FD pin. |

| 0   | The frame detection signal (FD) is put out from the RDF/FD pin.     |

#### 2) Control register 2

| Addr  | ess  | Data |     |      |     |     |     |     |     |

|-------|------|------|-----|------|-----|-----|-----|-----|-----|

| A 1   | A 0  | D 7  | D 6 | D 5  | D 4 | D 3 | D 2 | D 1 | D 0 |

| 1     | 1    | TC   | EM  | FRPT | -   |     | VR  | 3   |     |

| (Defa | ult) | 1    | 1   | 0    | _   | 1   | 0   | 0   | 0   |

| Data name | Function                         |                                       |  |  |  |  |  |  |

|-----------|----------------------------------|---------------------------------------|--|--|--|--|--|--|

| FRPT      | Frame detector detection pattern | "1": 1100010011010110 (base unit)     |  |  |  |  |  |  |

|           |                                  | "0": 1001001100110110 (portable unit) |  |  |  |  |  |  |

| ΕM        | Emphasis circuit                 | "1": Passage (ON)                     |  |  |  |  |  |  |

|           |                                  | "0": Bypass (OFF)                     |  |  |  |  |  |  |

| ТС        | COMPANDOR circuit                | "1": Passage (ON)                     |  |  |  |  |  |  |

|           |                                  | "0": Bypass (OFF)                     |  |  |  |  |  |  |

## 3) Volume register

| Addr | ess | Data |      |      |      |       |      |      |      |

|------|-----|------|------|------|------|-------|------|------|------|

| A 1  | A 0 | D 7  | D 6  | D 5  | D 4  | D 3   | D 2  | D 1  | D 0  |

| 0    | 1   | 1    | 1    | 1    | 1    | RECSW | VR42 | VR41 | VR40 |

| 1    | 0   | VR23 | VR22 | VR21 | VR20 | VR13  | VR12 | VR11 | VR10 |

| 1    | 1   | TC   | EM   | FRPT |      | VR33  | VR32 | VR31 | VR30 |

# a) VR1 volume control

| VR13 | VR12 | VR11 | VR10 | Volume gain (dB) |

|------|------|------|------|------------------|

| 0    | 0    | 0    | 0    | -8.0             |

| 0    | 0    | 0    | 1    | -7.0             |

| 0    | 0    | 1    | 0    | - <b>6</b> . 0   |

| 0    | 0    | 1    | 1    | -5.0             |

| 0    | 1    | 0    | 0    | -4.0             |

| 0    | 1    | 0    | 1    | - 3. 0           |

| 0    | 1    | 1    | 0    | -2.0             |

| 0    | 1    | 1    | 1    | -1.0             |

| 1    | 0    | 0    | 0    | 0                |

| 1    | 0    | 0    | 1    | +1.0             |

| 1    | 0    | 1    | 0    | + 2. 0           |

| 1    | 0    | 1    | 1    | + 3. 0           |

| 1    | l 1  | 0    | 0    | + 4. 0           |

| 1    | 1    | 0    | 1    | + 5. 0           |

| 1    | 1    | 1    | 0    | +6.0             |

| 1    | 1    | 1    | 1    | +7.0             |

# b) VR2, VR3 volume control

| VR23 | VR22 | VR21 | VR20 | Volume main (dD) |

|------|------|------|------|------------------|

| VR33 | VR32 | VR31 | VR30 | Volume gain (dB) |

| 0    | 0    | 0    | 0    | -4.0             |

| 0    | 0    | 0    | 1    | - 3. 5           |

| 0    | 0    | 1    | 0    | - 3. 0           |

| 0    | 0    | 1    | 1    | - 2. 5           |

| 0    | 1    | 0    | 0    | - 2. 0           |

| 0    | 1    | 0    | 1    | -1.5             |

| 0    | 1    | 1    | 0    | -1.0             |

| 0    | 1    | 1    | 1    | - 0. 5           |

| 1    | 0    | 0    | 0    | 0                |

| 1    | 0    | 0    | 1    | + 0. 5           |

| 1    | 0    | 1    | 0    | + 1. 0           |

| 1    | 0    | 1    | 1    | + 1. 5           |

| 1    | 1    | 0    | 0    | + 2. 0           |

| 1    | 1    | 0    | 1    | + 2. 5           |

| 1    | 1    | 1    | 0    | + 3. 0           |

| 1    | 1    | 1    | 1    | + 3. 5           |

#### c) VR4 volume control

| VR42 | VR41 | VR40 | Volume gain (dB) |

|------|------|------|------------------|

| 0    | 0    | 0    | -12              |

| 0    | 0    | 1    | <b>- 9</b>       |

| 0    | 1    | 0    | <u> </u>         |

| 0    | 1    | 1    | - 3              |

| 1    | 0    | 0    | 0                |

| 1    | 0    | 1    | + 3              |

| 1    | 1    | 0    | + 6              |

| 1    | 1    | 1    | + 9              |

Note) By reset, the gain of all volumes are set to 0dB and RECSW bit is changed to "0".

## 4) MSK MODEM reception data

| Data |     |     |     |     |     |     |     |

|------|-----|-----|-----|-----|-----|-----|-----|

| D 7  | D 6 | D 5 | D 4 | D 3 | D 2 | D 1 | D 0 |

| RD7  | RD6 | RD5 | RD4 | RD3 | RD2 | RD1 | RD0 |

| Data name |                                 | Function   |  |

|-----------|---------------------------------|------------|--|

| RD0       | MSK reception data              | "1":1.2kHz |  |

| } }       |                                 | "0":2.4kHz |  |

| R D 7     | RD7 is the first received data. |            |  |

#### MSK Modem

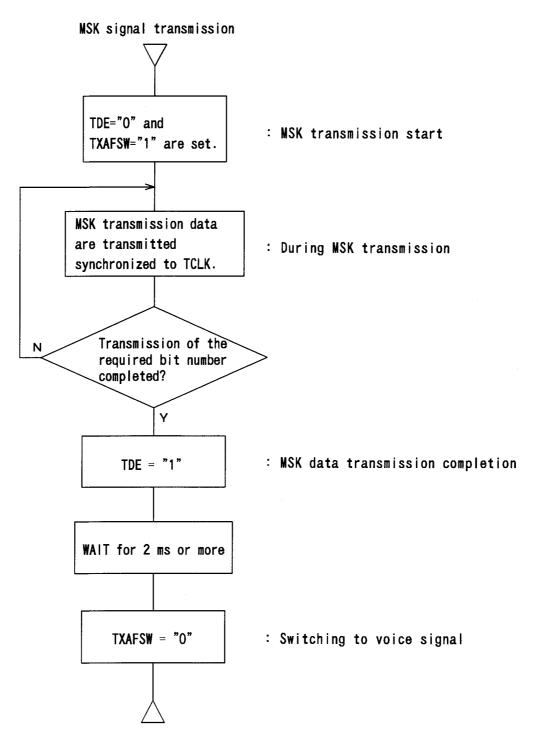

MSK signal transmission flow

- (1) Set the serial register "TDE" to "0" and "TXAFSW" to "1", so that MSK transmission state is provided.

- (2) A 2400Hz clock is put out from TCLK. Synchronizing with the rising edge of TCLK, AK2361 reads the MSK transmission data from TDATA pin and put out them to MOD pin.

- (3) After the transmission of the necessary number of signal bit, "TDE" of the serial register is set to "1".

- (4) Afterwards, before switching to a voice signal transmission mode, wait at least 2ms after "TDE" has set to "1" to complete the MSK signal final bit transmission. Then set TXAFSW register to "0".

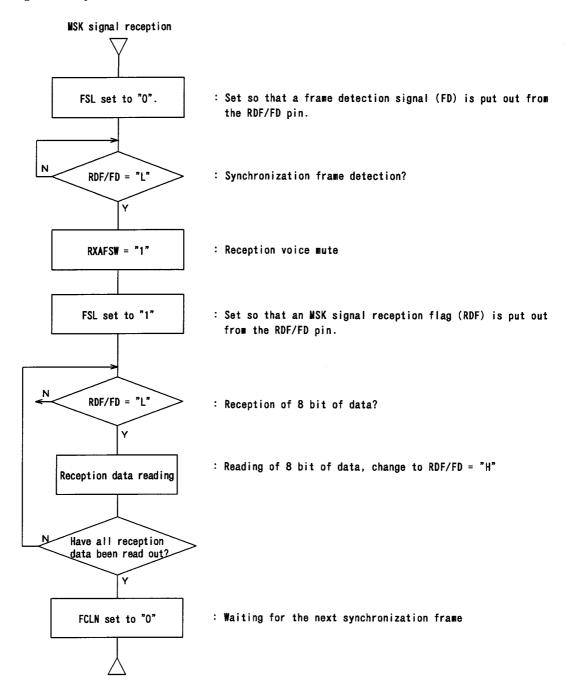

#### MSK Signal Reception

- (1) If the internal register "FCLN" is "O", the internal nodes RDATA, RCLK are fixed to

- (2) After a synchronization frame is detected, FD goes to "L" during the period "T", then FCLN is set to "1".

- (3) RDATA and RCLK put out the data following to the synchronized frame pattern, and these are stored in the internal buffer.

- (4) After 8 bit of reception data have been entered to the internal buffer, RDF goes "L".

(5) After the CPU detect that RDF is "L", it puts out 8 clock bits to SCLK, then read 8 bit of reception data from the DI/O pin.

- (6) With input of 8 clock bits to SCLK, RDF goes "H".(7) Afterwards, by repeating the steps (4) and (5) the necessary data bits are read.

- (8) After the necessary data have been read, DIR goes "H", "FCLN" is set to "O" via the serial interface, the internal nodes RDATA and RCLK are set to "1", then the system waits for the next synchronization frame.

## Application Circuit Example

#### ■Application Circuit

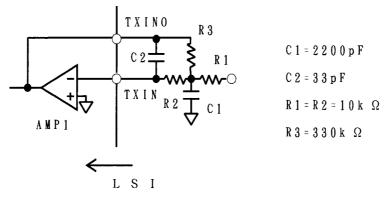

#### OAMP1

Use as a transmitting microphone amplifier. The gain should be less than 30dB. To eliminate high frequency noise component over than 100kHz from input signal, 1st order or 2nd order anti-aliasing filter is necessary. The following drawing is one example of the 2nd order anti-aliasing filter, which has 30dB gain and 10kHz cut-off frequency.

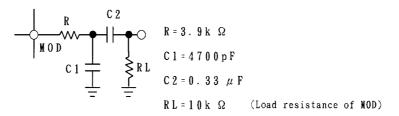

#### Smoothing filter for MOD output signal

Realize low-pass filter to eliminate 112kHz clock signal component from MOD pin output signal. The following is one example of the 1st order low-pass filter which has 8.7kHz cut-off frequency.  $10k\,\Omega$  of the modulator load resistor(RL) provide 3.3dB signal attenuation.

#### OAMP 2

The amplifier for the receiving gain adjustment and anti-aliasing filtering to eliminate high frequency noise component over 100kHz. The gain should be less than 30dB. The following is an example of the 2nd order low pass filter, which has 20 dB gain and 40kHz cut-off frequency.

#### OAMP3

The smoothing filter to eliminate 448kHz clock component from EXPOUT signal is provided by this amplifier. Also it works to adjust the receiving gain. Adding the other pass signal may be possible. The following is one example of the 1st order low-pass filter, which has 0dB gain , 19kHz cut-off frequency.

####

To stabilize the AGND potential, connect capacitors larger than 0.3  $\mu$ F between TAGND pin, RAGND pin and AVSS pin. Also between AGNDIN pin and AVSS pin some capacitor is necessary to reduce the ripple of the power.

#### ○VDD stabilizing capacitor

To reduce the noise on YDD, connect capacitors between YDD and VSS.

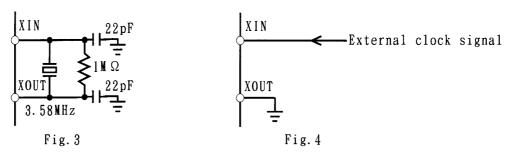

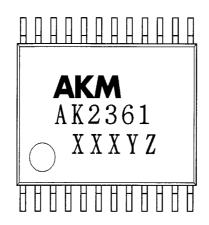

#### OCrystal oscillator

- Crystal resonator, resistor and capacitors should be connected as shown Fig. 3 for on-chip oscillator operation.

- For external clock operation, if the high(H) level of the input clock signal amplitude equals to or is greater than 1.5V, and the low(L) level equals to or is smaller than 0.5V, then connection should be made as shown in Fig. 4. If the input clock signal amplitude (peak-to-peak) equals to or is smaller than 1V, and equals to or is greater than 200mV, then AC coupling should be as illustrated in Fig. 5.

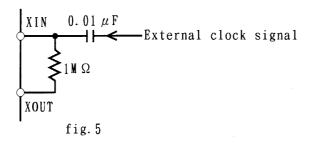

#### OLimit level adjusting resistor

The limiting level can be controlled externally by applying DC voltage to LIMIV pin. Applied DC voltage should be larger than TAGND, then the limiting level is shown as  $TAGND \pm Va(V)$ , while Va is the voltage between LIMIV and TAGND. Keeping LIMIV pin open provides default limit level. See following example.

#### Package

Marking

[Contents of XXXYZ]

XXX: Date of manufacture

Last digit of the year, week number of the year as 2 digits

Y: Production lot number

Z: Assembled place

■ Shape and dimensions of the package

Detail of part A

[Material] Resin: Low-stress type epoxy resin

Lead frame: Cu