# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Asahi**KASEI**

## AK2363

## Radio Signaling LSI

### **Features**

- DTMF Receiver including an AGC circuit

- □ Built-in MSK modem allowing selection from 1200 and 2400 bit/s

- □ Programmable modem frame detection pattern

- □ Built-in 3.6864MHz oscillator circuit

- Support of external clocks with frequencies twice, three times, and four times higher than 3.6864MHz

- □ Operating voltage range: 2.6V to 3.7V

- □ Operating temperature range: -40°C to +85°C

- □ Package: 24-pin QFNJ (4.0 x 4.0 x 0.75mm, 0.5mm pitch)

#### Overview

The AK2363 is a radio signaling LSI device into which an MSK modem and a DTMF Receiver are integrated on a single chip.

The MSK modem supports 1200 and 2400 bit/s, and the demodulator has a 16-bit frame pattern detection function that allows any settings. When the signal-to-noise (S/N) ratio is 12dB, the BER characteristic at 1200 bit/s is 5.0E-06, and the BER characteristic at 2400 bit/s is 1.0E-04.

The DTMF Receiver operates in two modes: Normal mode (AGD Disable) indicating input signal detection levels ranging from -27dBx to 0dBx and high sensitivity mode (AGC Enable) in which the receiver operates at –40dBx to 0dBx.

In addition to a fundamental frequency of 3.686MHz, the oscillator circuit supports external clock input with frequencies of 7.3728MHz (twice higher than 3.6864MHz), 11.0592MHz (three times higher than 3.6864MHz), and 14.7456MHz (four times higher than 3.6864MHz).

The internal operation is controlled by the three-wire serial method in which serial input data (SDATA) consisting of a 1-bit instruction, a 4-bit address, and 8-bit data is set in synchronization with the CSN and SCLK signals.

The 24-pin QFNJ package (4.0mm  $\times$  4.0mm) is employed to realize compact, high-density packaging.

## Contents

| Features1                             |

|---------------------------------------|

| Overview1                             |

| Contents 2                            |

| Block Diagram3                        |

| Pin Assignments3                      |

| Block Functions                       |

| Pin Functions                         |

| Absolute Maximum Ratings7             |

| Recommended Operating Conditions7     |

| Digital DC Characteristics7           |

| Clock Input Characteristics           |

| System Reset8                         |

| Current Consumption9                  |

| Analog Characteristics10              |

| Digital AC Timing11                   |

| Register Functions 17                 |

| MSK Modem Operation                   |

| DTMF Receiver Operation               |

| Recommended External Circuit Examples |

| Package                               |

| Important Notice                      |

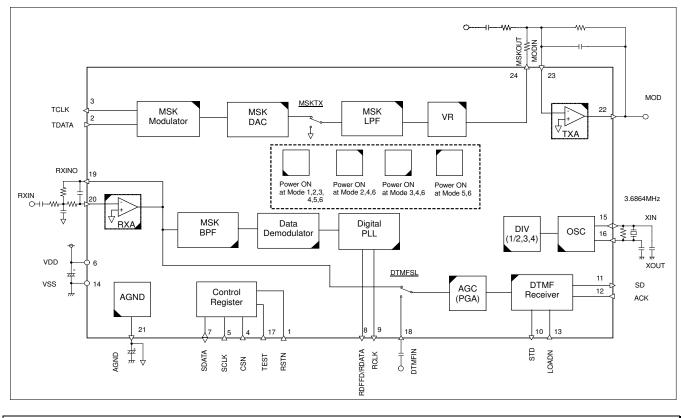

## **Block Diagram**

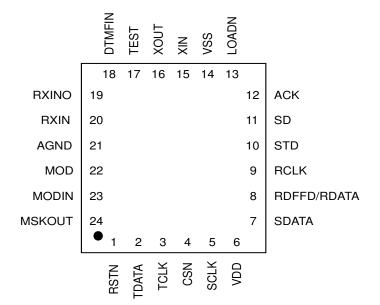

**Pin Assignments**

## **Block Functions**

| Block               | Function                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MSK Modulator       | This circuit generates an MSK signal according to the logic of a digital signal input from the TDATA pin.                                                                                                                                                                                                                                                                                                                  |

| MSK DAC             | DAC that converts data generated by the MSK Modulator into an analog signal.                                                                                                                                                                                                                                                                                                                                               |

| MSK LPF             | This circuit is a low-pass filter for eliminating the clock component included in the MSK DAC signal.<br>A switch for changing between the mute and active states is provided between this filter and VR and is set by setting register MSKTX.                                                                                                                                                                             |

| VR                  | This control adjusts the output level of the transmit MSK signal.<br>Setting register: VR[4:0] Adjustment range: -6.0dB to +6.0dB in 0.5dB steps                                                                                                                                                                                                                                                                           |

| ТХА                 | Operational amplifier for gain adjustment of the transmit MSK signal and for forming a smoothing filter for removing noise components included in the output signal. Use an external resistor and capacitor to set the gain to 0dB and the cut-off frequency to around 13kHz.                                                                                                                                              |

| RXA                 | Operational amplifier for gain adjustment of the receive demodulation signal and for forming a filter for preventing aliasing noise in the SCF circuit in the subsequent stage. Use external resistors and capacitors to set the gain to 20dB or less and the cut-off frequency to around 40kHz.                                                                                                                           |

| MSK BPF             | Band-pass filter to eliminate out-of-band components included in the receive MSK signal.                                                                                                                                                                                                                                                                                                                                   |

| Data Demodulator    | This circuit demodulates the MSK signal and generates data.                                                                                                                                                                                                                                                                                                                                                                |

| Digital PLL         | This circuit detects the carrier signal from the MSK signal and regenerates a clock signal.                                                                                                                                                                                                                                                                                                                                |

| AGC(PGA)            | AGC (Auto Gain Control) circuit for adjusting the input level of the DTMF signal<br>automatically.<br>Setting register: AGCSW or AGCSW. When disabled, this circuit functions as a<br>PGA (Programmable Gain Amp) circuit.<br>Setting register: PGA[1:0] Adjustment range: 0dB to +12dB in 4dB steps<br>A switch for changing the input is provided between this circuit and RXA and is set<br>by setting register DTMFSL. |

| DTMF Receiver       | DTMF signal detection circuit. It decodes the input signal and outputs 4-bit code.                                                                                                                                                                                                                                                                                                                                         |

| OSC                 | This circuit generates a 3.6864MHz reference clock signal from an external crystal oscillator and resistor.                                                                                                                                                                                                                                                                                                                |

| DIV (1/2,1/3,1/4)   | When a signal of which frequency is twice, three times, or four times higher than 3.6864MHz is input from the outside, this circuit divides the signal frequency by two, three, or four.<br>Setting register: MCKSL[1:0]                                                                                                                                                                                                   |

| AGND                | This circuit generates the reference voltage (1/2VDD) for internal analog signals.                                                                                                                                                                                                                                                                                                                                         |

| Control<br>Register | Control registers set the switches and control in the IC according to the serial input data consisting of a 1-bit instruction, a 4-bit address, and 8-bit data. A built-in data buffer is provided to hold 8-bit MSK receive data for easier interfacing with the CPU. At power-on, a system reset is caused by the RSTN pin. A soft reset is set by the SRST register. (Refer to the description of the registers.)       |

## **Pin Functions**

| Pin No. | Pin name        | Pin<br>type | Pin<br>status<br>at<br>power-<br>down | Function                                                                                                                                                                                                                                                                           |

|---------|-----------------|-------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | RSTN            | DI          | Z                                     | Reset pin                                                                                                                                                                                                                                                                          |

| 2       | TDATA           | DI          | z                                     | MSK signal transmit data input pin<br>Data is input from this pin on the rising edge of the clock signal on                                                                                                                                                                        |

|         |                 |             |                                       | the TCLK pin.                                                                                                                                                                                                                                                                      |

| 3       | TCLK            | DO          | L                                     | MSK signal transmit clock output pin                                                                                                                                                                                                                                               |

| 4       | CSN             | DI          | Z                                     | Chip select input pin for serial data                                                                                                                                                                                                                                              |

| 5       | SCLK            | DI          | Z                                     | Clock input pin for serial data                                                                                                                                                                                                                                                    |

|         |                 |             |                                       | VDD power supply pin                                                                                                                                                                                                                                                               |

| 6       | VDD             | PWR         | -                                     | Connect this pin to a power supply ranging from 2.6V to 3.7V with less noise. Connect a bypass capacitor of $0.1\mu F$ or higher between this pin and the VSS pin.                                                                                                                 |

| 7       | SDATA           | DB          | Z                                     | Serial data I/O pin                                                                                                                                                                                                                                                                |

|         |                 |             |                                       | MSK signal receive flag/frame detection signal/RDATA signal output pin                                                                                                                                                                                                             |

| 8       | RDFFD/<br>RDATA | DO          | L                                     | Two types of information is output depending on the FSL register status.<br>If FSL is set to 1 to set the MSK signal receive flag output mode (RDF), this pin is set to the low output level when 8 bits of the MSK receive signal have been written to the receive data register. |

|         |                 |             |                                       | If FSL is set to 0 to set the frame detection signal output mode (FD), a low-level pulse is output on this pin when a frame pattern is detected.                                                                                                                                   |

|         |                 |             |                                       | If setting register MSKRCLK is set to 1, the RDATA signal is output.                                                                                                                                                                                                               |

| 9       | RCLK            | DO          | L                                     | MSK signal receive clock output pin                                                                                                                                                                                                                                                |

|         |                 |             |                                       | Steering delay output pin for DTMF signal detection                                                                                                                                                                                                                                |

| 10      | STD             | DO          | L                                     | This pin goes high when internal data has been updated after completion of DTMF RX signal decoding.                                                                                                                                                                                |

|         |                 |             |                                       | DTMF signal receive data output pin                                                                                                                                                                                                                                                |

| 11      | SD              | DO          | L                                     | If the LOADN pin input is low, the result of DTMF RX signal decoding is output serially starting from the MSB in synchronization with the falling edge of the ACK pin input.                                                                                                       |

|         |                 |             |                                       | If the LOADN pin input is high, the high level is output.                                                                                                                                                                                                                          |

| 12      | ACK             | DI          | Z                                     | Clock input pin for DTMF signal receive data read                                                                                                                                                                                                                                  |

| 13      | LOADN           | DI          | Z                                     | Enable signal input pin for DTMF signal receive data read                                                                                                                                                                                                                          |

|         |                 |             |                                       | If the low level is input, DTMF signal receive data can be read.                                                                                                                                                                                                                   |

[AK2363]

| Pin No. | Pin name | Pin<br>type | Pin<br>status<br>at<br>power-<br>down | Function                                                                                                                                                                                                                                                                                                                                          |

|---------|----------|-------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14      | VSS      | PWR         | -                                     | VSS power supply pin<br>Always apply 0V.                                                                                                                                                                                                                                                                                                          |

| 15      | XIN      | DI/AO       | *4)                                   | Pin for connecting a crystal oscillator<br>A reference clock used within this IC is generated by connecting a<br>3.6864MHz oscillator between this pin and the adjacent XOUT<br>pin. For detailed information about the connection method and<br>the method for supplying an external clock, refer to<br>"Recommended External Circuit Examples." |

| 16      | XOUT     | AI          | *4)                                   | Pin for connecting a crystal oscillator                                                                                                                                                                                                                                                                                                           |

| 17      | TEST     | DI          | Z                                     | Test output pin<br>This pin is used as a test pin before shipment.<br>Normally, connect this pin to VSS.                                                                                                                                                                                                                                          |

| 18      | DTMFIN   | AI          | Z                                     | DTMF signal input pin                                                                                                                                                                                                                                                                                                                             |

| 19      | RXINO    | AO          | Z                                     | RXA amplifier output pin *1)                                                                                                                                                                                                                                                                                                                      |

| 20      | RXIN     | AI          | Z                                     | Demodulated receive signal input pin<br>Inverted input pin of the RXA amplifier. This pin, with resistors<br>and capacitors externally connected, forms a pre-filter.                                                                                                                                                                             |

| 21      | AGND     | AO          | *3)                                   | Analog ground output pin Connect a $0.1\mu$ F capacitor between this pin and the VSS pin to stabilize the analog ground level.                                                                                                                                                                                                                    |

| 22      | MOD      | AO          | Z                                     | Modulated transmit signal output pin *2)                                                                                                                                                                                                                                                                                                          |

| 23      | MODIN    | AI          | Z                                     | Modulated transmit signal input pin<br>Inverted input pin of the TXA amplifier. This pin, with a resistor<br>and capacitor externally connected, forms a smoothing filter.                                                                                                                                                                        |

| 24      | MSKOUT   | AO          | Z                                     | MSK signal level output pin *1)                                                                                                                                                                                                                                                                                                                   |

Note A: Analog, D: Digital, PWR: Power, I: Input, O: Output, B: Bidirectional, Z: High-Z, L: Low

\*1) Output load requirement: Load impedance >  $30k\Omega$ , load capacitance < 15pF

\*2) Output load requirement: Load impedance >  $10k\Omega$ , load capacitance < 50pF

\*3) AGND level

\*4) The XIN pin output level is determined by the XOUT pin input level.

## **Absolute Maximum Ratings**

| Parameter                        | Symbol           | Min. | Max.    | Unit |

|----------------------------------|------------------|------|---------|------|

| Power supply voltage             | VDD              | -0.3 | 4.6     | V    |

| Ground level                     | VSS              | 0    | 0       | V    |

| Input voltage                    | V <sub>IN</sub>  | -0.3 | VDD+0.3 | V    |

| Input current (except power pin) | I <sub>IN</sub>  | -10  | +10     | mA   |

| Storage temperature              | T <sub>stg</sub> | -55  | 130     | °C   |

Note All voltages are relative to the VSS pin.

Caution If the device is used in conditions exceeding these values, the device may be destroyed. Normal operations are not guaranteed in such extreme conditions.

## **Recommended Operating Conditions**

| Parameter                      | Symbol | Condition | Min. | Тур.   | Max. | Unit |

|--------------------------------|--------|-----------|------|--------|------|------|

| Operating temperature          | Та     |           | -40  |        | 85   | °C   |

| Operating power supply voltage | VDD    |           | 2.6  | 3.0    | 3.7  | V    |

| Analog reference<br>voltage    | AGND   |           |      | 1/2VDD |      | V    |

Note All voltages are relative to the VSS pin.

## **Digital DC Characteristics**

| Parameter                    | Symbol          | Condition                                                                | Min.    | Тур. | Max.   | Unit |

|------------------------------|-----------------|--------------------------------------------------------------------------|---------|------|--------|------|

| High level input voltage     | V <sub>IH</sub> | SCLK, SDATA, CSN,<br>LOADN, ACK, TDATA,<br>RSTN,                         | 0.8VDD  |      |        | V    |

| Low level input voltage      | V <sub>IL</sub> | SCLK, SDATA, CSN,<br>LOADN, ACK, TDATA,<br>RSTN,                         |         |      | 0.2VDD | V    |

| High level input current     | IIH             | V <sub>IH</sub> =VDD<br>SCLK, SDATA, CSN,<br>LOADN, ACK, TDATA,<br>RSTN, |         |      | 10     | μΑ   |

| Low level input current      | I <sub>IL</sub> | V <sub>IL</sub> =0V<br>SCLK, SDATA, CSN,<br>LOADN, ACK, TDATA,<br>RSTN,  | -10     |      |        | μΑ   |

| High level output<br>voltage | V <sub>OH</sub> | I <sub>OH</sub> =+0.2mA<br>SDATA, RDFFD/RDATA,<br>RCLK, STD, SD, TCLK    | VDD-0.4 |      | VDD    | V    |

| Low level output<br>voltage  | V <sub>OL</sub> | I <sub>OL</sub> =-0.4mA<br>SDATA, RDFFD/RDATA,<br>RCLK, STD, SD, TCLK    | 0.0     |      | 0.4    | V    |

## **Clock Input Characteristics**

| Parameter                | Symbol               | Condition | Min. | Тур.                         | Max. | Unit     | Remarks  |

|--------------------------|----------------------|-----------|------|------------------------------|------|----------|----------|

| Clock frequency          | MCK0                 | XIN,XOUT  |      | 3.6864                       |      | MHz      |          |

|                          | MCK1,2               | XIN       |      | 7.3728<br>11.0592<br>14.7456 |      | MHz      | *1), *2) |

| High level input voltage | V <sub>MCK1_IH</sub> | XIN       | 1.5  |                              |      | V        | *1)      |

| Low level input voltage  | $V_{MCK1_{IL}}$      | XIN       |      |                              | 0.4  | V        | *1)      |

| Input amplitude          | V <sub>MCK2</sub>    | XIN       | 0.2  |                              | 1.0  | $V_{PP}$ | *2)      |

\*1) These values apply when the clock signal is input on the XIN pin directly. For details, refer to 6), "Oscillator circuit", in "Recommended External Circuit Examples".

\*2) These values apply when the clock signal is input on the XIN pin via DC cut. For details, refer to 6), "Oscillator circuit", in "Recommended External Circuit Examples".

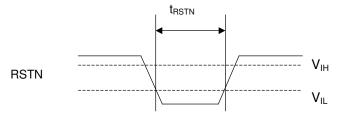

### System Reset

| Parameter                            | Symbol            | Condition        | Min. | Тур. | Max. | Unit | Remarks |

|--------------------------------------|-------------------|------------------|------|------|------|------|---------|

| Hardware reset signal<br>input width | t <sub>RSTN</sub> | RSTN pin         | 1    |      |      | US   | *1)     |

| Software reset                       |                   | SRST<br>register |      |      |      |      | *2)     |

\*1) After power-on and passed 35ms or longer, be sure to perform a hardware reset operation (register initialization). The system is reset by a low pulse input of <u>1μs (min.)</u> and enters the normal operation state. At this moment, the digital (DI) pins are set as follows: RSTN pin to high, TDATA pin to low, CSN pin to high, SCLK pin to low, ACK pin to high, LOADN pin to high, TEST pin to VSS.

\*2) When data 0xAA:10101010 is written to the SRST[8:0] register, a software reset is performed. This setting initializes the registers and the operation mode is set to mode 1 (standby). For details, refer to "Register Functions".

## **Current Consumption**

| Parameter           | Symbol | Condition                                                           | Min. | Тур. | Max. | Unit |

|---------------------|--------|---------------------------------------------------------------------|------|------|------|------|

|                     | IDD0   | Mode 0<br>OSC: OFF, DTMF Receiver: OFF,<br>MSK Tx: OFF, MSK Rx: OFF |      | 0.1  | 0.2  |      |

|                     | IDD1   | Mode 1<br>OSC: ON, DTMF Receiver: OFF,<br>MSK_Tx: OFF, MSK_Rx: OFF  |      | 0.6  | 1.0  |      |

|                     | IDD2   | Mode 2<br>OSC: ON, DTMF Receiver: OFF,<br>MSK_Tx: ON, MSK_Rx: OFF   |      | 1.3  | 2.1  |      |

| Current consumption | IDD3   | Mode 3<br>OSC: ON, DTMF Receiver: OFF,<br>MSK_Tx: OFF, MSK_Rx: ON   |      | 1.1  | 1.8  | mA   |

|                     | IDD4   | Mode 4<br>OSC: ON, DTMF Receiver: OFF,<br>MSK_Tx: ON, MSK_Rx: ON    |      | 1.7  | 2.7  |      |

|                     | IDD5   | Mode 5<br>OSC: ON, DTMF Receiver: ON,<br>MSK_Tx: OFF, MSK_Rx: OFF   |      | 1.3  | 2.2  |      |

|                     | IDD6   | Mode 6<br>OSC: ON, DTMF Receiver: ON,<br>MSK_Tx: ON, MSK_Rx: ON     |      | 2.4  | 3.8  |      |

## **Analog Characteristics**

Unless otherwise specified, the following apply: MCLK = 3.6864MHz, f = 1kHz, VR = 0dB

The external circuit constants are set based on the recommended external circuit examples on pages 29 to 31.

dBx is a standardized notation to match the operating voltage and is defined by equation 0dBx = -5 + 20log(VDD/2)dBm. 0dBm = 0.775Vrms

#### 1) MSK modem characteristics

Parameter

TX signal

racteristicsConditionMin.Typ.Max.UnitRemarks@MOD<br/>1.2kHz signal output-12-11-10dBx

|                      | 1.2kHz signal output                                     | 16   |     | 10  | GDX |

|----------------------|----------------------------------------------------------|------|-----|-----|-----|

| TX signal distortion | @MOD<br>1.2kHz signal output                             |      |     | -32 | dB  |

| RX signal            | @RXINO<br>1.2kHz signal output                           | -17  | -11 | -1  | dBx |

| VR gain deviation    | @MSKOUT<br>-6.0dB to +6.0dB, in 0.5dB steps<br>Linearity | -0.5 |     | 0.5 | dB  |

#### 2) DTMF Receiver characteristics

| Parameter                           | Condition                                      | Min.  | Тур. | Max.          | Unit | Remarks |

|-------------------------------------|------------------------------------------------|-------|------|---------------|------|---------|

|                                     | @RXINO, AGC Disable,<br>PGA=0dB *2), *3), *6)  | -27   |      | 0             | dBx  |         |

| Tone input level accept             | @RXINO, AGC Enable,<br>*2), *3), *6)           | -40   |      | 0             | dBx  |         |

| (for each tone of composite signal) | @DTMFIN, AGC Disable,<br>PGA=0dB *2), *3), *6) | -27   |      | -2            | dBx  |         |

|                                     | @DTMFIN, AGC Enable,<br>*2), *3), *6)          | -40   |      | -2            | dBx  |         |

| Twist accept                        | *3), *6), *8)                                  |       | ±10  |               | dB   |         |

| Frequency deviation accept          | *2), *6)                                       |       |      | ±1.5%<br>±2Hz |      |         |

| Frequency deviation reject          | *2), *6)                                       | ±3.5% |      |               |      |         |

| Third tone tolerance                | *1), *2), *6), *7)                             |       | -16  |               | dB   |         |

| Noise tolerance                     | *1), *2), *4), *6), *7)                        |       | -12  |               | dB   |         |

| Dial tone tolerance                 | *1), *2), *5), *6), *7)                        |       | +17  |               | dB   |         |

| PGA gain deviation                  | 0dB to +12dB, in 4dB steps                     | -0.5  |      | +0.5          | dB   |         |

\*1) Refers to nominal DTMF frequencies.

\*2) High/low tones have the same amplitudes.

\*3) High/low tones are deviated by  $\pm 1.5\% \pm 2$ Hz.

\*4) Bandwidth is limited from 0 to 3kHz Gaussian noise.

\*5) Dialtones of 350Hz and 440Hz  $\pm 2\%$

\*6) Error rates better than 1 in 10000

\*7) Reference DTMF signal input level is -22dBx or less.

\*8) Twist = high tone/low tone

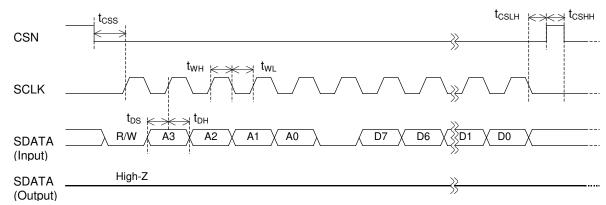

|     | Digital AC Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

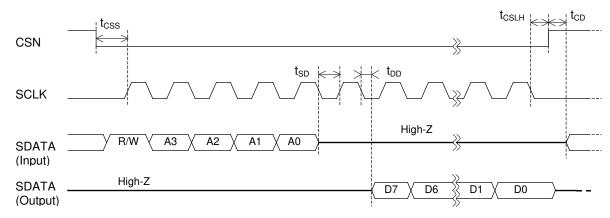

| 1)  | Serial interface timing<br>The AK2363 writes and reads data via the three-wire synchronous serial interface by means of CSN,<br>SCLK, and SDATA.<br>SDATA (serial data) consists of a write/read identification bit (R/W), a register address (starting from<br>the MSB, A3 to A0), and control data (starting from the MSB, D7 to D0).                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Wri | e (WRITE instruction)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     | CSN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | SCLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     | SDATA         R/W         A3         A2         A1         A0         D7         D6         D5         D4         D3         D2         D1         D0           (Input)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     | SDATA Hi-Z<br>(Output)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Rea | d (READ instruction)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     | CSN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | SCLК                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     | SDATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     | (Input) Hi-Z<br>SDATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     | R/W: This bit indicates whether an access to a register is a write access or read access. If this bit is <b>Low</b> , a <b>write</b> is performed; if the bit is <b>High</b> , a <b>read</b> is performed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     | A3 to A0: These bits indicate the address of the register to be accessed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|     | D7 to D0: Data to be written to or read from the register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| <   | 1> CSN (chip select) is normally set to the high level.<br>When CSN is set to the low level, the serial interface becomes active.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <   | <ul> <li>2&gt; When a write operation is performed, an identification bit, an address, and data are input from SDATA in synchronization with the rising edges of 14 SCLK clock pulses while CSN is low. During the time between address A0 and data D7, SDATA must be held low.</li> <li>When a read operation is performed, an identification bit and an address are input from SDATA in synchronization with the rising edges of the first five clock pulses of SCLK, and data at a specified address is output in synchronization with the falling edges of the following nine clock pulses while CSN is low.</li> <li>Note that data between address A0 and data D7 is undefined.</li> <li>During the data output period in the latter nine clock pulses of SCLK, the input to SDATA must be Hi-Z.</li> </ul> |

<3> Write and read settings are made on the assumption that 14 clock pulses are input from SCLK while CSN is low. Note that if clock pulses more than or less than 14 clock pulses are input, data cannot be set

Note that if clock pulses more than or less than 14 clock pulses are input, data cannot be set correctly.

## 2) Detail timing WRITE instruction

#### **READ** instruction

Rising and falling times

t<sub>R</sub>

t<sub>F</sub>

| SCLK                             | $\rightarrow \leftarrow \rightarrow$ | ←                                        |      |      |      |      |

|----------------------------------|--------------------------------------|------------------------------------------|------|------|------|------|

|                                  |                                      | V <sub>IH</sub><br>└──── V <sub>IL</sub> |      |      |      |      |

| Parameter                        | Symbol                               | Condition                                | Min. | Тур. | Max. | Unit |

| CSN setup time                   | t <sub>CSS</sub>                     |                                          | 100  |      |      | ns   |

| SDATA setup time                 | t <sub>DS</sub>                      |                                          | 100  |      |      | ns   |

| SDATA hold time                  | t <sub>DH</sub>                      |                                          | 100  |      |      | ns   |

| SCLK high time                   | t <sub>WH</sub>                      |                                          | 500  |      |      | ns   |

| SCLK low time                    | t <sub>WL</sub>                      |                                          | 500  |      |      | ns   |

| CSN low hold time                | t <sub>CSLH</sub>                    |                                          | 100  |      |      | ns   |

| CSN high hold time               | t <sub>CSHH</sub>                    |                                          | 100  |      |      | ns   |

| SDATA Hi-Z setup time            | t <sub>SD</sub>                      |                                          | 500  |      |      | ns   |

| SCLK to SDATA output delay time  | t <sub>DD</sub>                      | Loaded by<br>20pF                        |      |      | 400  | ns   |

| CSN to SDATA input<br>delay time | t <sub>CD</sub>                      | Loaded by<br>20pF                        | 200  |      |      | ns   |

| SCLK rising time                 | t <sub>R</sub>                       |                                          |      |      | 100  | ns   |

| SCLK falling time                | t <sub>F</sub>                       |                                          |      |      | 100  | ns   |

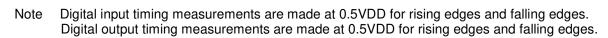

#### 3) MSK Modulator timing

| Parameter                  |           | Symbol          | Min. | Тур. | Max. | Unit |

|----------------------------|-----------|-----------------|------|------|------|------|

| CSN rising to TCLK falling |           |                 |      |      |      |      |

|                            | MSKSL = 0 | T <sub>1</sub>  |      | 208  |      | μS   |

|                            | MSKSL = 1 |                 |      | 417  |      | •    |

| TCLK period                |           |                 |      |      |      |      |

|                            | MSKSL = 0 | T <sub>2</sub>  |      | 417  |      | μS   |

|                            | MSKSL = 1 |                 |      | 833  |      |      |

| TDATA set up time          |           | ts              | 1    |      |      |      |

| TDATA hold time            |           | t <sub>H</sub>  | 1    |      |      | μS   |

| TDATA hold time2           |           | t <sub>H2</sub> | 2    |      |      | •    |

Note Register setting is synchronized with the rising edge on the CSN pin. When the data is maintained for  $2\mu s$  or longer specified by TDATA hold time2 ( $t_{H2}$ ), the signal from MOD pin is ended in zero cross point.

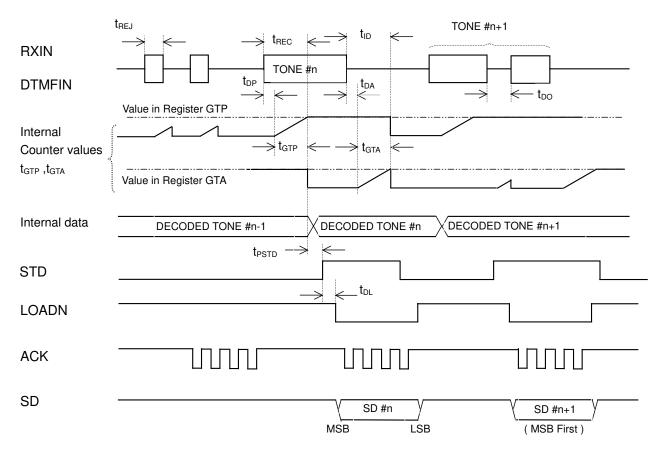

#### 4) MSK Demodulator timing

| Parameter                                                | Symbol | Condition | Min. | Тур.       | Max. | Unit |

|----------------------------------------------------------|--------|-----------|------|------------|------|------|

| RCLK period and FD pulse width<br>MSKSL = 0<br>MSKSL = 1 | Т      |           |      | 417<br>833 |      | μS   |

| CSN                                                                        |               |          |         |     |         |     |                   |     |     |     |     |     |     |     |               |             |

|----------------------------------------------------------------------------|---------------|----------|---------|-----|---------|-----|-------------------|-----|-----|-----|-----|-----|-----|-----|---------------|-------------|

| SCLK                                                                       |               |          |         |     |         |     |                   |     |     |     |     |     |     |     |               |             |

| SDATA<br>(Input)<br>Mode 3,4,6<br>FSL=FCLN=0<br>FSL<br>(Internal Register) | FSL=1         | X        |         |     |         |     | A[3:0]=<br>Data R |     | X   |     |     |     |     |     | XX<br>Mode 1, | <br>2,5<br> |

| FCLN<br>(Internal Register)                                                | FCLN=1 automa | itically |         |     |         |     |                   |     |     |     |     |     |     | }   |               |             |

| RCLK_n                                                                     |               |          |         |     |         |     |                   |     |     |     |     |     |     | ∟⊦∛ |               |             |

| RDATA_n<br>(Internal Node)                                                 | MD7 MD6       | MD5 MD4  | MD3 MD2 | MD1 | MD0 MD7 | MD6 | MD5               | MD4 | MD3 | MD2 | MD1 | MD0 | MD7 | MD6 |               |             |

| FD_n                                                                       |               |          |         |     |         |     |                   |     |     |     |     |     |     |     |               |             |

| RDF_n                                                                      |               |          |         |     |         |     |                   |     |     |     |     |     |     |     |               |             |

| SDATA                                                                      |               |          |         |     |         |     |                   |     |     |     |     |     |     |     |               |             |

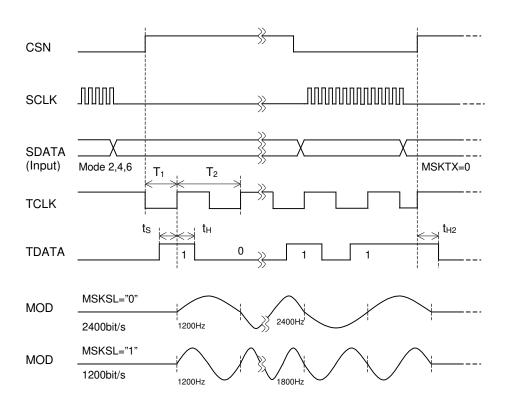

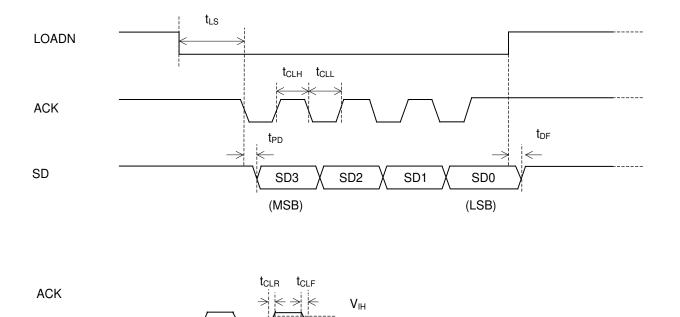

#### 5) DTMF Receiver timing

| Parameter                                      | Symbol            | Condition                    | Min. | Тур. | Max. | Unit |

|------------------------------------------------|-------------------|------------------------------|------|------|------|------|

|                                                |                   | AGC Disable                  | 5    | 11   | 16.8 | ms   |

| Tone present detection time(reference value)   | t <sub>DP</sub>   | AGC Enable                   | 5    | 20   | 44   | ms   |

| Tone absent detection time (reference value)   | t <sub>DA</sub>   |                              | 0.5  | 4    | 8.5  | ms   |

| Topo duration accort time *1)                  | +                 | AGC Disable<br>GTP[3:0]=0100 | 54.5 |      |      | ms   |

| Tone duration accept time *1)                  | t <sub>REC</sub>  | AGC Enable<br>GTP[3:0]=0001  | 54   |      |      | ms   |

| Tone duration reject time*1)                   | t <sub>REJ</sub>  |                              |      |      | 32.2 | ms   |

| Interdigit pause accept time *1)               | t <sub>ID</sub>   |                              | 28.4 |      |      | ms   |

| Interdigit pause reject time *1)               | t <sub>DO</sub>   |                              |      |      | 1.6  | ms   |

| GT (internal counter) to STD propagation delay | t <sub>PSTD</sub> |                              |      | 21.7 |      | μs   |

| STD rising to LOADN falling time               | t <sub>DL</sub>   |                              | 100  |      |      | ns   |

| ACK low period                                 | t <sub>CLL</sub>  |                              | 500  |      |      | ns   |

| ACK high period                                | t <sub>CLH</sub>  |                              | 500  |      |      | ns   |

| LOADN setup time                               | t <sub>LS</sub>   |                              | 500  |      |      | ns   |

| SD output delay time                           | t <sub>PD</sub>   | Loaded by 20pF               |      |      | 200  | ns   |

| SD output disable time                         | t <sub>DF</sub>   | Loaded by 20pF               |      |      | 200  | ns   |

| ACK rising time                                | t <sub>CLR</sub>  |                              |      |      | 100  | ns   |

| ACK falling time                               | t <sub>CLF</sub>  |                              |      |      | 100  | ns   |

\*1) The data shows the values when registers GTPn and GTAn (n = 0 to 3) contain their initial values. This data can be adjusted by setting registers GTPn and GTAn (n = 0 to 3) (refer to pages 26 and 27).

\*2) Digital input timing measurements are made at 0.5VDD for rising edges and falling edges. Digital output timing measurements are made at 0.5VDD for rising edges and falling edges.

Note Internal data of the LSI device is changed by DTMF data immediately before STD goes high.

$V_{\text{IL}}$

## **Register Functions**

#### 1) Register configuration

|              |              | lress        |               | Function                    |        |         |                | Da             | ata          |               |         |      |

|--------------|--------------|--------------|---------------|-----------------------------|--------|---------|----------------|----------------|--------------|---------------|---------|------|

| A3           | A2           | A1           | A0            | Function                    | D7     | D6      | D5             | D4             | D3           | D2            | D1      | D0   |

| 0            | 0            | 0            | 0             | Control register 1          | BS2    | BS1     | BS0            | MSKSL          | MSKTX        | MSKRCLK       | FSL     | FCLN |

| 0            | 0            | 0            | 1             | Control register 2          | MCKSL1 | MCKSL0  | TXRXA          | VR4            | VR3          | VR2           | VR1     | VR0  |

| 0            | 0            | 1            | 0             | DTMF register 1             | GTP3   | GTP2    | GTP1           | GTP0           | GTA3         | GTA2          | GTA1    | GTA0 |

| 0            | 0            | 1            | 1             | DTMF register 2             | _      | STDPGA1 | STDPGA0        | DTMFSL         | AGCSW1       | AGCSW0        | PGA1    | PGA0 |

| 0            | 1            | 0            | 0             | Modem frame<br>pattern 1    |        |         | Lower 8        | bits of MSK    | modem fram   | ne pattern    |         |      |

| 0            | 1            | 0            | 1             | Modem frame pattern 2       |        |         | Upper 8        | bits of MSK    | modem fran   | ne pattern    |         |      |

| 0            | 1            | 1            | 0             | Modem receive data register |        |         | N              | ISK receive    | data (RDAT   | A)            |         |      |

| 0            | 1            | 1            | 1             | Software reset              |        |         |                | SRS            | T[7:0]       |               |         |      |

| 1            | 0            | 0            | 0             | Revision register           | -      | -       | -              | -              |              | REVNU         | JM[3:0] |      |

| 1            | 0            | 0            | 1             | Test register 1             |        | Те      | est register 1 | for LSI test   | operation (r | not accessibl | e)      |      |

| 1            | 0            | 1            | 0             | Test register 2             |        | Те      | est register 2 | 2 for LSI test | operation (r | not accessibl | e)      |      |

| 1            | 0            | 1            | 1             | Not used                    |        |         |                |                |              |               |         |      |

| $\downarrow$ | $\downarrow$ | $\downarrow$ | $\rightarrow$ | Not used                    |        |         |                |                |              |               | -       |      |

| 1            | 1            | 1            | 1             | Not used                    | _      | -       | -              | _              | -            | -             | _       | _    |

Note 1 An access to data indicated by "-" does not have any effect on the LSI operation, and always reads 0.

Note 2 The SRST[7:0] register at address 0111 is write-only.

The MSK receive data register at address 0110 and the REVNUM[3:0] register at address 1000 are read-only. Note 3 Test registers are located at addresses 1001 and 1010 and cannot be accessed. If an access is made to these

addresses inadvertently, the LSI operation is not guaranteed.

#### 2) Descriptions of registers

#### 2.1) Control register 1

|    | Address Data |       |    |     |     |     |       |       |         |     |      |

|----|--------------|-------|----|-----|-----|-----|-------|-------|---------|-----|------|

| A3 | A2           | A1    | A0 | D7  | D6  | D5  | D4    | D3    | D2      | D1  | D0   |

| 0  | 0            | 0     | 0  | BS2 | BS1 | BS0 | MSKSL | MSKTX | MSKRCLK | FSL | FCLN |

|    | Initia       | value |    | 0   | 0   | 0   | 1     | 1     | 0       | 0   | 1    |

#### 2.1.1) Operation mode setting

| BS2 | BS1 | BS0 | Mode name       | OSC and | MSK modem | MSK modem | DTMF     |

|-----|-----|-----|-----------------|---------|-----------|-----------|----------|

| D32 | 001 | D30 |                 | AGND    | TX        | RX        | Receiver |

| 0   | 0   | 0   | Mode 0          | OFF     | OFF       | OFF       | OFF      |

|     |     |     | (power down)    |         |           |           |          |

| 0   | 0   | 1   | Mode1 (standby) | ON      | OFF       | OFF       | OFF      |

| 0   | 1   | 0   | Mode 2          | ON      | ON        | OFF       | OFF      |

| 0   | 1   | 1   | Mode 3          | ON      | OFF       | ON        | OFF      |

| 1   | 0   | 0   | Mode 4          | ON      | ON        | ON        | OFF      |

| 1   | 0   | 1   | Mode 5          | ON      | OFF       | OFF       | ON       |

| 1   | 1   | 0   | Mode 6          | ON      | ON        | ON        | ON       |

Note: After setting the system reset(Mode 0), select Mode 2 to 6 via setting Mode 1.

#### 2.1.2) MSK modem setting

| Data    | ltem                               | Fur                                                | nction                                             | Remarks |

|---------|------------------------------------|----------------------------------------------------|----------------------------------------------------|---------|

| Dala    | nem                                | 0                                                  | 1                                                  | nemains |

| MSKSL   | MSK modem<br>transmission<br>speed | 2400 bit/s                                         | 1200 bit/s                                         |         |

| MSKTX   | MSK transmit<br>output             | OFF (Mute)                                         | ON (Active)                                        |         |

|         |                                    | RCLK pin High output                               | RCLK pin Active                                    |         |

| MSKRCLK | RCLK output<br>switching           | RDFFD/RDATA pin<br>Active<br>(RDFFD signal output) | RDFFD/RDATA pin<br>Active<br>(RDATA signal output) |         |

| FSL     | RDF/FD output<br>switching         | Frame detection signal<br>(FD) output              | Receive flag signal (RDF)<br>output                |         |

| FCLN    | Frame Detect                       | ON (Enable)                                        | OFF (Disable)                                      |         |

#### 2.2) Control register 2

|    | Add     | ress  |    |        |        |       | Data |     |     |     |     |

|----|---------|-------|----|--------|--------|-------|------|-----|-----|-----|-----|

| A3 | A2      | A1    | A0 | D7     | D6     | D5    | D4   | D3  | D2  | D1  | D0  |

| 0  | 0       | 0     | 1  | MCKSL1 | MCKSL0 | TXRXA | VR4  | VR3 | VR2 | VR1 | VR0 |

|    | Initial | value |    | 0      | 0      | 0     | 0    | 1   | 1   | 0   | 0   |

| MCKSL1 | MCKSL0 | Function                 | Remarks             |

|--------|--------|--------------------------|---------------------|

| 0      | 0      | Master clock: 3.6864MHz  |                     |

| 0      | 1      | Master clock: 7.3728MHz  | External input only |

| 1      | 0      | Master clock: 11.0592MHz | External input only |

| 1      | 1      | Master clock: 14.7456MHz | External input only |

| Data  | ltem                            | Fund            | ction         | Remarks                                                          |  |

|-------|---------------------------------|-----------------|---------------|------------------------------------------------------------------|--|

| Dala  | llem                            | 0               | 1             |                                                                  |  |

| TXRXA | TXA and RXA amplifier operation | OFF (Power OFF) | ON (Power ON) | ORed with<br>operation mode<br>setting; valid in<br>modes 1 to 6 |  |

| VR4 | VR3 | VR2 | VR1 | VR0 | VR gain (dB) |

|-----|-----|-----|-----|-----|--------------|

| 0   | 0   | 0   | 0   | 0   | -6.0         |

| 0   | 0   | 0   | 0   | 1   | -5.5         |

| 0   | 0   | 0   | 1   | 0   | -5.0         |

| 0   | 0   | 0   | 1   | 1   | -4.5         |

| 0   | 0   | 1   | 0   | 0   | -4.0         |

| 0   | 0   | 1   | 0   | 1   | -3.5         |

| 0   | 0   | 1   | 1   | 0   | -3.0         |

| 0   | 0   | 1   | 1   | 1   | -2.5         |

| 0   | 1   | 0   | 0   | 0   | -2.0         |

| 0   | 1   | 0   | 0   | 1   | -1.5         |

| 0   | 1   | 0   | 1   | 0   | -1.0         |

| 0   | 1   | 0   | 1   | 1   | -0.5         |

| 0   | 1   | 1   | 0   | 0   | 0.0          |

| VR4 | VR3 | VR2 | VR1 | VR0 | VR gain (dB) |

|-----|-----|-----|-----|-----|--------------|

| 0   | 1   | 1   | 0   | 1   | +0.5         |

| 0   | 1   | 1   | 1   | 0   | +1.0         |

| 0   | 1   | 1   | 1   | 1   | +1.5         |

| 1   | 0   | 0   | 0   | 0   | +2.0         |

| 1   | 0   | 0   | 0   | 1   | +2.5         |

| 1   | 0   | 0   | 1   | 0   | +3.0         |

| 1   | 0   | 0   | 1   | 1   | +3.5         |

| 1   | 0   | 1   | 0   | 0   | +4.0         |

| 1   | 0   | 1   | 0   | 1   | +4.5         |

| 1   | 0   | 1   | 1   | 0   | +5.0         |

| 1   | 0   | 1   | 1   | 1   | +5.5         |

| 1   | 1   | 0   | 0   | 0   | +6.0         |

#### 2.3) DTMF register 1

| Address       |    |    |    |      | Data |      |      |      |      |      |      |

|---------------|----|----|----|------|------|------|------|------|------|------|------|

| A3            | A2 | A1 | A0 | D7   | D6   | D5   | D4   | D3   | D2   | D1   | D0   |

| 0             | 0  | 1  | 0  | GTP3 | GTP2 | GTP1 | GTP0 | GTA3 | GTA2 | GTA1 | GTA0 |

| Initial value |    |    |    | 0    | 1    | 0    | 0    | 0    | 0    | 1    | 0    |

| Data         | Function                                                                                                             | Remarks |

|--------------|----------------------------------------------------------------------------------------------------------------------|---------|

| GTP3 to GTP0 | Register for setting DTMF Receiver guard time t <sub>GTP</sub> .<br>For details, refer to "DTMF Receiver Operation". |         |

| GTA3 to GTA0 | Register for setting DTMF Receiver guard time t <sub>GTA</sub> .<br>For details, refer to "DTMF Receiver Operation". |         |

#### 2.4) DTMF register 2

|               | Ado | dress |    |    | Data    |         |        |        |        |      |      |  |

|---------------|-----|-------|----|----|---------|---------|--------|--------|--------|------|------|--|

| A3            | A2  | A1    | A0 | D7 | D6      | D5      | D4     | D3     | D2     | D1   | D0   |  |

| 0             | 0   | 1     | 1  | -  | STDPGA1 | STDPGA0 | DTMFSL | AGCSW1 | AGCSW0 | PGA1 | PGA0 |  |

| Initial value |     |       |    | _  | 0       | 0       | 1      | 0      | 1      | 0    | 0    |  |

| STDPGA1 | STDPGA0 | PGA gain<br>(dB) |

|---------|---------|------------------|

| 0       | 0       | 0                |

| 0       | 1       | +4               |

| 1       | 0       | +8               |

| 1       | 1       | +12              |

Note When AGC circuit is enable, automatic set PGA gain can be monitored by STDPGA[1:0] register. This register is <u>read-only</u> and synchronized with the rising edge on the DTMF signal detection pin: STD.

| Data   | ltom                    | Fund             | ction          | Domorko |

|--------|-------------------------|------------------|----------------|---------|

| Dala   | Item                    | 0                | 1              | Remarks |

| DTMFSL | DTMF input<br>switching | DTMFIN pin input | RXIN pin input |         |

| AGCSW1 | AGCSW0 |                           | Function                                                                                                                | Remarks       |

|--------|--------|---------------------------|-------------------------------------------------------------------------------------------------------------------------|---------------|

| 0      | 0      | AGC circuit Off (Disable) | PGA gain can be set with PGA[1:0] register.                                                                             |               |

| 0      | 1      | AGC circuit On (Enable)   | PGA gain can be monitored by<br>STDPGA[1:0] register.<br>The register data is renewal at every DTMF<br>detection.       | Initial value |

| 1      | 0      | AGC circuit Off (Disable) | PGA gain may be set with the latest<br>STDPGA[1:0] register, then AGC is off.<br>PGA gain can not be set with PGA[1:0]. |               |

| 1      | 1      | Not used                  |                                                                                                                         |               |

| PGA1 | PGA0 | PGA gain<br>(dB) |

|------|------|------------------|

| 0    | 0    | 0                |

| 0    | 1    | +4               |

| 1    | 0    | +8               |

| 1    | 1    | +12              |

Note When the AGC circuit is disabled, the gain of the PGA circuit can be set manually with PGA[1:0].

| Address       |               |    |    | <b>-0</b> | Data |     |     |     |     |     |     |

|---------------|---------------|----|----|-----------|------|-----|-----|-----|-----|-----|-----|

| A3            | A2            | A1 | A0 | D7        | D6   | D5  | D4  | D3  | D2  | D1  | D0  |

| 0             | 1             | 0  | 0  | F07       | F06  | F05 | F04 | F03 | F02 | F01 | F00 |

|               | Initial value |    |    | 1         | 0    | 1   | 0   | 1   | 0   | 0   | 0   |

| 0             | 1             | 0  | 1  | F15       | F14  | F13 | F12 | F11 | F10 | F09 | F08 |

| Initial value |               |    |    | 0         | 0    | 0   | 1   | 1   | 0   | 1   | 1   |

#### 2.5) Modem frame pattern register (at power-down: specific low-power radio)

#### 2.6) Modem receive data register

|    | Address |    |    |     | Data                   |     |     |     |     |     |     |

|----|---------|----|----|-----|------------------------|-----|-----|-----|-----|-----|-----|

| A3 | A2      | A1 | A0 | D7  | D7 D6 D5 D4 D3 D2 D1 D |     |     |     |     |     | D0  |

| 0  | 1       | 1  | 0  | RD7 | RD6                    | RD5 | RD4 | RD3 | RD2 | RD1 | RD0 |

| Dete   | ltem    | MSK rec | Demortes |               |

|--------|---------|---------|----------|---------------|

| Data   |         | 0       | 1        | Remarks       |

| RD7 to | MSKSL=0 | 2.4kHz  | 1.2kHz   | Data received |

| RD0    | MSKSL=1 | 1.8kHz  | 1.2kHz   | first is RD7. |

This register is <u>read-only</u>, and no data can be written to the register.

#### 2.7) Software reset register

|    | Address       |    |    |           | Data |    |    |    |    |    |    |

|----|---------------|----|----|-----------|------|----|----|----|----|----|----|

| A3 | A2            | A1 | A0 | D7        | D6   | D5 | D4 | D3 | D2 | D1 | D0 |

| 0  | 1             | 1  | 1  | SRST[7:0] |      |    |    |    |    |    |    |

|    | Initial value |    |    | 0         | 0    | 0  | 0  | 0  | 0  | 0  | 0  |

When data 0xAA:10101010 is written to the SRST[7:0] register, a software reset is performed. This sets BS[2:0] to mode 1 (standby) and the registers other than BS[2:0] to their initial values to place the system in the standby state.

This register is <u>write-only</u>, and after completion of software reset, the register is set to 0.

#### 2.8) Revision register

|    | Address       |    |    |    | Data |    |    |             |    |    |    |

|----|---------------|----|----|----|------|----|----|-------------|----|----|----|

| A3 | A2            | A1 | A0 | D7 | D6   | D5 | D4 | D3          | D2 | D1 | D0 |

| 1  | 0             | 0  | 0  | _  | _    | _  | _  | REVNUM[3:0] |    |    |    |

|    | Initial value |    |    |    |      | _  | _  | 0           | 0  | 0  | 0  |

When the D3 to D0 data is accessed, the revision number for management can be read. This register is <u>read-only</u>, and no data can be written to the register.

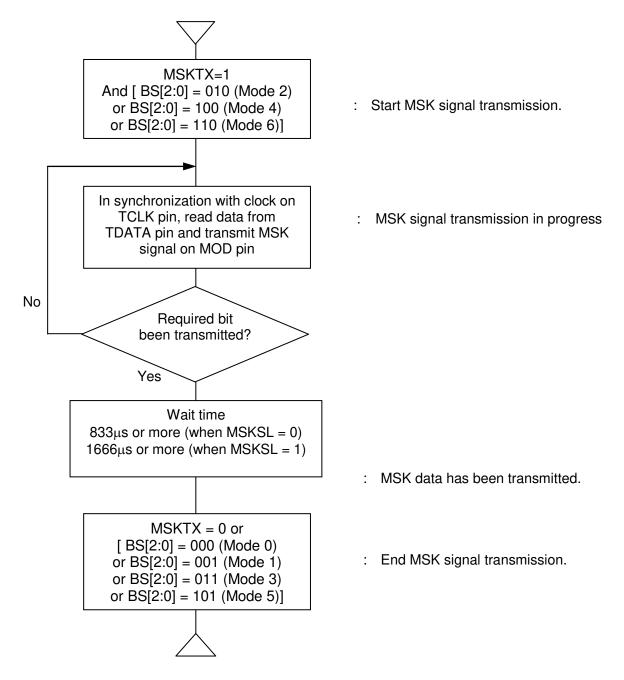

### **MSK Modem Operation**

1) MSK Modulator

The TX section of the modem interfaces with the Modulator by using the TCLK, TDATA, and MOD pins and register data BS2, BS1, BS0 (referred to as BS[2:0]), and MSKTX as follows:

- (1) Set MSKTX to 1 and BS[2:0] to mode 2, 4, or 6 to start MSK transmission.

- (2) A 1200Hz or 2400Hz clock is output on the TCLK pin. In synchronization with the rising edge of TCLK, the AK2363 reads MSK transmit data from the TDATA pin and outputs the modulated MSK signal on the MOD pin.

- (3) After as many bits as required have been transmitted, wait for two clock periods until the last bit of the MSK signal has been transmitted.

- (4) Then, set BS[2:0] to change from mode 2, 4, or 6 to mode 0,1, 3, or 5. Alternatively, set MSKTX to 0 to end signal transmission.

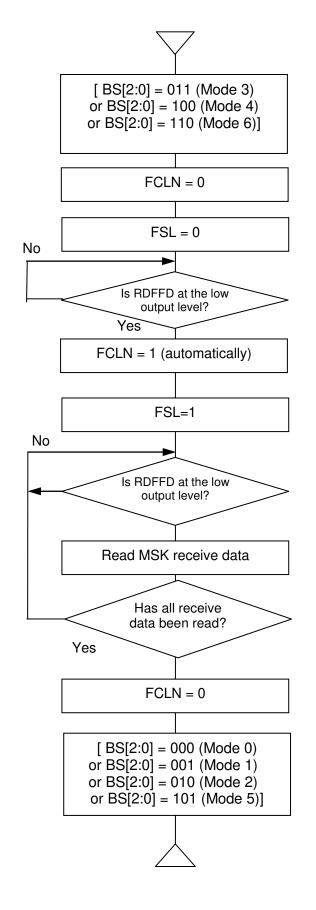

- 2) MSK Demodulator

- 2.1) When Frame Detect is not used

- The modem interfaces with the Demodulator by using the RXIN, RCLK, and RDFFD/RDATA pins, register data BS[2:0], and MSKRCLK as follows:

- (1) Set BS[2:0] to select mode 3, 4, or 6, and at the same time set MSKRCLK to 1 to start MSK reception.

- (2) When the MSK signal is received on the RXIN pin, data demodulated via MSK-BPF, Data-Demodulator, and the Digital-PLL circuit is output successively as RDATA on the RDFFD/RDATA pin in synchronization with the falling edge of the 1200Hz or 2400Hz clock signal output on the RCLK pin.