## imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### AKM

# $\begin{array}{c} \textbf{AK4353} \\ \textbf{96kHz 24Bit } \Delta \Sigma \textbf{ DAC with DIT} \end{array}$

#### **GENERAL DESCRIPTION**

The AK4353 is a stereo CMOS D/A Converter and Digital Audio Interface Transmitter. The DAC signal outputs are single-ended and are analog filtered to remove out of band noise. Therefore no external filters are required. The AK4353 can operate at the power supply from 2.7V to 5.5V and the digital I/F can correspond to both TTL and CMOS levels.

| FEATURES                                                  |                                |

|-----------------------------------------------------------|--------------------------------|

| $\Box$ Stereo $\Delta \Sigma$ DAC                         |                                |

| □ S/(N+D): 90dB@5V                                        |                                |

| □ DR: 102dB@5V                                            |                                |

| □ S/N: 102dB@5V                                           |                                |

| Sampling Speed: 16kHz~96kHz                               |                                |

| Multiple Master Clock Frequencies:                        |                                |

| 256fs/384fs/512fs/768fs/1024fs/1536fs                     | for Half speed (16kHz~24kHz)   |

| 256fs/384fs/512fs/768fs                                   | for Normal speed (32kHz~48kHz) |

| 128fs/192fs/256fs/384fs                                   | for Double speed (64kHz~96kHz) |

| Data Input Formats:                                       |                                |

| LSB justified / MSB justified / I <sup>2</sup> S select   | able                           |

| Selectable Function:                                      |                                |

| Soft Mute                                                 |                                |

| Digital Attenuator (256 Steps)                            |                                |

| Digital De-emphasis (44.1kHz/48kHz/32                     | -                              |

| Output Mode: Stereo, Mono, Reverse, Mu                    |                                |

| On-Chip Digital Audio Interface Transmitt                 |                                |

| Compatible with S/PDIF, IEC958, AES/E                     | :80                            |

| & EIAJ CP1201 consumer mode                               |                                |

| Input Level: TTL/CMOS Selectable Output Level: 3.0Vpp@5V  |                                |

| $\Box$ Control mode: 3-wire Serial / I <sup>2</sup> C Bus |                                |

| □ Low Power Dissipation: 80mW@5V                          |                                |

| □ Small 24pin VSOP Package                                |                                |

| □ Power Supply: 2.7~5.5V                                  |                                |

| □ Ta: -40~85°C                                            |                                |

|                                                           |                                |

|                                                           |                                |

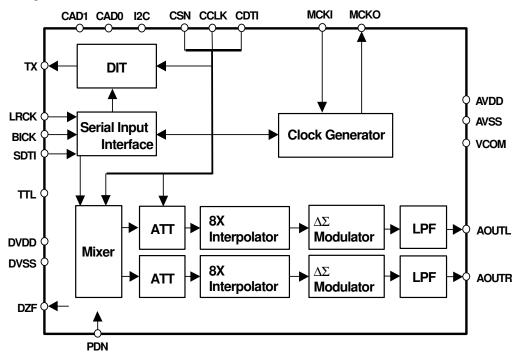

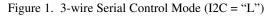

#### Block Diagram

Figure 2.  $I^2C$  Bus Control Mode (I2C = "H")

#### ■ Ordering Guide

| AK4353VF | -40~+85°C        | 24pin VSOP |

|----------|------------------|------------|

| AKD4353  | Evaluation Board |            |

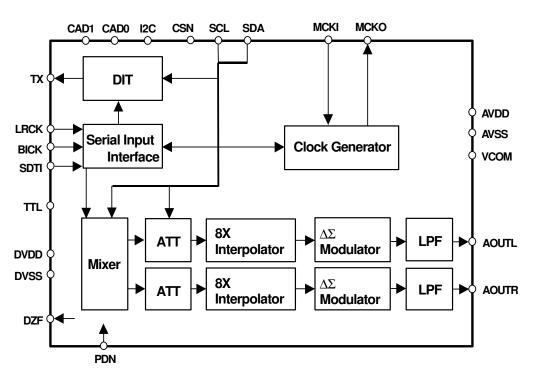

#### Pin Layout

#### **PIN/FUNCTION**

| No. | Pin Name | I/O | Description                                                                |

|-----|----------|-----|----------------------------------------------------------------------------|

| 1   | МСКО     | 0   | Master Clock Output Pin                                                    |

|     |          |     | Same frequency as MCKI is output                                           |

| 2   | ТХ       | 0   | Transmit Channel Output Pin                                                |

| 3   | DVDD     | -   | Digital Power Supply Pin, +2.7~+5.5V                                       |

| 4   | DVSS     | -   | Digital Ground Pin, 0V                                                     |

| 5   | MCKI     | Ι   | Master Clock Input Pin                                                     |

| 6   | BICK     | Ι   | Serial Data Clock Pin                                                      |

| 7   | SDTI     | Ι   | Serial Data Input Pin                                                      |

| 8   | LRCK     | Ι   | Serial Input Channel Clock Pin                                             |

| 9   | PDN      | Ι   | Power-Down Pin                                                             |

|     |          |     | When "L", the circuit is in power-down mode.                               |

|     |          |     | The AK4353 should always be reset upon power-up.                           |

| 10  | CSN      | Ι   | Chip Select Pin at 3-wire Serial control mode                              |

|     |          |     | This pin should be connected to DVDD at I <sup>2</sup> C Bus control mode. |

| 11  | SCL      | Ι   | Control Clock Pin at I <sup>2</sup> C bus control mode                     |

|     | CCLK     | Ι   | Control Clock Pin at 3-wire serial control mode                            |

| 12  | SDA      | I/O | Control Data Input/Output Pin at I <sup>2</sup> C Bus control mode         |

|     | CDTI     | Ι   | Control Data Input Pin at 3-wire serial control mode                       |

| 13  | TST      | Ι   | Test pin                                                                   |

|     |          |     | This pin should be connected to DVDD.                                      |

| 14  | TTL      | Ι   | Digital Input Level Select Pin                                             |

|     |          |     | "L": CMOS, "H": TTL                                                        |

| 15  | I2C      | Ι   | Control Mode Select Pin                                                    |

|     |          |     | "L": 3-wire Serial, "H": I <sup>2</sup> C Bus                              |

| 16  | CAD0     | Ι   | Chip Address Select 0 Pin                                                  |

| 17  | CAD1     | Ι   | Chip Address Select 1 Pin                                                  |

| 18  | AOUTR    | 0   | Rch Analog Output Pin                                                      |

| 19  | AOUTL    | 0   | Lch Analog Output Pin                                                      |

| 20  | VCOM     | 0   | Common Voltage Output Pin, AVDD/2                                          |

|     |          |     | Used for analog common voltage.                                            |

|     |          |     | Large external capacitor is used to reduce power supply noise.             |

| 21  | AVSS     | -   | Analog Ground Pin                                                          |

| 22  | AVDD     | -   | Analog Power Supply Pin                                                    |

| 23  | NC       | -   | No Connect                                                                 |

|     |          |     | Nothing should be connected externally to this pin.                        |

| 24  | DZF      | 0   | Zero Input Detect Pin                                                      |

|     |          |     | When SDTI follows a total 8192 LRCK cycles with "0" input data             |

|     |          |     | or RSTN = "0", this pin goes to "H".                                       |

Note: No input pins should be left floating.

|                     | ABSOLUTE MAXIMUM RATINGS  |              |      |          |       |  |  |  |  |  |

|---------------------|---------------------------|--------------|------|----------|-------|--|--|--|--|--|

| (AVSS, DVSS=0V      | ; Note 1)                 |              |      |          |       |  |  |  |  |  |

| Parameter           |                           | Symbol       | min  | max      | Units |  |  |  |  |  |

| Power Supplies      | Analog                    | AVDD         | -0.3 | 6.0      | V     |  |  |  |  |  |

|                     | Digital                   | DVDD         | -0.3 | 6.0      | V     |  |  |  |  |  |

|                     | AVSS-DVSS (Note 2)        | $\Delta GND$ | -    | 0.3      | V     |  |  |  |  |  |

| Input Current (any  | pins except for supplies) | IIN          | -    | ±10      | mA    |  |  |  |  |  |

| Analog Input Volta  | ige                       | VINA         | -0.3 | AVDD+0.3 | V     |  |  |  |  |  |

| Digital Input Volta | ge                        | VIND         | -0.3 | DVDD+0.3 | V     |  |  |  |  |  |

| Ambient Temperat    | ure                       | Та           | -40  | 85       | °C    |  |  |  |  |  |

| Storage Temperatu   | re                        | Tstg         | -65  | 150      | °C    |  |  |  |  |  |

Note: 1. All voltages with respect to ground.

2. AVSS and DVSS must be connected to the same analog ground plane.

WARNING: Operation at or beyond these limits may results in permanent damage to the device. Normal operation is not guaranteed at these extremes.

|                         | RECOMMENDED OPERATING CONDITIONS |        |     |     |             |       |  |  |  |  |

|-------------------------|----------------------------------|--------|-----|-----|-------------|-------|--|--|--|--|

| (AVSS, DVSS=0V; Note 1) |                                  |        |     |     |             |       |  |  |  |  |

| Parameter               |                                  | Symbol | min | typ | max         | Units |  |  |  |  |

| Power Supplies          | 3V operation (TTL = "L")         |        |     |     |             |       |  |  |  |  |

| (Note 3)                | Analog                           | AVDD   | 2.7 | 3.0 | 5.5         | V     |  |  |  |  |

|                         | Digital                          | DVDD   | 2.7 | 3.0 | 3.6 or AVDD | V     |  |  |  |  |

|                         | 5V operation $(TTL = "H")$       |        |     |     |             |       |  |  |  |  |

|                         | Analog                           | AVDD   | 4.5 | 5.0 | 5.5         | V     |  |  |  |  |

|                         | Digital                          | DVDD   | 4.5 | 5.0 | AVDD        | V     |  |  |  |  |

Note: 1. All voltages with respect to ground.

3. The power up sequence between AVDD and DVDD is not critical.

\*AKM assumes no responsibility for the usage beyond the conditions in this datasheet.

#### ANALOG CHARACTERISTICS (fs=44.1kHz)

(Ta=25°C; AVDD, DVDD=5V; fs=44.1kHz; DFS1-0 = "00"; CKS2-0 = "000"; DIF2-0 = "101";

| Parameter                           | min      | typ  | max | Units |        |

|-------------------------------------|----------|------|-----|-------|--------|

| Dynamic Characteristics             |          |      |     |       |        |

| Resolution                          |          |      |     | 24    | Bits   |

| S/(N+D)                             | AVDD=5V  | 84   | 90  |       | dB     |

|                                     | AVDD=3V  | 80   | 86  |       | dB     |

| DR (-60dB input, A-weighted)        | AVDD=5V  | 94   | 102 |       | dB     |

|                                     | AVDD=3V  | 90   | 97  |       | dB     |

| S/N (A-weighted)                    | AVDD=5V  | 94   | 102 |       | dB     |

|                                     | AVDD=3V  | 90   | 97  |       | dB     |

| Interchannel Isolation              |          | 90   | 110 |       | dB     |

| DC Accuracy                         |          |      |     |       |        |

| Interchannel Gain Mismatch          |          |      | 0.2 | 0.5   | dB     |

| Gain Drift                          |          |      | 20  | -     | ppm/°C |

| Output Voltage AOUT=0.6x(AVDD-AVSS) | AVDD=5V  | 2.8  | 3.0 | 3.2   | Vpp    |

|                                     | AVDD=3V  | 1.66 | 1.8 | 1.94  | Vpp    |

| Load Resistance                     | (Note 4) | 10   |     |       | kΩ     |

| Load Capacitance                    |          |      |     | 25    | pF     |

| Power Supplies                      |          |      |     |       |        |

| Power Supply Current                |          |      |     |       |        |

| Normal Operation (PDN = "H")        |          |      |     |       |        |

| AVDD                                |          |      | 8   | 12    | mA     |

| DVDD                                | (Note 5) |      | 8   | 16    | mA     |

| Power-Down-Mode (PDN = "L")         |          |      |     |       |        |

| AVDD+DVDD                           |          |      | 10  | 100   | μA     |

Note:4. AC load.

5. DVDD drops to 4mA at DVDD=3V.

#### ANALOG CHARACTERISTICS (fs=96kHz)

(Ta=25°C; AVDD, DVDD=5V; fs=96kHz; DFS1-0 = "01"; CKS2-0 = "001"; DIF2-0 = "101"; Signal Frequency =1kHz: Measurement frequency=20Hz~40kHz; unless otherwise specified)

| Parameter                           | min      | typ  | max | Units |        |

|-------------------------------------|----------|------|-----|-------|--------|

| Dynamic Characteristics             |          |      |     |       |        |

| Resolution                          |          |      |     | 24    | Bits   |

| S/(N+D)                             | AVDD=5V  | 80   | 86  |       | dB     |

|                                     | AVDD=3V  | 78   | 84  |       | dB     |

| DR (-60dB input)                    | AVDD=5V  | 88   | 96  |       | dB     |

|                                     | AVDD=3V  | 84   | 92  |       | dB     |

| S/N                                 | AVDD=5V  | 88   | 96  |       | dB     |

|                                     | AVDD=3V  | 84   | 92  |       | dB     |

| Interchannel Isolation              |          | 90   | 110 |       | dB     |

| DC Accuracy                         |          |      |     |       |        |

| Interchannel Gain Mismatch          |          |      | 0.2 | 0.5   | dB     |

| Gain Drift                          |          |      | 20  | -     | ppm/°C |

| Output Voltage AOUT=0.6x(AVDD-AVSS) | AVDD=5V  | 2.8  | 3.0 | 3.2   | Vpp    |

|                                     | AVDD=3V  | 1.66 | 1.8 | 1.94  | Vpp    |

| Load Resistance                     | (Note 4) | 10   |     |       | kΩ     |

| Load Capacitance                    |          |      |     | 25    | pF     |

| Power Supplies                      |          |      |     |       |        |

| Power Supply Current                |          |      |     |       |        |

| Normal Operation (PDN = "H")        |          |      |     |       |        |

| AVDD                                |          |      | 8   | 12    | mA     |

| DVDD                                | (Note 6) |      | 13  | 26    | mA     |

| Power-Down-Mode (PDN = "L")         |          |      |     |       |        |

| AVDD+DVDD                           |          |      | 10  | 100   | μA     |

Note:4. AC load.

6. DVDD drops to 7mA at DVDD=3V.

|                       |                 | FILTER CHARA      | ACTERISTI | <b>CS (fs=44.</b> 1 | lkHz) |       |       |

|-----------------------|-----------------|-------------------|-----------|---------------------|-------|-------|-------|

| (Ta=25°C; AV          | /DD, DVDD=2.7~3 | 5.5V; fs=44.1kHz; | DEM=OFF)  |                     |       |       |       |

| Parameter             |                 |                   | Symbol    | min                 | typ   | max   | Units |

| <b>Digital Filter</b> |                 |                   |           |                     |       |       |       |

| Passband              | (Note 7)        | -0.02dB           | PB        | 0                   |       | 20.0  | kHz   |

|                       |                 | -6.0dB            |           | -                   | 22.05 | -     | kHz   |

| Stopband              |                 | (Note 7)          | SB        | 24.1                |       |       | kHz   |

| Passband Ripp         | ole             |                   | PR        |                     |       | ±0.02 | dB    |

| Stopband Atte         | nuation         |                   | SA        | 54                  |       |       | dB    |

| Group Delay           |                 | (Note 8)          | GD        | -                   | 20.1  | -     | 1/fs  |

| <b>Digital Filter</b> | + Analog Filter |                   |           |                     |       |       |       |

| Frequency Res         | sponse: 0~20.0k | Hz                | FR        | -                   | ±0.2  | -     | dB    |

Note:7. The passband and stopband frequencies scale with fs.

For example, PB=0.4535\*fs(@±0.02dB), SB=0.546\*fs.

8. The calculating delay time which occurred by digital filtering. This time is from setting the 24bit data of both channels on the input register to the output of analog signal.

|                       | FILTER CHARACTERISTICS (fs=96kHz) |                    |         |      |      |       |       |  |  |

|-----------------------|-----------------------------------|--------------------|---------|------|------|-------|-------|--|--|

| (Ta=25°C; AV          | /DD, DVDD=2.7~3                   | 5.5V; fs=96kHz; DI | EM=OFF) |      |      |       |       |  |  |

| Parameter             |                                   |                    | Symbol  | min  | typ  | max   | Units |  |  |

| <b>Digital Filter</b> |                                   |                    |         |      |      |       |       |  |  |

| Passband              | (Note 7)                          | -0.02dB            | PB      | 0    |      | 43.5  | kHz   |  |  |

|                       |                                   | -6.0dB             |         | -    | 48.0 | -     | kHz   |  |  |

| Stopband              |                                   | (Note 7)           | SB      | 52.5 |      |       | kHz   |  |  |

| Passband Ripp         | ole                               |                    | PR      |      |      | ±0.02 | dB    |  |  |

| Stopband Atte         | enuation                          |                    | SA      | 54   |      |       | dB    |  |  |

| Group Delay           |                                   | (Note 8)           | GD      | -    | 20.1 | -     | 1/fs  |  |  |

| <b>Digital Filter</b> | + Analog Filter                   |                    |         |      |      |       |       |  |  |

| Frequency Res         | sponse: 0~20.0k                   | Hz                 | FR      | _    | ±0.2 | -     | dB    |  |  |

| - •                   | 40.0                              | кНz                |         | -    | ±0.2 | -     | dB    |  |  |

Note:7. The passband and stopband frequencies scale with fs.

For example, PB=0.4535\*fs(@±0.02dB), SB=0.546\*fs.

8. The calculating delay time which occurred by digital filtering. This time is from setting the 24bit data of both channels on the input register to the output of analog signal.

| DIGITAL CHARACTERISTICS (CMOS level input) |                    |        |          |     |          |       |  |  |

|--------------------------------------------|--------------------|--------|----------|-----|----------|-------|--|--|

| (Ta=25°C; AVDD=2.7~5.5V; DVDD=2.           | 7~3.6V; TTL = '    | 'L'')  |          |     |          |       |  |  |

| Parameter                                  |                    | Symbol | min      | typ | max      | Units |  |  |

| High-Level Input Voltage                   |                    | VIH    | 0.7xDVDD | -   | -        | V     |  |  |

| Low-Level Input Voltage                    |                    | VIL    | -        | -   | 0.3xDVDD | V     |  |  |

| High-Level Output Voltage                  |                    |        |          |     |          |       |  |  |

| (TX, MCKO pins:                            | Iout=-100µA)       | VOH    | DVDD-0.5 | -   | -        | V     |  |  |

| (DZF pin:                                  | Iout=-100µA)       | VOH    | AVDD-0.5 | -   | -        | V     |  |  |

| Low-Level Output Voltage                   |                    |        |          |     |          |       |  |  |

| (TX, MCKO, DZF pins:                       | Iout= $100\mu A$ ) | VOL    | -        | -   | 0.5      | V     |  |  |

| (SDA pin:                                  | Iout= 3mA)         | VOL    | -        | -   | 0.4      | V     |  |  |

| Input Leakage Current                      |                    | Iin    | -        | -   | ±10      | μΑ    |  |  |

| DIGITAL CHARACTERISTICS (TTL level input; except for TTL pin) |                           |        |          |     |          |       |  |  |

|---------------------------------------------------------------|---------------------------|--------|----------|-----|----------|-------|--|--|

| (Ta=25°C; AVDD, DVDD=4.5~5.5V                                 | <sup>/</sup> ; TTL = "H") |        |          |     |          |       |  |  |

| Parameter                                                     |                           | Symbol | min      | typ | max      | Units |  |  |

| High-Level Input Voltage                                      | (TTL pin)                 | VIH    | 0.7xDVDD | -   | -        | V     |  |  |

| (All pins                                                     | except for TTL pin)       | VIH    | 2.2      | -   | -        | V     |  |  |

| Low-Level Input Voltage                                       | (TTL pin)                 | VIL    | -        | -   | 0.3xDVDD | V     |  |  |

| (All pins                                                     | except for TTL pin)       | VIL    | -        | -   | 0.8      | V     |  |  |

| High-Level Output Voltage                                     |                           |        |          |     |          |       |  |  |

| (TX, MCKO pins:                                               | Iout= $-100\mu A$ )       | VOH    | DVDD-0.5 | -   | -        | V     |  |  |

| (DZF pin:                                                     | Iout= $-100\mu A$ )       | VOH    | AVDD-0.5 | -   | -        | V     |  |  |

| Low-Level Output Voltage                                      |                           |        |          |     |          |       |  |  |

| (TX, MCKO, DZF pin                                            | ns: Iout= $100\mu A$ )    | VOL    | -        | -   | 0.5      | V     |  |  |

| (SDA pin:                                                     | Iout= $3mA$ )             | VOL    | -        | -   | 0.4      | V     |  |  |

| Input Leakage Current                                         |                           | Iin    | -        | -   | ±10      | μΑ    |  |  |

#### MS0016-E-02

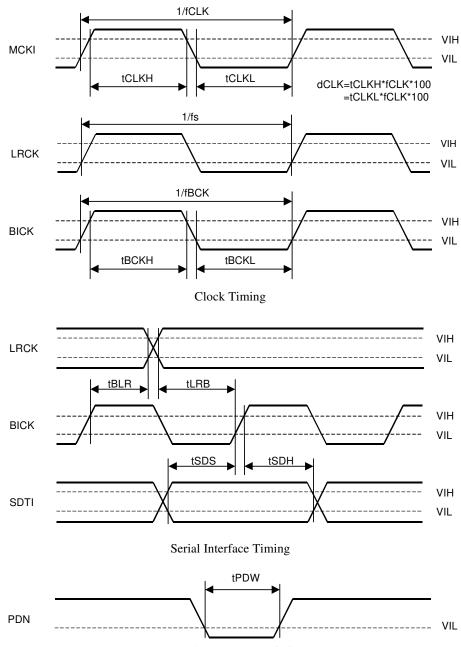

| SWITCHING CHARACTERISTICS                            |        |         |     |        |       |  |  |  |

|------------------------------------------------------|--------|---------|-----|--------|-------|--|--|--|

| (Ta=25°C; AVDD, DVDD=2.7~5.5V; C <sub>L</sub> =20pF) |        |         |     |        |       |  |  |  |

| Parameter                                            | Symbol | min     | typ | max    | Units |  |  |  |

| Master Clock Input:                                  |        |         |     |        |       |  |  |  |

| Frequency                                            |        |         |     |        |       |  |  |  |

| 128fs/256fs/512fs/1024fs                             | fCLK   | 4.096   |     | 24.576 | MHz   |  |  |  |

| 192fs/384fs/768fs/1536fs                             | fCLK   | 6.144   |     | 36.864 | MHz   |  |  |  |

| Duty Cycle                                           | dCLK   | 40      |     | 60     | %     |  |  |  |

| LRCK: (Note 9)                                       |        |         |     |        |       |  |  |  |

| Frequency                                            |        |         |     |        |       |  |  |  |

| Half Speed Mode (DFS1-0 = "11")                      | fsh    | 16      |     | 24     | kHz   |  |  |  |

| Normal Speed Mode (DFS1-0 = "00")                    | fsn    | 32      |     | 48     | kHz   |  |  |  |

| Double Speed Mode (DFS1-0 = "01")                    | fsd    | 64      |     | 96     | kHz   |  |  |  |

| Duty Cycle                                           | Duty   | 45      |     | 55     | %     |  |  |  |

| Serial Interface Timing:                             |        |         |     |        |       |  |  |  |

| BICK Period                                          |        |         |     |        |       |  |  |  |

| Half Speed Mode                                      | tBCK   | 1/128fs |     |        | ns    |  |  |  |

| Normal Speed Mode                                    | tBCK   | 1/128fs |     |        | ns    |  |  |  |

| Double Speed Mode                                    | tBCK   | 1/64fs  |     |        | ns    |  |  |  |

| BICK Pulse Width Low                                 | tBCKL  | 70      |     |        | ns    |  |  |  |

| BICK Pulse Width High                                | tBCKH  | 70      |     |        | ns    |  |  |  |

| BICK "↑" to LRCK Edge (Note 10)                      | tBLR   | 40      |     |        | ns    |  |  |  |

| LRCK Edge to BICK "↑" (Note 10)                      | tLRB   | 40      |     |        | ns    |  |  |  |

| SDTI Hold Time                                       | tSDH   | 40      |     |        | ns    |  |  |  |

| SDTI Setup Time                                      | tSDS   | 40      |     |        | ns    |  |  |  |

| Power-down & Reset Timing                            |        |         |     |        |       |  |  |  |

| PDN Pulse Width (Note 11)                            | tPDW   | 150     |     |        | ns    |  |  |  |

Note: 9. If sampling speed mode (DFS0-1) changes, please reset by PDN pin or RSTN bit.

10. BICK rising edge must not occur at the same time as LRCK edge. 11. The AK4353 can be reset by PDN pin "L" upon power up.

If CKS0-2 or DFS0-1 changes, the AK4353 should be reset by PDN pin or RSTN bit.

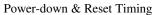

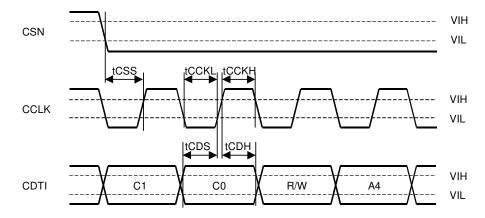

| Parameter                                              | Symbol  | min  | typ | max | Units |

|--------------------------------------------------------|---------|------|-----|-----|-------|

| Control Interface Timing (3-wire Serial mode):         |         |      |     |     |       |

| CCLK Period                                            | tCCK    | 200  |     |     | ns    |

| CCLK Pulse Width Low                                   | tCCKL   | 80   |     |     | ns    |

| Pulse Width High                                       | tCCKH   | 80   |     |     | ns    |

| CDTI Setup Time                                        | tCDS    | 40   |     |     | ns    |

| CDTI Hold Time                                         | tCDH    | 40   |     |     | ns    |

| CSN "H" Time                                           | tCSW    | 150  |     |     | ns    |

| CSN " $\downarrow$ " to CCLK " $\uparrow$ "            | tCSS    | 50   |     |     | ns    |

| CCLK "↑" to CSN "↑"                                    | tCSH    | 50   |     |     | ns    |

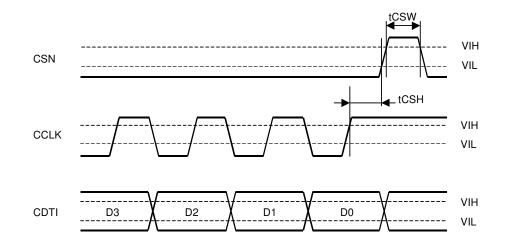

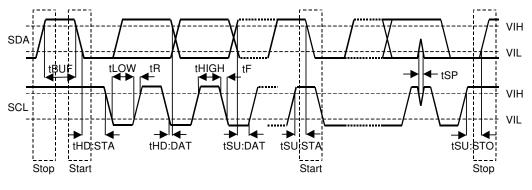

| Control Interface Timing (I <sup>2</sup> C Bus mode):  |         |      |     |     |       |

| SCL Clock Frequency                                    | fSCL    | -    |     | 100 | kHz   |

| Bus Free Time Between Transmissions                    | tBUF    | 4.7  |     | -   | μs    |

| Start Condition Hold Time (prior to first clock pulse) | tHD:STA | 4.0  |     | -   | μs    |

| Clock Low Time                                         | tLOW    | 4.7  |     | -   | μs    |

| Clock High Time                                        | tHIGH   | 4.0  |     | -   | μs    |

| Setup Time for Repeated Start Condition                | tSU:STA | 4.7  |     | -   | μs    |

| SDA Hold Time from SCL Falling (Note 12)               | tHD:DAT | 0    |     | -   | μs    |

| SDA Setup Time from SCL Rising                         | tSU:DAT | 0.25 |     | -   | μs    |

| Rise Time of Both SDA and SCL Lines                    | tR      | -    |     | 1.0 | μs    |

| Fall Time of Both SDA and SCL Lines                    | tF      | -    |     | 0.3 | μs    |

| Setup Time for Stop Condition                          | tSU:STO | 4.0  |     | -   | μs    |

| Pulse Width of Spike Noise Suppressed by Input Filter  | tSP     | 0    |     | 50  | ns    |

Note: 12. Data must be held for sufficient time to bridge the 300 ns transition time of SCL.

#### Timing Diagram

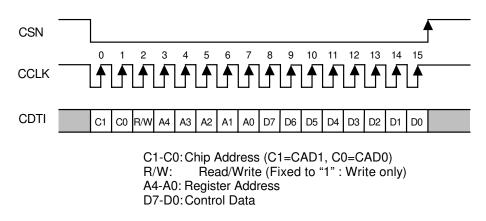

WRITE Command Input Timing (3-wire Serial mode)

WRITE Data Input Timing (3-wire Serial mode)

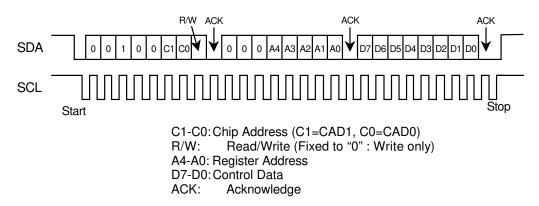

I<sup>2</sup>C Bus mode Timing

#### **OPERATION OVERVIEW**

#### System Clock Input

The external clocks which are required to operate the AK4353 are MCKI, LRCK and BICK. The master clock (MCKI) should be synchronized with sampling clock (LRCK) but the phase is not critical. MCKI is used to operate the digital interpolation filter and the delta-sigma modulator. The frequency of MCKI can be set by CKS2-0, and can be selected to half, normal or double speed mode by DFS1-0 (See Table 1).

All external clocks (MCKI,BICK,LRCK) should always be present whenever the AK4353 is in the normal operation mode (PDN = "H"). If these clock are not provided, the AK4353 may draw excess current and may not possibly operate properly because the device utilizes dynamic refreshed logic internally. If the external clocks are not present, the AK4353 should be in the power-down mode (PDN = "L") or in the reset mode (RSTN = "0"). After exiting reset at power-up etc., the AK4353 is in the power-down mode until MCKI and LRCK are input.

When the register data of CKS2-0 or DFS1-0 is changed during normal operation, the AK4353 should be reset by PDN pin "L" or RSTN bit "0".

|      |      |      |              |                |                | _      |

|------|------|------|--------------|----------------|----------------|--------|

|      |      |      |              | DFS1-0         |                |        |

| CKS2 | CKS1 | CKS0 | "11"         | "00"           | "01"           |        |

|      |      |      | (Half speed) | (Normal speed) | (Double speed) |        |

| 0    | 0    | 0    | 512fs        | 256fs          | 128fs          | defaul |

| 0    | 0    | 1    | 256fs        | 256fs          | 256fs          |        |

| 0    | 1    | 0    | 768fs        | 384fs          | 192fs          |        |

| 0    | 1    | 1    | 384fs        | 384fs          | 384fs          |        |

| 1    | 0    | 0    | 1024fs       | 512fs          | 256fs          | -      |

| 1    | 0    | 1    | 512fs        | 512fs          | N/A            |        |

| 1    | 1    | 0    | 1536fs       | 768fs          | 384fs          |        |

| 1    | 1    | 1    | 768fs        | 768fs          | N/A            |        |

Table 1. System Clock (DFS1-0="10": reserved)

default (DFS1-0 = "00")

| fs [kHz] | Mode   | 128fs   | 192fs   | 256fs   | 384fs   | 512fs   | 768fs   | 1024fs  | 1536fs  |

|----------|--------|---------|---------|---------|---------|---------|---------|---------|---------|

| 16       | Half   | -       | -       | 4.0960  | 6.1440  | 8.1920  | 12.2880 | 16.3840 | 24.5760 |

| 32       | Normal | -       | -       | 8.1920  | 12.2880 | 16.3840 | 24.5760 | -       | -       |

| 64       | Double | 8.1920  | 12.2880 | 16.3840 | 24.5760 | -       | -       | -       | -       |

| 22.05    | Half   | -       | -       | 5.6448  | 8.4672  | 11.2896 | 16.9344 | 22.5792 | 33.8688 |

| 44.1     | Normal | -       | -       | 11.2896 | 16.9344 | 22.5792 | 33.8688 | -       | -       |

| 88.2     | Double | 11.2896 | 16.9344 | 22.5792 | 33.8688 | -       | -       | -       | -       |

| 24       | Half   | -       | -       | 6.1440  | 9.2160  | 12.2880 | 18.4320 | 24.5760 | 36.8640 |

| 48       | Normal | -       | -       | 12.2880 | 18.4320 | 24.5760 | 36.8640 | -       | -       |

| 96       | Double | 12.2880 | 18.4320 | 24.5760 | 36.8640 | -       | -       | -       | -       |

Table 2. Example of System Clock [MHz]

#### ■ Audio Serial Interface Format

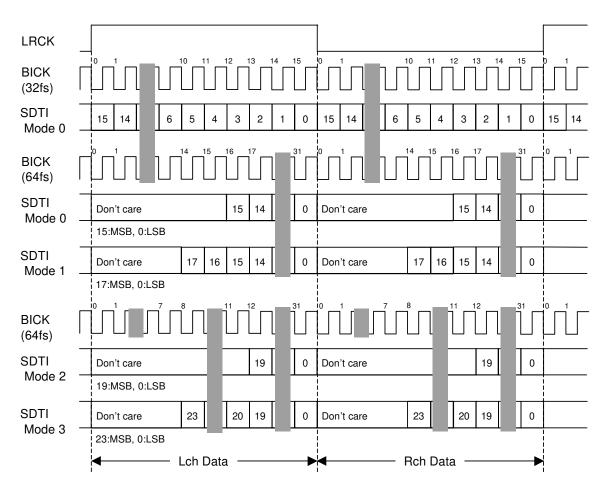

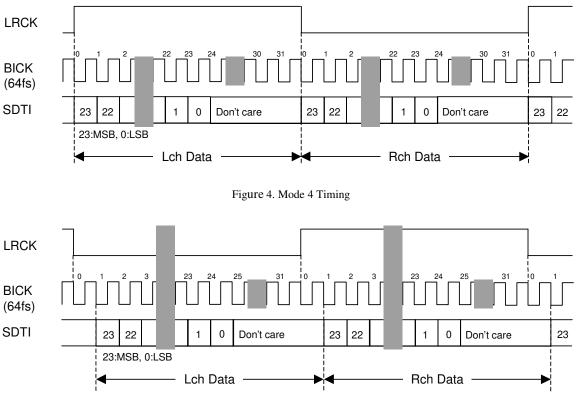

Data is shifted in via the SDTI pin using BICK and LRCK inputs. 6 serial data modes are supported and selected by register data of DIF2-0 as shown in Table 3. In all modes the serial data is MSB-first, 2's compliment format and is latched on the rising edge of BICK. Mode 4 can be used for 20, 18 and 16 MSB justified formats by zeroing the unused LSBs.

| Mode | DIF2 | DIF1 | DIF0   | SDTI                 | L/R | BICK  |         |

|------|------|------|--------|----------------------|-----|-------|---------|

| 0    | 0    | 0    | 0      | 16bit, LSB justified | H/L | ≥32fs |         |

| 1    | 0    | 0    | 1      | 18bit, LSB justified | H/L | ≥36fs |         |

| 2    | 0    | 1    | 0      | 20bit, LSB justified | H/L | ≥40fs |         |

| 3    | 0    | 1    | 1      | 24bit, LSB justified | H/L | ≥48fs |         |

| 4    | 1    | 0    | 0      | 24bit, MSB justified | H/L | ≥48fs |         |

| 5    | 1    | 0    | 1      | $I^2S$               | L/H | ≥48fs | default |

| 6    | 1    | 1    | 0      | Reserved             |     |       |         |

| 7    | 1    | 1    | 1      | Reserved             |     |       |         |

|      |      |      | T 11 C |                      |     |       |         |

Table 3. Audio Data Format

Figure 3. Mode 0-3 Timing

Figure 5. Mode 5 Timing

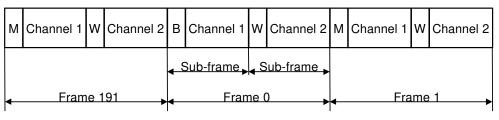

#### Data Transmission Format

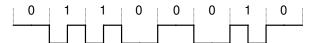

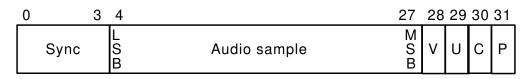

Data input via SDTI pin is formatted in digital interface format and output via TX pin. Data transmitted on the TX output is formatted in blocks as shown in figure 6. Each block consists of 192 frames. A frame of data contains two sub-frames. A sub-frame consists of 32 bits of information. Each data bit received is coded using a bi-phase mark encoding as a two binary state symbol. The preambles violate bi-phase encoding so they may be differentiated from data. In bi-phase encoding, the first state of an input symbol is always the inverse of the last state of the previous data symbol. For a logic 0, the second state of the symbol is the same as the first state. For a 1, the second state is the opposite of the first. Figure 7 illustrates a sample stream of 8 data bits encoded in 16 symbol states.

Figure 6. Block format

Figure 7. A biphase-encoded bit stream

The sub-frame is defined in the figure below:

- Bits 0-3 of the sub-frame represent a preamble for synchronization. There are three preambles:

The block preamble, B, is contained in the first sub-frame of Frame 0.

The channel 1 preamble, M, is contained in the first sub-frame of all other frames.

The channel 2 preamble, W, is contained in all of the second sub-frames.

- Table 4 defines the symbol encoding for each of the preambles.

- Bits 4-27 of the sub-frame contain the 24 bit audio sample in 2's complement format with bit 27 as the most significant bit (MSB). For 16 bit mode, Bits 4-11 are all 0.

- Bit 28 is the validity flag. This is equal to V bit in the register.

- Bit 29 is a user data bit. This is always "0" in the AK4353.

- Bit 30 is a channel status bit. Frame 0 contains the first bit of the 192 bit word with the last bit in frame 191.

- Bit 31 is an even parity bit for bits 4-31 of the sub-frame.

Figure 8. Sub-frame format

The block of data contains consecutive frames transmitted at a bit rate of 64 times the sample frequency, fs.

| Preamble | Preceding state $= 0$ | Preceding state = 1 |

|----------|-----------------------|---------------------|

| В        | 11101000              | 00010111            |

| М        | 11100010              | 00011101            |

| W        | 11100100              | 00011011            |

Table 4. Sub-frame preamble encoding

Figure 9 shows the relation between input data to SDTI pin and audio data on sub-frame.

Figure 9. Relation between input data to SDTI pin and audio data on sub-frame

A digital de-emphasis filter is available for 32, 44.1 or 48kHz sampling speed (tc= $50/15\mu$ s). It is enabled or disabled with the control register data of DEM1-0 and DFS1-0. The de-emphasis filter is disabled at half/double sampling mode.

| DEM1 | DEM0 | De-emphasis |         |

|------|------|-------------|---------|

| 0    | 0    | 44.1kHz     |         |

| 0    | 1    | OFF         | default |

| 1    | 0    | 48kHz       |         |

| 1    | 1    | 32kHz       |         |

Table 5. De-emphasis filter control with DEM1-0 (DFS1-0="00")

| DFS1 | DFS0 | De-emphasis  |         |

|------|------|--------------|---------|

| 0    | 0    | See Table 5. | default |

| 0    | 1    | OFF          |         |

| 1    | 0    | OFF          |         |

| 1    | 1    | OFF          |         |

Table 6. De-emphasis filter control with DFS1-0

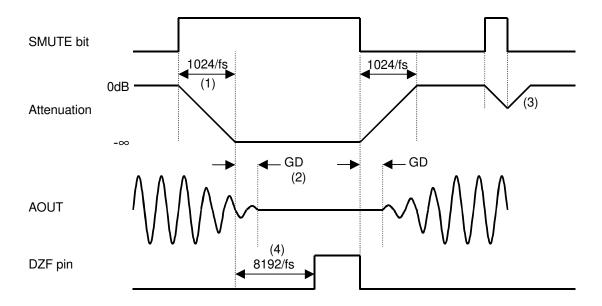

#### Zero detection

When the input data at both channels is continuously zeros for 8192 LRCK cycles, DZF pin goes to "H". DZF pin immediately goes to "L" if input data is not zero after going DZF "H". If RSTN bit becomes "0", DZF pin goes to "H". DZF pin goes to "L" at 4~5/fs after RSTN bit returns to "1".

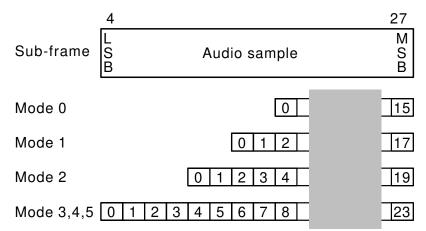

#### ■ Soft mute operation

Soft mute operation is performed at digital domain. When the serial control register data of SMUTE goes "1", the output signal is attenuated by  $-\infty$  during 1024 LRCK cycles. When SMUTE is returned to "0", the mute is cancelled and the output attenuation gradually changes to 0dB during 1024 LRCK cycles. If the soft mute is cancelled within 1024 LRCK cycles after starting the operation, the attenuation is discontinued and returned to 0dB. The soft mute is effective for changing the signal source without stopping the signal transmission.

Notes:

- (1) The output signal is attenuated by  $-\infty$  during 1024 LRCK cycles (1024/fs).

- (2) Analog output corresponding to digital input have the group delay (GD).

- (3) If the soft mute is cancelled within 1024 LRCK cycles, the attenuation is discontinued and returned to 0dB.

- (4) When the input data at both channels are continuously zeros for 8192 LRCK cycles, DZF pin goes to "H". DZF pin immediately goes to "L" if input data are not zero after going DZF "H".

Figure 10. Soft mute and zero detection

#### Power-down

The DAC is placed in the power-down mode by bringing PDN pin "L" and the digital filter is also reset at the same time. The internal register values are initialized by PDN "L". This reset should always be done after power-up. Because some click noise occurs at the edge of PDN, the analog output should be muted externally if the click noise influences system application.

| PDN                  |                  |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------|------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Internal<br>State    | Normal Operation | Power-down | Normal Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| D/A In<br>(Digital)  |                  | "0" data   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| D/A Out              | → GD (1)         | (3) (2)    | (3) $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ $(3)$ |

| (Analog)<br>Clock In |                  | (4)        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| MCKI, LRCK, BICK     |                  | Don't care |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DZF                  |                  | (6)        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| External<br>MUTE     | (5)              | Mute ON    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

Notes:

- (1) The analog output corresponding to digital input has the group delay (GD).

- (2) Analog outputs are floating (Hi -Z) at the power-down mode.

- (3) Click noise occurs at the edge of PDN signal. This noise is output even if "0" data is input.

- (4) The external clocks (MCKI, BICK and LRCK) can be stopped in the power-down mode (PDN = "L").

- (5) Please mute the analog output externally if the click noise (3) influences system application. The timing example is shown in this figure.

- (6) DZF pin is "L" in the power-down mode (PDN = "L").

Figure 11. Power-down/up sequence example

#### Reset function

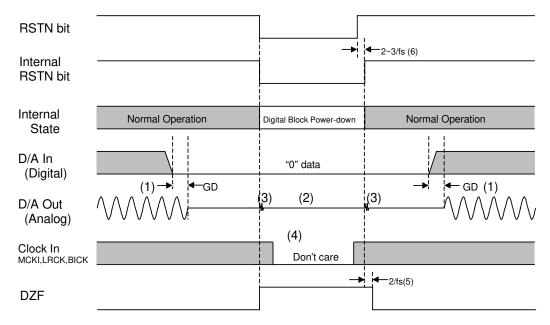

When RSTN = "0", the DAC is powered down but the internal register values are not initialized. The analog outputs go to VCOM voltage and DZF pin goes to "H". Figure 12 shows the sequence of reset by RSTN bit.

#### Notes:

- (1) The analog output corresponding to digital input has the group delay (GD).

- (2) Analog outputs go to VCOM voltage.

- (3) Click noise occurs at the edges("↑↓") of the internal timing of RSTN bit. This noise is output even if "0" data is input.

- (4) The external clocks (MCKI, BICK and LRCK) can be stopped in the reset mode (RSTN = "L").

- (5) DZF pin goes to "H" when the RSTN bit becomes "0", and goes to "L" at 4~5/fs after RSTN bit becomes "1".

- (6) There is a delay, 2~3/fs from RSTN bit "1" to the internal RSTN "1".

Figure 12. Reset sequence example

#### Serial Control Interface

The AK4353 can control its functions via registers. Internal registers may be written by 2 types of control mode. The chip address is determined by the state of the CAD0 and CAD1 inputs. PDN = "L" initializes the registers to their default values. Writing "0" to the RSTN bit can initialize the internal timing circuit. But in this case, the register data is not be initialized.

(1) 3-wire Serial Control Mode (I2C = "L")

Internal registers may be written to the 3 wire  $\mu$ P interface pins (CSN,CCLK and CDTI). The data on this interface consists of Chip address (2bits, CAD0/1), Read/Write (1bit, Fixed to "1"; Write only), Register address (MSB first, 5bits) and Control data (MSB first, 8bits). Address and data is clocked in on the rising edge of CCLK and data is clocked out on the falling edge. For write operations, data is latched after a low-to-high transition of CSN. The clock speed of CCLK is 5MHz(max). The CSN and CCLK pins should be held to "H" except for access.

(2) I<sup>2</sup>C Bus Control Mode (I2C = "H")

Internal registers may be written to  $I^2C$  Bus interface pins: SCL & SDA. The data on this interface consists of Chip address (2bits, CAD0/1), Read/Write (1bit, Fixed to "0"; Write only), Register address (MSB first, 5bits) and Control data (MSB first, 8bits). Address and data is clocked in on the rising edge of SCL and data is clocked out on the falling edge. Data can be written after a high-to-low transition of SDA when SCL is "H"(start condition), and is latched after a low-to-high transition of SDA when SCL is "H"(stop condition). The clock speed of SCL is 100kHz(max). The CSN pin should be connected to DVDD at I<sup>2</sup>C Bus control mode. The AK4353 does not have a register address auto increment capability.

\* When the AK4353 is in the power down mode (PDN = "L") or the MCLK is not provided, writing into the control register is inhibited.

#### Mapping of Program Registers

| Addr | Register Name    | D7   | D6   | D5   | D4   | D3   | D2   | D1   | D0    |

|------|------------------|------|------|------|------|------|------|------|-------|

| 00H  | Control 1        | 0    | 0    | 0    | 0    | DIF2 | DIF1 | DIF0 | RSTN  |

| 01H  | Control 2        | 0    | 0    | DFS1 | DFS0 | CKS2 | CKS1 | CKS0 | RSTN  |

| 02H  | Control 3        | PL3  | PL2  | PL1  | PL0  | DEM1 | DEM0 | ATC  | SMUTE |

| 03H  | Lch ATT          | ATT7 | ATT6 | ATT5 | ATT4 | ATT3 | ATT2 | ATT1 | ATT0  |

| 04H  | Rch ATT          | ATT7 | ATT6 | ATT5 | ATT4 | ATT3 | ATT2 | ATT1 | ATT0  |

| 05H  | TX               | 0    | 0    | 0    | 0    | 0    | 0    | V    | TXE   |

| 06H  | Channel Status 1 | 0    | CS29 | CS28 | CS25 | CS24 | CS3  | CS2  | CS1   |

| 07H  | Channel Status 2 | CS15 | CS14 | CS13 | CS12 | CS11 | CS10 | CS9  | CS8   |

Note: For addresses from 08H to 1FH, data should not be written.

When PDN goes to "L", the registers are initialized to their default values.

When RSTN bit goes to "0", the internal timing is reset, DZF pin goes to "H" and registers are not initialized to their default values.

#### Register Definitions

| Addr | Register Name | D7 | D6 | D5 | D4 | D3   | D2   | D1   | D0   |

|------|---------------|----|----|----|----|------|------|------|------|

| 00H  | Control 1     | 0  | 0  | 0  | 0  | DIF2 | DIF1 | DIF0 | RSTN |

|      | Default       | 0  | 0  | 0  | 0  | 1    | 0    | 1    | 1    |

RSTN: Internal timing reset

0: Reset. DZF pin goes to "H" and registers are not initialized.1: Normal operationWhen the states of DIF2-0,CKS2-0 or DFS1-0 changes, the AK4353 should be reset by PDN pin or RSTN bit. Some click noise may occur at that timing.

DIF2-0: Audio data interface modes (See Table 3.) Initial: "101", Mode 5

| Addr | Register Name | D7 | D6 | D5   | D4   | D3   | D2   | D1   | D0   |

|------|---------------|----|----|------|------|------|------|------|------|

| 01H  | Control 2     | 0  | 0  | DFS1 | DFS0 | CKS2 | CKS1 | CKS0 | RSTN |

|      | Default       | 0  | 0  | 0    | 0    | 0    | 0    | 0    | 1    |

RSTN: Internal timing reset

0: Reset. DZF pin goes to "H" and registers are not initialized.

1: Normal operation

When the states of DIF2-0,CKS2-0 or DFS1-0 changes, the AK4353 should be reset by PDN pin or RSTN bit. Some click noise may occur at that timing.

CKS2-0: Clock select (See Table 1.) Initial: "000"

DFS1-0: Half/Normal/Double sampling modes (See Table 1), De-emphasis response (See Table 6.) Initial: "00"

| Addr | Register Name | D7  | D6  | D5  | D4  | D3   | D2   | D1  | D0    |

|------|---------------|-----|-----|-----|-----|------|------|-----|-------|

| 02H  | Control 3     | PL3 | PL2 | PL1 | PL0 | DEM1 | DEM0 | ATC | SMUTE |

|      | Default       | 1   | 0   | 0   | 1   | 0    | 1    | 0   | 0     |

SMUTE: Soft Mute Enable

0: Normal operation

1: DAC outputs soft-muted

ATC: Attenuation Control

0: The attenuation data for each register is applied separately to left and right channels.

1: The attenuation data loaded in addr=03H is used for both left and right channels.

DEM1-0: De-emphases response (See Table 5,6.) Initial: "01", OFF

#### PL3-0: Mixing mode

| PL3 | PL2 | PL1 | PL0 | Lch Output | Rch Output | Note    |         |

|-----|-----|-----|-----|------------|------------|---------|---------|

| 0   | 0   | 0   | 0   | MUTE       | MUTE       | MUTE    |         |

| 0   | 0   | 0   | 1   | MUTE       | R          |         |         |

| 0   | 0   | 1   | 0   | MUTE       | L          |         |         |

| 0   | 0   | 1   | 1   | MUTE       | (L+R)/2    |         |         |

| 0   | 1   | 0   | 0   | R          | MUTE       |         |         |

| 0   | 1   | 0   | 1   | R          | R          |         |         |

| 0   | 1   | 1   | 0   | R          | L          | REVERSE |         |

| 0   | 1   | 1   | 1   | R          | (L+R)/2    |         |         |

| 1   | 0   | 0   | 0   | L          | MUTE       |         |         |

| 1   | 0   | 0   | 1   | L          | R          | STEREO  | default |

| 1   | 0   | 1   | 0   | L          | L          |         |         |

| 1   | 0   | 1   | 1   | L          | (L+R)/2    |         |         |

| 1   | 1   | 0   | 0   | (L+R)/2    | MUTE       |         |         |

| 1   | 1   | 0   | 1   | (L+R)/2    | R          |         |         |

| 1   | 1   | 1   | 0   | (L+R)/2    | L          |         |         |

| 1   | 1   | 1   | 1   | (L+R)/2    | (L+R)/2    | MONO    |         |

Table 7. Programmable Output Format

| STEREO:          | Normal stereo output |

|------------------|----------------------|

| <b>REVERSE</b> : | L/R Reverse output   |

| MONO:            | Monaural output      |

| MUTE:            | Soft mute operation  |

| MUTE.            | Soft mule operation  |