Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Two Outputs Clock Generator **AK8146B**

#### **Features**

- Pin Selectable External Input

- 74.17582MHz

- 74.25MHz

- 60MHz

- Clock out Frequencies:

- 12.000MHz

- 13.5MHz

- Low Jitter Performance

- Period Jitter

125 psec (max) at CLK1

205 psec (max) at CLK2

- Low Current Consumption:

5.0mA (Typ.) at 3.0V

Supply Voltage:

2.7 - 3.3V

Operating Temperature Range:

-20 to +85°C

Package:

8-pin USON (Lead free) 2.2mm x 2.2mm

#### **Description**

The AK8146B is a low power multi clock generator which generates different frequency clocks from a external clock input. It provides two outputs of 12MHz and 13.5MHz. PLL in AK8146B are derived from AKEMD's long-term-experienced clock device technology, and enable clock output to perform low jitter and to operate with very low current consumption. The AK8146B is available in a 8-pin USON package.

#### **Applications**

Digital Video Camera

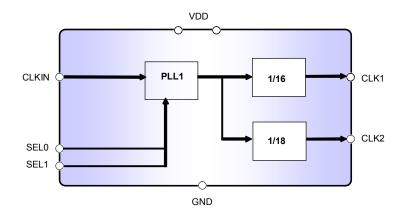

#### **Block Diagram**

AK8146B Multi Clock Generator

## **Pin Descriptions**

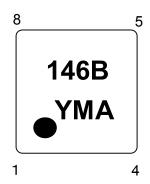

Package: 8-Pin USON(Top View)

| Pin<br>No. | Pin<br>Name | Pin<br>Type | Description                                                                                                                                                                      |

|------------|-------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | SEL0        | IN          | SEL0 and SEL1 pins select the external clock frequency from among 74.17582MHz, 74.25MHz and 60MHz. Please refer to the table of External clock frequency selection" shown below. |

| 2          | GND         | PWR         | Ground                                                                                                                                                                           |

| 3          | VDD         | PWR         | Power                                                                                                                                                                            |

| 4          | CLK1        | OUT         | 12.0 MHz clock output                                                                                                                                                            |

| 5          | CLK2        | OUT         | 13.5 MHz clock output                                                                                                                                                            |

| 6          | SEL1        | IN          | External clock frequency selection pin. Same as SEL0.                                                                                                                            |

| 7          | VDD         | PWR         | Power                                                                                                                                                                            |

| 8          | CLKIN       | IN          | External clock input pin. It accepts one of the four frequencies selected by SEL0 and SEL1.                                                                                      |

| SEL1 | SEL0 | Input Frequency                |

|------|------|--------------------------------|

| 0    | 0    | 74.17582MHz (=74.25 MHz/1.001) |

| 0    | 1    | 74.25 MHz                      |

| 1    | 0    | Not in use                     |

| 1    | 1    | 60.0 MHz                       |

# **Ordering Information**

| Part Number | Marking | Shipping<br>Packaging | Package    | Temperature<br>Range |  |  |

|-------------|---------|-----------------------|------------|----------------------|--|--|

| AK8146B     | 146B    | Tape and Reel         | 8-pin USON | -20 to 85 °C         |  |  |

#### **Absolute Maximum Rating**

Over operating free-air temperature range unless otherwise noted (1)

| Items                                    | Symbol          | Ratings            | Unit |

|------------------------------------------|-----------------|--------------------|------|

| Supply voltage                           | VDD             | -0.3 to 4.6        | V    |

| Input voltage                            | Vin             | VSS-0.3 to VDD+0.3 | V    |

| Input current (any pins except supplies) | I <sub>IN</sub> | ±10                | mA   |

| Storage temperature                      | Tstg            | -55 to 130         | °C   |

#### Note

(1) Stress beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" is not implied. Exposure to absolute-maximum-rating conditions for extended periods may affect device reliability. Electrical parameters are guaranteed only over the recommended operating temperature range.

#### **ESD Sensitive Device**

This device is manufactured on a CMOS process, therefore, generically susceptible to damage by excessive static voltage. Failure to observe proper handling and installation procedures can cause damage. AKEMD recommends that this device is handled with appropriate precautions.

#### **Recommended Operation Conditions**

| Parameter               | Symbol | Conditions     | Min | Тур | Max | Unit |

|-------------------------|--------|----------------|-----|-----|-----|------|

| Operating temperature   | Та     |                | -20 |     | 85  | °C   |

| Supply voltage (1)      | VDD    |                | 2.7 | 3.0 | 3.3 | V    |

| Output Load Capacitance | Cp1    | Pin: CLK1,CLK2 |     |     | 15  | pF   |

#### Note:

(1) Power to VDD requires to be supplied from a single source. A decoupling capacitor of  $0.1\mu F$  for power supply line should be installed close to each VDD pin.

MS0994-E-00 Oct-2008

#### **DC Characteristics**

All specifications at VDD: over 2.7 to 3.3V, Ta: -20 to +85°C, unless otherwise noted

| Parameter                   | Symbol          | Conditions              | MIN     | TYP | MAX      | Unit |

|-----------------------------|-----------------|-------------------------|---------|-----|----------|------|

| High Level Input Voltage    | $V_{IH}$        | Pin: SEL0 SEL1          | 0.7*VDD |     |          | V    |

| Low Level Input Voltage     | $V_{IL}$        | Pin: SEL0 SEL1          |         |     | 0.3*VDD  | V    |

| Input Leakage Current       | lι              | Pin: SEL0 SEL1          | -10     |     | +10      | μΑ   |

| High Lovel Output Voltage 1 | V               | Pin: CLK1, CLK2         | 0.8VDD  |     |          | V    |

| High Level Output Voltage 1 | V <sub>OH</sub> | I <sub>OH</sub> =-4.0mA |         |     |          | V    |

| Low level Output Voltage 1  | V               | Pin: CLK1, CLK2         |         |     | 0.2VDD   | V    |

| Low level Output Voltage 1  | V <sub>OL</sub> | I <sub>OL</sub> =+4.0mA |         |     | 0.2000   | V    |

| High Lovel Output Voltage 2 | V <sub>OH</sub> | Pin: CLK1, CLK2         | 0.9VDD  |     |          | V    |

| High Level Output Voltage 2 |                 | I <sub>OH</sub> =-1.5mA |         |     |          | V    |

| Law layed Output Valtage 2  | V <sub>OL</sub> | Pin: CLK1, CLK2         |         |     | 0.05/100 | V    |

| Low level Output Voltage 2  |                 | I <sub>OL</sub> =+0.1mA |         |     | 0.05VDD  | V    |

|                             | I <sub>DD</sub> | No load, CLKIN=74.25MHz |         |     |          |      |

| Current Consumption         |                 | TYP case is VDD=3.0V,   |         | 5.0 | 6.4      | mA   |

|                             |                 | Ta=25°C                 |         |     |          |      |

#### **AC Characteristics**

All specifications at VDD: over 2.7 to 3.3V, Ta: over -20 to +85°C, unless otherwise noted

| Parameter                                 | Symbol            | Conditions                                         | MIN | TYP                       | MAX | Unit |

|-------------------------------------------|-------------------|----------------------------------------------------|-----|---------------------------|-----|------|

| External Clock Input                      |                   | Pin: CLKIN                                         |     | 74.17582<br>74.25<br>60.0 |     | MHz  |

| External Clock Input                      |                   | Pin: CLKIN                                         | 0.7 |                           |     | Vpp  |

| External Clock Duty                       |                   | Pin: CLKIN,<br>Specified at 0.5*Clock<br>Amplitude | 30  |                           | 70  | %    |

| Period Jitter (1)(2)                      |                   | Pin: CLK1                                          |     |                           | 125 | ps   |

| renou sillei                              |                   | Pin: CLK2                                          |     |                           | 205 | ps   |

| Output Clock Duty<br>Cycle <sup>(1)</sup> |                   | Pin: CLK1                                          | 45  | 50                        | 55  | %    |

| Output Clock Rise Time <sup>(1)</sup>     | t <sub>rise</sub> | Pin: CLK1 ,CLK2<br>Cp1=15pF                        |     |                           | 4.0 | ns   |

| Output Clock Fall Time <sup>(1)</sup>     | t <sub>fall</sub> | Pin: CLK1 ,CLK2<br>Cp1=15pF                        |     |                           | 4.0 | ns   |

| Power-up Time <sup>(3)</sup>              |                   | Pin: CLK1 Cp1=15pF                                 |     | 1.4                       | 2.8 | ms   |

- (1) Design Value

- (2) 5sigma in 10000 sampling

- (3) The time that output reaches the target frequency within accuracy of  $\pm 100$ ppm from the point that the power supply reaches VDD

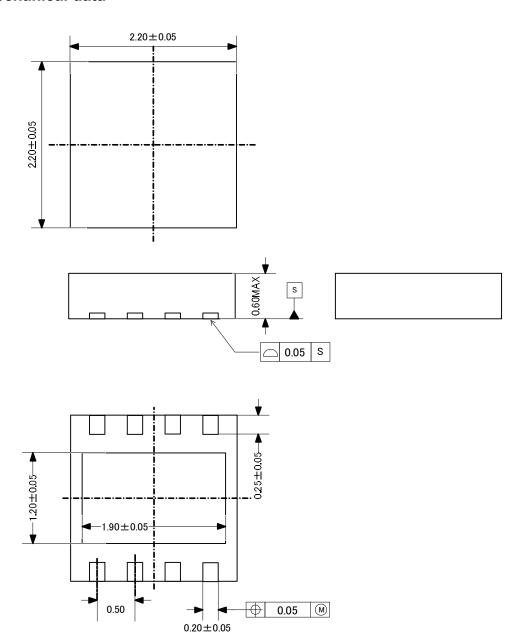

# **Package Information**

#### • Mechanical data

# • Marking

a: #1 Pin Index : Circle b: Part number : 146B c: Date code (3 digits) : YMA

MS0994-E-00 Oct-2008

### IMPORTANT NOTICE

- These products and their specifications are subject to change without notice.

When you consider any use or application of these products, please make inquiries the sales office of Asahi Kasei EMD Corporation (AKEMD) or authorized distributors as to current status of the products.

- AKEMD assumes no liability for infringement of any patent, intellectual property, or other rights in the application or use of any information contained herein.

- Any export of these products, or devices or systems containing them, may require an export license or other official approval under the law and regulations of the country of export pertaining to customs and tariffs, currency exchange, or strategic materials.

- AKEMD products are neither intended nor authorized for use as critical components<sub>Note1)</sub> in any safety, life support, or other hazard related device or system<sub>Note2)</sub>, and AKEMD assumes no responsibility for such use, except for the use approved with the express written consent by Representative Director of AKEMD. As used here:

- Note1) A critical component is one whose failure to function or perform may reasonably be expected to result, whether directly or indirectly, in the loss of the safety or effectiveness of the device or system containing it, and which must therefore meet very high standards of performance and reliability.

- Note2) A hazard related device or system is one designed or intended for life support or maintenance of safety or for applications in medicine, aerospace, nuclear energy, or other fields, in which its failure to function or perform may reasonably be expected to result in loss of life or in significant injury or damage to person or property.

- It is the responsibility of the buyer or distributor of AKEMD products, who distributes, disposes of, or otherwise places the product with a third party, to notify such third party in advance of the above content and conditions, and the buyer or distributor agrees to assume any and all responsibility and liability for and hold AKEMD harmless from any and all claims arising from the use of said product in the absence of such notification.