# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

### Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## AK8160B2

Low Power & Low Jitter Clock Generator for PCI Express

#### **1. General Description**

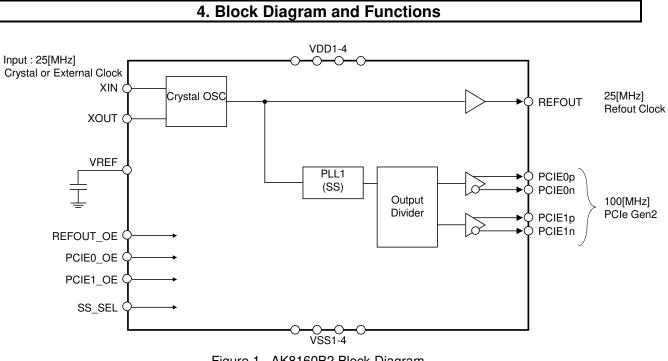

The AK8160B2 is a member of AKM's low power and low jitter clock generator family designed for PCI Express generation 2.0. This device has one PLL with spread spectrum (SS) function and enables to output high quality differential 100MHz as PCI Express clock and 25MHz as reference simultaneously.

#### 2. Features

- Low Current Consumption 31mA Typ. (Full function, 25MHz output and 100MHz output)

25MHz Crystal Input or External Clock Input

- One single-end 25MHz-Reference Output without Spread Spectrum

- Two differential 100MHz Clock Outputs with Spread Spectrum Selectable Spread Spectrum ON / OFF

- Spread Spectrum Modulation ratio 0% (Off), -0.5%

- Spread Spectrum Modulation frequency 30kHz to 33kHz

- Low Jitter Performance of 100MHz Output Clock RMS Jitter: 2.6ps Max. (PCIE0p-1p/0n-1n pin, BW=10kHz – 1.5MHz) 2.6ps Max. (PCIE0p-1p/0n-1n pin, BW=1.5MHz – 50MHz)

Cycle to Cycle Jitter: 125ps Max. (PCIE0p-1p/0n-1n pin)

23ps Typ. (1σ), (REFOUT pin)

- Supply Voltage

3.0V 3.6V

- Operating Temperature Range -40°C to +85°C

- Package

- 0.4mm pitch 3mm x 3mm 20-pin QFN (Lead free)

- Application

- DSLR : Digital Single-Lens Reflex camera

- Network apparatus, Server, Datacenter

- MFP : Multi-Function Printer

- Game

#### 3. Table of Contents

| 1. General Description               |

|--------------------------------------|

| 2. Features1                         |

| 3. Table of Contents2                |

| 4. Block Diagram and Functions       |

| 5. Pin Configurations and Functions4 |

| 6. Absolute Maximum Ratings          |

| 7. Recommended Operating Conditions6 |

| 8. Electrical Characteristics7       |

| 9. Recommended External Circuits     |

| 10. Package14                        |

| 11. Important Notice                 |

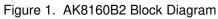

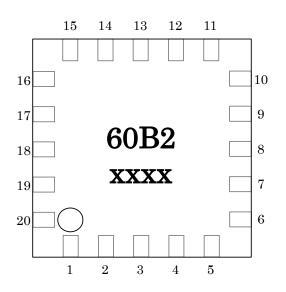

#### 5. Pin Configurations and Functions

| Fiaure 2. | AK8160B2 Package: 20-Pin QFN | (Top View) |

|-----------|------------------------------|------------|

|           |                              | (          |

| Pin No. | Pin Name | Pin Type | Description                                                                                                                                                            |

|---------|----------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | SS_SEL   | DI       | SS Modulation Control Pin<br>This pin must be connected to "H" or "L".<br>SS_SEL = "L" : Modulation ratio is 0[%] (Off)<br>SS_SEL = "H" : Modulation ratio is -0.5 [%] |

| 2       | VSS3     | PWR      | Ground pin 3                                                                                                                                                           |

| 3       | VDD3     | PWR      | Power Supply Pin 3                                                                                                                                                     |

| 4       | VREF     | AO       | Reference Voltage Generation Pin<br>This pin must be connected to 1µF capacitor.<br>This pin goes to Hi-Z when power down.                                             |

| 5       | VDD4     | PWR      | Power Supply Pin 4                                                                                                                                                     |

| 6       | VSS4     | PWR      | Ground Pin 4                                                                                                                                                           |

| 7       | PCIE1p   | DO       | PCI Express Gen2 Clock Output pin 1 (Positive)<br>This pin outputs 100MHz.                                                                                             |

| 8       | PCIE1n   | DO       | PCI Express Gen2 Clock Output pin 1 (Negative)<br>This pin outputs 100MHz.                                                                                             |

| 9       | PCIE0p   | DO       | PCI Express Gen2 Clock Output pin 0 (Positive)<br>This pin outputs 100MHz.                                                                                             |

| 10      | PCIE0n   | DO       | PCI Express Gen2 Clock Output pin 0 (Negative)<br>This pin outputs 100MHz.                                                                                             |

|    |              |     | PCIE1p/n Output Control Pin                               |

|----|--------------|-----|-----------------------------------------------------------|

|    |              |     | This pin must be connected to "H" or "L".                 |

| 11 | 11 PCIE1_OE  |     | PCIE1_OE = "L" : PCIE1p/n outputs "L".                    |

|    |              |     | $PCIE1_OE = "H" : PCIE1p/n outputs 100MHz.$               |

|    |              |     | PCIE0p/n Output Control Pin                               |

|    |              |     | This pin must be connected to "H" or "L".                 |

| 12 | PCIE0_OE     | DI  | PCIE0_OE = "L" : PCIE0p/n outputs "L".                    |

|    |              |     | $PCIE0_OE = "H" : PCIE0p/n outputs 100MHz.$               |

| 13 | VDD2         | PWR | Power Supply Pin 2                                        |

|    |              |     |                                                           |

| 14 | VSS2         | PWR | Ground Pin 2                                              |

| 15 | 15 XOUT AO   |     | 25MHz Crystal Connection Pin                              |

| 15 |              |     | OPEN when an External Clock Input is used                 |

| 16 | XIN          | AI  | 25MHz Crystal Connection Pin or External Clock Input Pin  |

| 17 | VSS1         | PWR | Ground Pin 1                                              |

| 18 | VDD1         | PWR | Power Supply Pin 1                                        |

| 19 | REFOUT       | DO  | 25MHz Output Pin                                          |

|    |              |     | 25MHz Output Control Pin                                  |

| 20 |              | DI  | This pin must be connected to "H" or "L".                 |

| 20 | 20 REFOUT_OE |     | REFOUT_OE = "L" : REFOUT outputs "L".                     |

|    |              |     | REFOUT_OE = "H" : REFOUT outputs 25MHz.                   |

|    |              |     | Connecting exposed pad of package to board ground must be |

|    | Exposed Pad  |     | required.                                                 |

Note:

AI : Analog input pinAO : Analog output pinDI : Digital input pinDO : Digital output pinPWR : Power supply and Ground pin

#### 6. Absolute Maximum Ratings

| Items                                    | Symbol          | Ratings            | Unit |

|------------------------------------------|-----------------|--------------------|------|

| Supply voltage                           | VDD             | -0.3 to 4.6        | V    |

| Input voltage                            | Vin             | VSS-0.3 to VDD+0.3 | V    |

| Input current (any pins except supplies) | I <sub>IN</sub> | ±10                | mA   |

| Storage temperature                      | Tstg            | -65 to 150         | °C   |

Over operating free-air temperature range unless otherwise noted <sup>(1)</sup>

Note

(1) Stress beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" is not implied. Exposure to absolute-maximum-rating conditions for extended periods may affect device reliability. Electrical parameters are guaranteed only over the recommended operating temperature range.

**ESD Sensitive Device** This device is manufactured on a CMOS process, therefore, generically susceptible to damage by excessive static voltage. Failure to observe proper handling and installation procedures can cause damage. AKM recommends that this device is handled with appropriate precautions.

#### 7. Recommended Operating Conditions

| Parameter                     | Symbol | Conditions    | Min | Тур | Max | Unit |

|-------------------------------|--------|---------------|-----|-----|-----|------|

| Operating temperature         | Та     |               | -40 |     | 85  | °C   |

| Supply voltage <sup>(1)</sup> | VDD    | Pin: VDD1 - 4 | 3.0 | 3.3 | 3.6 | V    |

| Output Load Capacitance       | Cpl    | Pin: REFOUT   |     |     | 25  | pF   |

Note:

Power to VDD1 – VDD4 requires to be supplied from a single source. A decoupling capacitor of 0.1µF for power supply line should be connected close to each VDD pin.

#### 8. Electrical Characteristics

#### **Current Consumption**

All specifications at VDD: over 3.0V to 3.6V, Ta: -40 to +85°C, 25MHz Crystal, unless otherwise noted

| Parameter             | Symbol            | Conditions | Min | Тур | Max | Unit |

|-----------------------|-------------------|------------|-----|-----|-----|------|

| Current Consumption 1 | I <sub>DD</sub> 1 | (1), (2)   |     | 31  | 38  | mA   |

| Current Consumption 2 | I <sub>DD</sub> 2 | (1), (3)   |     | 30  | 37  | mA   |

| Current Consumption 3 | I <sub>DD</sub> 3 | (1), (4)   |     | 0   | 100 | μA   |

#### Note:

(1) REFOUT : No load, PCIE0p/n, PCIE1p/n : CL=2[pF]

- (2) Full function REFOUT output, 100MHz output \*REFOUT\_OE = PCIE0\_OE = PCIE1\_OE = SS\_SEL = "H"

- (3) REFOUT output off, 100MHz output

\*REFOUT\_OE = "L", PCIE0\_OE = PCIE1\_OE = SS\_SEL = "H"

- (4) Full power down\* REFOUT\_OE = PCIE0\_OE = PCIE1\_OE = "L"

#### **DC Characteristics**

All specifications at VDD: over 3.0V to 3.6V, Ta: -40 to +85°C, 25MHz Crystal, unless otherwise noted

| Parameter                 | Symbol           | Conditions                                                  | Min     | Тур | Max     | Unit |

|---------------------------|------------------|-------------------------------------------------------------|---------|-----|---------|------|

| High Level Input Voltage  | $V_{\rm IH}$     | REFOUT_OE pin<br>PCIE0_OE pin<br>PCIE1_OE pin<br>SS_SEL pin | 0.7*VDD |     |         | V    |

| Low Level Input Voltage   | $V_{IL}$         | REFOUT_OE pin<br>PCIE0_OE pin<br>PCIE1_OE pin<br>SS_SEL pin |         |     | 0.3*VDD | V    |

| Input Leakage Current     | $I_L$            | REFOUT_OE pin<br>PCIE0_OE pin<br>PCIE1_OE pin<br>SS_SEL pin | -1      |     | +1      | μΑ   |

| VREF Output Voltage       | $V_{\text{REF}}$ | VREF pin<br>C <sub>VREF</sub> = 1µF                         | 0.72    | 0.8 | 0.88    | V    |

| High Level Output Voltage | $V_{OH}$         | REFOUT pin<br>Іон = -4mA                                    | 0.8*VDD |     |         | V    |

| Low level Output Voltage  | V <sub>OL</sub>  | REFOUT pin<br>IoL = 4mA                                     |         |     | 0.2*VDD | V    |

| All specifications at VDD: 3.0V to 3.6V, Ta: -40 to +85°C, 25MHz Crystal, unless otherwise noted |                        |                     |     |        |     |      |  |  |

|--------------------------------------------------------------------------------------------------|------------------------|---------------------|-----|--------|-----|------|--|--|

| Parameter                                                                                        | Symbol                 | Conditions          | Min | Тур    | Max | Unit |  |  |

| Crystal Clock Frequency                                                                          | F <sub>in_xo</sub>     | XIN pin<br>XOUT pin |     | 25.000 |     | MHz  |  |  |

| Oscillation Accuracy                                                                             | Faccuracy              | REFOUT pin (1)      | -30 | 0      | +30 | ppm  |  |  |

| External Clock Frequency                                                                         | F <sub>in_ext</sub>    | XIN pin (2)         |     | 25.000 |     | MHz  |  |  |

| Input Clock Voltage Swing                                                                        | V <sub>swing_ext</sub> | XIN pin (2)         | 1   |        | VDD | Vpp  |  |  |

| Input Clock Duty Cycle                                                                           | T <sub>extindc</sub>   | XIN pin (2)         |     | 50     |     | %    |  |  |

| Output Frequency                                                                                 | F <sub>osc</sub>       | <b>REFOUT</b> pin   |     | 25.000 |     | MHz  |  |  |

| Output Rising and Falling                                                                        | T <sub>RF</sub>        | REFOUT pin (3)      |     | 1.8    | 5.0 | ns   |  |  |

| Output Clock Duty Cycle                                                                          | $T_{outdc_xtal}(4)$    | <b>REFOUT</b> pin   | 45  | 50     | 55  | %    |  |  |

| Output Clock Duty Cycle                                                                          | $T_{outdc_ext}(5)$     | <b>REFOUT</b> pin   | 40  | 50     | 60  | %    |  |  |

| Cycle to Cycle Jitter                                                                            | Jit <sub>c2c</sub>     | REFOUT pin (6)      |     | 23     | 48  | ps   |  |  |

| Output Lock Time                                                                                 | T <sub>lock</sub>      | REFOUT pin (7)      |     | 0.5    | 2   | ms   |  |  |

#### AC Characteristics (except Differential Output)

All specifications at VDD: 3 OV to 3 6V Tay 40 t

Note:

(1) Specification of Frequency Accuracy is measured by connecting the standard 25MHz crystal unit for part number XRCGB25M000F3M00R0 of Murata Manufacturing Co., Ltd. on page 11. This Output Clock Frequency Accuracy does not include accuracy of crystal unit. Total output clock frequency accuracy could be up to "Output Clock Frequency Accuracy" + "Crystal unit accuracy".

- (2) Use Case of External Clock Input

- (3) Transition time between 0.2VDD and 0.8VDD

- (4) When the standard 25MHz Crystal Unit is connected.

- (5) When the Duty Cycle of External Clock Input is 50%.

- (6)  $1\sigma$  in 10000 sampling or more

- (7) Transition time to settle output into  $\pm 0.1\%$  of specified frequency after escaping power down mode. (REFOUT\_OE pin = PCIE0\_OE pin = PCIE1\_OE pin = 'L').

#### AC Characteristics (Differential Output pin : PCIE0p-1p/0n-1n pin)

All specifications at VDD: over 3.0V to 3.6V, Ta: -40 to +85°C, 25MHz Crystal, unless otherwise noted

| Denemeter                                     | Cruch al                | Conditions               | Min   | True    | Ман    | T Let |

|-----------------------------------------------|-------------------------|--------------------------|-------|---------|--------|-------|

| Parameter                                     | Symbol                  | Conditions               | Min   | Тур     | Max    | Unit  |

| Average Output Frequency                      | F <sub>in</sub>         | SS Off (1)               | 99.97 | 100.000 | 100.03 | MHz   |

| Average Output Frequency                      | 1 in                    | SS On (1)                | 99.47 |         | 100.03 | MHz   |

| Output Skew                                   | T <sub>slew</sub>       |                          |       |         | 250    | ps    |

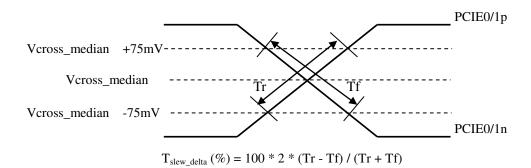

| Slew Rate of<br>Output Rising and Falling     | T <sub>slew</sub>       | Differential<br>Figure 6 | 2.5   | 4.0     | 8.0    | V/ns  |

| High Level Output Voltage                     | V <sub>IH</sub>         | Differential             | 150   |         |        | mV    |

| Low Level Output Voltage                      | V <sub>IL</sub>         | Differential             |       |         | -150   | mV    |

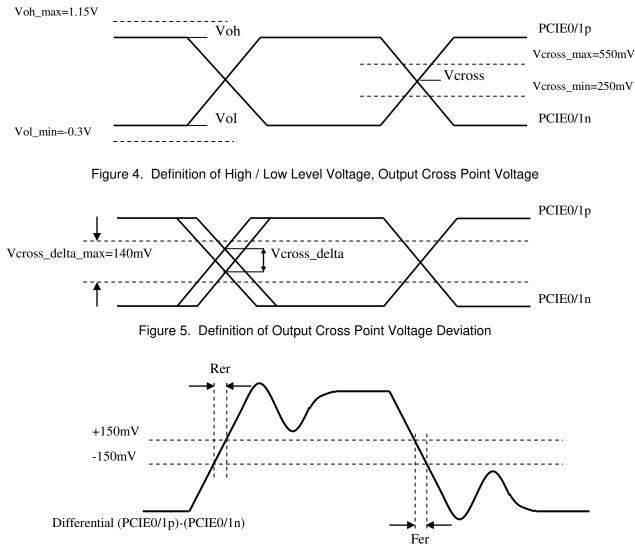

| Output Cross Point Voltage                    | V <sub>cross</sub>      | Figure 4                 | 250   |         | 550    | mV    |

| Output Cross Point Voltage Deviation          | $V_{cross\_delta}$      | Figure 5                 |       |         | 140    | mV    |

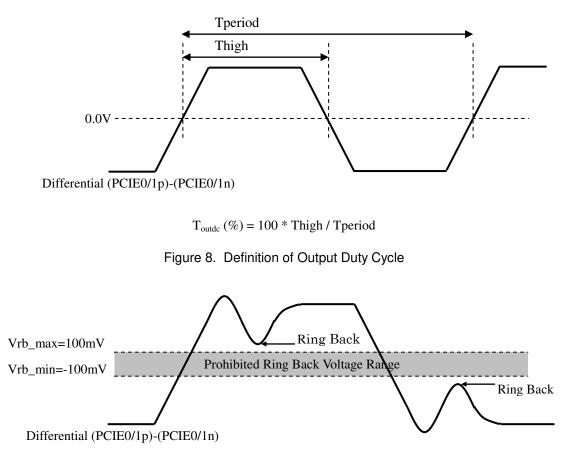

| Output Ring Back Voltage<br>Margin            | V <sub>rb</sub>         | Figure 9                 | -100  |         | 100    | mV    |

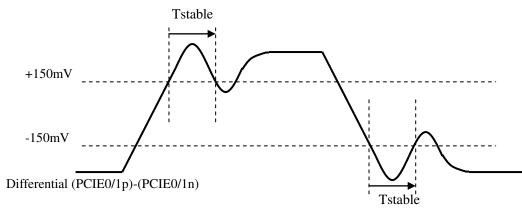

| Output Ring Back Time                         | T <sub>stable</sub>     | Figure 10                | 500   |         |        | ps    |

| Average Clock Period<br>Accuracy              | $T_{period\_avg}$       |                          | -300  |         | 2800   | ppm   |

| Absolute Period                               | T <sub>period_abs</sub> | Figure 8                 | 9.847 |         | 10.203 | ns    |

| Maximum Output Voltage                        | V <sub>max</sub>        | Single End<br>Figure 4   |       |         | 1.15   | V     |

| Minimum Output Voltage                        | $\mathbf{V}_{\min}$     | Single End<br>Figure 4   | -0.3  |         |        | V     |

| Output Duty Cycle                             | T <sub>outdc</sub>      | Figure 8                 | 45    | 50      | 55     | %     |

| Time Matching of<br>Output Rising and Falling | $T_{slew\_delta}$       | Figure 7                 |       |         | 20     | %     |

| Parameter                      | Symbol             | Conditions                   | Min | Тур | Max | Unit |

|--------------------------------|--------------------|------------------------------|-----|-----|-----|------|

| PCI Express Gen2<br>RMS Jitter | T:+                | BW=<br>10kHz - 1.5MHz<br>(2) |     | 0.5 | 2.6 | ps   |

|                                | Jit <sub>RMS</sub> | BW=<br>1.5MHz - 50MHz<br>(2) |     | 1.2 | 2.6 | ps   |

| Cycle to Cycle Jitter (p-p)    | Jit <sub>c2c</sub> | (3)                          |     | 60  | 125 | ps   |

| Output Lock Time               | T <sub>lock</sub>  | SS Off (4)                   |     | 0.5 | 2   | ms   |

Note:

(1) Specification of Frequency Accuracy is measured by connecting the standard 25MHz crystal unit for part number XRCGB25M000F3M00R0 of Murata Manufacturing Co., Ltd. on page 11. This Output Clock Frequency Accuracy does not include accuracy of crystal unit. Total output clock frequency accuracy could be up to "Output Clock Frequency Accuracy" + "Crystal unit accuracy".

- (2) The specifications are values applied the jitter filter function specified PCI Express standard.

- (3)  $\pm 7\sigma$  in 10000 sampling or more

- (4) Transition time to settle output into ±0.1% of specified frequency after escaping power down mode. (PCIE0\_OE pin = PCIE1\_OE pin = 'L').

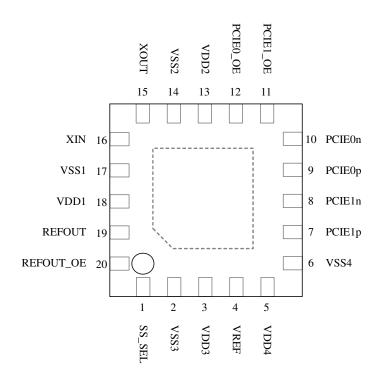

#### **Differential Output Measurement Circuit**

Each Characteristic is measured at the point of "Measure point" in Figure 3

Figure 3. Differential Output Measurement Circuit

#### **Definition of Differential Output AC Characteristics**

Figure 6. Definition of Output Slew Rate

Figure 7. Definition of Time Matching of Output Rising and Falling

Figure 9. Definition of Output Ring Back Voltage Margin

Figure 10. Definition of Output Ring Back Time

#### **Crystal Specification**

Murata Manufacturing Co.,Ltd, XRCGB25M000F3M00R0

| Parameter               | Symbol | Conditions | Min | Тур    | Max | Unit |

|-------------------------|--------|------------|-----|--------|-----|------|

| Crystal Clock Frequency | f0     | CL=6[pF]   |     | 25.000 |     | MHz  |

| Series Resistance       | R1     |            |     | 56.9   | 150 | Ω    |

| Shunt Capacitance       | C0     |            |     | 0.59   |     | pF   |

| Motional Capacitance    | C1     |            |     | 1.29   |     | fF   |

| Motional Inductance     | L1     |            |     | 31.52  |     | mH   |

| Power level             |        |            |     |        | 300 | μW   |

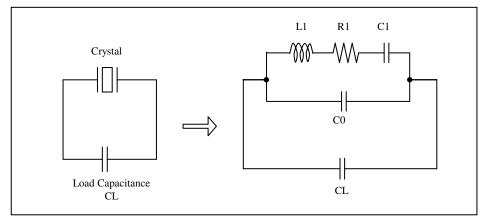

Figure 11. Equivalent parameters of crystal and load capacitance

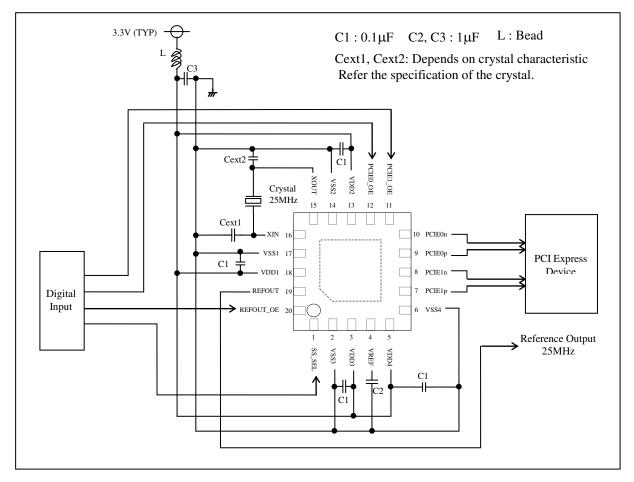

#### 9. Recommended External Circuits

Figure 12 Recommended External Circuits

#### PCB Layout Consideration

The AK8160B2 is a high-accuracy and low-jitter clock generator. For proper performances specified in this datasheet, careful PCB layout should be taken. The followings are layout guidelines based on the typical connection diagram shown in Figure 12

#### Power supply line & Ground pin connection

AK8160B2 has four power supply pins (VDD1-4) which deliver power to internal circuitry segments. And AK8160B2 has four ground pins (VSS1-4). These pins require connecting to plane ground which will eliminate any common impedance with other critical switching signal return.

0.1µF decoupling capacitors placed at VDD1, VDD2, VDD3 and VDD4 should be grounded at close to the VSS1pin, the VSS2 pin, VSS3 pin and the VSS4 pin, respectively.

#### **Crystal connection**

Proper oscillation performance are susceptible to stray or parasitic capacitors around crystal. The wiring traces to a crystal form XIN (Pin 16) and XOUT (Pin 15) have equal lengths with no via and as short in length as possible. These traces should be also located away from any traces with switching signal.

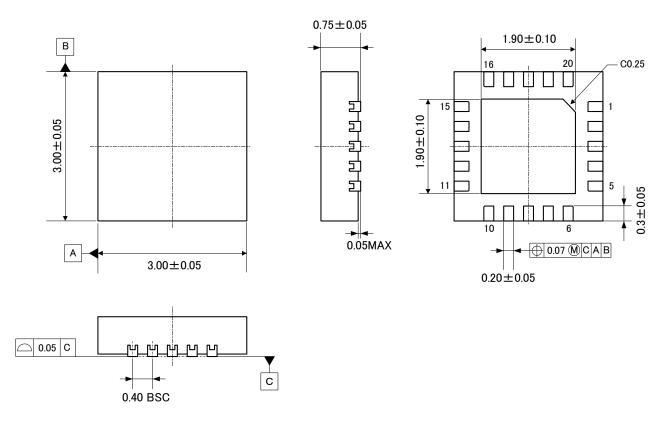

#### 10. Package

#### **Outline Dimensions**

0.4mm pitch 3mm x 3mm 20-pin QFN (Unit: mm)

#### Package & Lead Frame Material

Package molding compound: Epoxy Resin (Green Compound)Lead frame material: Cu AlloyLead frame surface treatment: Au

#### Asahi**KASEI**

#### Marking

- a: #1 Pin Index : Circle

- b: Part number : 60B2

- c: Date code : 4 digits

| Revision History |  |

|------------------|--|

|                  |  |

| Date     | Revision | Reason           | Page/Line | Contents |

|----------|----------|------------------|-----------|----------|

| 14/06/27 | 00       | Initial Release. |           |          |

#### **11. Important Notice**

#### IMPORTANT NOTICE

- 0. Asahi Kasei Microdevices Corporation ("AKM") reserves the right to make changes to the information contained in this document without notice. When you consider any use or application of AKM product stipulated in this document ("Product"), please make inquiries the sales office of AKM or authorized distributors as to current status of the Products.

- All information included in this document are provided only to illustrate the operation and application examples of AKM Products. AKM neither makes warranties or representations with respect to the accuracy or completeness of the information contained in this document nor grants any license to any intellectual property rights or any other rights of AKM or any third party with respect to the information in this document. You are fully responsible for use of such information contained in this document in your product design or applications. AKM ASSUMES NO LIABILITY FOR ANY LOSSES INCURRED BY YOU OR THIRD PARTIES ARISING FROM THE USE OF SUCH INFORMATION IN YOUR PRODUCT DESIGN OR APPLICATIONS.

- 2. The Product is neither intended nor warranted for use in equipment or systems that require extraordinarily high levels of quality and/or reliability and/or a malfunction or failure of which may cause loss of human life, bodily injury, serious property damage or serious public impact, including but not limited to, equipment used in nuclear facilities, equipment used in the aerospace industry, medical equipment, equipment used for automobiles, trains, ships and other transportation, traffic signaling equipment, equipment used to control combustions or explosions, safety devices, elevators and escalators, devices related to electric power, and equipment used in finance-related fields. Do not use Product for the above use unless specifically agreed by AKM in writing.

- 3. Though AKM works continually to improve the Product's quality and reliability, you are responsible for complying with safety standards and for providing adequate designs and safeguards for your hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of the Product could cause loss of human life, bodily injury or damage to property, including data loss or corruption.

- 4. Do not use or otherwise make available the Product or related technology or any information contained in this document for any military purposes, including without limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass destruction weapons). When exporting the Products or related technology or any information contained in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. The Products and related technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 5. Please contact AKM sales representative for details as to environmental matters such as the RoHS compatibility of the Product. Please use the Product in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. AKM assumes no liability for damages or losses occurring as a result of noncompliance with applicable laws and regulations.

- 6. Resale of the Product with provisions different from the statement and/or technical features set forth in this document shall immediately void any warranty granted by AKM for the Product and shall not create or extend in any manner whatsoever, any liability of AKM.

- 7. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of AKM.