Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### SMALL PANEL BACKLIGHT LED DRIVER

### **Description**

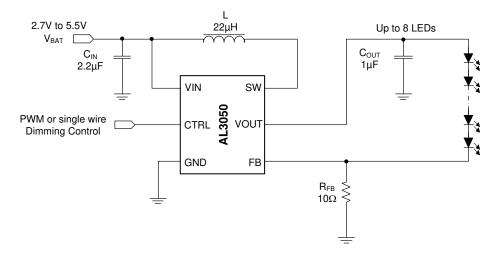

The AL3050 is a current mode Boost-type LED driver with programmable brightness dimming control for portable devices. With a 30V rated integrated MOSFET and power diode, the AL3050 can support up to 8 LEDs in series. The small solution size, advanced dimming features and high efficiency are suitable for LED backlight solutions for single cell Li-ion based equipment. The boost converter runs at 750kHz fixed switching frequency to reduce output ripple, improve conversion efficiency, and allows for the use of small external components.

The default LED current is adjustable by an external resister at FB pin and the feedback voltage is regulated to 200mV typically. The AL3050 provides PWM dimming mode and single wire digital dimming mode for accurate LED current control from CTRL pin. In PWM dimming mode, the feedback reference voltage is changed with the PWM duty cycle proportionally and the available PWM frequency range is from 20kHz to 100kHz. In single wire digital dimming mode, it provides a programmable 32-step brightness dimming function with the CTRL pin setting.

The AL3050 provides protection functions including Under Voltage Lockout, Over Voltage Protection, Over Current Protection and Over Temperature Protection to protect the circuit.

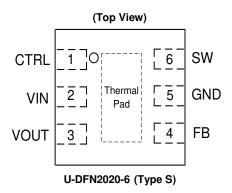

The AL3050 is available in U-DFN2020-6 (Type S) packages.

#### **Features**

- 2.7V to 5.5V Input Voltage Range

- 28V Open LED Protection (Up to 8 LEDs)

- Integrated 0.7A/30V Internal MOSFET and Power Diode

- 200mV Reference with ±3% Accuracy

- 750kHz Switching Frequency

- Flexible Digital and PWM Brightness Control

- Single Wire Control Interface

- PWM Dimming Control Interface

- Up to 100:1 PWM Dimming Ratio

- Integrated Loop Compensation

- Built-in Soft-Start

- Built-in OTP

- Built-in OCP

- Tiny Package with U-DFN2020-6 (Type S) Package

- Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

- Halogen and Antimony Free. "Green" Device (Note 3)

### **Pin Assignments**

### **Applications**

- Feature Phones

- Smart Phones

- Portable Media Players

- Ultra Mobile Devices

- GPS Receivers

- Backlight for Small and Media Form Factor LCD Display

Notes:

- 1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS) & 2011/65/EU (RoHS 2) compliant.

- See http://www.diodes.com/quality/lead\_free.html for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

- 3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

# **Typical Applications Circuit**

# **Pin Descriptions**

| Pin Number | Pin Name    | Function                                                                                                                                            |

|------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | CTRL        | Control pin of the boost converter. It is a multi-functional pin which can be used for enable control, PWM and digital dimming.                     |

| 2          | VIN         | Supply input pin. A capacitor should be connected between the VIN pin and GND pin to keep the DC input voltage constant.                            |

| 3          | VOUT        | Output of the boost converter.                                                                                                                      |

| 4          | FB          | Feedback pin for current. Connect a resistor between this pin and GND to set the current.                                                           |

| 5          | GND         | Ground.                                                                                                                                             |

| 6          | SW          | This is the switching node of the IC. Connect the inductor between the VIN and SW pin.                                                              |

| -          | Thermal Pad | The thermal pad should be soldered to the analog ground plane. If possible, use thermal via to connect to ground plane for ideal power dissipation. |

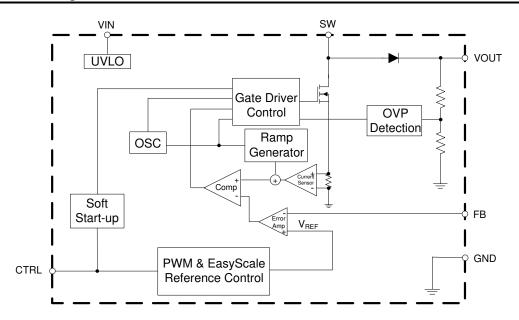

# **Functional Block Diagram**

# **Absolute Maximum Ratings** (@ $T_A = +25^{\circ}C$ , unless otherwise specified.) (Note 4)

| Symbol                              | Parameter                                | Rat                     | Rating    |      |

|-------------------------------------|------------------------------------------|-------------------------|-----------|------|

| $V_{IN}$                            | Input Pin Voltage                        | -0.3 to 6               |           | V    |

| $V_{VOUT}, V_{SW}$                  | VOUT and SW Pin Voltage                  | -0.3 to 32              |           | V    |

| V <sub>FB</sub> , V <sub>CTRL</sub> | FB and CTRL Pin Voltage                  | -0.3                    | -0.3 to 6 |      |

| θ <sub>JA</sub>                     | Thermal Resistance (Junction to Ambient) | U-DFN2020-6<br>(Type S) | 70.4      | °C/W |

| TJ                                  | Operating Junction Temperature           | +150                    |           | °C   |

| T <sub>STG</sub>                    | Storage Temperature                      | -65 to +150             |           | °C   |

| ESD                                 | ESD (Human Body Model)                   | 2000                    |           | V    |

| LOD                                 | ESD (Machine Model)                      | 20                      | 200       |      |

Note:

# Recommended Operating Conditions (@TA = +25°C, unless otherwise specified.)

| Symbol           | Parameter                      | Min      | Max  | Unit |

|------------------|--------------------------------|----------|------|------|

| V <sub>IN</sub>  | Input Voltage                  | 2.7      | 5.5  | V    |

| Vo               | Output Voltage                 | $V_{IN}$ | 30   | V    |

| Io               | Output Current                 | -        | 40   | mA   |

| f <sub>PWM</sub> | PWM Dimming Frequency          | 20       | 100  | kHz  |

| T <sub>A</sub>   | Operating Ambient Temperature  | -40      | +85  | ōC   |

| TJ               | Operating Junction Temperature | -40      | +125 | ōC   |

<sup>4.</sup> Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" is not implied. Exposure to "Absolute Maximum Ratings" for extended periods may affect device reliability.

# **Electrical Characteristics** ( $V_{IN} = 3.6V$ , CTRL = High, $T_A = +25$ °C, unless otherwise specified.)

| Symbol                     | Parameter                             | Condition                                                               | Min                 | Тур  | Max  | Unit     |  |

|----------------------------|---------------------------------------|-------------------------------------------------------------------------|---------------------|------|------|----------|--|

| SUPPLY VOLTA               | AGE (VIN PIN)                         |                                                                         |                     |      |      |          |  |

| $V_{IN}$                   | Input Voltage                         | -                                                                       | 2.7                 | -    | 5.5  | V        |  |

| la                         | Quiescent Current                     | Device enable, no switching and no load $(V_{FB} = 0.4V)$               | -                   | 0.3  | 0.5  | mA       |  |

| IQ                         | Quiescent Current                     | Device enable, switching 750kHz and no load ( $V_{FB} = 0V$ )           | -                   | 0.5  | 1.65 |          |  |

| I <sub>SHDN</sub>          | Shutdown Supply Current               | CRTL = GND                                                              | -                   | 0.1  | 1    | μΑ       |  |

| UNDER VOLTA                | GE LOCKOUT                            |                                                                         |                     |      |      |          |  |

| V                          | Input IIVI O Throphold                | V <sub>IN</sub> ramp down                                               | -                   | 2.2  | 2.35 | V        |  |

| V <sub>UVLO</sub>          | Input UVLO Threshold                  | V <sub>IN</sub> ramp up                                                 | -                   | 2.5  | 2.65 | V        |  |

| V <sub>HYS</sub>           | Input UVLO Hysteresis                 | -                                                                       | -                   | 300  | -    | mV       |  |

| <b>ENABLE CONT</b>         | ROL                                   |                                                                         |                     |      |      |          |  |

| V <sub>CTRL-H</sub>        | CTRL Logic High Voltage               | -                                                                       | 1.2                 | -    | -    | V        |  |

| V <sub>CTRL-L</sub>        | CTRL Logic Low Voltage                | -                                                                       | -                   | -    | 0.4  | V        |  |

| RCTRL                      | CTRL Pull Down Resistor               | -                                                                       | -                   | 300  | -    | kΩ       |  |

| toff (Note 5)              | CTRL Pulse With to Shutdown           | CTRL from high to low                                                   | 3.5                 | -    | -    | ms       |  |

| FEEDBACK AN                | D REFERENCE (FB PIN)                  |                                                                         |                     |      | •    | •        |  |

| $V_{REF}$                  | Feedback Reference Voltage            | Duty = 100%                                                             | 194                 | 200  | 206  | mV       |  |

| I <sub>FB</sub>            | Feedback Input Bias Current           | V <sub>FB</sub> = 200mV                                                 | -                   | -    | 2    | μA       |  |

| t <sub>REF</sub> (Note 5)  | V <sub>REF</sub> Filter Time Constant | -                                                                       | -                   | 230  | -    | μs       |  |

|                            | NCY OSCILLATOR                        |                                                                         |                     |      | ı    |          |  |

| fosc                       | Oscillator Frequency                  | -                                                                       | 600                 | 750  | 900  | kHz      |  |

| D <sub>MAX</sub> (Note 5)  | Maximum Duty Cycle                    | V <sub>FB</sub> = 0V, measured on the drive signal of the switch MOSFET | 88                  | 94   | -    | %        |  |

| POWER SWITC                | H AND DIODE                           | Modi E.                                                                 |                     |      |      | L        |  |

| R <sub>DS(ON)</sub>        | N-MOSFET On-Resistance                | V <sub>IN</sub> = 3.6V                                                  | -                   | 0.56 | 1    | Ω        |  |

| VF                         | Power Diode Forward Voltage           | I <sub>DIODE</sub> = 0.2A                                               | -                   | 0.75 | 1    | V        |  |

| I <sub>LEAK_SW</sub>       | SW Pin Leakage Current                | V <sub>SW</sub> = 28V                                                   | -                   | 0.1  | 2    | μA       |  |

| PROTECTION L               |                                       | - 50V = 5 ·                                                             |                     |      | 1    | <u> </u> |  |

| I <sub>LIM</sub>           | N-MOSFET Current Limit                | D = D <sub>MAX</sub>                                                    | 0.6                 | 0.7  | 0.84 | Α        |  |

| ILIM_OPEN                  | LED Open Current Limit                | LED open                                                                | -                   | 0.3  | -    | Α        |  |

| V <sub>OVP</sub>           | Open LED Protection Threshold         | Measured on the VOUT pin                                                | 27                  | 28.2 | 30   | V        |  |

| T <sub>OTSD</sub> (Note 5) | Thermal Shutdown Threshold            | -                                                                       | -                   | +160 | -    | ºC       |  |

| T <sub>HYS</sub> (Note 5)  | Thermal Shutdown Hysteresis           | -                                                                       | -                   | +20  | -    | °C       |  |

|                            | NG TIMING (Note 5)                    |                                                                         |                     |      |      |          |  |

| t <sub>1W_DET</sub>        | Digital Dimming Detection Time        | CTRL pin low                                                            | 450                 | -    | _    | μs       |  |

| t <sub>1W_DELAY</sub>      | Digital Dimming Detection Delay       | -                                                                       | 100                 | -    | -    | μs       |  |

| t <sub>1W_WIN</sub>        | Digital Dimming Detection Window Time | Measured from CTRL High                                                 | 3.5                 | _    | -    | ms       |  |

| tstart                     | Start Time of Program Stream          | acaraaa aa                                                              | 3.5                 | _    | -    | μs       |  |

| teos                       | End Time Of Program Stream            | -                                                                       | 3.5                 |      | 600  | μs       |  |

| t <sub>H_LB</sub>          | High Time Low Bit                     | Logic 0                                                                 | 3.5                 |      | 300  | μs       |  |

| tl_lB                      | Low Time Low Bit                      | Logic 0                                                                 | 2×t <sub>H_LB</sub> | _    | 600  | μs       |  |

| tt<br>tн_нв                | High Time High Bit                    | Logic 1                                                                 | 2×th_LB             | _    | 600  | μs       |  |

| t <sub>L_НВ</sub>          | Low Time High Bit                     | Logic 1                                                                 | 3.5                 |      | 300  | μs       |  |

| V <sub>ACKN</sub>          | Acknowledge Output Voltage Low        | Open Drain, R <sub>PULL-UP</sub> =15KΩ to VIN                           | -                   | -    | 0.4  | V        |  |

| tval ackn                  | Acknowledge Valid Time                | -                                                                       | -                   | -    | 3.5  | μs       |  |

| t <sub>ACKN</sub>          | Duration of Acknowledge Condition     |                                                                         | _                   |      | 900  | μs       |  |

Note: 5. Guaranteed by design.

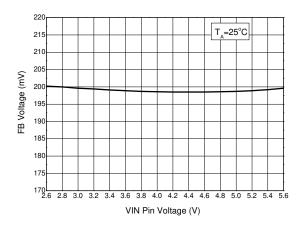

# $\textbf{Performance Characteristics} \ \, (V_{IN} = 3.6V, \, L = 22 \mu H, \, R_{FB} = 10 \Omega, \, 8 \, \text{LEDs in series}, \, T_{A} = +25 ^{\circ} C, \, \text{unless otherwise specified.})$

### FB vs. VIN Pin Voltage

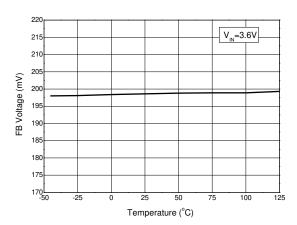

#### FB vs. Temperature

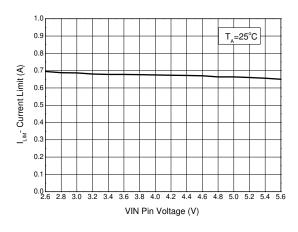

### **Current Limit vs. VIN Pin Voltage**

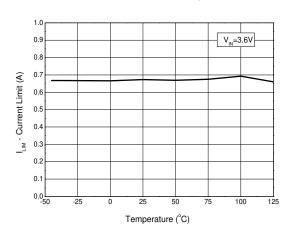

### **Current Limit vs. Temperature**

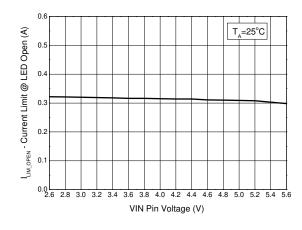

### Current Limit @LED Open vs. VIN Pin Voltage

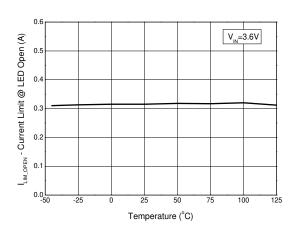

#### Current Limit @LED Open vs. Temperature

# $\begin{tabular}{ll} \textbf{Performance Characteristics} & (V_{IN} = 3.6V, \ L = 22 \mu H, \ R_{FB} = 10 \underline{\Omega}, \ 8 \ LEDs \ in \ series, \ T_A = +25 ^{\circ}C, \ unless \ otherwise \ specified.) \end{tabular}$

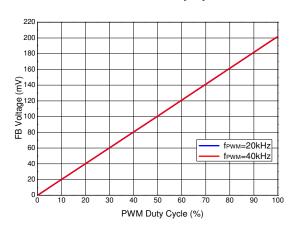

### FB vs. PWM Duty Cycle

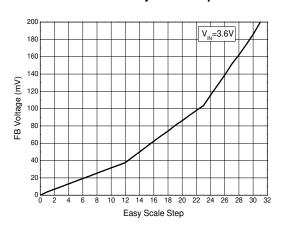

### FB vs. Easy Scale Step

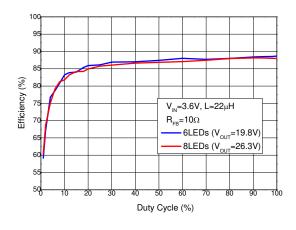

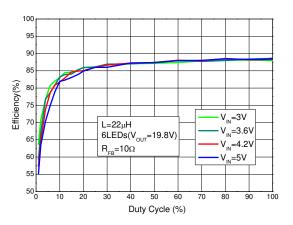

### Efficiency vs. PWM Duty Cycle

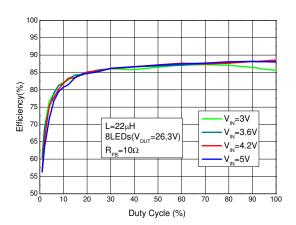

### Efficiency vs. PWM Duty Cycle

### Efficiency vs. PWM Duty Cycle

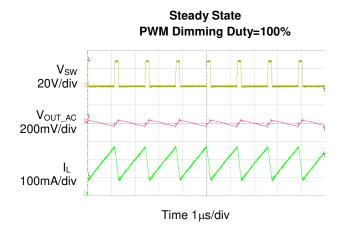

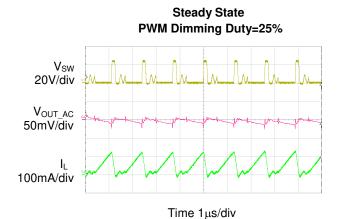

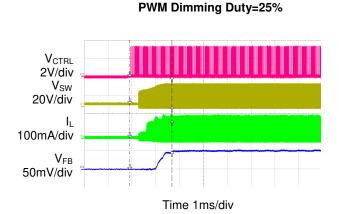

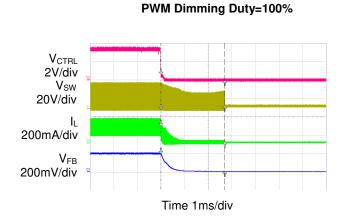

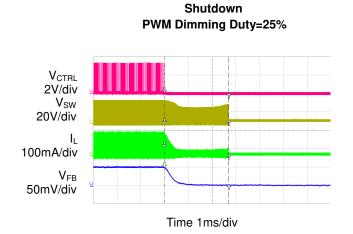

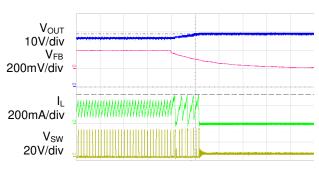

### Performance Characteristics ( $V_{IN} = 3.6V$ , $L = 22\mu H$ , $R_{FB} = 10\Omega$ , 8 LEDs in series, $T_A = +25$ °C, unless otherwise specified.)

PWM Dimming Duty=100%

VCTRL

2V/div

Vsw

20V/div

VFB

200mV/div

Time 1ms/div

**Shutdown**

Start up

Start up

### **Performance Characteristics** ( $V_{IN} = 3.6V$ , $L = 22\mu H$ , $R_{EB} = 10\Omega$ , 8 LEDs in series, $T_A = +25$ °C, unless otherwise specified.)

Time 10µs /div

### **Application Information**

#### 1. General Operation

The AL3050 is a high efficiency boost converter with integrated power diode in a small package size. The device is ideal for driving white LED in series. The serial LED connection provides even illumination by sourcing the same output current through all LEDs, eliminating the need for expensive factory calibration. The device integrates a 30V/0.7A low side switch MOSFET and a 30V power diode, and operates in pulse width modulation (PWM) with 750 kHz fixed switching frequency. For operation see the block diagram. The duty cycle of the converter is set by the error amplifier output and the current signal applied to the PWM control comparator. The control architecture is based on traditional current-mode control; therefore, slope compensation is added to the current signal to allow stable operation for duty cycles larger than 50%. The feedback loop regulates the FB pin to a low reference voltage (200mV typical), reducing the power dissipation in the current sense resistor.

#### 2. Soft Start-up

Soft-start circuitry is integrated into the IC to avoid a high inrush current during start-up. After the device is enabled, the voltage at FB pin ramps up slowly to the reference voltage in 32 steps with each step taking 341µs. This ensures that the output voltage rises slowly to reduce the input current. Additionally, during the start up process, the current limit of the switch is set to half of the normal current limit spec. During this period, the input current is kept below 360mA (typical).

#### 3. Open LED Protection

Open LED protection circuitry prevents IC damage as the result of white LED disconnection. The AL3050 monitors the voltages at the VOUT pin and FB pin. The circuitry turns off the switch MOSFET and shuts down the IC completely if both of the following two conditions are met: 1) the VOUT voltage reaches OVP threshold (28.2V typical), 2) FB voltage is lower than half of its regulation voltage. This means the LED string is open or the FB pin is short to ground. During open LED condition, the cycle by cycle switch current limit is set to be 0.3A typically to protect external devices. As a result, the output voltage falls to the level of the input supply. The device remains in shutdown mode until it is enabled by pulling down the CTRL pin logic low for at least 3.5ms and then pulling it high.

#### 4. Shutdown

The AL3050 enters shutdown mode when the CTRL voltage is logic low for more than 3.5ms. During shutdown, the input supply current for the device is less than 1µA (max). Although the internal MOSFET does not switch in shutdown mode, there is still a DC current path between the input and the LEDs through the inductor and the power diode. The minimum forward voltage of the LED array must exceed the maximum input voltage to ensure that the LEDs remain off in shutdown. In the typical application with two or more LEDs, the forward voltage is large enough to reverse bias the diode and keep leakage current low.

#### 5. Current Setting

The FB voltage is regulated by a low 0.2V reference voltage. The LED current is programmed externally using a current-sense resistor in series with the LED string. The LED current can be calculated by Equation 1:

$$I_{LED} = \frac{V_{FB}}{R_{SET}} \tag{1}$$

Where

$I_{\mathit{LED}}$  = full-scale output current of LEDs

$V_{\it FB}$  = 200mV (regulated voltage of FB)

$R_{\it SET}$  = current sense resistor at FB pin

The output current tolerance depends on the FB accuracy and the current sensor resistor accuracy.

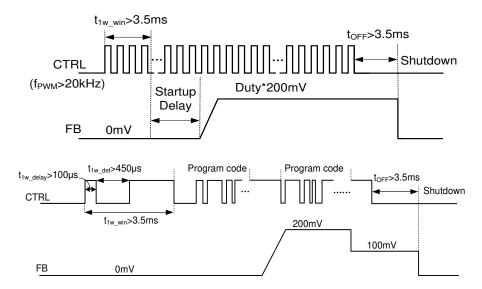

#### 6. LED Brightness Dimming Mode Selection

The CTRL pin is used for the control input for both dimming modes, PWM dimming and single wire dimming. The dimming mode for the AL3050 is selected each time the device is enabled. The default dimming mode is PWM dimming. To enter the single wire mode, the following digital pattern on the CTRL pin must be recognized by the IC every time the IC starts from the shutdown mode.

- 1. Pull CTRL pin high to enable the AL3050, and to start the single wire dimming detection window;

- 2. After the single wire dimming detection delay  $(t_{1W\_DELAY}, 100\mu s)$  expires, drive the CTRL pin low for more than single wire detection time  $(t_{1W\_DET}, 450\mu s)$ ;

- 3. The CTRL pin has to be low for more than t<sub>1w\_DET</sub> before the single wire dimming detection window (t<sub>1W\_WIN</sub>, 3.5ms) expires. Single wire detection

window starts from the first CTRL pin low to high transition.

If all above three conditions are fulfilled, the IC enters single wire dimming mode, otherwise enters PWM dimming mode. Once the dimming mode is programmed, it can not be changed without another start up. This means the IC needs to be shut down by pulling the CTRL low for 3.5ms and restarts. See the Dimming Mode Detection and Soft Start (Figure 1) for a graphical explanation.

Figure 1. Dimming Mode Detection and Soft Start

#### 7. PWM Dimming Mode

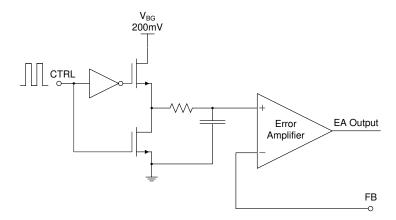

When the CTRL pin is constantly high, the FB voltage is regulated to 200mV typically. However, the CTRL pin allows a PWM signal to reduce this regulation voltage; therefore, it achieves LED brightness dimming. The relationship between the duty cycle and FB voltage is given by Equation 2.

$$V_{FB} = Duty \times 200mV \tag{2}$$

Where

Duty = duty cycle of the PWM signal 200mV = internal reference voltage

Figure 2. Block Diagram of Programmable FB Voltage in PWM Dimming Mode

As shown in Figure 2, the AL3050 chops up the internal 200mV reference voltage at the duty cycle of the PWM signal. The pulse signal is then filtered by an internal low pass filter. The output of the filter is connected to the error amplifier as the reference voltage for the FB pin regulation. Therefore, although a PWM signal is used for brightness dimming, only the LED DC current is modulated, which is often referred as analog dimming. This eliminates the audible noise which often occurs when the LED current is pulsed in replica of the frequency and duty cycle of PWM control.

For optimum performance, use the PWM dimming frequency in the range of 20kHz to 100kHz. Since the CTRL pin is logic only pin, adding an external RC filter applied to the pin does not work.

The minimum dimming duty cycle the IC can support is 1% within the PWM dimming frequency range 20kHz to 100kHz.

### 8. Single Wire Digital Dimming Mode

The CTRL pin features a simple digital interface to allow digital brightness control. The digital dimming can save the processor power and battery life as it does not require a PWM signal all the time, and the processor can enter idle mode if available.

The AL3050 adopts a single wire digital protocol for the digital dimming mode control, which can program the FB voltage to any of the 32 steps with single command. The step increment increases with the voltage to produce pseudo logarithmic curve for the brightness step. See the Table 1 for the FB pin voltage steps. The default step is full scale when the device is first enabled (V<sub>FB</sub> = 200mV). The programmed reference voltage is stored in an internal register. A power reset clears the register value and reset it to default.

| -  | FB Voltage (mV) | D4 | D3 | D2 | D1 | D0 |

|----|-----------------|----|----|----|----|----|

| 0  | 0               | 0  | 0  | 0  | 0  | 0  |

| 1  | 5               | 0  | 0  | 0  | 0  | 1  |

| 2  | 8               | 0  | 0  | 0  | 1  | 0  |

| 3  | 11              | 0  | 0  | 0  | 1  | 1  |

| 4  | 14              | 0  | 0  | 1  | 0  | 0  |

| 5  | 17              | 0  | 0  | 1  | 0  | 1  |

| 6  | 20              | 0  | 0  | 1  | 1  | 0  |

| 7  | 23              | 0  | 0  | 1  | 1  | 1  |

| 8  | 26              | 0  | 1  | 0  | 0  | 0  |

| 9  | 29              | 0  | 1  | 0  | 0  | 1  |

| 10 | 32              | 0  | 1  | 0  | 1  | 0  |

| 11 | 35              | 0  | 1  | 0  | 1  | 1  |

| 12 | 38              | 0  | 1  | 1  | 0  | 0  |

| 13 | 44              | 0  | 1  | 1  | 0  | 1  |

| 14 | 50              | 0  | 1  | 1  | 1  | 0  |

| 15 | 56              | 0  | 1  | 1  | 1  | 1  |

| 16 | 62              | 1  | 0  | 0  | 0  | 0  |

| 17 | 68              | 1  | 0  | 0  | 0  | 1  |

| 18 | 74              | 1  | 0  | 0  | 1  | 0  |

| 19 | 80              | 1  | 0  | 0  | 1  | 1  |

| 20 | 86              | 1  | 0  | 1  | 0  | 0  |

| 21 | 92              | 1  | 0  | 1  | 0  | 1  |

| 22 | 98              | 1  | 0  | 1  | 1  | 0  |

| 23 | 104             | 1  | 0  | 1  | 1  | 1  |

| 24 | 116             | 1  | 1  | 0  | 0  | 0  |

| 25 | 128             | 1  | 1  | 0  | 0  | 1  |

| 26 | 140             | 1  | 1  | 0  | 1  | 0  |

| 27 | 152             | 1  | 1  | 0  | 1  | 1  |

| 28 | 164             | 1  | 1  | 1  | 0  | 0  |

| 29 | 176             | 1  | 1  | 1  | 0  | 1  |

| 30 | 188             | 1  | 1  | 1  | 1  | 0  |

| 31 | 200             | 1  | 1  | 1  | 1  | 1  |

Table 1. 32-Step Digital Dimming Setting

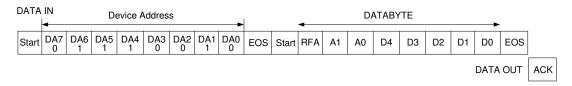

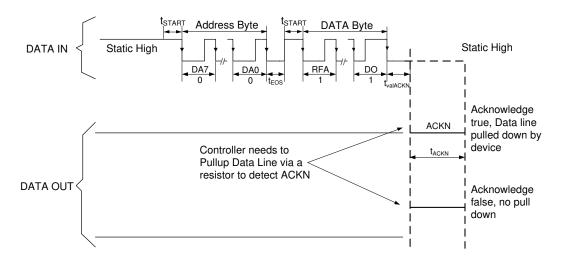

The digital dimming interface is based on a master-slave structure, where the master is typically a microcontroller or application processor. Figure 3 and Table 2 give an overview of the protocol. The protocol consists of a device specific address byte and a data byte. The device specific address byte is fixed to 58 hex. The data byte consists of five bits for information, two address bits ("00"), and the RFA bit. The RFA bit set to high indicates the Request for Acknowledge condition. The Acknowledge condition is only applied if the protocol was received correctly. The advantage of single wire digital dimming compared with other on pin interfaces is that its bit detection is in a large extent independent from the bit transmission rate. It can automatically detect bit rates between 1.1kBit/sec and up to 100kBit/sec.

Figure 3. Single Wire Digital Protocol Overview

| Byte                | Bit Number | Name | Transmission<br>Direction | Description                                                                                                                                                                                                                                                                                                                                  |

|---------------------|------------|------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | 7          | DA7  |                           | 0 (MSB Device Address)                                                                                                                                                                                                                                                                                                                       |

|                     | 6          | DA6  |                           | 1                                                                                                                                                                                                                                                                                                                                            |

|                     | 5          | DA5  |                           | 0                                                                                                                                                                                                                                                                                                                                            |

| Device Address Byte | 4          | DA4  |                           | 1                                                                                                                                                                                                                                                                                                                                            |

| 72 Hex              | 3          | DA3  | IN                        | 1                                                                                                                                                                                                                                                                                                                                            |

|                     | 2          | DA2  |                           | 0                                                                                                                                                                                                                                                                                                                                            |

|                     | 1          | DA1  |                           | 0                                                                                                                                                                                                                                                                                                                                            |

|                     | 0          | DA0  |                           | 0 (LSB Device Address)                                                                                                                                                                                                                                                                                                                       |

|                     | 7 (MSB)    | RFA  |                           | Request for acknowledge. If high, acknowledge is applied by device.                                                                                                                                                                                                                                                                          |

|                     | 6          | A1   | IN                        | 0 (Address bit A1)                                                                                                                                                                                                                                                                                                                           |

|                     | 5          | A0   |                           | 0 (Address bit A0)                                                                                                                                                                                                                                                                                                                           |

| Data Byte           | 4          | D4   |                           | Data bit D4                                                                                                                                                                                                                                                                                                                                  |

| ,                   | 3          | D3   |                           | Data bit D3                                                                                                                                                                                                                                                                                                                                  |

|                     | 2          | D2   |                           | Data bit D2                                                                                                                                                                                                                                                                                                                                  |

|                     | 1          | D1   |                           | Data bit D1                                                                                                                                                                                                                                                                                                                                  |

|                     | 0 (LSB)    | D0   |                           | Data bit D0                                                                                                                                                                                                                                                                                                                                  |

| -                   | -          | ACK  | OUT                       | Acknowledge condition active 0, this condition will only be applied to case RFA bit is set. Open drain output, line needs to be pulled high by the host with a pullup resistor. This feature can only be used if the master has an open drain output stage. In case of a push pull output stage, acknowledge condition may not be requested! |

Table 2. Single Wire Dimming Bit Description

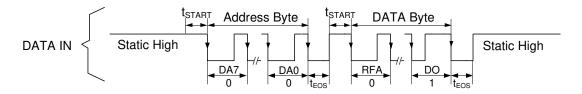

All bits are transmitted MSB first and LSB last. Figure 4 shows the protocol without acknowledge request (Bit RFA = 0), Figure 5 with acknowledge (Bit RFA = 1) request. Prior to both bytes, device address byte and data byte, a start condition must be applied. For this, the CTRL pin must be pulled high for at least  $t_{START}$  (3.5µs) before the bit transmission starts with the falling edge. If the CTRL pin is already at high level, no start condition is needed prior to the device address byte. The transmission of each byte is closed with an End of Stream condition for at least  $t_{EOS}$  (3.5µs).

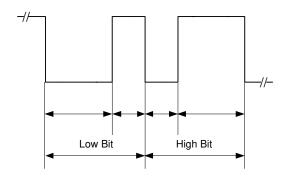

The bit detection is based on a Logic Detection scheme, where the criterion is the relation between  $t_{LOW}$  and  $t_{HIGH}$  (refer to Figure 6). It can be simplified to:

High Bit:  $t_{HIGH} > t_{LOW}$ , but with  $t_{HIGH}$  at least 2x  $t_{LOW}$ . Low Bit:  $t_{HIGH} < t_{LOW}$ , but with  $t_{LOW}$  at least 2x  $t_{HIGH}$ .

The bit detection starts with a falling edge on the CTRL pin and ends with the next falling edge. Depending on the relation between  $t_{HIGH}$  and  $t_{LOW}$ , the logic 0 or 1 is detected.

The acknowledge condition is only applied if:

- Acknowledge is requested by setting RFA bit to 1.

- The transmitted device address matches with the device address of the device.

- Device address byte and data byte are received correctly.

July 2016

# **Application Information (Cont.)**

If above conditions are met, after t<sub>VAL ACKN</sub> (3.5µs) delay from the moment when the last falling edge of the protocol is detected, an internal ACKN-MOSFET is turned on to pull the CTRL pin low for the time t<sub>ACKN</sub> (900µs maximum), then the Acknowledge condition is valid. During the tyal ACKN delay, the master controller keeps the line low; after the delay, it should release the line by outputting high impedance and then detect the acknowledge condition. If it reads back a logic 0, it means the IC has received the command correctly. The CTRL pin can be used again by the master when the acknowledge condition ends after t<sub>ACKN</sub> time.

Note that the acknowledge condition may only be requested in case the master device has an open drain output. For a push-pull output stage, the use a series resistor in the CRTL line to limit the current to 500µA is recommended to for such cases as:

- · an accidentally requested acknowledge, or

- · to protect the internal ACKN-MOSFET.

Figure 4. Single Wire Digital Dimming Timing, without Acknowledge RFA=0

Figure 5. Single Wire Digital Dimming Timing, with Acknowledge RFA=1

Figure 6. Single Wire Digital Dimming - Bit Coding

### 9. Under Voltage Lockout

An under voltage lockout prevents operation of the device at input voltages below typical 2.2V. When the input voltage is below the under voltage threshold, the device is shutdown and the internal switch is turned off. If the input voltage rises by under voltage lockout hysteresis, the IC restarts.

#### 10. Thermal Shutdown

An internal thermal shutdown turns off the device when the typical junction temperature of +160°C is exceeded. The device is released from shutdown automatically when the junction temperature decreases by +20°C.

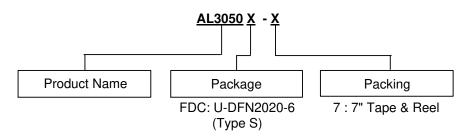

### Ordering Information

| Doub Number | Doolsono Codo               | Dookses              | 7" Tape and Reel |                    |  |

|-------------|-----------------------------|----------------------|------------------|--------------------|--|

| Part Number | Number Package Code Package |                      | Quantity         | Part Number Suffix |  |

| AL3050FDC-7 | FDC                         | U-DFN2020-6 (Type S) | 3000/Tape & Reel | -7                 |  |

# **Marking Information**

#### U-DFN2020-6 (Type S)

(Top View)

XX<u>Y W X</u> XX: Identification Code

Y: Year: 0~9

W: Week: A~Z: 1~26 week;

a~z: 27~52 week; z represents

52 and 53 week

X: Internal Code

| Part Number | Package              | Identification Code |  |

|-------------|----------------------|---------------------|--|

| AL3050FDC-7 | U-DFN2020-6 (Type S) | Z9                  |  |

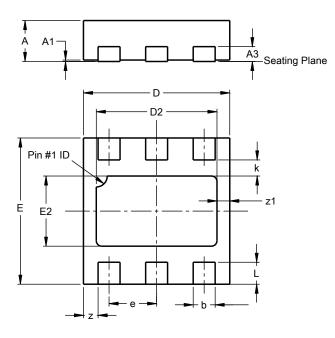

# **Package Outline Dimensions**

Please see http://www.diodes.com/package-outlines.html for the latest version.

### U-DFN2020-6 (Type S)

| U-DFN2020-6          |          |        |       |  |  |  |  |

|----------------------|----------|--------|-------|--|--|--|--|

|                      | (Type S) |        |       |  |  |  |  |

| Dim                  | Min      | Max    | Тур   |  |  |  |  |

| Α                    | 0.51     | 0.61   | 0.56  |  |  |  |  |

| <b>A</b> 1           | 0.00     | 0.05   | 0.02  |  |  |  |  |

| A3                   | 1        | 1      | 0.203 |  |  |  |  |

| b                    | 0.25     | 0.35   | 0.30  |  |  |  |  |

| D                    | 1.95     | 2.05   | 2.00  |  |  |  |  |

| D2                   | 1.55     | 1.75   | 1.65  |  |  |  |  |

| Е                    | 1.95     | 2.05   | 2.00  |  |  |  |  |

| E2                   | 0.86     | 1.06   | 0.96  |  |  |  |  |

| е                    | 0.       | 650 BS | C     |  |  |  |  |

| k                    |          |        | 0.22  |  |  |  |  |

| L                    | 0.25     | 0.35   | 0.30  |  |  |  |  |

| Z                    |          | -      | 0.20  |  |  |  |  |

| z1                   |          | -      | 0.175 |  |  |  |  |

| All Dimensions in mm |          |        |       |  |  |  |  |

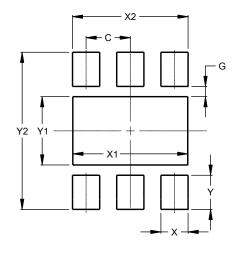

# **Suggested Pad Layout**

Please see http://www.diodes.com/package-outlines.html for the latest version.

### U-DFN2020-6 (Type S)

| Dimensions   | Value   |

|--------------|---------|

| Difficusions | (in mm) |

| С            | 0.650   |

| G            | 0.150   |

| Х            | 0.400   |

| X1           | 1.690   |

| X2           | 1.700   |

| Υ            | 0.500   |

| Y1           | 1.000   |

| Y2           | 2.300   |

#### **IMPORTANT NOTICE**

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel. Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

#### **LIFE SUPPORT**

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

- A. Life support devices or systems are devices or systems which:

- 1. are intended to implant into the body, or

- 2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

- B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2016, Diodes Incorporated

www.diodes.com