# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## **AMMP-5618** 6–20 GHz General Purpose Amplifier

### **Data Sheet**

#### Description

Avago's AMMP-5618 is a high power, medium gain amplifier that operates from 6 GHz to 20 GHz. The amplifier is designed to be an easy-to-use component for any surface mount PCB application. In communication systems, it can be used as a LO buffer, or as a transmit driver amplifier. During typical operation with a single 5V supply, each gain stage is biased for Class-A operation for optimal power output with minimal distortion. The amplifier has integrated  $50\Omega$  I/O match, DC blocking, self-bias and choke to eliminate complex tuning and assembly processes typically required by hybrid (discrete-FET) amplifiers. The package is fully SMT compatible with backside grounding and I/O to simplify assembly.

Note: These devices are ESD sensitive. The following precautions are strongly recommended. Ensure that an ESD approved carrier is used when dice are transported from one destination to another. Personal grounding is to be worn at all times when handling these devices.

#### Features

- 5 x 5 mm surface mount package

- Broad band performance 6–20 GHz

- High +19 dBm output power

- Medium 13 dB typical gain

- $50\Omega$  input and output match

- Single 5V (107 mA) supply bias

#### **Applications**

- Microwave radio systems

- Satellite VSAT

- Commercial grade military

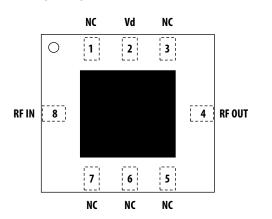

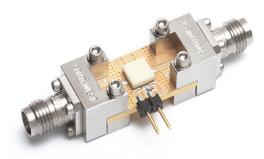

#### Package Diagram

Attention: Observe precautions for handling electrostatic sensitive devices. ESD Machine Model (Class A) = 50V ESD Human Body Model (Class 0) = 150V Refer to Avago Application Note A004R: Electrostatic Discharge Damage and Control.

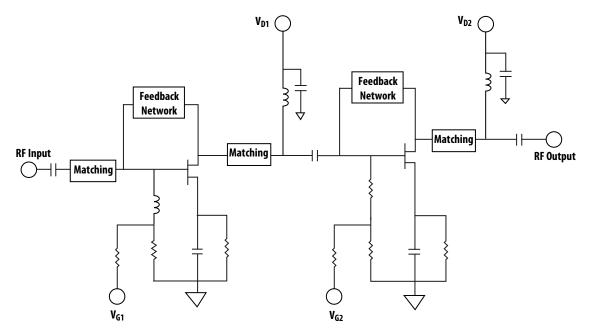

#### **Functional Block Diagram**

| Function |  |  |

|----------|--|--|

| NC       |  |  |

| Vd       |  |  |

| NC       |  |  |

| RF_out   |  |  |

| NC       |  |  |

| NC       |  |  |

| NC       |  |  |

| RF_in    |  |  |

|          |  |  |

#### **Electrical Specifications**

- 1. Small/Large -signal data measured in a fully de-embedded test fixture form TA = 25°C, Vd=5V, Idq=107mA.

- 2. Pre-assembly into package performance verified 100% on-wafer per AMMC-5618 published specifications

- 3. This final package part performance is verified by a functional test correlated to actual performance at one or more frequencies

- 4. Specifications are derived from measurements in a 50Ω test environment. Aspects of the amplifier performance may be improved over a more narrow bandwidth by application of additional conjugate, linearity, or low noise (Γopt) matching.

| Parameter                                  | Тур. | Sigma | Unit | Frequency |

|--------------------------------------------|------|-------|------|-----------|

| Small-signal Gain, Gain                    | 12   | 0.40  | dB   | 5-6 GHz   |

|                                            | 13   |       |      |           |

| Noise Figure into 50 Ω, NF                 | 4.4  | 0.2   | dB   |           |

| Output Power at 1dB Gain Compression, P1dB | 19   | 0.9   | dBm  |           |

| Third Order Intercept Point;               | 25   | 1.2   | dBm  | 5-6 GHz   |

| Δf=100MHz; Pin=-20dBm, OIP3                | 30   |       |      |           |

| Input Return Loss, RLin                    | -12  | 0.7   | dB   |           |

| Output Return Loss, Rlout                  | -12  | 0.6   | dB   |           |

| Reverse Isolation, Isolation               | -40  | 1.2   | dB   |           |

|                                            |      |       |      |           |

#### Table 2. Recommended Operating Range

- 1. Ambient operational temperature  $T_{A} = 25^{\circ}$ C unless otherwise noted.

- 2. Channel-to-backside Thermal Resistance (Tchannel (Tc) = 34°C) as measured using infrared microscopy. Thermal Resistance at backside temperature (Tb)= 25°C calculated from measured data.

|                          |      | Specifications |      |      |                                                     |

|--------------------------|------|----------------|------|------|-----------------------------------------------------|

| Description              | Min. | Typical        | Max. | Unit | Comments                                            |

| Drain Supply Current, Id |      | 107            | 140  | mA   | (Vd = 5 V, Under any RF power drive and temperature |

#### **Table 3. Thermal Properties**

| Parameter                           | Test Conditions                           | Value                             |

|-------------------------------------|-------------------------------------------|-----------------------------------|

| Thermal Resistance, $\theta_{ch-b}$ | Backside Temperature, $T_A = 25^{\circ}C$ | $\theta_{ch-b} = 34 \text{ °C/W}$ |

#### **Absolute Minimum and Maximum Ratings**

#### **Table 4. Minimum and Maximum Ratings**

|                            | Specifi | cations | Unit | Comments          |

|----------------------------|---------|---------|------|-------------------|

| Description                | Min.    | Max.    |      |                   |

| Positive Drain Voltage, Vd |         | 7       | V    |                   |

| Drain Current, Id          |         | 150     | mA   |                   |

| RF Input Power (Pin), RFin |         | 20      | dBm  | CW                |

| Channel Temperature, Tch   |         | +150    | °C   |                   |

| Storage Temperature, Tstg  | -65     | +150    | °C   |                   |

| Max. Assembly Temp, Tmax   | +300    |         | °C   | 30 second maximum |

Notes:

1. Operation in excess of any one of these conditions may result in permanent damage to this device.

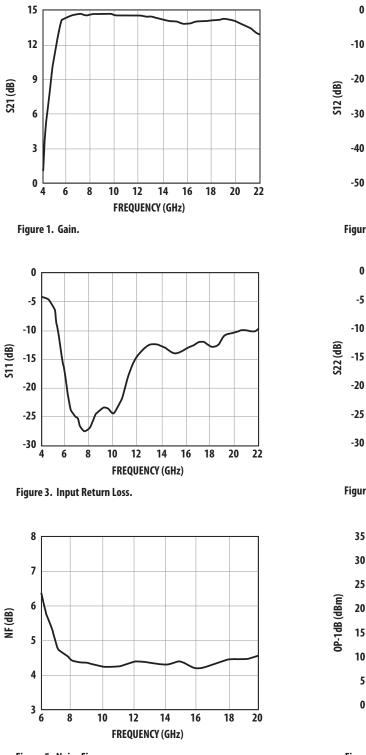

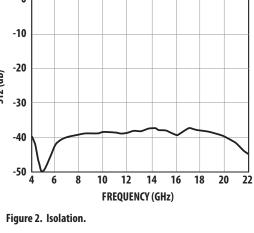

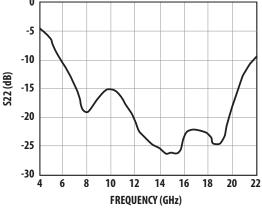

#### Selected performance plots

These measurements are in  $50\Omega$  test environment at TA =  $25^{\circ}$ C, Vd = 5V, Id = 107 mA. Aspects of the amplifier performance may be improved over a narrower bandwidth by application of additional conjugate, linearity or low noise (Fopt) matching.

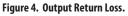

Figure 6. Typical Power, OP-1dB and OIP3.

#### **Over Temperature Performance Plots**

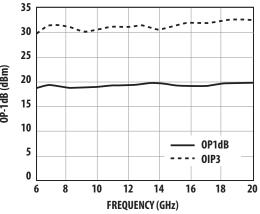

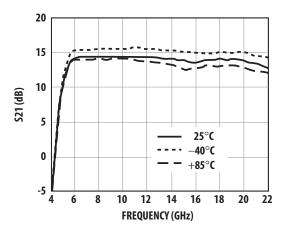

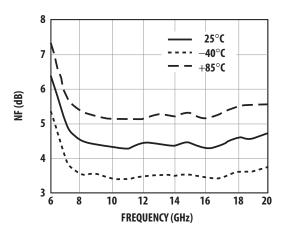

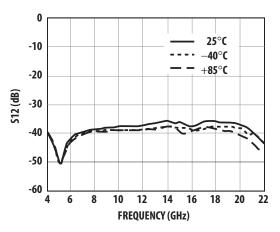

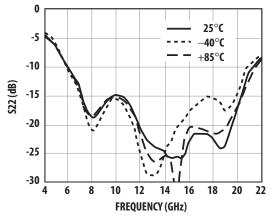

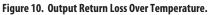

These measurements are in  $50\Omega$  test environment at TA =  $25^{\circ}$ C, Vd = 5V, Id = 107 mA. Aspects of the amplifier performance may be improved over a narrower bandwidth by application of additional conjugate, linearity or low noise (Fopt) matching.

Figure 7. Gain Over Temperature.

Figure 9. Input RL Over Temperature.

Figure 11. NF Over Temperature.

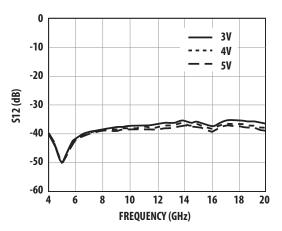

Figure 8. Isolation Over Temperature.

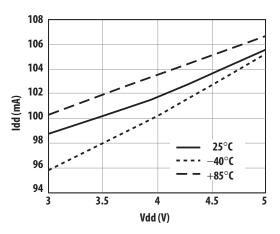

Figure 12. Bias Current Over Temperature.

#### **Over Voltage plots**

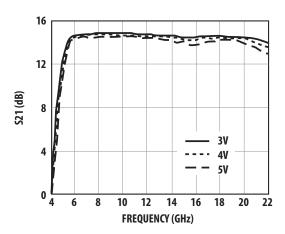

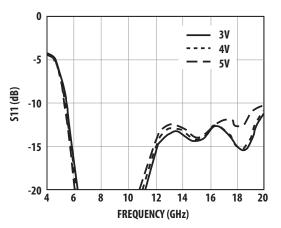

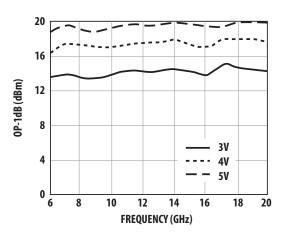

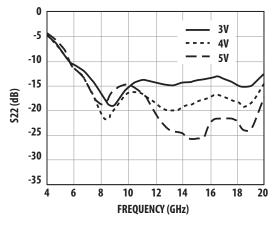

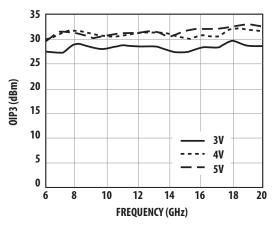

These measurements are in  $50\Omega$  test environment at TA =  $25^{\circ}$ C, Vd = 5V, Id = 107 mA. Aspects of the amplifier performance may be improved over a narrower bandwidth by application of additional conjugate, linearity or low noise (Fopt) matching.

Figure 13. Gain Over Vdd.

Figure 15. Input RL Over Vdd.

Figure 17. Output Power Over Vdd.

Figure 14. Isolation Over Vdd.

Figure 16. Output Return Loss Over Vdd.

Figure 18. OIP3 Over Vdd.

#### **Typical Scattering Parameters**

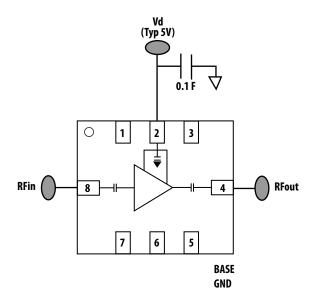

**Application Circuit**

Please refer to <http://www.avagotech.com> for typical scattering parameters data.

#### **Biasing and Operation**

The AMMC-5618 is normally biased with a single positive drain supply connected to both  $V_D$  pins through bypass capacitors as shown in Figure 19. The recommended supply voltage is 5V. It is important to have 0.1  $\mu$ F bypass capacitor, and the capacitor should be placed as close to the component as possible.

The AMMC-5618 does not require a negative gate voltage to bias any of the two stages. No ground wires are needed because all ground connections are made with plated through-holes to the backside of the package.

Refer to the Absolute Maximum Ratings table for allowed DC and thermal conditions.

Figure 21. Demonstration Board (available upon request).

Figure 20. Simplified MMIC Schematic.

#### Package Dimension, PCB Layout and Tape and Reel information

Please refer to Avago Technologies Application Note 5520, AMxP-xxxx production Assembly Process (Land Pattern A).

| Part Number Ordering Information |                          |                |  |  |

|----------------------------------|--------------------------|----------------|--|--|

| Part Number                      | Devices<br>per Container | Container      |  |  |

| AMMP-5618-BLK                    | 10                       | antistatic bag |  |  |

| AMMP-5618-TR1                    | 100                      | 7" Reel        |  |  |

| AMMP-5618-TR2                    | 500                      | 7" Reel        |  |  |

For product information and a complete list of distributors, please go to our web site: www.avagotech.com

Avago, Avago Technologies, and the A logo are trademarks of Avago Technologies in the United States and other countries. Data subject to change. Copyright © 2005-2013 Avago Technologies. All rights reserved. Obsoletes 5989-3545EN AV02-0485EN - July 8, 2013