# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

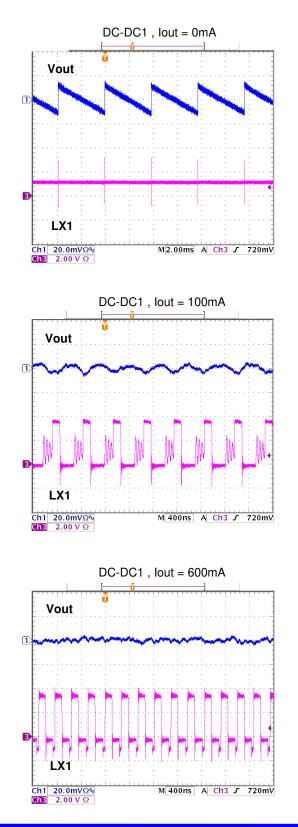

# AN30183A

### 600mA Synchronous DC-DC Step Down Regulator (1ch) 300mA LDO Regulator (4ch) Multi Power Supply (High Efficiency Power LSI)

### FEATURES

- High-Speed Response DC-DC Step Down Regulator Circuit that employs Hysteretic System

- DC-DC Step Down Regulator : 1-ch Input voltage Range VBAT :2.5V to 5.5V DVDD : 1.7V to 3.0V Output voltage Range 0.8 V to 2.4 V Up to 600 mA Output Current

- LDO Regulator : 4-ch Input voltage Range VBAT :2.5V to 5.5V DVDD : 1.7V to 3.0V Output voltage Range 1.0 V to 3.3 V Up to 300 mA Output Current

- I<sup>2</sup>C control (2-slave address selectable)

- 20 pin Wafer Level Chip Size Package (WLCSP) (Size : 1.56 mm × 2.06 mm, 0.4 mm Pitch)

#### DESCRIPTION

AN30183A is a multi power supply LSI which has High-Speed Response DC-DC Step Down Regulators (1-ch) and LDO Regulators (4-ch).

By this DC-DC system, when load current charges suddenly, it responds at high speed and minimizes the changes of output voltage.

Since it is possible to use capacitors with small capacitance and it is unnecessary to add external parts for system phase compensation, this IC realizes downsizing of set and reducing in the number of external parts.

The output DC of each power supply is variable by I<sup>2</sup>C control.

#### **APPLICATIONS**

Mobile phone, Portable appliance, etc

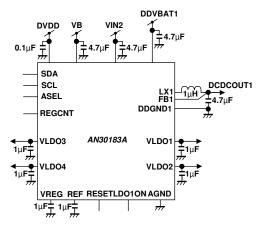

#### SIMPLIFIED APPLICATION

Notes) This application circuit is an example. The operation of mass production set is not guaranteed. You should perform enough evaluation and verification on the design of mass production set. You are fully responsible for the incorporation of the above application circuit and information in the design of your equipment.

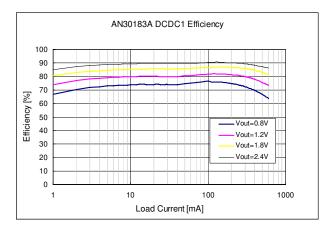

#### **EFFICIENCY CURVE**

Condition ) DDVBAT1 = DDVBAT2 = VB = VIN2 = 3.7V

Lo = 1.0  $\mu$ H, Cout = 4.7  $\mu$ F

### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                      | Symbol                                  | Rating                            | Unit | Notes    |

|--------------------------------|-----------------------------------------|-----------------------------------|------|----------|

| Supply voltage                 | VB,VIN2,DDVBAT1                         | 6.0                               | V    | *1       |

| Supply voltage                 | DVDD                                    | 3.6                               | V    | *1       |

| Output Current                 | I <sub>IN</sub>                         | —                                 | А    | *1       |

| Operating free-air temperature | T <sub>opr</sub>                        | - 30 to + 85                      | °C   | *2       |

| Operating junction temperature | Tj                                      | – 30 to + 150                     | °C   | *2       |

| Storage temperature            | T <sub>stg</sub>                        | – 55 to + 150                     | °C   | *2       |

| Input Voltago Pongo            | RESET,LDO1ON,FB1,<br>REGCNT             | $-0.3$ to $V_{\text{VBAT}}$ + 0.3 | V    | *1<br>*3 |

| Input Voltage Range            | SCL,SDA,ASEL                            | - 0.3 to DVDD + 0.3               | V    | *1<br>*3 |

| Output Voltage Range           | LX1,VREG,REF,SDA<br>LDO1,LDO2,LDO3,LDO4 | - 0.3 to V <sub>VBAT</sub> + 0.3  | V    | *1<br>*3 |

| ESD                            | HBM (Human Body Model)                  | 2                                 | kV   | _        |

Notes) Do not apply external currents and voltages to any pin not specifically mentioned.

This product may sustain permanent damage if subjected to conditions higher than the above stated absolute maximum rating. This rating is the maximum rating and device operating at this range is not guaranteeable as it is higher than our stated recommended operating range. When subjected under the absolute maximum rating for a long time, the reliability of the product may be affected.

\*1: The values under the condition not exceeding the above absolute maximum ratings and the power dissipation.

\*2:Except for the power dissipation, operating ambient temperature, and storage temperature, all ratings are for Ta = 25 °C. \*3: $V_{VBAT}$  is voltage for DDVBAT1 = VB = VIN2, ( $V_{VBA}$  + 0.3) V must not be exceeded 6 V.

$V_{\text{DVDD}}$  is voltage for DVDD, (V\_{\text{DVDD}} + 0.3) V must not be exceeded 3.6 V.

### POWER DISSIPATION RATING

| PACKAGE                                              | $\theta_{JA}$ | PD ( Ta = 25 °C) | PD ( Ta = 85 °C ) | Notes |

|------------------------------------------------------|---------------|------------------|-------------------|-------|

| 20 pin Wafer level chip size Package<br>(WLCSP Type) | 359.0 °C / W  | 0.348 W          | 0.181 W           | *1    |

Note). For the actual usage, please refer to the PD-Ta characteristics diagram in the package specification, follow the power supply voltage, load and ambient temperature conditions to ensure that there is enough margin and the thermal design does not exceed the allowable value.

\*1:Glass Epoxy Substrate ( 4 Layers ) [ Glass-Epoxy: 50 X 50 X 0.8 t ( mm ) ] Die Pad Exposed , Soldered.

### **CAUTION**

Although this has limited built-in ESD protection circuit, but permanent damage may occur on it. Therefore, proper ESD precautions are recommended to avoid electrostatic damage to the MOS gates

# AN30183A

### **RECOMMENDED OPERATING CONDITIONS**

| Parameter            | Pin Name | Min.  | Тур. | Max.                    | Unit | Notes |

|----------------------|----------|-------|------|-------------------------|------|-------|

|                      | VB       | 2.5   | 3.7  | 5.5                     | V    | *1    |

| Supply voltage renge | VIN2     | 2.5   | 3.7  | 5.5                     | V    | *1    |

| Supply voltage range | DDVBAT1  | 2.5   | 3.7  | 5.5                     | V    | *1    |

|                      | DVDD     | 1.7   | 1.85 | 3.0                     | V    | *1    |

|                      | RESET    | - 0.3 | _    | V <sub>VBAT</sub> + 0.3 | V    | *2    |

|                      | LDO10N   | - 0.3 | _    | V <sub>VBAT</sub> + 0.3 | V    | *2    |

|                      | REGCNT   | - 0.3 | _    | V <sub>VBAT</sub> + 0.3 | V    | *2    |

| Input Voltage Range  | FB1      | - 0.3 | _    | V <sub>VBAT</sub> + 0.3 | V    | *2    |

|                      | SCL      | - 0.3 | _    | DVDD + 0.3              | V    | *2    |

|                      | SDA      | - 0.3 | _    | DVDD + 0.3              | V    | *2    |

|                      | ASEL     | - 0.3 | _    | DVDD + 0.3              | V    | *2    |

|                      | LX1      | - 0.3 | _    | V <sub>VBAT</sub> + 0.3 | V    | *2    |

|                      | VREG     | - 0.3 | _    | V <sub>VBAT</sub> + 0.3 | V    | *2    |

|                      | REF      | - 0.3 | _    | V <sub>VBAT</sub> + 0.3 | V    | *2    |

|                      | SDA      | - 0.3 | _    | DVDD + 0.3              | V    | *2    |

| Output Voltage Rang  | VLDO1    | - 0.3 | _    | V <sub>VBAT</sub> + 0.3 | V    | *2    |

|                      | VLDO2    | - 0.3 | _    | V <sub>VBAT</sub> + 0.3 | V    | *2    |

|                      | VLDO3    | - 0.3 | _    | V <sub>VBAT</sub> + 0.3 | V    | *2    |

|                      | VLDO4    | - 0.3 | _    | V <sub>VBAT</sub> + 0.3 | V    | *2    |

Note) Do not apply external currents and voltages to any pin not specifically mentioned.

Voltage values, unless otherwise specified, are with respect to GND. GND is voltage for AGND = DDGND1

$V_{\text{VBAT}}$  is voltage for DDVBAT1 = VB = VIN2.

\*1 : The values under the condition not exceeding the above absolute maximum ratings and the power dissipation.

\*2 : (V<sub>VBAT</sub> + 0.3) V must not be exceeded 6 V. (DVDD + 0.3) V must not be exceeded 3.6 V.

### **ELECRTRICAL CHARACTERISTICS**

$V_{VBAT}(DDVBAT1 = VB = VIN2) = 3.7V, DVDD = 1.85V$ DC-DC : Co = 4.7  $\mu$ F, Lo = 1  $\mu$ H / LDO : Co =1.0  $\mu$ F

$T_a$  = 25 °C  $\pm$  2 °C unless otherwise noted.

|    | Parameter                       |        | Symbol Conditions                  |   | Limits |     | Unit | Notes |

|----|---------------------------------|--------|------------------------------------|---|--------|-----|------|-------|

|    |                                 |        |                                    |   | Тур    | Max | Unit | Notes |

| Co | Consumption current             |        |                                    |   |        |     |      |       |

|    | Consumption current 1 on active | IBAT_1 | only LDO1 (PS mode) ON             | — | 10     | 20  | μA   | _     |

|    | Consumption current 2 on active | IBAT_2 | DCDC1, LDO1-4 = ON                 | _ | 240    | 400 | μA   | —     |

|    | Static consumption current      | IBAT_3 | DCDC1, LDO1-4 = OFF<br>RESET = "L" |   | 0.1    | 1.0 | μA   | _     |

### ELECRTRICAL CHARACTERISTICS (Continued)

$$\label{eq:Vbat} \begin{split} V_{VBAT}(DDVBAT1 = VB = VIN2) &= 3.7V, \ DVDD = 1.85V \\ DC\text{-}DC : Co &= 4.7 \ \mu\text{F}, \ Lo &= 1 \ \mu\text{H} \ / \ LDO : Co &= 1.0 \ \mu\text{F} \\ T_a &= 25 \ ^\circ\text{C} \pm 2 \ ^\circ\text{C} \ unless \ otherwise \ noted. \end{split}$$

Limits Conditions Parameter Symbol Unit Notes Тур Max Min LDO1 – 4 (Normal Mode) - (LDO Regulator) ILDO = -150 mAOutput voltage VLDO 1.803 1.850 1.897 ٧ Vout = 1.85 V setting ILDO Output current 300 mΑ \_\_\_\_ \_ \_\_\_\_ \_\_\_\_ DVLDO mV  $\Delta$  ILDO = - 10  $\mu$ A  $\rightarrow$  - 150 mA -5 20 50 Load regulation \_\_\_  $VB = 3.1~V \rightarrow 4.5~V$ **VLDOLR** - 10 Line regulation ILDO = - 150 mA 0 10 mV \_\_\_\_ Vout = 1.85 V setting VB = 3.7 VShort-circuit current ISTLDO 35 100 255 mΑ \_ VLDO = 0 VLDO1 - 4 ( Power Save Mode ) - (LDO Regulator) ILDO = -5 mAOutput voltage **VLDOPS** 1.803 1.850 1.897 V Vout = 1.85 V setting **ILDOPS** Output current 10 mΑ \_\_\_\_ \_ \_\_\_\_ \_ **DVLDOPS**  $\Delta$  ILDO = - 10  $\mu$ A  $\rightarrow$  - 5 mA - 5 20 50 Load regulation mV \_\_\_\_  $VB = 3.1 V \rightarrow 4.5 V$ Line regulation **VLDOLRPS** ILDO = -5 mA0 25 mV - 25 \_\_\_\_ Vout = 1.85 V setting

### ELECRTRICAL CHARACTERISTICS (Continued)

$\label{eq:Vbat} \begin{array}{l} V_{VBAT}(DDVBAT1=VB=VIN2)=3.7V,\ DVDD=1.85V\\ DC\text{-}DC:\ Co=4.7\ \mu\text{F},\ Lo=1\ \mu\text{H}\ /\ LDO:\ Co=1.0\ \mu\text{F}\\ T_a=25\ ^\circ\text{C}\pm2\ ^\circ\text{C}\ unless\ otherwise\ noted. \end{array}$

Limits Conditions Parameter Symbol Unit Notes Тур Max Min DCDC1 (DC-DC Step Down Regulator) IDCDC1 = -300 mAVDCDC1 Output voltage 1.170 1.200 1.230 V Vout = 1.2 V setting Output current IDCDC1 \_ 600 mΑ \_ \_\_\_\_ \_\_\_\_  $\Delta$  IDCDC1 = - 10  $\mu$ A  $\rightarrow$  - 500 mA Load regulation DVDCDC1 25 45 mV Vout = 1.2 V setting  $\mathsf{DDVBAT1} = 3.1 \ \mathsf{V} \to 4.5 \ \mathsf{V}$ Line regulation VDCDC1LR IDCDC1 = - 300 mA 4 13 m٧ \_\_\_\_ Vout = 1.2 V setting Oscillation frequency ISTDCDC1 IDCDC1 = -300 mA (CCM)2 3 4 MHz I/O characteristics of control terminal (RESET, LDO1ON, REGCNT) ٧ Low input voltage VIL1 Voltage recognized as low level \_\_\_\_ \_ 0.45 Voltage recognized as high level VIH1 ٧ High input voltage 1.2 Input pull-down resistance PDR1 1 3 6 MΩ \_\_\_\_\_ \_ I/O characteristics of control terminal (ASEL) VDVDD VIL2 Voltage recognized as low level Low input voltage ٧ imes 0.3 V<sub>DVDD</sub> VIH2 High input voltage Voltage recognized as high level V \_\_\_\_ imes 0.7

# AN30183A

### APPLICATION INFORMATION

REFERENCE VALUES FOR DESIGN

#### $V_{VBAT}(DDVBAT1 = VB = VIN2) = 3.7V, DVDD = 1.85V$

$T_a = 25 \ ^\circ C \pm 2 \ ^\circ C$  unless otherwise noted.

|                  | Parameter                              | Cumbol | Conditions                                                            | Refe                    | erence va | alues                             | Unit | Notes    |

|------------------|----------------------------------------|--------|-----------------------------------------------------------------------|-------------------------|-----------|-----------------------------------|------|----------|

|                  | i aranielei                            |        | Symbol Conditions                                                     |                         | Тур       | Max                               | Unit | notes    |

| I <sup>2</sup> C | Bus (Internal I/O Stage Characteristic | cs)    |                                                                       |                         |           | _                                 | _    |          |

|                  | Low-level input voltage                | VIL1   | Voltage which recognized that SDA and SCL are Low-level               | - 0.5                   | _         | $0.3 	imes V_{DVDD}$              | V    | *1<br>*2 |

|                  | High-level input voltage               | VIH1   | Voltage which recognized that SDA and SCL are High-level              | $0.7 	imes V_{ m DVDD}$ | _         | V <sub>DVDD</sub><br>max<br>+ 0.5 | v    | *1<br>*2 |

|                  | Low-level output voltage 1             | VOL1   | V <sub>DVDD</sub> > 2 V<br>SDA(sink current) = 3 mA                   | 0                       | _         | 0.4                               | V    | *2       |

|                  | Low-level output voltage 2             | VOL2   | V <sub>DVDD</sub> < 2 V<br>SDA(sink current) = 3 mA                   | 0                       | _         | $0.2 \times V_{DVDD}$             | V    | *2       |

|                  | Input current each I/O pin             | IL     | SCL, SDA =<br>$0.1 \times V_{DVDDmax}$ to<br>$0.9 \times V_{DVDDmax}$ | - 10                    |           | 10                                | μΑ   | *2       |

|                  | SCL clock frequency                    | FOSC   | _                                                                     | 0                       |           | 400                               | kHz  | *2       |

Notes) \*1 : The input threshold voltage of I²C bus (Vth) is linked to  $V_{\mbox{\tiny DVDD.}}$

In case the pull-up voltage is not  $V_{DVDD}$ , the threshold voltage (Vth) is fixed to (( $V_{DVDD}$  / 2) ± (Schmitt width) / 2) and High-level, Low-level of input voltage are not specified.

In this case, pay attention to Low-level (max.) value (V $_{\rm ILmax}).$

It is recommended that the pull-up voltage of  $I^{2}C$  bus is set to the  $I^{2}C$  bus I/O stage supply voltage (V<sub>DVDD</sub>).

### **APPLICATION INFORMATION (Continued)**

REFERENCE VALUES FOR DESIGN

$V_{VBAT}(DDVBAT1$  = VB = VIN2) = 3.1V to 4.5V,  $V_{DVDD}$  = 1.85V , DC-DC : Co = 4.7  $\mu$ F, Lo = 1  $\mu$ H / LDO : Co =1.0  $\mu$ F T<sub>a</sub> = 25 °C ± 2 °C unless otherwise noted.

|    | Deremeter                        | Symbol       | Conditions                                                                                                                                   | Refe  | erence va | lues  | Unit | Natas |

|----|----------------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------|-------|------|-------|

|    | Parameter                        | Symbol       | Conditions                                                                                                                                   | Min   | Тур       | Max   | Unit | Notes |

| LD | O1 – 4 ( Normal Mode ) - (LDO Re | egulator)    | -                                                                                                                                            |       |           |       |      |       |

|    | Output voltage                   | VLDO         | ILDO = - 150 mA<br>Vout = 1.85 V setting                                                                                                     |       | 1.850     | 1.897 | v    | *2    |

|    | Consumption current on active    | IREGLDO      | Normal mode<br>VB > Vout + 0.1 V or<br>VIN2 > Vout + 0.1 V                                                                                   | 25    | 50        | 75    | μA   | *2    |

|    | I/O voltage difference           | VSATLDO      | ILDO = - 300 mA                                                                                                                              | 0.3   | _         | _     | V    | *2    |

|    | Ripple rejection                 | VLDORR       | $\label{eq:states} \begin{array}{l} \Delta  VB = 3.7 \ V \pm 0.15 \ V \\ ILDO = - \ 150 \ mA \\ fvin = 100 \ Hz \ to \ 10 \ kHz \end{array}$ | _     | - 60      | - 40  | dB   | *2    |

|    | Discharge resistance             | RDISLDO      | _                                                                                                                                            | 50    | 100       | 200   | kΩ   | *2    |

|    | Load change characteristic       | LTRLDO       | $ILDO = -10 \ \mu A \leftrightarrow -100 \ mA$                                                                                               | —     | 30        | 150   | mV   | *2    |

| LD | O1 – 4 ( Power Save Mode ) - (LD | O Regulator) |                                                                                                                                              |       |           |       |      |       |

|    | Output voltage                   | VLDOPS       | ILDO = - 5 mA<br>Vout = 1.85 V setting                                                                                                       | 1.803 | 1.850     | 1.897 | V    | *2    |

|    | Consumption current on active    | IREGLDOPS    | Power Save mode<br>VB > Vout + 0.1 V or<br>VIN2 > Vout + 0.1 V                                                                               | 1     | 3         | 5     | μA   | *2    |

|    | Ripple rejection VLD             |              | $\Delta$ VB = 3.7 V ± 0.15 V<br>ILDO = - 5 mA<br>fvin = 100 Hz to 10 kHz                                                                     | _     | - 10      | - 5   | dB   | *2    |

|    | Short-circuit current            | ISTLDOPS     | VB = 3.7 V<br>VLDO = 0 V                                                                                                                     | 5     | 20        | 40    | mA   | *2    |

### **APPLICATION INFORMATION (Continued)**

REFERENCE VALUES FOR DESIGN

$V_{VBAT}(DDVBAT1$  = VB = VIN2) = 3.1V to 4.5V, DVDD = 1.85V , DC-DC : Co = 4.7  $\mu$ F, Lo = 1  $\mu$ H / LDO : Co =1.0  $\mu$ F  $T_a$  = 25 °C  $\pm$  2 °C unless otherwise noted.

|    | Devemeter                     | Cumbol    | Conditions                                                | Refe  | erence va | alues | Unit | Notes |

|----|-------------------------------|-----------|-----------------------------------------------------------|-------|-----------|-------|------|-------|

|    | Parameter                     | Symbol    | Conditions                                                | Min   | Тур       | Max   | Unit | notes |

| DC | DC1 (DC-DC Step Down Regulat  | or)       |                                                           |       |           | _     | _    |       |

|    | Output Voltage                | VDCDC1    | IDCDC1 = - 300 mA<br>Vout = 1.2 V setting                 | 1.170 | 1.200     | 1.230 | v    | *2    |

|    | Consumption current on active | IREGDCCD1 | IDCDC1 = 0 mA                                             | 10    | 25        | 40    | μA   | *2    |

|    | Output over current limit     | ILIMDCDC1 | From FB1 × 100% to FB1 ×<br>70%<br>VB = 3.7 V             | _     | 1.0       | 1.2   | A    | *2    |

|    | Efficiency 1                  | EFFDCDC11 | DDVBAT1 = 3.4 V<br>VDCDC1 = 2.4 V<br>IDCDC1 = - 150 mA    | 85    | 90        | _     | %    | *2    |

|    | Efficiency 2                  | EFFDCDC12 | DDVBAT1 = 3.7 V<br>VDCDC1 = 1.2 V<br>IDCDC1 = - 150 mA    | 75    | 80        | _     | %    | *2    |

|    | LX leak current               | ILXL1     | DDVBAT1 = 5.5 V<br>DCDC1 = Disable<br>VLX1 = 0 V or 5.5 V | - 1   | 0         | 1     | μA   | *2    |

|    | Discharge resistance          | RDISDCDC1 |                                                           | 0.5   | 1.0       | 2.0   | kΩ   | *2    |

### **APPLICATION INFORMATION (Continued)**

REFERENCE VALUES FOR DESIGN

$V_{VBAT}(DDVBAT1$  = VB = VIN2) = 3.1V to 4.5V, DVDD = 1.85V , DC-DC : Co = 4.7  $\mu$ F, Lo = 1  $\mu$ H / LDO : Co =1.0  $\mu$ F  $T_a$  = 25 °C  $\pm$  2 °C unless otherwise noted.

| Devenedar                                              | Currente                 | Conditions                                                                                                                                          | Refe                                                          | erence va | alues | Linit  | Num   |

|--------------------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----------|-------|--------|-------|

| Parameter                                              | Symbo                    | I Conditions                                                                                                                                        | Min                                                           | Тур       | Max   | - Unit | Notes |

| I <sup>2</sup> C bus (Internal I/O stage chara         | cteristics)              |                                                                                                                                                     |                                                               |           |       |        |       |

| Hysteresis of Schmitt trigge input 1                   | Vhys1                    | $V_{IO}$ > 2 V,<br>Hysteresis 1 of SDA, SCL                                                                                                         | $\begin{array}{c} 0.05 \times \\ V_{\text{DVDD}} \end{array}$ | —         | _     | V      | *2    |

| Hysteresis of Schmitt trigge input 2                   | r Vhys2                  | V <sub>IO</sub> < 2 V,<br>Hysteresis 2 of SDA, SCL                                                                                                  | $0.1 \times V_{DVDD}$                                         | _         | _     | V      | *2    |

| Output fall time from V <sub>IHmin</sub> t             | o V <sub>ILmax</sub> Tof | $\begin{array}{l} Bus \ capacitance: 10 \ pF \ to \\ 400 \ pF \\ I_P \leq 6 \ mA \ (V_{OLmax} = 0.6 \ V) \\ I_P: Max. \ sink \ current \end{array}$ | $20 + 0.1 \times C_b$                                         | _         | 250   | ns     | *2    |

| Pulse width of spikes which be suppressed by the input |                          | _                                                                                                                                                   | 0                                                             | _         | 50    | ns     | *2    |

| Capacitance for each I/O pi                            | n Ci                     | —                                                                                                                                                   | —                                                             | —         | 10    | pF     | *2    |

| I <sup>2</sup> C bus (Bus line specifications)         |                          |                                                                                                                                                     |                                                               |           |       |        |       |

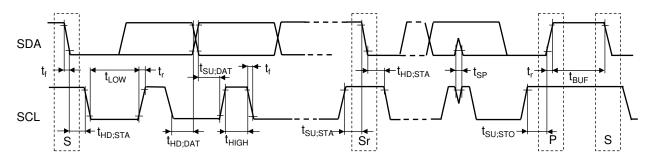

| Hold time<br>(repeated) START condition                | t <sub>HD:STA</sub>      | The first clock pulse is generated after t <sub>HD:STA</sub> .                                                                                      | 0.6                                                           | _         | _     | μs     | *2    |

| Low period of the SCL clock                            | t <sub>LOW</sub>         | —                                                                                                                                                   | 1.3                                                           | _         | _     | μs     | *2    |

| High period of the SCL cloc                            | k t <sub>HIGH</sub>      | _                                                                                                                                                   | 0.6                                                           | _         | _     | μs     | *2    |

| Set-up time for a repeat ST<br>condition               | ART t <sub>su:sta</sub>  | _                                                                                                                                                   | 0.6                                                           |           | _     | μs     | *2    |

| Data hold time                                         | t <sub>HD:DAT</sub>      | _                                                                                                                                                   | 0                                                             |           | 0.9   | μs     | *2    |

| Data set-up time                                       | t <sub>SU:DAT</sub>      | _                                                                                                                                                   | 100                                                           | _         | —     | ns     | *2    |

| Rise time of both SDA and SCL signals                  | t <sub>r</sub>           | _                                                                                                                                                   | $20 + 0.1 \times C_b$                                         | —         | 300   | ns     | *2    |

| Fall time of both SDA and SCL signals                  | t <sub>f</sub>           | _                                                                                                                                                   | $\begin{array}{c} 20 \ + \\ 0.1 \times C_b \end{array}$       | _         | 300   | ns     | *2    |

| Set-up time of STOP condit                             | on t <sub>su:stc</sub>   | —                                                                                                                                                   | 0.6                                                           |           | _     | μs     | *2    |

| Bus free time between STO and START condition          | P t <sub>BUF</sub>       | _                                                                                                                                                   | 1.3                                                           | —         | _     | μs     | *2    |

### **APPLICATION INFORMATION (Continued)**

REFERENCE VALUES FOR DESIGN

$V_{VBAT}(DDVBAT1$  = VB = VIN2) = 3.1V to 4.5V, DVDD = 1.85V , DC-DC : Co = 4.7  $\mu$ F, Lo = 1  $\mu$ H / LDO : Co =1.0  $\mu$ F  $T_a$  = 25 °C  $\pm$  2 °C unless otherwise noted.

|                  | Decemeter                                                | Sumbol            | Conditions                                                             | Refe                  | erence va | alues | Unit | Notes    |

|------------------|----------------------------------------------------------|-------------------|------------------------------------------------------------------------|-----------------------|-----------|-------|------|----------|

|                  | Parameter                                                | Symbol Conditions |                                                                        | Min                   | Тур       | Max   | Unit | Notes    |

| I <sup>2</sup> C | bus (Bus line specifications) (continu                   | ed)               |                                                                        |                       |           |       |      |          |

|                  | Capacitive load for each bus line                        | C <sub>b</sub>    | _                                                                      |                       | _         | 400   | pF   | *2<br>*3 |

|                  | Noise margin at the Low-level for each connected device  | V <sub>nL</sub>   | —                                                                      | $0.1 \times V_{DVDD}$ | _         |       | V    | *2<br>*3 |

|                  | Noise margin at the High-level for each connected device | V <sub>nH</sub>   | _                                                                      | $0.2 \times V_{DVDD}$ | _         | _     | v    | *2<br>*3 |

| Co               | nsumption current                                        |                   |                                                                        |                       |           |       |      |          |

|                  | Static consumption current 2                             | IBAT_4            | DDVBAT1 = VB = VIN2<br>= 3.7 V<br>DCDC1, LDO1 to 4 = OFF<br>RESET= "H" |                       | 8         | 17    | μA   | *2       |

Notes) \*2 :Checked by design, not production tested.

\*3 :The timing of Fast-mode devices in I<sup>2</sup>C-bus is specified as the following.

All values referred to  $V_{IHmin}$  and  $V_{ILmax}$  level.

S: START condition

Sr : Repeat START condition

P: STOP condition

# AN30183A

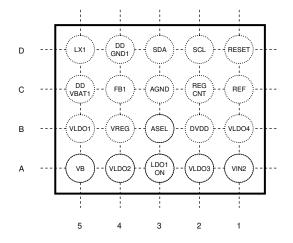

### **PIN CONFIGURATION**

TOP VIEW

### **PIN FUNCTIONS**

| Pin No. | Pin name | Туре         | Description                           |

|---------|----------|--------------|---------------------------------------|

| A1      | VIN2     | Power Supply | Input for LDO3 and LDO4               |

| A2      | VLDO3    | Output       | LDO3 output                           |

| A3      | LDO1ON   | Input        | LDO1 ON/OFF control                   |

| A4      | VLDO2    | Output       | LDO2 output                           |

| A5      | VB       | Power Supply | Input for LDO1, LDO2 and other VB     |

| B1      | VLDO4    | Output       | LDO4 output                           |

| B2      | DVDD     | Power Supply | Power supply for Logic                |

| B3      | ASEL     | Input        | I <sup>2</sup> C slave address select |

| B4      | VREG     | Output       | Reference output                      |

| B5      | VLDO1    | Output       | LDO1 output                           |

| C1      | REF      | Output       | Reference output                      |

| C2      | REGCNT   | Input        | Control to select power setting       |

| C3      | AGND     | Ground       | GND                                   |

| C4      | FB1      | Input        | DCDC1 voltage feedback                |

| C5      | DDVBAT1  | Power Supply | DCDC1 input                           |

| D1      | RESET    | Input        | Reset input for Logic                 |

| D2      | SCL      | Input        | I <sup>2</sup> C clock input          |

| D3      | SDA      | Input/Output | I <sup>2</sup> C data input/output    |

| D4      | DDGND1   | Ground       | GND                                   |

| D5      | LX1      | Output       | DCDC1 switching                       |

Notes) Concerning detail about pin description, please refer to OPERATION and APPLICATION INFORMATION section.

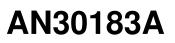

### FUNCTIONAL BLOCK DIAGRAM

- Notes) This application circuit is an example. The operation of mass production set is not guaranteed. You should perform enough evaluation and verification on the design of mass production set. You are fully responsible for the incorporation of the above application circuit and information in the design of your equipment.

- This block diagram is for explaining functions. Part of the block diagram may be omitted, or it may be simplified.

# AN30183A

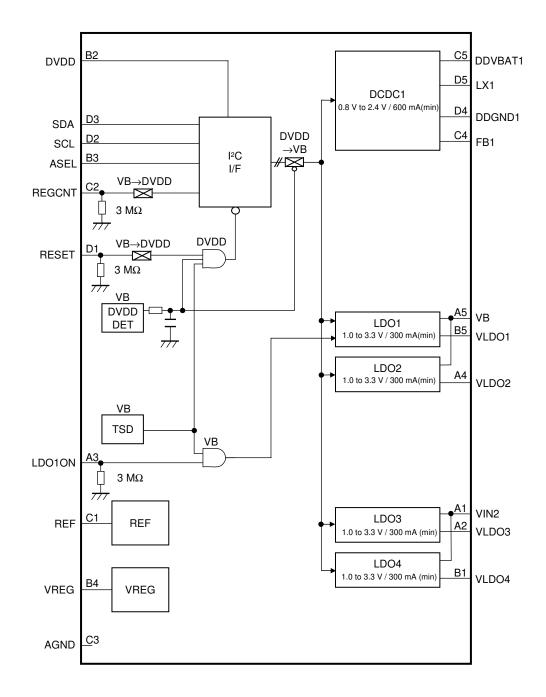

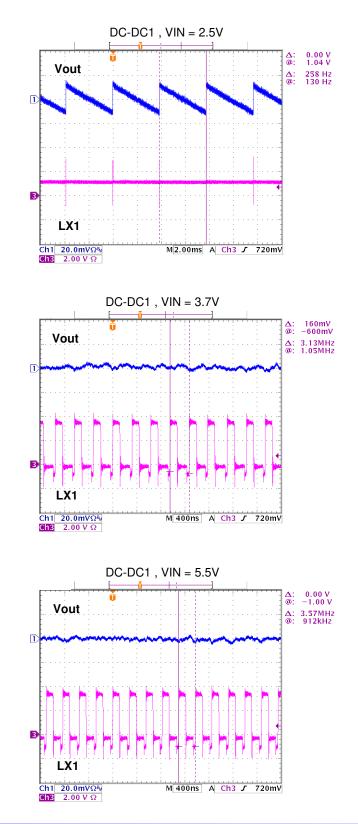

### **TYPICAL CHARACTERISTICS CURVES**

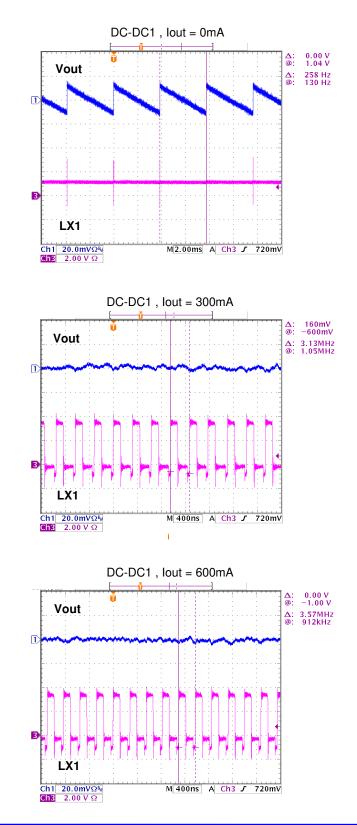

#### (1) Output Ripple Voltage of DC-DC1

$V_{IN} = 3.7 \text{ V}, \text{ DC-DC1}_\text{Vout} = 1.2 \text{ V}, \text{ L1} = 1 \text{ }\mu\text{H}, \text{ CDCDCOUT1} = 4.7 \text{ }\mu\text{F}$

# AN30183A

### TYPICAL CHARACTERISTICS CURVES (Continued)

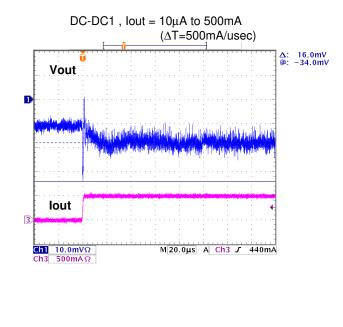

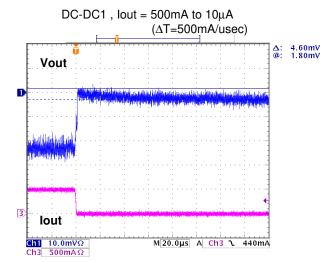

#### (2) Load Transient of DC-DC1

$V_{IN}$  = 3.7 V, DC-DC1\_Vout = 1.2 V , L1 = 1  $\mu$ H , CDCDCOUT1 = 4.7  $\mu$ F

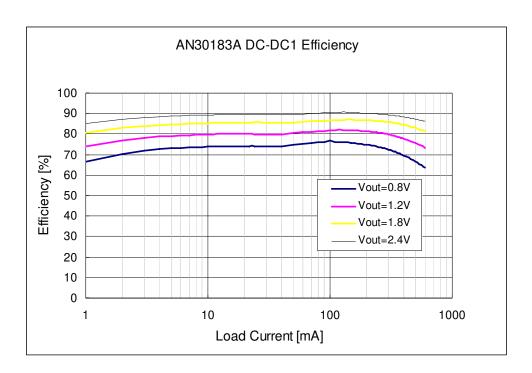

### TYPICAL CHARACTERISTICS CURVES (Continued)

(3) Efficiency of DC-DC1  $$V_{IN}$$  = 3.7 V, DC-DC1\_Vout = 1.2 V , L1 = 1  $\mu H$  , CDCDCOUT1  $\,$  = 4.7  $\mu F$

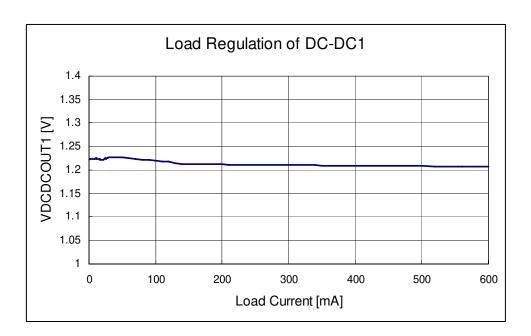

### TYPICAL CHARACTERISTICS CURVES (Continued)

### (4) Load Regulation of DC-DC1

$V_{IN} = 3.7 \text{ V}, \text{ DC-DC1}_\text{Vout} = 1.2 \text{ V}, \text{ L1} = 1 \text{ }\mu\text{H}, \text{ CDCDCOUT1} = 4.7 \text{ }\mu\text{F}$

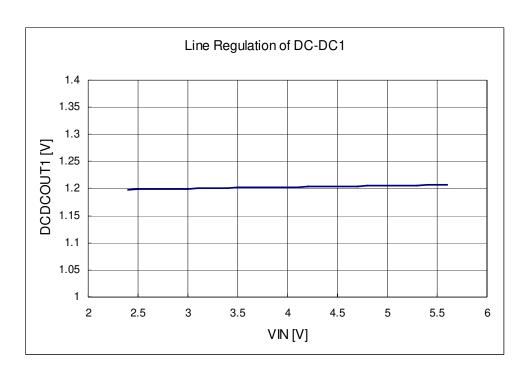

### TYPICAL CHARACTERISTICS CURVES (Continued)

(5) Line Regulation of DC-DC1 lout = 300mA, DC-DC1\_Vout = 1.2 V, L1 = 1  $\mu H$  , CDCDCOUT1 = 4.7  $\mu F$  , V\_{IN} = 2.4V to 5.5V

# AN30183A

### TYPICAL CHARACTERISTICS CURVES (Continued)

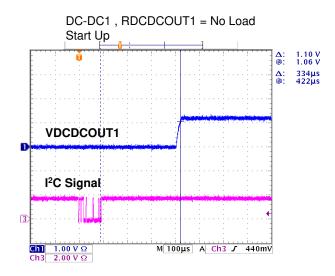

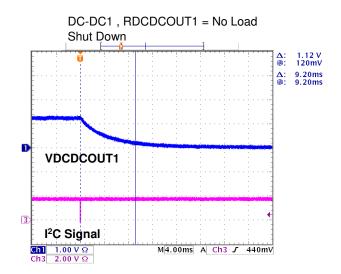

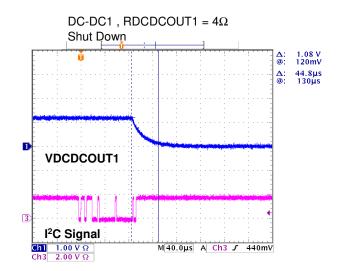

#### (6) Start Up & Shut Down of DC-DC1

$\dot{V}_{IN}$  = 3.7  $\dot{V}$ , DC-DC1\_Vout = 1.2 V, L1 = 1 µH , CDCDCOUT1 = 4.7 µF

# AN30183A

### TYPICAL CHARACTERISTICS CURVES (Continued)

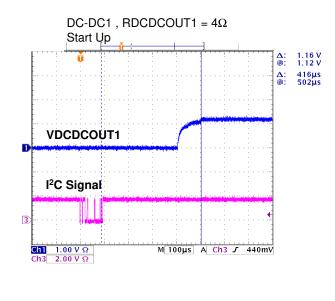

### (7) Start Up & Shut Down of DC-DC1 (Continued)

$V_{IN} = 3.7 \text{ V}, \text{ DC-DC1}_V \text{ out} = 1.2 \text{ V}, \text{ L1} = 1 \,\mu\text{H}, \text{ CDCDCOUT1} = 4.7 \,\mu\text{F}$

# AN30183A

### TYPICAL CHARACTERISTICS CURVES (Continued)

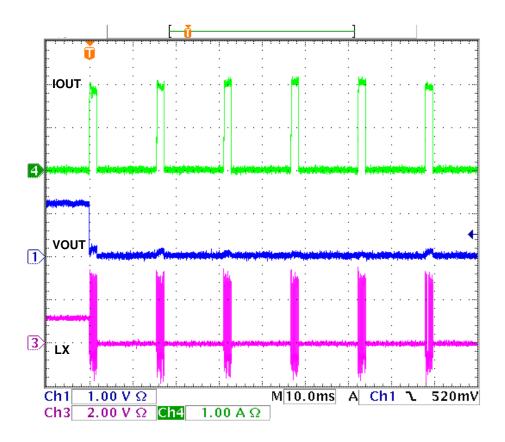

#### (8) Short Protection of DC-DC1

$V_{IN} = 3.7 \text{ V}, \text{ DC-DC1}_\text{Vout} = 1.2 \text{ V}, \text{ L1} = 1 \text{ }\mu\text{H}, \text{ CDCDCOUT1} = 4.7 \text{ }\mu\text{F}$

# AN30183A

### TYPICAL CHARACTERISTICS CURVES (Continued)

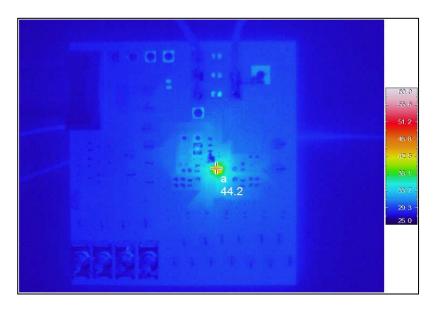

### (9) Thermal Performance of DC-DC1

$V_{IN} = 3.7 \text{ V}, \text{ DC-DC1}_V\text{out} = 1.2 \text{ V}, \text{ ILoad} = 600\text{mA}, \text{ L1} = 1 \text{ }\mu\text{H}, \text{ CDCDCOUT1} = 4.7 \text{ }\mu\text{F}$

# AN30183A

### TYPICAL CHARACTERISTICS CURVES (Continued)

(10) Frequency of DC-DC1  $$V_{\rm IN}$$  = 3.7 V, DC-DC1\_Vout = 1.2 V, L1 = 1  $\mu H$  , CDCDCOUT1 = 4.7  $\mu F$

# AN30183A

### TYPICAL CHARACTERISTICS CURVES (Continued)

(11) Frequency of DC-DC1 (Continued) IOUT = 300mA, DC-DC1\_Vout = 1.2 V, L1 = 1  $\mu H$  , CDCDCOUT1 = 4.7  $\mu F$

# AN30183A

#### OPERATION

Note) The characteristics listed below are reference values derived from the design of the IC and are not guaranteed.

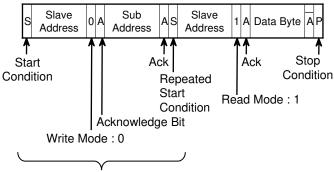

#### 1. I<sup>2</sup>C-bus Interface

a.) Basic Rules

This IC, I2C-bus, is designed to correspond to the Standard-mode (100 kbps) and Fast-mode(400 kbps) devices in the version 2.1 of NXP's specification. However, it does not correspond to the HS-mode (to 3.4 Mbps). This IC will operate as a slave device in the I<sup>2</sup>Cbus system. This IC will not operate as a master device. The program operation check of this IC has not been conducted on the multi-master bus system and the mixspeed bus system, yet. The connected confirmation of this IC to the CBUS receiver also has not been checked. Please confirm with our company if the IC will be used in these mode systems. The I<sup>2</sup>C is the brand of NXP.

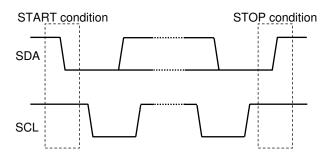

#### b.) START and STOP conditions

A High to Low transition on the SDA line while SCL is High is one such unique case. This situation indicates START condition. A Low to High transition on the SDA line while SCL is High defines STOP condition. START and STOP conditions are always generated by the master. After START condition occur, the bus will be busy. The bus is considered to be free again a certain time after the STOP condition.

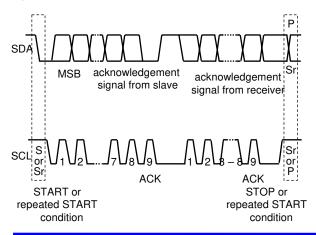

Every byte put on the SDA line must be 8-bits long. The number of bytes that can be transmitted per transfer is unrestricted. Each byte has to be followed by an acknowledge bit. Data is transferred with the most significant bit (MSB) first.

#### d.) Data format

Slave Address

| Pin ASEL | A6 | A5 | A4 | A3 | A2 | A1 | A0 | R/W | Hex |

|----------|----|----|----|----|----|----|----|-----|-----|

| Low      | 1  | 1  | 1  | 0  | 0  | 1  | 0  | х   | 6Eh |

| High     | 1  | 1  | 1  | 0  | 0  | 1  | 1  | х   | 6Fh |

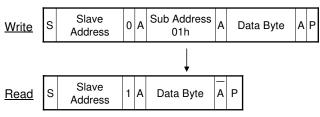

#### Write mode

| s s                                   | lave Address | w | A  | Sub Address | A | Data Byte | A P      |

|---------------------------------------|--------------|---|----|-------------|---|-----------|----------|

| 1                                     |              | A | 1  |             |   |           | 1        |

| Start                                 |              |   | Ac | :k          |   |           | Stop     |

| Start Ack<br>Condition Write mode : 0 |              |   |    |             |   | С         | ondition |

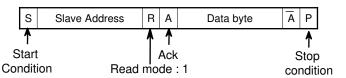

#### Read mode

d1.) When Sub address is not specified

When data is read without assigning sub-address, it is possible to read the value of sub-address specified in Write mode immediately before.

Ex) When writing data into address and reading data from "01 h".

d2.) When Sub address is specified

Sub-address should be assigned first.