# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## AN30185A

## VIN = 2.9V to 5.5V 2ch,0.8A General-purpose High Efficiency Power LSI

### FEATURES

- High-speed response DC-DC Step-Down Regulator circuit that employs hysteretic control system : 2-ch (1.0 V, 0.8 A / 1.8 V, 0.8 A)

- LDO: 1-ch (0.9 V, 10 mA)

- Built-in external Pch MOSFET gate drive circuits

- Built-in Reset function

- Built-in Under Voltage Lockout function (UVLO)

- 24pin Plastic Quad Flat Non-leaded Package (Size : 4 × 4 mm, 0.5 mm pitch)

#### DESCRIPTION

AN30185A is a power management LSI which has DC-DC step down regulators (2-ch) that employs hysteretic control system.

By this system, when load current changes suddenly, it responds at high speed and minimizes the changes of output voltage.

Since it is possible to use capacitors with small capacitance and it is unnecessary to use parts for phase compensation, this IC realizes downsizing of set and reducing in the number of external parts.

Output voltages are 1.0 V and 1.8 V. Each maximum current is 0.8 A.

This LSI has a LDO circuit, external Pch-MOSFET gate drive circuits and a reset circuit of input power supply voltage.

### APPLICATIONS

High Current Distributed Power Systems such as SSD (Solid State Drive), Cellular Phone, etc.

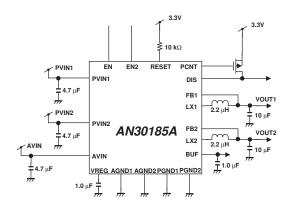

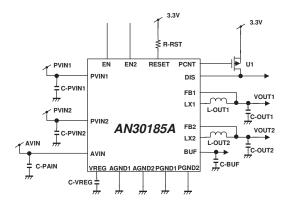

#### SIMPLIFIED APPLICATION

Notes) This application circuit is an example. The operation of mass production set is not guaranteed. You should perform enough evaluation and verification on the design of mass production set. You are fully responsible for the incorporation of the above application circuit and information in the design of your equipment.

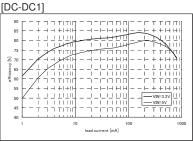

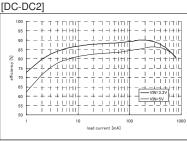

#### **EFFICIENCY CURVE**

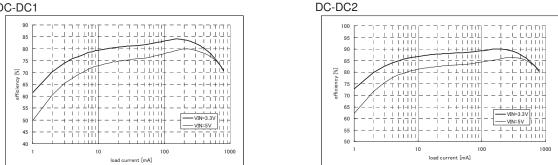

Condition : V<sub>IN</sub>=3.3V or 5.0V , Vout=1.0V , Cout=10µF , Lout=2.2µH

Condition : V<sub>IN</sub>=3.3V or 5.0V , Vout=1.8V , Cout=10µF , Lout=2.2µH

## **ABSOLUTE MAXIMUM RATINGS**

| Parameter                      | Symbol                              | Rating                           | Unit | Notes    |

|--------------------------------|-------------------------------------|----------------------------------|------|----------|

| Supply voltage                 | V <sub>IN</sub>                     | 6.0                              | V    | *1<br>*3 |

| Operating free-air temperature | T <sub>opr</sub>                    | - 40 to + 85                     | °C   | *2       |

| Operating junction temperature | Τ <sub>j</sub>                      | - 40 to + 150                    | °C   | *2       |

| Storage temperature            | $T_{stg}$                           | - 55 to + 150                    | °C   | *2       |

| Input Voltage Range            | EN,EN2,FB1,FB2                      | -0.3 to (V <sub>IN</sub> + 0.3)  | V    | *1<br>*3 |

| Output Voltage Range           | LX1,LX2,PCNT,DIS,<br>RESET,BUF,VREG | – 0.3 to (V <sub>IN</sub> + 0.3) | V    | *1<br>*3 |

| ESD                            | HBM (Human Body Model)              | 2                                | kV   | -        |

Notes) Do not apply external currents and voltages to any pin not specifically mentioned.

This product may sustain permanent damage if subjected to conditions higher than the above stated absolute maximum rating. This rating is the maximum rating and device operating at this range is not guaranteeable as it is higher than our stated recommended operating range. When subjected under the absolute maximum rating for a long time, the reliability of the product may be affected.

\*1: The values under the condition not exceeding the above absolute maximum ratings and the power dissipation.

\*2:Except for the power dissipation, operating ambient temperature, and storage temperature, all ratings are for Ta = 25°C. \*3:V<sub>IN</sub> is voltage for AVIN, PVIN1 = PVIN2,(V<sub>IN</sub> + 0.3) V must not be exceeded 6 V.

### POWER DISSIPATION RATING

| PACKAGE                                            | $\theta_{JA}$ | PD(Ta=25°C) | PD(Ta=85°C) | Notes |

|----------------------------------------------------|---------------|-------------|-------------|-------|

| 9pin Wafer level chip size package<br>(WLCSP Type) | 84.9 °C /W    | 1.472 W     | 0.765 W     | *1    |

Note). For the actual usage, please refer to the PD-Ta characteristics diagram in the package specification, follow the power supply voltage, load and ambient temperature conditions to ensure that there is enough margin and the thermal design does not exceed the allowable value.

\*1:Glass Epoxy Substrate(4 Layers) [Glass-Epoxy: 50 X 50 X 0.8t(mm)] Die Pad Exposed , Soldered.

#### **CAUTION**

Although this has limited built-in ESD protection circuit, but permanent damage may occur on it. Therefore, proper ESD precautions are recommended to avoid electrostatic damage to the MOS gates

## AN30185A

### **RECOMMENDED OPERATING CONDITIONS**

| Parameter            | Symbol          | Min.  | Тур. | Max.                  | Unit | Notes    |

|----------------------|-----------------|-------|------|-----------------------|------|----------|

| Supply voltage range | V <sub>IN</sub> | 2.9   | 3.3  | 5.5                   | V    | *1<br>*2 |

|                      | EN              | - 0.3 | —    | V <sub>IN</sub> + 0.3 | V    | *3       |

| Input Voltage Denge  | EN2             | - 0.3 | —    | V <sub>IN</sub> + 0.3 | V    | *3       |

| Input Voltage Range  | FB1             | - 0.3 | —    | V <sub>IN</sub> + 0.3 | V    | *3       |

|                      | FB2             | - 0.3 | —    | V <sub>IN</sub> + 0.3 | V    | *3       |

|                      | LX1,LX2         | - 0.3 | —    | V <sub>IN</sub> + 0.3 | V    | *3       |

|                      | PCNT            | - 0.3 | —    | V <sub>IN</sub> + 0.3 | V    | *3       |

| Output Valtaga Banga | DIS             | - 0.3 | —    | V <sub>IN</sub> + 0.3 | V    | *3       |

| Output Voltage Range | RESET           | - 0.3 | _    | V <sub>IN</sub> + 0.3 | V    | *3       |

|                      | BUF             | - 0.3 | _    | V <sub>IN</sub> + 0.3 | V    | *3       |

|                      | VREG            | - 0.3 | —    | V <sub>IN</sub> + 0.3 | V    | *3       |

Note) Do not apply external currents and voltages to any pin not specifically mentioned.

Voltage values, unless otherwise specified, are with respect to GND. GND is voltage for AGND1, AGND2, PGND1, PGND2.

AGND1 = AGND2 = PGND1 = PGND2. Vin is voltage for AVIN, PVIN1, PVIN2. AVIN = PVIN1 = PVIN2.

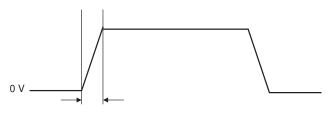

- \*1 : Please set the rising time of power input pin to the following range.

In addition, please input the voltage with the rising time which has margin enough in consideration of the variation in external parts.

- \*2 : The values under the condition not exceeding the above absolute maximum ratings and the power dissipation.

- \*3 : (V<sub>IN</sub> + 0.3) V must not be exceeded 6 V.

100  $\mu s < Tr < 1.5$  ms (Tr is the rise time from 0 V to the setup voltage of V\_IN-)

### **ELECTRICAL CHARACTERISTICS**

$V_{\text{IN}} = \text{AVIN} = \text{PVIN1} = \text{PVIN2} = 3.3\text{V}$

$\label{eq:constraint} \begin{bmatrix} DC-DC1 \end{bmatrix} Cout = 10 \ \mu F \ (GRM21BB31A106K[Murata]) \ , \ Lout = 2.2 \ \mu H \ ( \ NR3012T2R2M[Taiyo \ Yuden]) \ \\ \begin{bmatrix} DC-DC2 \end{bmatrix} Cout = 10 \ \mu F \ (GRM21BB31A106K[Murata]) \ , \ Lout = 2.2 \ \mu H \ ( \ NR3012T2R2M[Taiyo \ Yuden]) \ \\ T_a = 25 \ ^{\circ}C \ \pm 2 \ ^{\circ}C \ unless \ otherwise \ noted. \end{aligned}$

| Devemeter                                                                | Cumhal       | Conditions                                              |       | Limits |       | Unit | Notes |

|--------------------------------------------------------------------------|--------------|---------------------------------------------------------|-------|--------|-------|------|-------|

| Parameter                                                                | Symbol       | Conditions                                              | Min   | Тур    | Max   | Unit | Notes |

| C-DC1] (1.0 V DC/DC step-down regu<br>C-DC2] (1.8 V DC/DC step-down regu |              |                                                         |       |        |       |      |       |

| Consumption current at active                                            | IACT         |                                                         | _     | 200    | 300   | μA   | _     |

| EN pin Low-level input voltage                                           | VENL         | $V_{IN} = 3.3 V$                                        | —     | 0      | 0.3   | V    | —     |

| EN pin High-level input voltage                                          | VENH         | V <sub>IN</sub> = 3.3 V                                 | 1.5   | 3.3    | —     | V    | —     |

| EN pin leak current                                                      | ILEAK<br>EN  | EN = 3.3 V                                              | _     | 2.4    | 10    | μA   |       |

| EN2 pin Low-level input voltage                                          | VEN2L        | V <sub>IN</sub> = 3.3 V                                 |       | 0      | 0.3   | V    | —     |

| EN2 pin High-level input voltage                                         | VEN2H        | V <sub>IN</sub> = 3.3 V                                 | 1.5   | 3.3    | _     | V    | _     |

| EN2 pin leak current                                                     | ILEAK<br>EN2 | EN2 = 3.3 V                                             |       | 2.0    | 10    | μA   | _     |

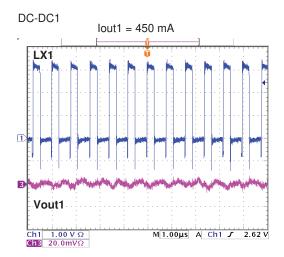

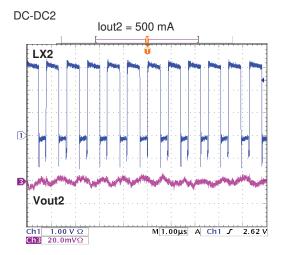

| DC-DC1 output voltage                                                    | DD1<br>VOUT  | I <sub>OUT1</sub> = 450 mA                              | 0.980 | 1.000  | 1.020 | V    | _     |

| DC-DC2 output voltage                                                    | DD2<br>VOUT  | I <sub>OUT2</sub> = 500 mA                              | 1.764 | 1.800  | 1.836 | V    | _     |

| UVLO start voltage                                                       | VUVLO<br>DET | $V_{\text{IN}} = 3.3 \text{ V} \rightarrow 0 \text{ V}$ | 2.4   | 2.5    | 2.6   | V    |       |

| UVLO stop voltage                                                        | VUVLO<br>RMV | $V_{\text{IN}} = 0 \text{ V} \rightarrow 3.3 \text{ V}$ | 2.45  | 2.6    | 2.8   | V    | _     |

| Reset detection voltage                                                  | VRST<br>DET  | $V_{\text{IN}} = 3.3 \text{ V} \rightarrow 0 \text{ V}$ | 2.740 | 2.810  | 2.880 | V    | _     |

| Reset cancel voltage                                                     | VRST<br>RMV  | $V_{\text{IN}} = 0 \text{ V} \rightarrow 3.3 \text{ V}$ | 2.847 | 2.920  | 2.993 | V    | _     |

| Reset ON resistance                                                      | RON<br>RST   | EN = 0 V                                                | _     | 10     | 20    | Ω    | _     |

| DIS discharge resistance                                                 | RON<br>DIS   | EN = 0 V                                                | _     | 90     | 190   | Ω    | _     |

| BUF output voltage                                                       | BUF<br>VOUT  | $I_{OUT(BUF)} = 10 \ \mu A$                             | 0.873 | 0.900  | 0.927 | V    | _     |

### ELECTRICAL CHARACTERISTICS (Continued)

$V_{\text{IN}} = \text{AVIN} = \text{PVIN1} = \text{PVIN2} = 3.3\text{V}$

$\label{eq:constraint} \begin{bmatrix} DC-DC1 \end{bmatrix} Cout = 10 \ \mu F \ (GRM21BB31A106K[Murata]) \ , \ Lout = 2.2 \ \mu H \ ( \ NR3012T2R2M[Taiyo \ Yuden]) \ \\ \begin{bmatrix} DC-DC2 \end{bmatrix} Cout = 10 \ \mu F \ (GRM21BB31A106K[Murata]) \ , \ Lout = 2.2 \ \mu H \ ( \ NR3012T2R2M[Taiyo \ Yuden]) \ \\ T_a = 25 \ ^{\circ}C \ \pm 2 \ ^{\circ}C \ unless \ otherwise \ noted. \end{aligned}$

| Parameter                                                                    | Symbol       | Conditions                                                                                                                 | Refe | erence va | alues | Unit    | Notes |

|------------------------------------------------------------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------|------|-----------|-------|---------|-------|

| Farameter                                                                    | Symbol       | Conditions                                                                                                                 | Min  | Тур       | Max   | Unit    | NULES |

| [DC-DC1] (1.0 V DC/DC step-down regu<br>[DC-DC2] (1.8 V DC/DC step-down regu |              |                                                                                                                            |      |           |       |         |       |

| Consumption current at standby                                               | ISTB         | EN = 0 V                                                                                                                   | _    | 0         |       | μA      | *1    |

| DC-DC1 line regulation                                                       | DD1<br>REGIN | $\begin{array}{l} V_{\text{IN}} = 2.9 \text{ V} \rightarrow 5.5 \text{ V} \\ I_{\text{OUT1}} = 450 \text{ mA} \end{array}$ | _    | 6         | _     | mV      | *1    |

| DC-DC2 line regulation                                                       | DD2<br>REGIN | $\begin{array}{l} V_{\text{IN}} = 2.9 \text{ V} \rightarrow 5.5 \text{ V} \\ I_{\text{OUT2}} = 500 \text{ mA} \end{array}$ | _    | 8         | _     | mV      | *1    |

| DC-DC1 load regulation                                                       | DD1<br>REGLD | $I_{OUT1} = 10 \; \mu A \rightarrow 800 \; mA$                                                                             | —    | 10        | _     | mV      | *1    |

| DC-DC2 load regulation                                                       | DD2<br>REGLD | $I_{OUT2} = 10 \; \mu A \rightarrow 800 \; mA$                                                                             | _    | 15        | _     | mV      | *1    |

| DC-DC1 output current limit                                                  | DD1<br>ILMT  | $FB1 = 1.0 \text{ V} \rightarrow 0.5 \text{ V}$                                                                            | —    | 1.6       | _     | A       | *1    |

| DC-DC2 output current limit                                                  | DD2<br>ILMT  | $FB2 = 1.8 \text{ V} \rightarrow 0.9 \text{ V}$                                                                            | —    | 1.6       | _     | A       | *1    |

| DC-DC1 efficiency 1                                                          | DD1<br>EFF1  | V <sub>IN</sub> = 3.3 V<br>I <sub>OUT1</sub> = 10 mA                                                                       | _    | 77        | _     | %       | *1    |

| DC-DC1 efficiency 2                                                          | DD1<br>EFF2  | $V_{IN} = 5 V$<br>$I_{OUT1} = 10 mA$                                                                                       | _    | 71        | _     | %       | *1    |

| DC-DC1 efficiency 3                                                          | DD1<br>EFF3  | $V_{IN} = 3.3 V$<br>$I_{OUT1} = 450 mA$                                                                                    | _    | 80        | _     | %       | *1    |

| DC-DC1 efficiency 4                                                          | DD1<br>EFF4  | $V_{IN} = 5 V$<br>$I_{OUT1} = 450 mA$                                                                                      | _    | 77        | _     | %       | *1    |

| DC-DC2 efficiency 1                                                          | DD2<br>EFF1  | $V_{IN} = 3.3 V$<br>$I_{OUT2} = 10 mA$                                                                                     | _    | 86        | _     | %       | *1    |

| DC-DC2 efficiency 2                                                          | DD2<br>EFF2  | $V_{IN} = 5 V$<br>$I_{OUT2} = 10 mA$                                                                                       | _    | 80        | _     | %       | *1    |

| DC-DC2 efficiency 3                                                          | DD2<br>EFF3  | $\begin{array}{l} V_{\text{IN}} = 3.3 \text{ V} \\ I_{\text{OUT2}} = 500 \text{ mA} \end{array}$                           | _    | 85        | _     | %       | *1    |

| DC-DC2 efficiency 4                                                          | DD2<br>EFF4  | $V_{IN} = 5 V$<br>$I_{OUT2} = 500 \text{ mA}$                                                                              | _    | 84        | _     | %       | *1    |

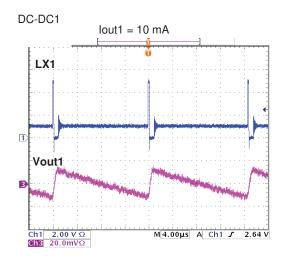

| DC-DC1 output ripple voltage 1                                               | DD1<br>VRPL1 | I <sub>OUT1</sub> = 10 mA                                                                                                  | _    | 30        | _     | mV[p-p] | *1    |

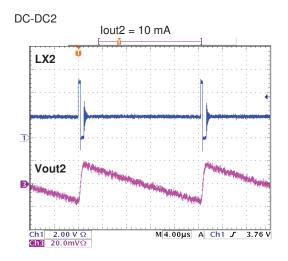

| DC-DC1 output ripple voltage 2                                               | DD1<br>VRPL2 | I <sub>OUT1</sub> = 450 mA                                                                                                 | _    | 7         | _     | mV[p-p] | *1    |

| D-CDC2 output ripple voltage 1                                               | DD2<br>VRPL1 | I <sub>OUT2</sub> = 10 mA                                                                                                  | _    | 30        | _     | mV[p-p] | *1    |

| DC-DC2 output ripple voltage 2                                               | DD2<br>VRPL2 | I <sub>OUT2</sub> = 500 mA                                                                                                 | _    | 7         | _     | mV[p-p] | *1    |

\*1 : Typical Value checked by design.

### ELECTRICAL CHARACTERISTICS (Continued)

$V_{\text{IN}} = \text{AVIN} = \text{PVIN1} = \text{PVIN2} = 3.3\text{V}$

$\begin{bmatrix} DC-DC1 \end{bmatrix} Cout = 10 \ \mu\text{F} (GRM21BB31A106K[Murata]), Lout = 2.2 \ \mu\text{H} (NR3012T2R2M[Taiyo Yuden]) \\ \begin{bmatrix} DC-DC2 \end{bmatrix} Cout = 10 \ \mu\text{F} (GRM21BB31A106K[Murata]), Lout = 2.2 \ \mu\text{H} (NR3012T2R2M[Taiyo Yuden]) \\ T_a = 25 \ ^{\circ}C \pm 2 \ ^{\circ}C \ unless \ otherwise \ noted.$

| Devemeter                                                                  | Cumphal     | Conditions                                                                                                                         | Refe | erence va | alues | Unit | Notes |

|----------------------------------------------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------|------|-----------|-------|------|-------|

| Parameter                                                                  | Symbol      | Conditions                                                                                                                         | Min  | Тур       | Max   | Unit | Notes |

| C-DC1] (1.0 V DC/DC step-down regul<br>C-DC2] (1.8 V DC/DC step-down regul |             |                                                                                                                                    |      |           |       |      |       |

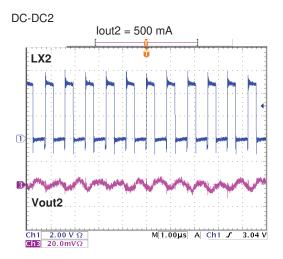

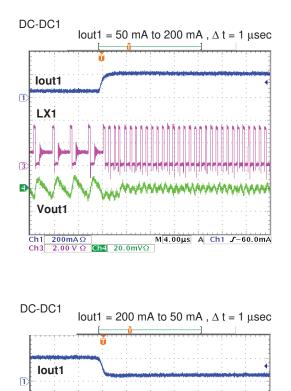

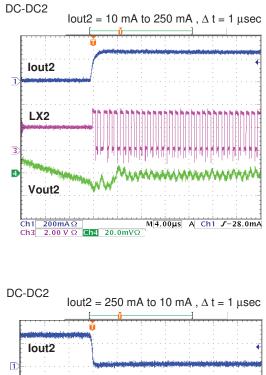

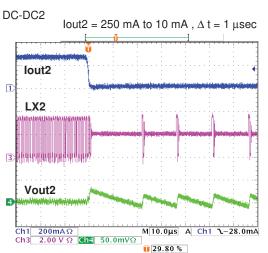

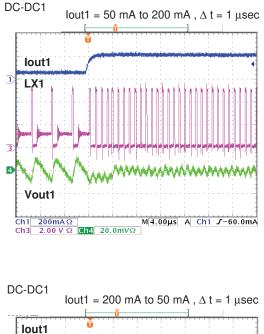

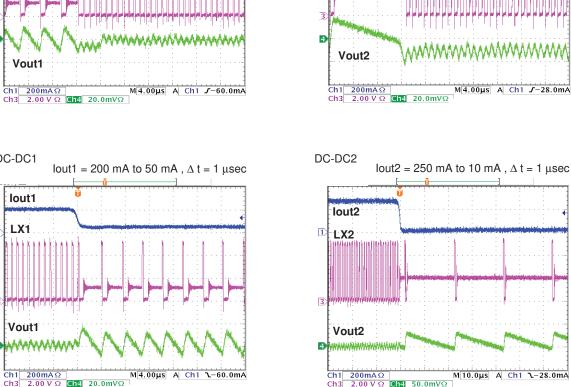

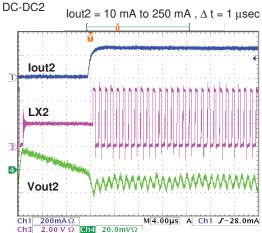

| DC-DC1 load transient response                                             | DD1<br>DVAC | $\begin{array}{l} I_{\text{OUT1}} = 50 \text{ mA} \leftrightarrow 200 \text{ mA} \\ \Delta \text{ t} = 1  \mu\text{s} \end{array}$ | _    | 25        | _     | mV   | *1    |

| DC-DC2 load transient response                                             | DD2<br>DVAC | $I_{OUT2} = 10 \text{ mA} \leftrightarrow 250 \text{ mA}$<br>$\Delta t = 1  \mu \text{s}$                                          | —    | 25        | _     | mV   | *1    |

| DC-DC1 operating frequency                                                 | DD1<br>FSW  | I <sub>OUT1</sub> = 450 mA                                                                                                         | —    | 1.2       | _     | MHz  | *1    |

| DC-DC2 operating frequency                                                 | DD2<br>FSW  | I <sub>OUT2</sub> = 500 mA                                                                                                         | _    | 1.2       | _     | MHz  | *1    |

| DC-DC1 discharge resistance                                                | DD1<br>RDIS | EN = 0 V                                                                                                                           | _    | 100       | _     | Ω    | *1    |

| DC-DC2 discharge resistance                                                | DD2<br>RDIS | EN = 0 V                                                                                                                           | _    | 150       | _     | Ω    | *1    |

| DC-DC1 Pch-MOS ON resistance                                               | DD1<br>RONP | _                                                                                                                                  | —    | 0.25      | _     | Ω    | *1    |

| DC-DC2 Pch-MOS ON resistance                                               | DD2<br>RONP | _                                                                                                                                  | —    | 0.3       |       | Ω    | *1    |

| DC-DC1 Nch-MOS ON resistance                                               | DD1<br>RONN | _                                                                                                                                  | —    | 0.2       | _     | Ω    | *1    |

| DC-DC2 Nch-MOS ON resistance                                               | DD2<br>RONN | _                                                                                                                                  | —    | 0.25      | _     | Ω    | *1    |

| DC-DC1 start time                                                          | DD1<br>TSTU | Capacitive load : $26 \ \mu F$<br>I <sub>OUT1</sub> = 0 A<br>The time until 90 % from 10 %<br>of target value.                     | _    | 0.1       | _     | ms   | *1    |

| DC-DC2 start time                                                          | DD2<br>TSTU | Capacitive load : $24 \ \mu F$<br>I <sub>OUT2</sub> = 0 A<br>The time until 90 % from 10 %<br>of target value.                     |      | 0.15      |       | ms   | *1    |

\*1 : Typical Value checked by design.

### ELECTRICAL CHARACTERISTICS (Continued)

$V_{\text{IN}} = \text{AVIN} = \text{PVIN1} = \text{PVIN2} = 3.3\text{V}$

$[DC-DC1] \ Cout = 10 \ \mu F \ (GRM21BB31A106K[Murata]), \ Lout = 2.2 \ \mu H \ (NR3012T2R2M[Taiyo Yuden]) \\ [DC-DC2] \ Cout = 10 \ \mu F \ (GRM21BB31A106K[Murata]), \ Lout = 2.2 \ \mu H \ (NR3012T2R2M[Taiyo Yuden]) \\ T_a = 25 \ ^{\circ}C \ \pm 2 \ ^{\circ}C \ unless \ otherwise \ noted.$

| Duranta                                                                      | 0                |                                                                                                                                      | Refe | erence va | alues | 11.2 |       |

|------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------|------|-----------|-------|------|-------|

| Parameter                                                                    | Symbol           | Conditions                                                                                                                           | Min  | Тур       | Max   | Unit | Notes |

| [DC-DC1] (1.0 V DC/DC step-down regu<br>[DC-DC2] (1.8 V DC/DC step-down regu |                  | -                                                                                                                                    |      |           |       |      |       |

| BUF line regulation                                                          | BUF<br>REG<br>IN | $\begin{array}{l} V_{\text{IN}} = 2.9V \rightarrow 5.5V \\ I_{\text{OUT(BUF)}} = 10 \; \mu A \end{array} \end{array} \label{eq:VIN}$ | _    | 0         | _     | mV   | *1    |

| BUF load regulation                                                          | BUF<br>REG<br>LD | $I_{OUT(BUF)} = 10 \ \mu A \rightarrow 10 \ mA$                                                                                      | _    | 5         |       | mV   | *1    |

| BUD output current limit                                                     | BUF<br>ILMT      | BUF = 0V                                                                                                                             | _    | 10        | _     | mA   | *1    |

| BUF PSRR                                                                     | BUF<br>PSR       | $I_{OUT(BUF)} = 10 \ \mu A$<br>f = 10 kHz                                                                                            |      | -50       |       | dB   | *1    |

| BUF load transient response 1                                                | BUF<br>DVAC<br>1 | $\begin{array}{l} I_{OUT(BUF)} = 10 \; \mu A \rightarrow 10 \; mA \\ \Delta \; t = 1 \; \mu s \end{array}$                           | _    | 160       | _     | mV   | *1    |

| BUF load transient response 2                                                | BUF<br>DVAC<br>2 | $\begin{array}{l} I_{OUT(BUF)} = 10 \text{ mA} \rightarrow 10 \mu\text{A} \\ \Delta \ t = 1 \mu\text{s} \end{array}$                 | _    | 100       | _     | mV   | *1    |

| BUF discharge resistance                                                     | BUF<br>RDIS      | EN = 0 V                                                                                                                             | _    | 80        | _     | Ω    | *1    |

| BUF start time                                                               | BUF<br>TSTU      | $I_{OUT(BUF)} = 0 \text{ A}$<br>The time until 90 % from 10 % of target value.                                                       | —    | 50        |       | μs   | *1    |

| Reset delay                                                                  | RST<br>DLY       | —                                                                                                                                    | —    | 30        | _     | ms   | *1    |

| PCNT sink current                                                            | IPCNT            | PCNT = 3.3 V                                                                                                                         | _    | 2.5       | _     | μA   | *1    |

| Timer latch time                                                             | TLAT<br>CH       | _                                                                                                                                    | _    | 1         | _     | ms   | *1    |

| DC-DC1 Ground-short detection voltage                                        | DD1<br>SCP       | $FB1 = 1.0 \ V \to 0 \ V$                                                                                                            | _    | 0.5       | _     | V    | *1    |

| DC-DC2 Ground-short detection voltage                                        | DD2<br>SCP       | $FB2 = 1.8 \text{ V} \rightarrow 0 \text{ V}$                                                                                        |      | 0.9       |       | V    | *1    |

| TSD operating temperature                                                    | TJSO             | Temperature error detection                                                                                                          | —    | 160       | _     | °C   | *1    |

\*1 : Typical Value checked by design.

## AN30185A

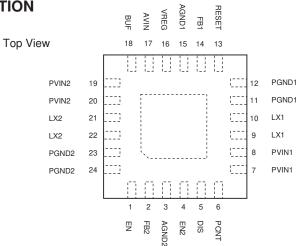

#### **PIN CONFIGURATION**

### **PIN FUNCTION**

| Pin No. | Pin name | Туре         | Description                                                           |

|---------|----------|--------------|-----------------------------------------------------------------------|

| 1       | EN       | Input        | ON/OFF control pin                                                    |

| 2       | FB2      | Input        | Feed Back pin ( for DC-DC2 )                                          |

| 3       | AGND2    | Ground       | Ground pin                                                            |

| 4       | EN2      | Input        | DCDC2 and BUF control pin                                             |

| 5       | DIS      | Output       | Discharge pin ( open drain )                                          |

| 6       | PCNT     | Output       | External Pch MOSFET gate control pin                                  |

| 7       | PVIN1    | Power supply | Power supply pin ( for DC-DC1 )                                       |

| 8       | PVIN1    | Power supply | Power supply pin ( for DC-DC1 )                                       |

| 9       | LX1      | Output       | Driver output pin ( for DC-DC1 )                                      |

| 10      | LX1      | Output       | Driver output pin ( for DC-DC1 )                                      |

| 11      | PGND1    | Ground       | Ground pin ( for DC-DC1 )                                             |

| 12      | PGND1    | Ground       | Ground pin ( for DC-DC1 )                                             |

| 13      | RESET    | Output       | Reset output pin ( open drain )                                       |

| 14      | FB1      | Input        | Feed Back pin ( for DC-DC1 )                                          |

| 15      | AGND1    | Ground       | Ground pin                                                            |

| 16      | VREG     | Output       | LDO output pin ( Power supply for internal control circuit / 2.55 V ) |

| 17      | AVIN     | Power supply | Power supply pin                                                      |

| 18      | BUF      | Output       | LDO output pin ( 0.9 V )                                              |

| 19      | PVIN2    | Power supply | Power supply pin ( for DC-DC2 )                                       |

| 20      | PVIN2    | Power supply | Power supply pin ( for DC-DC2 )                                       |

| 21      | LX2      | Output       | Driver output pin ( for DC-DC2 )                                      |

| 22      | LX2      | Output       | Driver output pin ( for DC-DC2 )                                      |

| 23      | PGND2    | Ground       | Ground pin ( for DC-DC2 )                                             |

| 24      | PGND2    | Ground       | Ground pin ( for DC-DC2 )                                             |

Notes) Concerning detail about pin description, please refer to OPERATION and APPLICATION INFORMATION section.

AN30185A

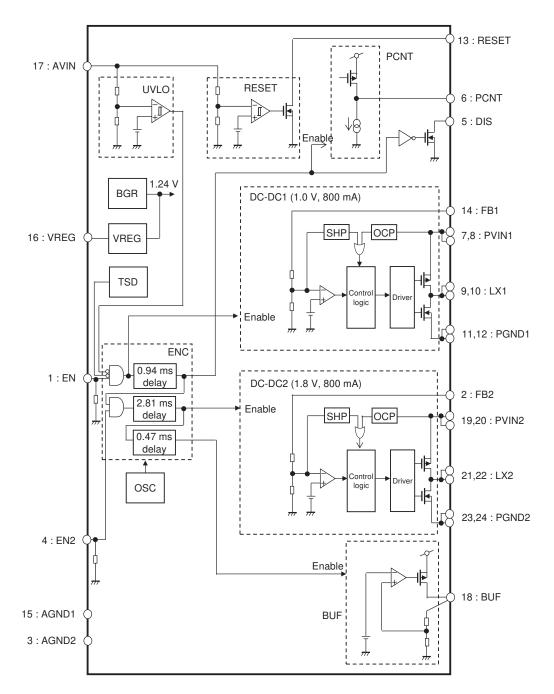

### FUNCTIONAL BLOCK DIAGRAM

Notes) This block diagram is for explaining functions. Part of the block diagram may be omitted, or it may be simplified.

### OPERATION

### 1. Pin Setting For Start / Stop Control

| EN                                         | Hiç      | ŋh  | Low  |     |  |

|--------------------------------------------|----------|-----|------|-----|--|

| EN2                                        | High Low |     | High | Low |  |

| DC-DC1(1.0V)                               | ON       | ON  | OFF  | OFF |  |

| External Pch-MOSFE<br>Gate control circuit | ON       | ON  | OFF  | OFF |  |

| DC-DC2(1.8V)                               | ON       | OFF | OFF  | OFF |  |

| BUF(0.9V)                                  | ON       | OFF | OFF  | OFF |  |

EN pin is the main control pin. When EN pin becomes High, DC-DC1 and external Pch-MOSFET gate control circuit turn on, and DC-DC2 and BUF become controllable by EN2 pin. EN2 pin is the control pin for DC-DC2 and BUF. When EN2 pin becomes High, DC-DC2 and BUF turn on.

Even if EN2 is High under the condition that EN is Low, DC-DC2 and BUF do not turn on.

### **OPERATION** (Continued)

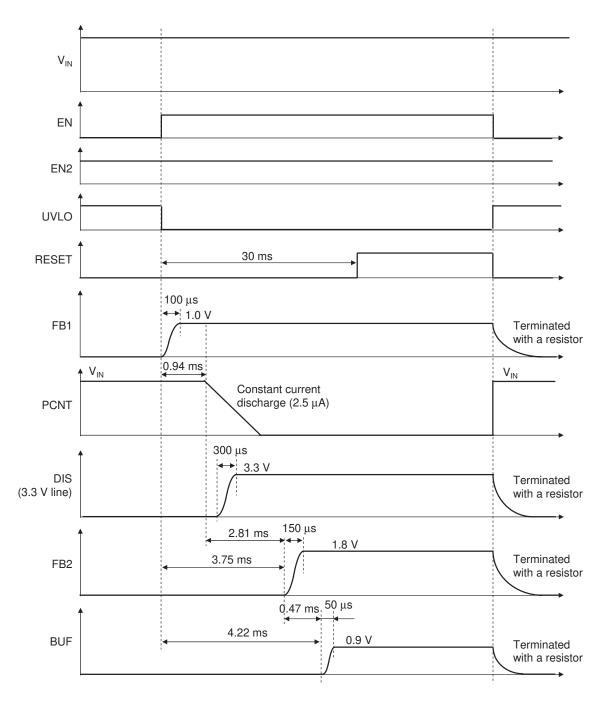

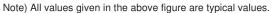

#### 2. Start / Stop Control Timing Chart

Note) The characteristics listed below are reference values derived from the design of the IC and are not guaranteed.

Start / Stop control sequence by EN pin under the condition that EN2 pin is fixed to High is as follows.

Note) All values given in the above figure are typical values.

### **OPERATION** (Continued)

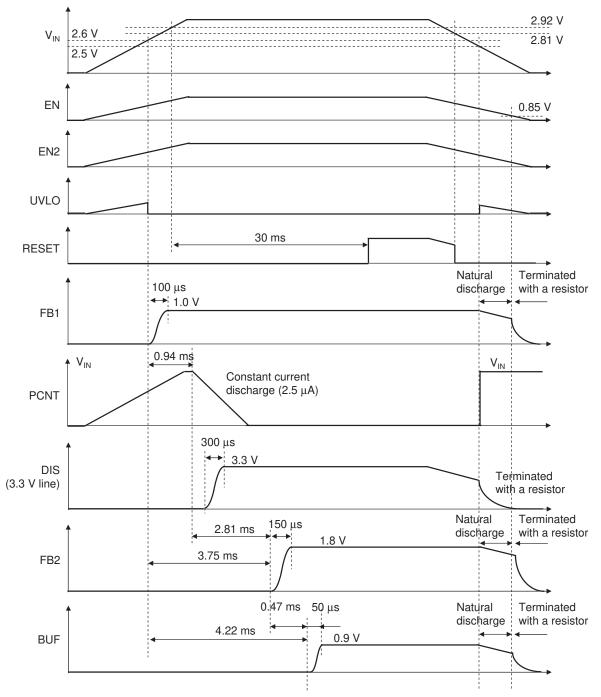

#### 2. Start / Stop Control Timing Chart

Note) The characteristics listed below are reference values derived from the design of the IC and are not guaranteed.

Start / Stop sequence in case that EN pin and EN2 pin are connected to power supply  $(V_{IN})$  is as follows.

### **OPERATION** (Continued)

#### 2. Start / Stop Control Timing Chart

Note) The characteristics listed below are reference values derived from the design of the IC and are not guaranteed.

Start / Stop control sequence by EN2 pin under the condition that EN pin is fixed to High is as follows.

### **OPERATION** (Continued)

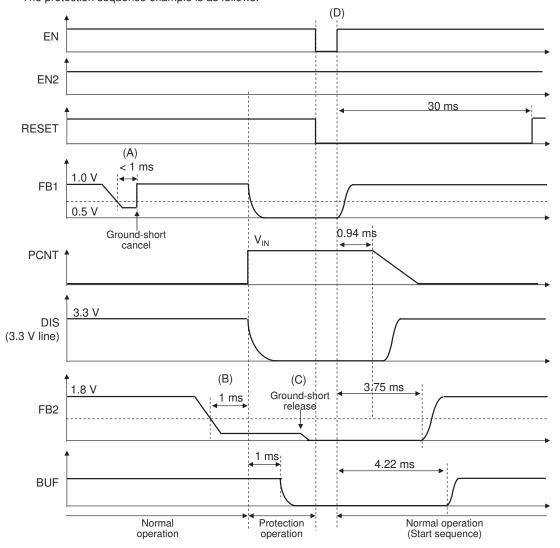

#### 3. Protection

Note) The characteristics listed below are reference values derived from the design of the IC and are not guaranteed.

• UVLO function

When power supply rises to 2.6 V or higher at EN = High, UVLO is released, and the operation of each function starts.

Since this function's hysteresis is 100 mV, UVLO detects when power supply falls to 2.5 V or lower, then each function shuts down.

Reset function

RESET pin shifts to High at 30 ms delay after power supply rises to 2.92 V or higher. (Output type : Nch MOS open drain) Since this function's hysteresis is 110 mV, RESET pin shifts to Low when power supply falls to 2.81 V or lower.(No delay in case of High  $\rightarrow$  Low)

• DC-DC1 (Output voltage : 1.0 V)

When UVLO is released, DC-DC1 starts and outputs 1.0 V. Soft-start function operates for 1 ms after startup. Since output voltage rises slowly, limiting input current, it is possible to prevent rush current and overshoot. When UVLO detects, DC-DC1 turns off. When EN pin shifts to Low, an output pin (FB1) is terminated with a resistor.

External Pch-MOSFET gate control function

PCNT pin is discharged by the constant current (2.5  $\mu$ A) at 0.94 ms delay after UVLO is released. By connecting the gate of Pch MOSFET to PCNT pin, it is possible to turn on this FET softly. At the same time, the termination with a resistor of DIS pin is released. Just after UVLO detects, PCNT pin voltage becomes V<sub>IN</sub> and DIS pin is terminated with a resistor.

• DC-DC2 (Output voltage : 1.8 V)

When both EN pin and EN2 pin are fixed to High, DC-DC2 turns on and outputs 1.8 V. Start-up timing is as follows.

- 1) In case that EN pin becomes Low  $\rightarrow$  High when EN2 pin is fixed to High  $\rightarrow~$  3.75 ms delay from UVLO release

- 2) In case that EN2 pin becomes Low  $\rightarrow$  High within 3.75 ms from UVLO release when EN pin is fixed to High

- $\rightarrow$  3.75 ms delay from UVLO release

- 3) In case that EN2 pin becomes Low  $\rightarrow$  High after 3.75 ms from UVLO release when EN pin is fixed to High

- $\rightarrow$  1.88 ms to 3.76 ms delay from when EN2 pin becomes Low  $\rightarrow$  High

DC-DC2 has the same soft-start function as DC-DC1 and starts, preventing rush current and overshoot. DC-DC2 stops because UVLO detects. When EN pin shifts to Low, an output pin (FB2) is terminated with a resistor.

DC-DC2 also stops when EN2 pin becomes Low, and the output pin is terminated with a resistor.

• BUF (Output voltage : 0.9 V)

BUF pin outputs 0.9 V when both EN pin and EN2 pin are fixed to High. Start-up timing is 0.47 ms delay after DC-DC2

turns on. BUF starts, preventing rush current and overshoot.

BUF stops because UVLO detects. BUF is terminated with a resistor when EN pin shifts to Low.

BUF also stops when EN2 pin becomes Low, and the output pin is terminated with a resistor.

### **OPERATION** (Continued)

#### 3. Protection

Note) The characteristics listed below are reference values derived from the design of the IC and are not guaranteed.

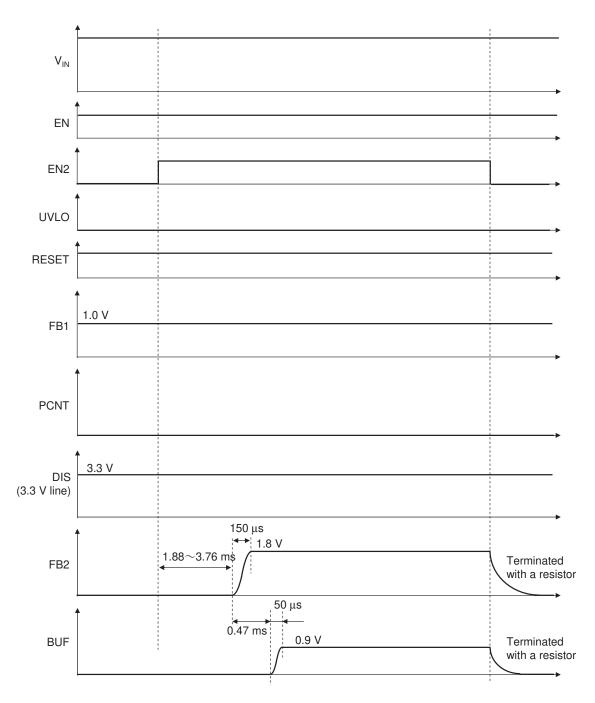

Ground-short protection function

DC-DC1 and DC-DC2 have ground-short detection circuits respectively. When output voltage falls to 50% or lower Of target value (DC-DC1 : 0.5 V, DC-DC2 : 0.9 V), it shifts to the protection sequence shown in [3.Protection]. However, even if BUF pin shorts to GND, BUF does not shift to the protection sequence.

Over-current limit function

DC-DC1, DC-DC2 and BUF have over-current limit circuits respectively. This function limits the output current which exceeds the setup value. The over-current limit characteristics are as follows.

The output currents of DC-DC1 and DC-DC2 are limited to 1.6 A(typ) regardless of the output voltage. BUF has limit characteristics, which the output current decreases as the output voltage falls. The peak input current is 40 mA(typ). The input current at BUF = 0 V is 10 mA(typ).

### **OPERATION** (Continued)

#### 3. Protection

Note) The characteristics listed below are reference values derived from the design of the IC and are not guaranteed.

Protection Sequence

When the following state continues for 1 ms(typ), AN30185A shifts to the protection sequence.

Any of DCDC1 and DCDC2 shorts to GND. (Output voltage is 50% or lower of target value.)

TSD circuit detects abnormal state.

When this LSI shifts to the protection sequence, it is latched to the state at which each function is shut down. It recovers from the protection sequence by applying to EN pin again or releasing UVLO again. The protection sequence example is as follows.

In (A) of the above figure, DCDC1 output shorts to GND. However, this LSI doesn't shift to protection sequence because the term of ground-short is 1 ms or shorter.

In (B) of the above figure, DCDC2 output shorts to GND. After ground-short state continues for 1 ms, this LSI shifts to protection sequence, DCDC1, DCDC2 and external Pch-MOSFET gate drive circuits shift to OFF state, and BUF shifts to OFF state after another 1 ms and are latched.

Even if ground-short is released, the operation of each circuit does not recover (C).

During the protection sequence, RESET pin is not set to Low.

In (D) of the above figure, they recover to normal start sequence after EN is input again.

### **OPERATION** (Continued)

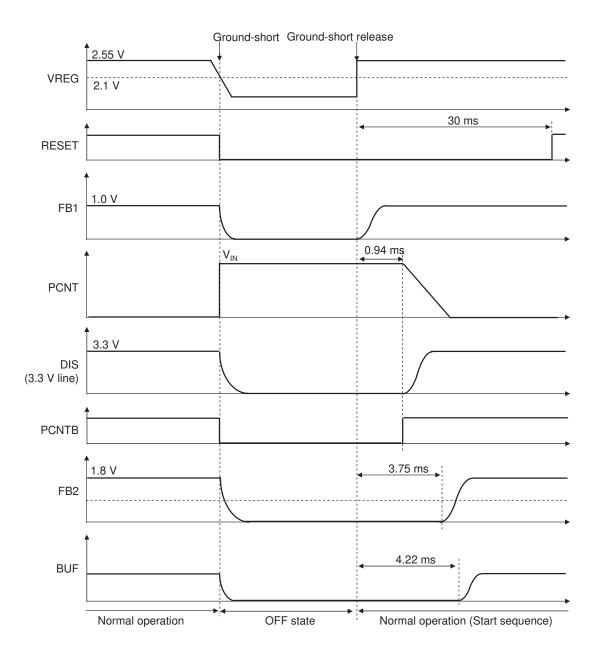

#### 3. Protection

Note) The characteristics listed below are reference values derived from the design of the IC and are not guaranteed.

VREG pin Ground Short Operation

VREG pin is an output pin of LDO used in internal circuits. The operation of each function stops just after VREG pin Is shorted to GND. Since each function is not latched unlike the case of [3.Protection : Protection sequence], it recovers by the release of ground-short. The operation is as follows.

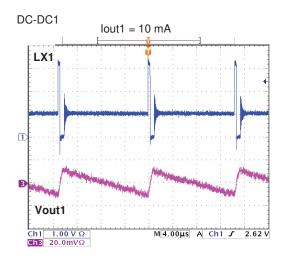

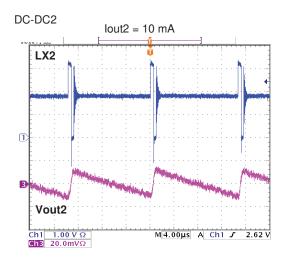

## **TYPICAL CHARACTERISTICS CURVES**

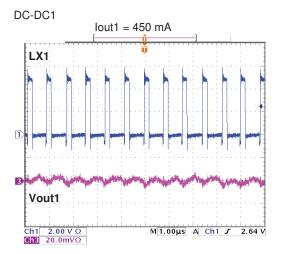

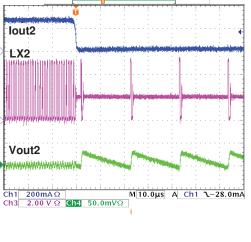

#### (1) Output ripple voltage

$VIN = 3.3 \text{ V}, \text{ Cout} = 10 \ \mu\text{F} (\text{ GRM21BB31A106K[Murata]}), \text{ Lout} = 2.2 \ \mu\text{H} (\text{ NR3012T2R2M[Taiyo Yuden]})$

## TYPICAL CHARACTERISTICS CURVES (Continued)

#### (1) Output ripple voltage

$VIN = 5.0 \text{ V}, \text{ Cout} = 10 \ \mu\text{F} (\text{ GRM21BB31A106K[Murata]}), \text{ L} = 2.2 \ \mu\text{H} (\text{ NR3012T2R2M[Taiyo Yuden]})$

## TYPICAL CHARACTERISTICS CURVES (Continued)

(2) Load transient response

LX1

nnnnnnn Vout1

Ch1

200mA Ω

Ch3

2.00 V Ω

Ch4

20.0mVΩ

A

M 4.00µs **11** 30.40 % Ch1 1-60.0mA

DWWWWW

3

VIN = 3.3 V , Cout = 10 µF ( GRM21BB31A106K[Murata] ) , Lout = 2.2 µH ( NR3012T2R2M[Taiyo Yuden] )

## TYPICAL CHARACTERISTICS CURVES (Continued)

#### (2) Load transient response

LX1

Vout1

DWWWW

3

VIN = 5.0 V, Cout = 10 µF (GRM21BB31A106K[Murata]), Lout = 2.2 µH (NR3012T2R2M[Taiyo Yuden])

## TYPICAL CHARACTERISTICS CURVES (Continued)

#### (3) Efficiency

VIN = 3.3 V or 5.0V, Cout = 10 µF (GRM21BB31A106K[Murata]), Lout = 2.2 µH (NR3012T2R2M[Taiyo Yuden])

DC-DC1

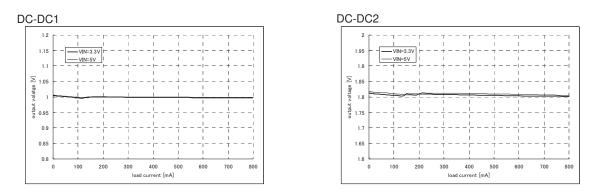

#### (4) Load regulation

VIN = 3.3 V or 5.0V, Cou t= 10 µF (GRM21BB31A106K[Murata]), Lout = 2.2 µH (NR3012T2R2M[Taiyo Yuden])

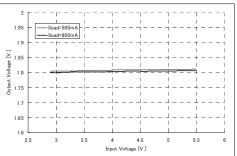

#### (5) Line regulation

#### Cout = 10 $\mu$ F (GRM21BB31A106K[Murata]), Lout = 2.2 $\mu$ H (NR3012T2R2M[Taiyo Yuden])

DC-DC1

| 0.9                    | <br>- L -<br>I         | !<br> <br> | !<br>!    |           | +<br>+      | <br>        |

|------------------------|------------------------|------------|-----------|-----------|-------------|-------------|

| 한 0.95<br>0.9          | <br>-  <br> <br>-      | <br> <br>  | <br> <br> | <br> <br> | +<br> <br>+ | I<br> <br>I |

| 0.95 [V] 1.05 [V] 0.95 | <br>                   |            |           |           | <br>        |             |

| 1.1<br>2 1.05          | <br><br> <br>          | i          | i         |           | <br>+<br>+  | i<br>i      |

| 1.2<br>1.15            | Iload=450<br>Iload=800 |            |           |           | <br>+       | 1           |

#### DC-DC2

## AN30185A

### **APPLICATIONS INFORMATION**

1. Application circuit

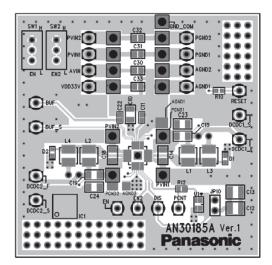

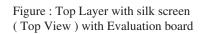

#### 2. Layout of Evaluation Board

Figure : Bottom Layer with silk screen (Bottom View )with Evaluation board

Notes) This application circuit and layout is an example. The operation of mass production set is not guaranteed. You should perform enough evaluation and verification on the design of mass production set. You are fully responsible for the incorporation of the above application circuit and information in the design of your equipment.

## **APPLICATIONS INFORMATION** (Continued)

#### 3. Recommended Component

| Reference Designator | QTY | Value  | Manufacturer | Part Number        |

|----------------------|-----|--------|--------------|--------------------|

| C-PVIN1              | 1   | 4.7 μF | Murata       | GRM21BB31A475KA74L |

| C-PVIN2              | 1   | 4.7 μF | Murata       | GRM21BB31A475KA74L |

| CAVIN                | 1   | 4.7 μF | Murata       | GRM21BB31A475KA74L |

| C-VREG               | 1   | 1 μF   | Murata       | GRM155B31A105KE15D |

| C-BUF                | 1   | 1 μF   | Murata       | GRM155B31A105KE15D |

| C-VOUT1              | 1   | 10 μF  | Murata       | GRM21BB31A106KE18L |

| C-VOUT2              | 1   | 10 μF  | Murata       | GRM21BB31A106KE18L |

| L-OUT1               | 1   | 2.2 μH | TAIYO YUDEN  | NR3012T2R2M        |

| L-OUT2               | 1   | 2.2 μΗ | TAIYO YUDEN  | NR3012T2R2M        |

| U1                   | 1   | —      | Panasonic    | MTM76111           |

| R-RST                | 1   | 10 KΩ  | Panasonic    | ERA3ARW103V        |

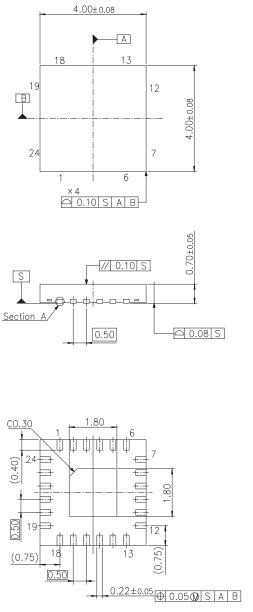

## PACKAGE INFORMATION (Reference Data)

## Package Code : HQFN024-P-0404

0.12 to 0.18

Section A(Reference value)

0.17 to 0.27

0.00 to 0.05

| Body Material                   | Br / Sb Free<br>Epoxy Resin |

|---------------------------------|-----------------------------|

| Lead Material                   | : Cu Alloy                  |

| Lead Finish Method : Au Plating |                             |