Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

Communications

#### Edition 2005-12-15

Published by Infineon Technologies AG, St.-Martin-Strasse 53, 81669 München, Germany

© Infineon Technologies AG 2005.

All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as a guarantee of characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

### AN983B/BX, PCI/Mini PCI-to-Ethernet LAN; PQFP - 128Pin

Revision History: 2005-12-15, Rev. 1.81

| Previous Version: |                                                                                  |  |  |  |  |  |  |  |  |

|-------------------|----------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Page/Date         | Subjects (major changes since last revision)                                     |  |  |  |  |  |  |  |  |

| 2000-10           | Rev.0.1: Draft data sheet for review                                             |  |  |  |  |  |  |  |  |

| 2001-02           | Rev.1.0: First release                                                           |  |  |  |  |  |  |  |  |

| 2001-03           | Rev.1.1: Add CSR15.bit28 MRXCK, Add CSR18.bit26 PMEP, Add CSR18.bit27 PMEPEN     |  |  |  |  |  |  |  |  |

| 2001-09           | Rev.1.2: Add 25MHz crystal accuracy, Revise PHY registers                        |  |  |  |  |  |  |  |  |

| 2001-09           | Rev.1.3: Revise product logo of Pin assignment diagram                           |  |  |  |  |  |  |  |  |

| Page17,14/        | Rev.1.4:                                                                         |  |  |  |  |  |  |  |  |

| 2001-09           | 1.MrxD0~D3P.23 CIOSA: 1 means enable; 0 means disable                            |  |  |  |  |  |  |  |  |

|                   | 2.P.14 Add LED info to pin diagram                                               |  |  |  |  |  |  |  |  |

| Page25,40/        | Rev.1.5:                                                                         |  |  |  |  |  |  |  |  |

| 2002-07           | 1.Offset 80h, DID default value; 0981h                                           |  |  |  |  |  |  |  |  |

|                   | 2.CSR18[25]/PWRS_clr; 1 means PCI_reset rising will clear CR49[1:0]/PWRS         |  |  |  |  |  |  |  |  |

| Page85/           | Rev.1.6: FIG21, FIG22, FIG23, FIG24 added for MII interface signal timing        |  |  |  |  |  |  |  |  |

| 2002-07           |                                                                                  |  |  |  |  |  |  |  |  |

| Page45/           | Rev.1.7(B): Unicast registers added, BGA package                                 |  |  |  |  |  |  |  |  |

| 2002-09           |                                                                                  |  |  |  |  |  |  |  |  |

| Page69/           | Rev.1.8(B): Modify some error statement about Loop-back Operation of transceiver |  |  |  |  |  |  |  |  |

| 2003-05           |                                                                                  |  |  |  |  |  |  |  |  |

| 2005-09-13        | Rev.1.81: when changed to the new Infineon format                                |  |  |  |  |  |  |  |  |

| 2005-11-30        | Minor change. Included Green package information                                 |  |  |  |  |  |  |  |  |

#### **Trademarks**

ABM®, ACE®, AOP®, ARCOFI®, ASM®, ASP®, DigiTape®, DuSLIC®, EPIC®, ELIC®, FALC®, GEMINAX®, IDEC®, INCA®, IOM®, IPAT®-2, ISAC®, ITAC®, IWE®, IWORX®, MUSAC®, MuSLIC®, OCTAT®, OptiPort®, POTSWIRE®, QUAT®, QuadFALC®, SCOUT®, SICAT®, SICOFI®, SIDEC®, SLICOFI®, SMINT®, SOCRATES®, VINETIC®, 10BaseV®, 10BaseVX® are registered trademarks of Infineon Technologies AG. 10BaseS™, EasyPort™, VDSLite™ are trademarks of Infineon Technologies AG. Microsoft® is a registered trademark of Microsoft Corporation, Linux® of Linus Torvalds, Visio® of Visio Corporation, and FrameMaker® of Adobe Systems Incorporated.

| 1              | General Description                               | 8    |

|----------------|---------------------------------------------------|------|

| 2              | System Block Diagram                              | 8    |

| 3              | Features                                          | 8    |

| 4              | Block Diagram                                     | . 10 |

| 5              | Pin Assignment Diagram                            | . 11 |

| 5.1            | Pin Type and Buffer Type Abbreviations            |      |

| 6              | Pin Description                                   | . 13 |

| 7              | Functional Descriptions                           | . 19 |

| 7.1            | Initialization Flow                               |      |

| 7.2<br>7.2.1   | Network Packet Buffer Management                  |      |

| 7.2.1<br>7.2.2 | Descriptor Structure Types                        |      |

| 7.3            | Transmit Scheme and Transmit Early Interrupt      |      |

| 7.3.1          | Transmit Flow                                     | . 23 |

| 7.3.2          | Transmit Pre-fetch Data Flow                      |      |

| 7.3.3          | Transmit Early interrupt Scheme                   |      |

| 7.4<br>7.5     | Receive Scheme and Receive Early Interrupt Scheme |      |

| 7.5.1          | MAC Operation                                     |      |

| 7.5.2          | Transceiver Operation                             |      |

| 7.5.3          | Flow Control in Full Duplex Application           |      |

| 7.6            | LED Display Operation                             |      |

| 7.6.1<br>7.6.2 | First Mode – 3 LED Displays                       |      |

| 7.0.2<br>7.7   | Second Mode – 4 LED Displays                      |      |

| 7.7.1          | Reset Whole Chip                                  |      |

| 7.7.2          | Reset Transceiver Only                            |      |

| 7.8            | Wake on LAN Function                              |      |

| 7.8.1          | The Magic Packet Format                           |      |

| 7.8.2<br>7.9   | The Wake on LAN Operation                         |      |

| 7.9.1          | Power States                                      |      |

| 8              | General EEPROM Format Description                 |      |

| 9              | Registers and Descriptors Description             |      |

| 9.1            | AN983B/BX Configuration Registers                 |      |

| 9.1.1          | AN983B/BX Configuration Registers Descriptions    | . 39 |

| 9.2            | PCI Control/Status Registers                      |      |

| 9.2.1          | PCI Control/Status Registers Description          |      |

| 9.3<br>9.3.1   | PHY Registers(Accessed by CSR9 MDI/MMC/MDO/MDC)   |      |

| 9.4            | Descriptors and Buffer Management                 |      |

| 9.4.1          | Receive Descriptor Descriptions                   |      |

| 9.4.2          | Transmit Descriptor Descriptions                  | . 99 |

| 10             | Electrical Specifications and Timings             |      |

| 10.1           | Absolute Maximum Ratings                          |      |

| 10.2           | DC Specifications                                 |      |

| 10.3<br>10.4   | AC Specifications                                 |      |

|                |                                                   |      |

| 11             | Package Outlines                                  | 111  |

# AN983B/BX

## **Table of Contents**

| 12   | Layout Guide (Rev. 1.0B)    | 113 |

|------|-----------------------------|-----|

| 12.1 | Placement                   | 113 |

| 12.2 | Trace Routing               | 113 |

| 12.3 | $V_{	t CC}$ and GND $\dots$ | 114 |

Data Sheet 5 Rev. 1.81, 2005-12-15

# AN983B/BX

# List of Figures

| Figure 1  | System Diagram of the AN983B/BX                                      | 8    |

|-----------|----------------------------------------------------------------------|------|

| Figure 2  | Block Diagram of the AN983B/BX                                       | . 10 |

| Figure 3  | Pin Assignment (top view)                                            | . 11 |

| Figure 4  | Initialization Flow                                                  | . 19 |

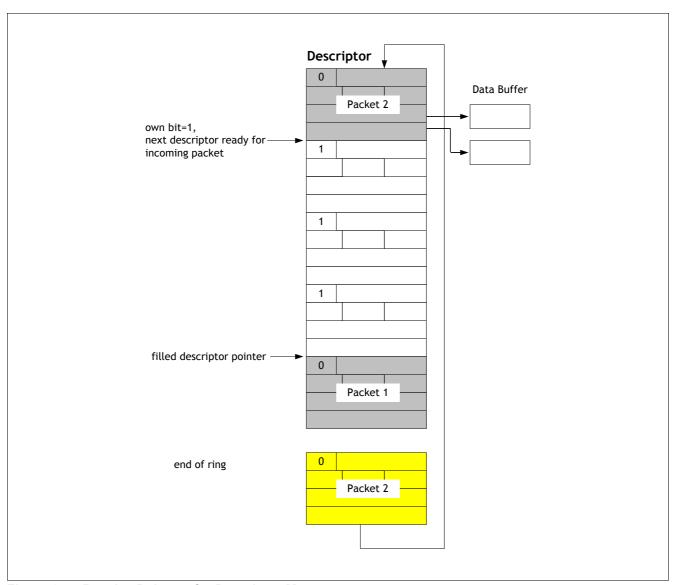

| Figure 5  | Ring Structure of Frame Buffer                                       | . 20 |

| Figure 6  | Chain Structure of Frame Buffer                                      | . 20 |

| Figure 7  | Transmit Pointers for Descriptor Management                          | . 21 |

| Figure 8  | Receive Pointers for Descriptor Management                           | . 22 |

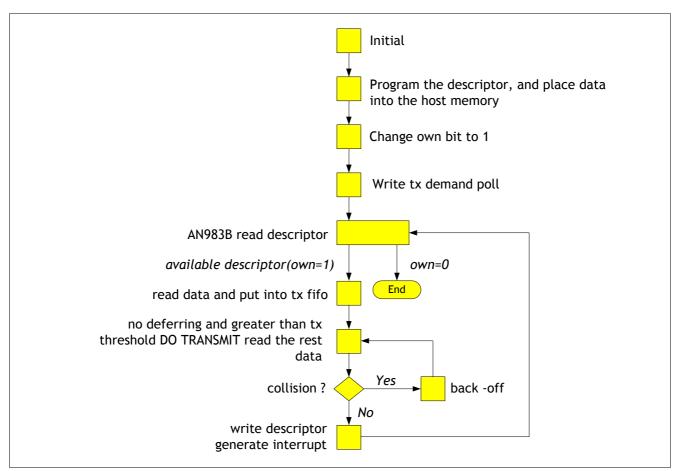

| Figure 9  | Transmit Flow                                                        |      |

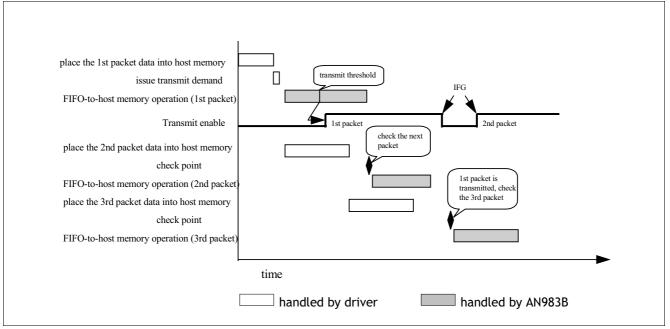

| Figure 10 | Transmit Data Flow of Pre-fetch Data                                 | . 24 |

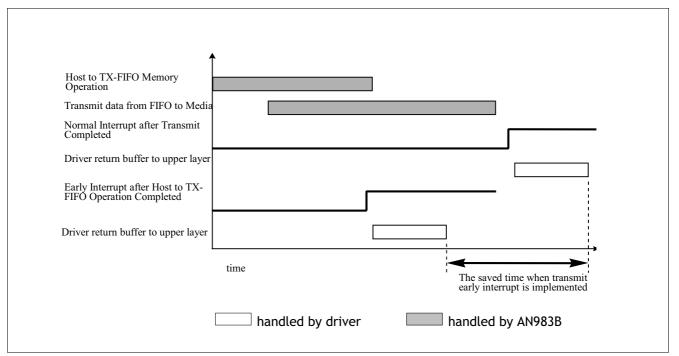

| Figure 11 | Transmit Normal Interrupt and Early Interrupt Comparison             | . 24 |

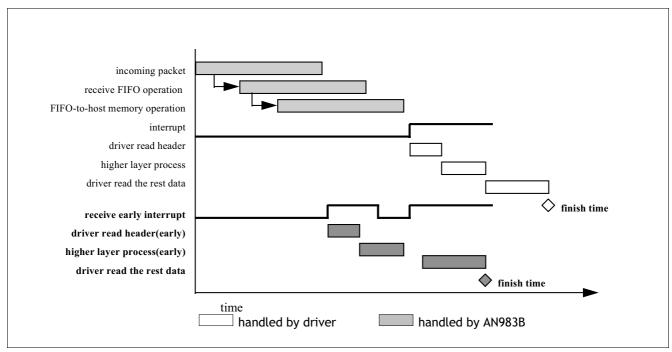

| Figure 12 | Receive Data Flow (without early interrupt and with early interrupt) | . 25 |

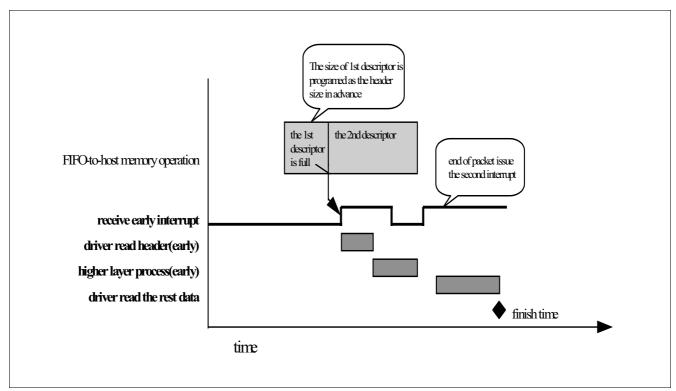

| Figure 13 | Detailed Receive Early Interrupt Flow                                | . 25 |

| Figure 14 | MAC Control Frame Format                                             |      |

| Figure 15 | PAUSE Operation Receive State Diagram                                |      |

| Figure 16 | PCI Clock Waveform                                                   | 104  |

| Figure 17 | PCI Timings                                                          | 105  |

| Figure 18 | Flash Write Timings                                                  |      |

| Figure 19 | Flash Read Timings                                                   | 107  |

| Figure 20 | Serial EEPROM Timing                                                 | 108  |

| Figure 21 | Transmit Signal Timing Relationships at the MII                      |      |

| Figure 22 | Receive Signal Timing Relations at the MII                           |      |

| Figure 23 | MDIO Sourced by STA                                                  |      |

| Figure 24 | MDIO Sourced by PHY                                                  |      |

| Figure 25 | Package outline for the AN983B / AN983BL                             | 111  |

| Figure 26 | Ground Via Trace Arrangement                                         |      |

| Figure 27 | Power Trace Arrangement                                              |      |

| Figure 28 | Ground Plane Arrangement                                             | 115  |

|           |                                                                      |      |

# AN983B/BX

## **List of Tables**

| Table 1  | Abbreviations for Pin Type                             | 12  |

|----------|--------------------------------------------------------|-----|

| Table 2  | Abbreviations for Buffer Type                          | 12  |

| Table 3  | Pin Definitions and Functions                          | 13  |

| Table 4  | Format                                                 | 26  |

| Table 5  | Power State                                            | 33  |

| Table 6  | Connection Type Definition                             | 35  |

| Table 7  | Registers Address Space                                | 38  |

| Table 8  | Registers Overview                                     | 38  |

| Table 9  | Registers Access ConditionsRegisters Access Conditions | 38  |

| Table 10 | Registers Access Types                                 | 38  |

| Table 11 | Registers Clock Domains                                | 39  |

| Table 12 | Registers Address Space                                | 51  |

| Table 13 | Registers Overview                                     |     |

| Table 14 | Registers Access Types                                 | 52  |

| Table 15 | Registers Address Space                                | 85  |

| Table 16 | Registers Overview                                     | 85  |

| Table 17 | Registers Access Types                                 | 85  |

| Table 18 | Registers Overview                                     | 94  |

| Table 19 | Registers Access Types                                 | 94  |

| Table 20 | Receive Descriptor Table                               | 95  |

| Table 21 | Transmit Descriptor Table                              | 99  |

| Table 22 | Min-Max Ratings                                        | 102 |

| Table 23 | General DC Specifications                              | 102 |

| Table 24 | PCI Interface DC Specifications                        | 102 |

| Table 25 | Flash/EEPROM Interface DC Specifications               | 103 |

| Table 26 | PCI Signaling AC Specifications for 3.3 V              | 103 |

| Table 27 | PCI Clock Specifications                               | 103 |

| Table 28 | PCI Timings                                            | 104 |

| Table 29 | Flash Interface Timings                                | 105 |

| Table 30 | EEPROM Interface Timings (AC/AD)                       | 107 |

| Table 31 | Dimensions for 128 -pin PQFP Package (AN983B/X)        | 111 |

| Table 32 | Dimensions for 128 -pin LQFP Package (AN983BLX)        | 112 |

| Table 33 | Layout Guide Revision History                          |     |

|          | •                                                      |     |

**General Description**

# 1 General Description

The AN983B/BX is a high performance PCI Fast Ethernet controller with a integrated physical layer interface for 10BASE-T and 100BASE-TX applications. The AN983BX is the environmentally friendly "green" package version.

The AN983B/BX was designed with advanced CMOS technology to provide a glueless 32-bit bus master interface for PCI, boot ROM interface, and CSMA/CD protocol for Fast Ethernet, as well as the physical media interface for 100BASE-TX of IEEE802.3u and 10BASE-T of IEEE802.3. The auto-negotiation function is also supported for speed and duplex detections.

The AN983B/BX can be programmed as MAC-only controller. In this mode, it provides the standard MII interface to link to an external PHY. With this mode, it can be connected to the HomePNA PHY to support the HomePNA networking solution or Homeplug PHY (Power-line solution) to support Homeplug networking solution.

The AN983B/BX provides both half-duplex and full-duplex operations, as well as supports for full-duplex flow control.

It provides long FIFO buffers for transmission and reception, and an early interrupt mechanism to enhance performance.

The AN983B/BX also supports ACPI and PCI compliant power management functions and Magic Packet wakeup event.

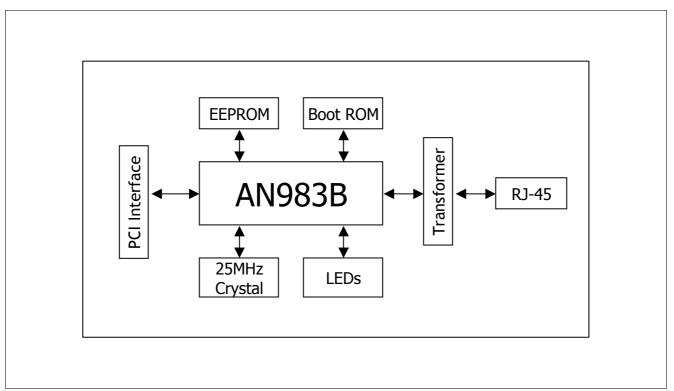

# 2 System Block Diagram

Figure 1 System Diagram of the AN983B/BX

### 3 Features

#### **Industry standard**

IEEE802.3u 100BASE-TX and IEEE802.3 10BASE-T compliant

**Features**

- Supports for IEEE802.3x flow control

- IEEE802.3u Auto-Negotiation support for 10BASE-T and 100BASE-TX

- · PCI Specification 2.2 compliant

- · ACPI and PCI power management Ver.1.1 compliant

- Supports PC99 wake on LAN

#### **FIFO**

- Provides two independent long FIFOs with 2k bytes each for transmission and receiving

- Pre-fetch up to two transmit packets to minimize inter frame gap (IFG) to 0.96 μs

- Retransmit collided packet without reload from host memory within 64 bytes

- Automatically retransmit FIFO under-run packet with maximum drain threshold until 3 times retry failure and that will not influence the registers and transmit threshold of next packet

### PCI I/F

- · Provides 32-bit PCI bus master data transfer

- Supports PCI clock with frequency from 0 Hz to 33 MHz

- Supports network operation with PCI system clock from 20 MHz to 33 MHz

- Provides performance meter, PCI bus master latency timer, for tuning the threshold to enhance the performance

- · Provides burst transmit packet interrupt and transmit/receive early interrupt to reduce host CPU utilization

- Supports memory-read, memory-read-line, memory-read-multiple, memory-write, memory-write-and-invalidate command while being bus master

- · Supports big or little endian byte ordering

#### EEPROM/Boot ROM I/F

- Provides write-able Flash ROM and EPROM as boot ROM with size up to 128 KB

- Provides PCI to access boot ROM by byte, word, or double word

- Re-write Flash boot ROM through I/O port by programming register

- Provides serial interface for read/write 93C46/66 EEPROM

- Automatically load device ID, vendor ID, subsystem ID, subsystem vendor ID, Maximum-Latency, and Minimum-Grand from the 64 byte contents of 93C46/66 after PCI reset de-asserted in PCI environment.

### **MAC/Physical**

- Integrates the whole Physical layer functions of 100BASE-TX and 10BASE-T

- Provides Full -duplex operation on both 100 Mbit/s and 10 Mbit/s modes

- Provides Auto-negotiation (NWAY) function of full/half duplex operation for both 10 and 100 Mbit/s

- · Provides transmit wave-shaper, receives filters, and adaptive equalizer

- Provides MLT-3 transceiver with DC restoration for Base-line wander compensation

- Provides MAC and Transceiver (TXCVR) loop-back modes for diagnostic

- Built in Stream Cipher Scrambler/ De-scrambler and 4B/5B encoder/decoder

- Supports external transmit transformer with turn ratio 1:1

- Supports external receive transformer with turn ratio 1:1

### **LED Display**

- 3 LED displays scheme provided:

- 100 Mbit/s (on) or Speed 10 (off)

- Link (keeps on when link ok) or Activity (will be blinking with 10 Hz when receiving or transmitting but not collision)

- FD (keeps on when in Full duplex mode) or Collision (will be blinking with 20 Hz when colliding)

- 4 LED displays scheme provided:

- 100 Mbit/s and Link (keep on when link and 100 Mbit/s)

- 10 Mbit/s and Link (keep on when link and 10 Mbit/s)

- Activity (will be blinking with 10 Hz when receiving or transmitting but not collision)

- FD (keeps on when in Full duplex mode) or Collision (will be blinking with 20 Hz when colliding)

Data Sheet 9 Rev. 1.81, 2005-12-15

**Block Diagram**

### Miscellaneous

- Provides 128-pin QFP/LQFP packages for PCI/mini-PCI interfaces

- 3.3 V power supply with 5 V/3.3 V I/O tolerance

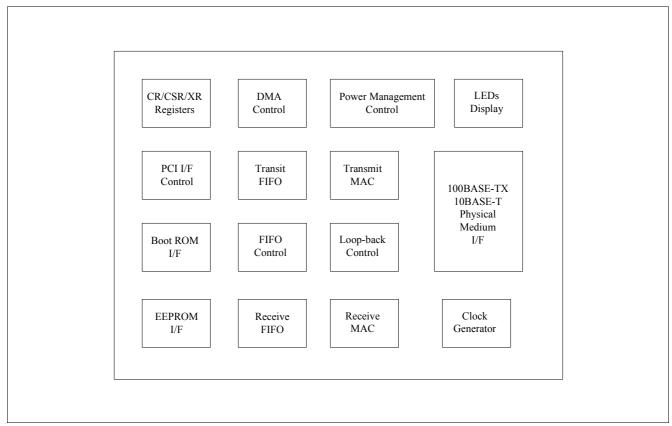

# 4 Block Diagram

Figure 2 Block Diagram of the AN983B/BX

Pin Assignment Diagram

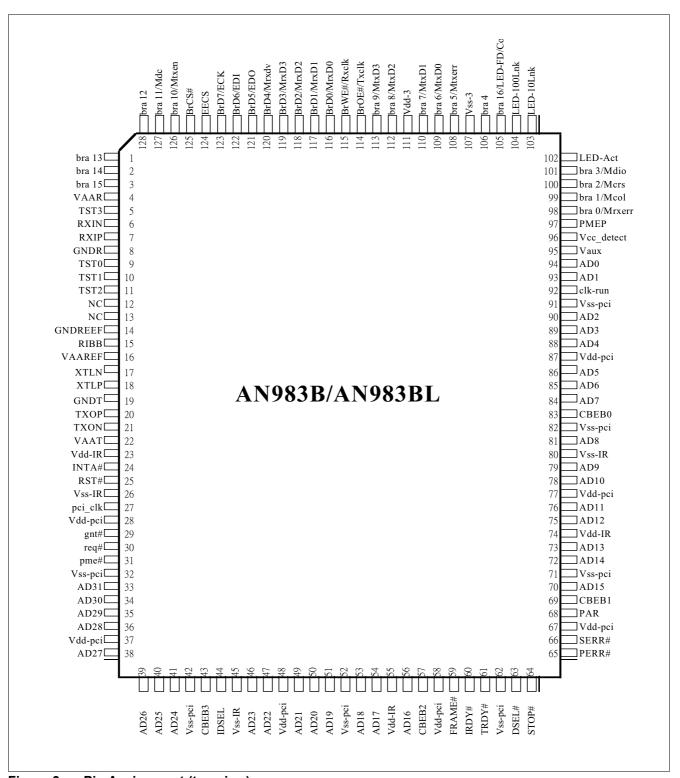

# 5 Pin Assignment Diagram

Figure 3 Pin Assignment (top view)

Pin Assignment Diagram

# 5.1 Pin Type and Buffer Type Abbreviations

Standardized abbreviations:

Table 1 Abbreviations for Pin Type

| Abbreviations | Description                                 |

|---------------|---------------------------------------------|

| I             | Standard input-only pin. Digital levels.    |

| 0             | Output. Digital levels.                     |

| I/O           | I/O is a bidirectional input/output signal. |

| Al            | Input. Analog levels.                       |

| AO            | Output. Analog levels.                      |

| AI/O          | Input or Output. Analog levels.             |

| PWR           | Power                                       |

| GND           | Ground                                      |

| MCL           | Must be connected to Low (JEDEC Standard)   |

| MCH           | Must be connected to High (JEDEC Standard)  |

| NU            | Not Usable (JEDEC Standard)                 |

| NC            | Not Connected (JEDEC Standard)              |

# Table 2 Abbreviations for Buffer Type

| Abbreviations | Description                                                                                                                                                                                                                                                                        |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Z             | High impedance                                                                                                                                                                                                                                                                     |

| PU1           | Pull up, 10 kΩ                                                                                                                                                                                                                                                                     |

| PD1           | Pull down, 10 kΩ                                                                                                                                                                                                                                                                   |

| PD2           | Pull down, 20 kΩ                                                                                                                                                                                                                                                                   |

| TS            | Tristate capability: The corresponding pin has 3 operational states: Low, high and high-impedance.                                                                                                                                                                                 |

| OD            | Open Drain. The corresponding pin has 2 operational states, active low and tristate, and allows multiple devices to share as a wire-OR. An external pull-up is required to sustain the inactive state until another agent drives it, and must be provided by the central resource. |

| OC            | Open Collector                                                                                                                                                                                                                                                                     |

| PP            | Push-Pull. The corresponding pin has 2 operational states: Active-low and active-high (identical to output with no type attribute).                                                                                                                                                |

| OD/PP         | Open-Drain or Push-Pull. The corresponding pin can be configured either as an output with the OD attribute or as an output with the PP attribute.                                                                                                                                  |

| ST            | Schmitt-Trigger characteristics                                                                                                                                                                                                                                                    |

| TTL           | TTL characteristics                                                                                                                                                                                                                                                                |

Table 3 Pin Definitions and Functions

| Pin or Ball  | Name    | Pin  | Buffer | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------|---------|------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No.          |         | Type | Type   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PCI Interfac | е       |      |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 24           | INTA#   | O/D  |        | PCI Interrupt Request AN983B/BX asserts this signal when one of the interrupt events occurs.                                                                                                                                                                                                                                                                                                                                                                                        |

| 25           | RST#    | I    |        | PCI Signal to Initialize the AN983B/BX The active reset signal should be sustained at least 100μs to guarantee that the AN983B/BX has completed the initializing activity. During the reset period, all the output pins of AN983B/BX will be set to tristate and all the O/D pins are floated.                                                                                                                                                                                      |

| 27           | PCI-CLK | I    |        | This PCI Clock Inputs to AN983B/BX for PCI Relative Circuits as the Synchronized Timing Base with PCI Bus The Bus signals are recognized on rising edge of PCI-CLK. In order to let network operating properly, the frequency range of PCI-CLK is limited between 20 MHz and 33 MHz when network operating.                                                                                                                                                                         |

| 29           | GNT#    | I    |        | PCI Bus Granted This signal indicates that the PCI bus request of AN983B/BX has been accepted.                                                                                                                                                                                                                                                                                                                                                                                      |

| 30           | REQ#    | 0    |        | PCI Bus Request Bus master device want to get bus access right                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 31           | PME#    | I/O  |        | Power Management Event The Power Management Event signal is an open drain, active low signal. When WOL-bit 18 of CSR 18 be set into "1", means that the AN983B/BX is set into Wake On LAN mode. In this mode, when the AN983B/BX receives a Magic Packet frame from network then the AN983B/BX will active this signal too.In the Wake On LAN mode, when LWS-bit (bit 17) of CSR18 is set into "1" means the LAN- WAKE signal is HP-style signal, otherwise it is IBM-style signal. |

Table 3

Pin Definitions and Functions (cont'd)

| Pin or Ball | Name      | Pin  | Buffer | Function                                                                                                                                       |

|-------------|-----------|------|--------|------------------------------------------------------------------------------------------------------------------------------------------------|

| No.         |           | Type | Туре   |                                                                                                                                                |

| 33, 34      | AD-31, 30 | I/O  |        | Multiplexed Address Data Pin of PCI Bus                                                                                                        |

| 35, 36      | AD-29, 28 |      |        |                                                                                                                                                |

| 38, 39      | AD-27, 26 |      |        |                                                                                                                                                |

| 40, 41      | AD-25, 24 |      |        |                                                                                                                                                |

| 46, 47      | AD-23, 22 |      |        |                                                                                                                                                |

| 49, 50      | AD-21, 20 |      |        |                                                                                                                                                |

| 51, 53      | AD-19, 18 |      |        |                                                                                                                                                |

| 54, 56      | AD-17, 16 |      |        |                                                                                                                                                |

| 70, 72      | AD-15, 14 |      |        |                                                                                                                                                |

| 73, 75      | AD-13, 12 |      |        |                                                                                                                                                |

| 76, 78      | AD-11, 10 |      |        |                                                                                                                                                |

| 79, 81      | AD-9, 8   |      |        |                                                                                                                                                |

| 84, 85      | AD-7, 6   |      |        |                                                                                                                                                |

| 86, 88      | AD-5, 4   |      |        |                                                                                                                                                |

| 89, 90      | AD-3, 2   |      |        |                                                                                                                                                |

| 93, 94      | AD-1, 0   |      |        |                                                                                                                                                |

| 43          | C-BEB3    | I/O  |        | Bus Command and Byte Enable                                                                                                                    |

| 57          | C-BEB2    |      |        |                                                                                                                                                |

| 69          | C-BEB1    |      |        |                                                                                                                                                |

| 83          | C-BEB0    |      |        |                                                                                                                                                |

| 44          | IDSEL     | I    |        | Initialization Device Select                                                                                                                   |

|             |           |      |        | This signal is asserted when host issues the configuration cycles to the AN983B/BX.                                                            |

| 59          | FRAME#    | I/O  |        | Begin and Duration of Bus Access Driven by master device                                                                                       |

| 60          | IRDY#     | I/O  |        | Master Device is Ready to Data Transaction                                                                                                     |

| 61          | TRDY#     | I/O  |        | Slave Device is Ready to Data Transaction                                                                                                      |

| 63          | DEVSEL#   | I/O  |        | Device Select  Device select, target is driving to indicate the address is decoded                                                             |

| 64          | STOP#     | I/O  |        | Stop the Current Transaction  Target device request the master device to stop the current transaction                                          |

| 65          | PERR#     | I/O  |        | Data Parity Error  Data parity error is detected, driven by the agent receiving data                                                           |

| 66          | SERR#     | O/D  |        | Address Parity Error                                                                                                                           |

| 68          | PAR       | I/O  |        | Parity Parity, even parity (AD [31:0] + C/BE [3:0]), master drives par for address and write data phase, target drives par for read data phase |

Table 3

Pin Definitions and Functions (cont'd)

| Pin or Ball   | Name                 | Pin          | Buffer   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------|----------------------|--------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No.           |                      | Туре         | Type     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 92            | Clk-run              | I/O          | OD       | Clock Run for PCI System In the normal operation situation, Host should assert this signal to indicate AN983B/BX about the normal situation. On the other hand, when Host will deassert this signal wher the clock is going down to a non-operating frequency. When AN983B/BX recognizes the deasserted status of clk run, then it will assert clk-run to request host to maintain the normal clock operation. When clk-run function is disabled then the AN983B/BX will set clk-run in tristate. |

|               | EEPROM Interfa       |              | _        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 98            | BrA0                 | I/O          |          | ROM Data Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 99            | BrA1                 |              |          | Provides up to 128KB EPROM or Flash-ROM application                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 100           | BrA2                 |              |          | space.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 101           | BrA3                 |              |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 106           | BrA4                 |              |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 108           | BrA5                 |              |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 109           | BrA6                 |              |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 110           | BrA7                 |              |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 112           | BrA8                 |              |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 113           | BrA9                 |              |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 126           | BrA10                |              |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 127           | BrA11                |              |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 128           | BrA12                |              |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1             | BrA13                |              |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2             | BrA14                |              |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3             | BrA15                |              |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 105           | BrA16                |              |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 116           | BrD0                 | Ю            |          | BootROM Data Bus Bit (0~7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 117           | BrD1                 |              |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 118           | BrD2                 |              |          | Input/Output data for AN983B/BX                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 119           | BrD3                 |              |          | EDO: Data Output of serial EEPROM EDI: Data Input of serial EEPROM                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 120           | BrD4                 |              |          | ECK: Clock input of serial EEPROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 121           | BrD5/EDO             | IO/O         |          | The AN983B/BX output clock signal to EEPROM.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 123           | BrD6/EDI<br>BrD7/ECK | IO/I<br>IO/I |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 124           | EECS                 | 0            |          | Chip Select of Serial EEPROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 125           | BrCS#                | 0            |          | BootROM Chip Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 114           | BrOE#                | 0            |          | BootROM Read Enable for Flash ROM Application                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 115           | BrWE#                | О            |          | BootROM Write Enable for Flash ROM Application                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| MII Interface | e (Program AN9       | 83B/BX as    | MAC-Only | Mode,Set FCH [2:0] =100B)                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 127           | Mdc                  | 0            |          | MII Management Data Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

Table 3

Pin Definitions and Functions (cont'd)

| Pin or Ball | Name     | Pin  | Buffer | Function                                                                                                                                |

|-------------|----------|------|--------|-----------------------------------------------------------------------------------------------------------------------------------------|

| No.         |          | Type | Туре   |                                                                                                                                         |

| 128         | Mtxen    | 0    |        | MII Transmit Enable                                                                                                                     |

| 109         | MtxD0    | 0    |        | MII Transmit Data                                                                                                                       |

| 110         | MtxD1    |      |        |                                                                                                                                         |

| 112         | MtxD2    |      |        |                                                                                                                                         |

| 113         | MtxD3    |      |        |                                                                                                                                         |

| 108         | Mtxerr   | 0    |        | MII Transmit Error                                                                                                                      |

| 101         | Mdio     | I/O  |        | MII Management Data I/O                                                                                                                 |

| 120         | Mrxdv    | I    |        | MII Receive Data Valid                                                                                                                  |

| 100         | Mcrs     | I    |        | MII Carrier Sense                                                                                                                       |

| 116         | MrxD0    | I    |        | MII Receive Data                                                                                                                        |

| 117         | MrxD1    |      |        |                                                                                                                                         |

| 118         | MrxD2    |      |        |                                                                                                                                         |

| 119         | MrxD3    |      |        |                                                                                                                                         |

| 99          | Mcol     | I    |        | MII Collision                                                                                                                           |

| 98          | Mrxerr   | I    |        | MII Receive Error                                                                                                                       |

| 115         | Rxclk    | I    |        | MII Receive Clock                                                                                                                       |

| 114         | Txclk    | I    |        | MII Transmit Clock                                                                                                                      |

| Physical In | nterface | l    |        |                                                                                                                                         |

| 18          | XTLP     | I    |        | Crystal Inputs                                                                                                                          |

| 17          | XTLN     |      |        | To be connected to a 25 MHz crystal with 50 ppm accuracy                                                                                |

| 6           | RXIN     | I    |        | Differentials Receive Inputs                                                                                                            |

| 7           | RXIP     |      |        | The differentials receive inputs of 100BASE-TX or 10BASE-T, these pins directly input from Magnetic.                                    |

| 20          | TXOP     | 0    |        | Differential Transmit Outputs                                                                                                           |

| 21          | TXON     |      |        | The differential Transmit outputs of 100BASE-TX or 10BASE-T, these pins directly output to Magnetic.                                    |

| 15          | RIBB     | I    |        | Reference Bias Resistor  To be tied to an external 10.0K (1%) resistor which should be connected to the analog ground at the other end. |

| 9           | TST0     | I    |        | Test Pin                                                                                                                                |

| 10          | TST1     |      |        |                                                                                                                                         |

| 11          | TST2     |      |        |                                                                                                                                         |

| 5           | TST3     |      |        |                                                                                                                                         |

| 12, 13      | NC       | 0    |        |                                                                                                                                         |

LED Display and Miscellaneous

Table 3

Pin Definitions and Functions (cont'd)

| Table 3            | Pin Definitions |             |                |                                                                                                                                                                                                                                                                                                     |

|--------------------|-----------------|-------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin or Ball<br>No. | Name            | Pin<br>Type | Buffer<br>Type | Function                                                                                                                                                                                                                                                                                            |

| 102                | Led-Act         | 0           |                | 4 LED Mode: LED Display for Activity Status This pin will be driven on with 10 Hz blinking frequency when either effective receiving or transmitting is detected.                                                                                                                                   |

|                    | (Led-Ink/act)   | O           |                | (3 LED Mode): LED Display for Link and Activity Status This pin will be driven on continually when a good Link test is detected. This pin will be driven on with 10 Hz blinking frequency when either effective receiving or transmitting is detected.                                              |

| 103                | Led-10Lnk       | О           |                | 4 LED Mode: LED Display for 10 Mbit/s Speed This pin will be driven on continually when the 10 Mbit/s network operating speed is detected.                                                                                                                                                          |

|                    | (Led-fd/col)    | O           |                | (3 LED Mode): LED Display for Full Duplex or Collision Status  This pin will be driven on continually when a full duplex configuration is detected. This pin will be driven on with 20 Hz blinking frequency when a collision status is detected in the half duplex configuration.                  |

| 104                | Led-100Lnk      | 0           |                | 4 LED Mode: LED Display for 100 Mbit/s Speed This pin will be driven on continually when the 100 Mbit/s network operating speed is detected.                                                                                                                                                        |

|                    | (Led-speed)     | 0           |                | (3 LED Mode): LED Display for 100 Mbit/s or 10 Mbit/s speed This pin will be driven on continually when the 100M b/s network operating speed is detected.                                                                                                                                           |

| 105                | Led-Fd/Col      | 0           |                | 4 LED Mode: LED Display for Full Duplex or Collision Status This pin will be driven on continually when a full duplex configuration is detected. This pin will be driven on with 20 Hz blinking frequency when a collision status is detected in the half duplex configuration.  (3 LED Mode): none |

| 95                 | Vaux            | 1           |                | When this pin is asserted, it indicates an auxiliary power source is supported. ACPI purpose, for detecting the auxiliary power source. This pin should be or-wired connected to:  1) 3.3 V when 3.3 Vaux support, or 2) 5 V when 5 Vaux support from 3-way switch.                                 |

| 96                 | Vcc-detect      | I           |                | When this pin is asserted, it indicates PCI power source is supported. ACPI purpose, for detecting the main power is remained or not. This pin should be connected to PCI bus power source +5 V.                                                                                                    |

Table 3 Pin Definitions and Functions (cont'd)

| Pin or Ball<br>No.                                   | Name                                              | Pin<br>Type | Buffer<br>Type | Function                                                                                                                  |

|------------------------------------------------------|---------------------------------------------------|-------------|----------------|---------------------------------------------------------------------------------------------------------------------------|

| 97                                                   | PMEP                                              | 0           |                | This signal is used as the WOL pin. It provides a programmable positive or negative pulse with approximately 50 ms width. |

| Digital Power                                        | er Pins                                           | <u> </u>    |                |                                                                                                                           |

| 26, 32, 42,<br>45, 52, 62,<br>71, 80, 82,<br>91, 107 |                                                   |             |                |                                                                                                                           |

| 23, 28, 37,<br>48, 55, 58,<br>67, 74, 77,<br>87, 111 | aa po. aa                                         |             |                | Connect to 3.3 V                                                                                                          |

| <b>Analog Pow</b>                                    | er Pins                                           | <u> </u>    |                |                                                                                                                           |

| 4, 16, 22                                            | $V_{ m AAR},V_{ m AAREF},\ V_{ m AAT},3.3~{ m V}$ |             |                |                                                                                                                           |

| 8, 14, 19                                            | GNDR,<br>GNDREF,<br>GNDT                          |             |                |                                                                                                                           |

# 7 Functional Descriptions

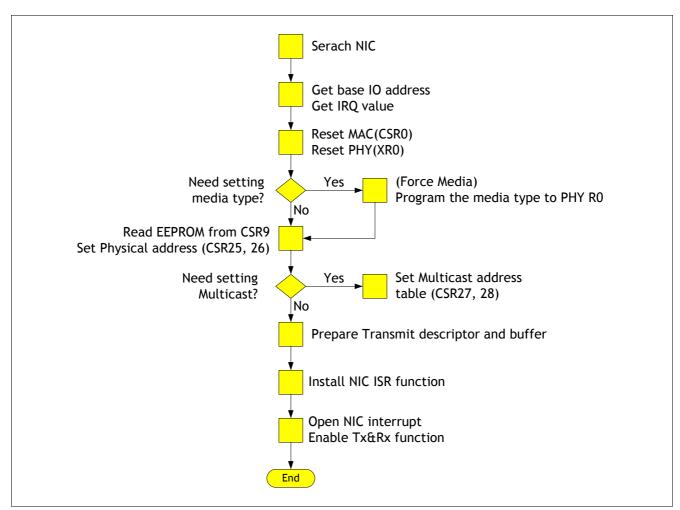

### 7.1 Initialization Flow

The flow of initialize AN983B/BX is shown as below.

Figure 4 Initialization Flow

## 7.2 Network Packet Buffer Management

# 7.2.1 Descriptor Structure Types

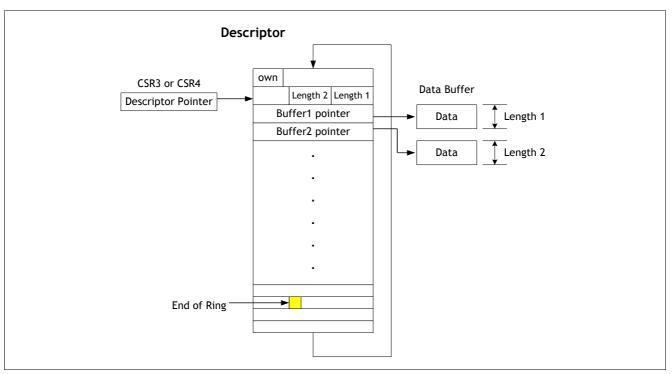

For networking operations the AN983B/BX transmits the data packet from transmit buffers in host memory to AN983B/BX's transmit FIFO and receives the data packet from AN983B/BX's receiving FIFO to receive buffers in host memory. The descriptors that the AN983B/BX supports to build in host memory are used as the pointers of these transmit and receive buffers.

There are two structure types for the descriptor, **Ring and Chain**, supported by the AN983B/BX and are shown as below. The type selection is controlled by the bit24 of RDES1 and the bit24 of TDES1.

The transmitting and receiving buffers are physically built in host memory. Any buffer can contain either a whole packet or just parts of a packet. But it can't contain more than one packet.

### · Ring structure

There are two buffers per descriptor in the ring structure. Support receives early interrupt.

Figure 5 Ring Structure of Frame Buffer

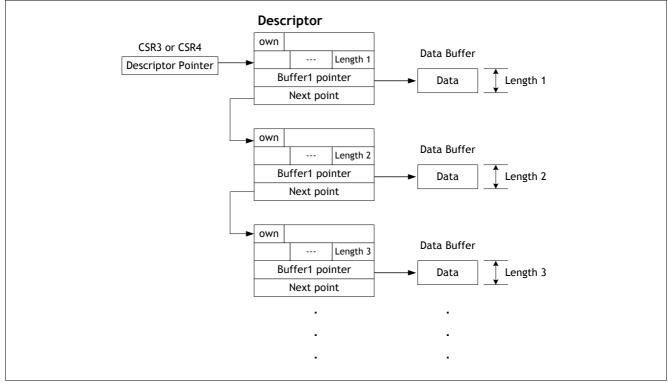

· Chain structure

There is only one buffer per descriptor in chain structure.

Figure 6 Chain Structure of Frame Buffer

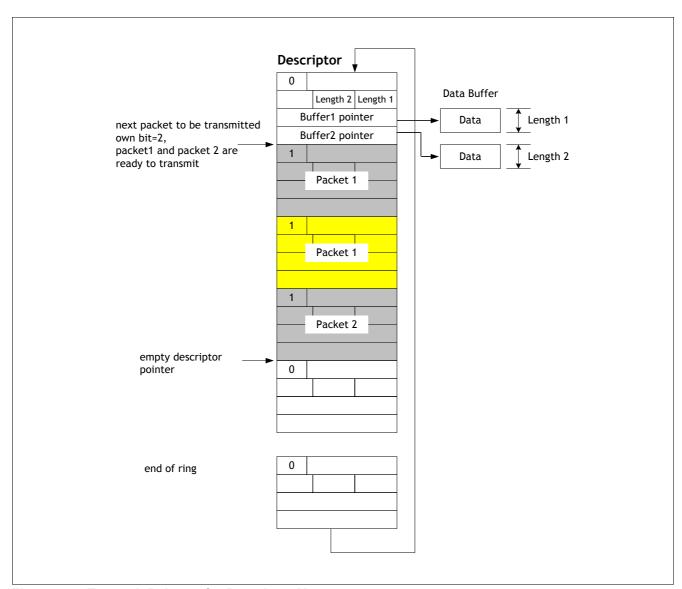

# 7.2.2 The Point of Descriptor Management

OWN bit = 1, ready for network side access

OWN bit = 0, ready for host side access

· Transmit Descriptor Pointers

Figure 7 Transmit Pointers for Descriptor Management

Receive Descriptor Pointers

Figure 8 Receive Pointers for Descriptor Management

# 7.3 Transmit Scheme and Transmit Early Interrupt

### 7.3.1 Transmit Flow

The flow of packet transmit is shown as below.

Figure 9 Transmit Flow

### 7.3.2 Transmit Pre-fetch Data Flow

- Transmit FIFO size = 2K-byte

- · Two packets in the FIFO at the same time

- · Meet the transmit min. back-to-back

Figure 10 Transmit Data Flow of Pre-fetch Data

# 7.3.3 Transmit Early interrupt Scheme

Figure 11 Transmit Normal Interrupt and Early Interrupt Comparison

## 7.4 Receive Scheme and Receive Early Interrupt Scheme

The following figure shows the difference of timing without early interrupt and with early interrupt.

Figure 12 Receive Data Flow (without early interrupt and with early interrupt)

Figure 13 Detailed Receive Early Interrupt Flow

## 7.5 Network Operation