Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Compact Flash III series AP-CFxxxxE3NR-XXXXXXQ

# **RoHS Compliant**

# **Compact Flash Series** II

Industrial CF Specifications

September 10<sup>th</sup>, 2014

Version 1.5

#### Apacer Technology Inc.

1F, No.32, Zhongcheng Rd., Tucheng Dist., New Taipei City, Taiwan, R.O.C Tel: +886-2-2267-8000 Fax: +886-2-2267-2261 www.apacer.com

#### AP-CFxxxxE3NR-XXXXXQ

### **Features:**

- Compact Flash Association

Specification Revision 3.0 Standard

Interface

- ATA command set compatible

- ATA mode support for up to:

PIO Mode-6

Multiword DMA Mode-4

Ultra DMA Mode-4

- Connector Type

- 50 pins female

- Power consumption (typical)\*

- Supply voltage: 3.3V & 5V

- Active mode: 80 mA/95 mA (3.3V/5.0V)

- Sleep mode: 700 μA/900 μA (3.3V/5.0V)

- Performance<sup>\*</sup>

- Sustained read: up to 29 MB/sec

- Sustained write: up to 15 MB/sec

- Capacity

- 128, 256, 512 MB 1, 2, 4, 8, 16 GB

- NAND Flash Type: SLC

- Shock & Vibration\*\*

- Shock: 1,500 GVibration: 15 G

- Temperature ranges

- Operating:

Standard: 0 ℃ to 70 ℃ Extended: -40 ℃ to 85 ℃

- Storage: -40 °C to 100 °C

- Flash management

- Advanced wear-leveling algorithms

- S.M.A.R.T. technology

- Built-in hardware ECC

- Flash block management

- Power failure management

- Endurance (TBW: Terabytes Written)

- 128 MB: 3.3 TBW

- 256 MB: 6.7 TBW

- 512 MB: 12.9 TBW

- 1 GB: 25.6 TBW

- 2 GB: 38.4 TBW

- 4 GB: 51.9 TBW

- 8 GB: 69.8 TBW

- 16 GB: 115.0 TBW

- Physical Dimensions

- 36.4mm x 42.8mm x 3.3mm

- RoHS compliant

<sup>\*</sup>Varies from capacities. The values addressed for Performance and Power consumptions are typical and may vary depending on settings and platforms.

<sup>\*\*</sup>Non-operating

# Compact Flash Ⅲ series AP-CFxxxxE3NR-XXXXXXQ

## **Table of Contents**

| 1. GENERAL DESCRIPTION                                              | 3  |

|---------------------------------------------------------------------|----|

| 2. FUNCTIONAL BLOCK                                                 | 3  |

| 3. PIN ASSIGNMENTS                                                  | 4  |

| 4. PRODUCT SPECIFICATIONS                                           | 6  |

| 4.1 CAPACITY                                                        |    |

| 4.2 PERFORMANCE SPECIFICATION                                       |    |

| 4.5 ENDURANCE                                                       |    |

| 5. FLASH MANAGEMENT                                                 | 8  |

| 5.1. ADVANCED WEAR-LEVELING ALGORITHMS                              | 8  |

| 5.2 S.M.A.R.T. TECHNOLOGY                                           |    |

| 5.3 BUILT-IN HARDWARE ECC                                           |    |

| 5.5 POWER FAILURE MANAGEMENT                                        |    |

| 6. SOFTWARE INTERFACE                                               |    |

| 6.1 COMMAND SET                                                     | 9  |

| 7. ELECTRICAL SPECIFICATION                                         | 11 |

| 7.1 DC CHARACTERISTICS                                              | 12 |

| 7.2 AC CHARACTERISTICS                                              |    |

| 7.2.1 Attribute Memory Read Timing Specification                    |    |

| 7.2.2 Configuration Register (Attribute Memory) Write Specification |    |

| 7.2.4 Common Memory Write Timing Specification                      |    |

| 7.2.5 I/O Input (Read) Timing Specification                         |    |

| 7.2.6 I/O Output (Write) Timing Specification                       |    |

| 7.2.7 True IDE I/O Read Timing                                      |    |

| 7.2.8 True IDE I/O Write Timing                                     |    |

| 7.2.9 Olira DMA Mode Data Transfer Input/Output (Reda/Write) Timing |    |

| 8. PHYSICAL CHARACTERISTICS                                         |    |

| 8.1 DIMENSION                                                       |    |

| 9. PRODUCT ORDERING INFORMATION                                     |    |

|                                                                     |    |

| 9.1 Product Code Designations                                       |    |

### 1. General Description

Apacer's value-added Industrial CompactFlash Card offers high performance, high reliability and power-efficient storage. Regarding standard compliance, this CompactFlash Card complies with CompactFlash specification revision 3.0, supporting transfer modes up to Programmed Input Output (PIO) Mode 6, Multiword Direct Memory Access (DMA) Mode 4, and Ultra DMA Mode 4.

Apacer's value-added CFC provides complete PCMCIA – ATA functionality and compatibility. Apacer 's CompactFlash technology is designed for applications in Point of Sale (POS) terminals, telecom, IP-STB, medical instruments, surveillance systems, industrial PCs and handheld applications.

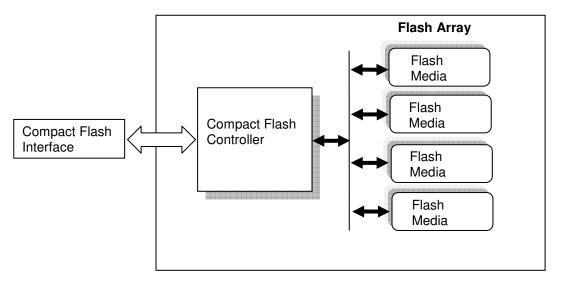

### 2. Functional Block

The Compact Flash Card (CFC) includes a controller and flash media, as well as the Compact Flash standard interface. Figure 2-1 shows the functional block diagram.

Figure 2-1: Functional block diagram

# **Compact Flash Ⅲ series AP-CFxxxxE3NR-XXXXXXQ**

# 3. Pin Assignments

Table 3-1 lists the pin assignments with respective signal names for the 50-pin configuration. A "#" suffix indicates the active low signal. The pin type can be input, output or input/output.

Table 3-1: Pin assignments (1 of 2)

| Pin No. | Memory            | card mode    | I/O car           | rd mode      | True ID                                       | True IDE mode |  |  |

|---------|-------------------|--------------|-------------------|--------------|-----------------------------------------------|---------------|--|--|

|         | Signal name       | Pin I/O type | Signal name       | Pin I/O type | Signal name                                   | Pin I/O type  |  |  |

| 1       | GND               | -            | GND               | -            | GND                                           | ı             |  |  |

| 2       | D3                | I/O          | D3                | I/O          | D3                                            | I/O           |  |  |

| 3       | D4                | I/O          | D4                | I/O          | D4                                            | I/O           |  |  |

| 4       | D5                | I/O          | D5                | I/O          | D5                                            | I/O           |  |  |

| 5       | D6                | I/O          | D6                | I/O          | D6                                            | I/O           |  |  |

| 6       | D7                | I/O          | D7                | I/O          | D7                                            | I/O           |  |  |

| 7       | -CE1              | I            | -CE1              | I            | -CS0                                          | I             |  |  |

| 8       | A10               | I            | A10               | I            | A10 <sup>2</sup>                              | I             |  |  |

| 9       | -OE               | I            | -OE               |              | -ATA SEL                                      |               |  |  |

| 10      | A9                | I            | A9                |              | A9 <sup>2</sup>                               |               |  |  |

| 11      | A8                | I            | A8                | I            | A8 <sup>2</sup>                               | I             |  |  |

| 12      | A7                | I            | A7                | I            | A7 <sup>2</sup>                               | I             |  |  |

| 13      | VCC               | -            | VCC               | -            | VCC                                           | -             |  |  |

| 14      | A6                | I            | A6                | I            | A6 <sup>2</sup>                               | I             |  |  |

| 15      | A5                | I            | A5                |              | A5 <sup>2</sup>                               |               |  |  |

| 16      | A4                | I            | A4                | I            | A4 <sup>2</sup>                               | I             |  |  |

| 17      | A3                | I            | A3                |              | A3 <sup>2</sup>                               |               |  |  |

| 18      | A2                | I            | A2                |              | A2                                            |               |  |  |

| 19      | A1                |              | A1                |              | A1                                            |               |  |  |

| 20      | A0                | I            | A0                |              | A0                                            |               |  |  |

| 21      | D0                | I/O          | D0                | I/O          | D0                                            | I/O           |  |  |

| 22      | D1                | I/O          | D1                | I/O          | D1                                            | I/O           |  |  |

| 23      | D2                | I/O          | D2                | I/O          | D2                                            | I/O           |  |  |

| 24      | WP                | 0            | -IOCS16           | 0            | -IOCS16                                       | 0             |  |  |

| 25      | -CD2              | 0            | -CD2              | 0            | -CD2                                          | 0             |  |  |

| 26      | -CD1              | 0            | -CD1              | 0            | -CD1                                          | 0             |  |  |

| 27      | D11 <sup>1</sup>  | I/O          | D11 <sup>1</sup>  | I/O          | D11 <sup>1</sup>                              | I/O           |  |  |

| 28      | D12 <sup>1</sup>  | I/O          | D12 <sup>1</sup>  | I/O          | D12 <sup>1</sup>                              | I/O           |  |  |

| 29      | D13 <sup>1</sup>  | I/O          | D13 <sup>1</sup>  | I/O          | D13 <sup>1</sup>                              | I/O           |  |  |

| 30      | D14 <sup>1</sup>  | I/O          | D14 <sup>1</sup>  | I/O          | D14 <sup>1</sup>                              | I/O           |  |  |

| 31      | D15 <sup>1</sup>  | I/O          | D15 <sup>1</sup>  | I/O          | D15 <sup>1</sup>                              | I/O           |  |  |

| 32      | -CE2 <sup>1</sup> | I            | -CE2 <sup>1</sup> | Ī            | -CS1 <sup>1</sup>                             | I             |  |  |

| 33      | -VS1              | Ö            | -VS1              | Ö            | -VS1                                          | Ö             |  |  |

| 34      | -IORD             | Ī            | -IORD             | i            | -IORD                                         | I             |  |  |

| -       |                   | ·            |                   |              | HSTROBE <sup>8</sup><br>-HDMARDY <sup>9</sup> |               |  |  |

| 35      | -IOWR             | I            | -IOWR             | I            | -IOWR <sup>7</sup><br>STOP <sup>8,9</sup>     | I             |  |  |

| 36      | -WE               | I            | -WE               | I            | -WE <sup>3</sup>                              | I             |  |  |

| 37      | READY             | 0            | -IREQ             | 0            | INTRQ                                         | 0             |  |  |

| 38      | VCC               | -            | VCC               | -            | VCC                                           | -             |  |  |

| 39      | -CSEL⁵            | I            | -CSEL⁵            | I            | -CSEL                                         | I             |  |  |

| 40      | -VS2              | 0            | -VS2              | 0            | -VS2                                          | 0             |  |  |

| 41      | RESET             | I            | RESET             | I            | -RESET                                        | I             |  |  |

#### AP-CFxxxxE3NR-XXXXXQ

Table 3-1: Pin assignments (2 of 2)

| Pin No. | Memory card mode |              | I/O card mode    |              | True IDE mode                                           |              |

|---------|------------------|--------------|------------------|--------------|---------------------------------------------------------|--------------|

|         | Signal name      | Pin I/O type | Signal name      | Pin I/O type | Signal name                                             | Pin I/O type |

| 42      | -WAIT            | 0            | -WAIT            | 0            | IORDY'<br>-DDMARDY <sup>8</sup><br>DSTROBE <sup>9</sup> | 0            |

| 43      | -INPACK          | 0            | -INPACK          | 0            | DMARQ                                                   | 0            |

| 44      | -REG             | I            | -REG             | I            | -DMACK <sup>6</sup>                                     | I            |

| 45      | BVD2             | 0            | -SPKR            | 0            | -DASP                                                   | I/O          |

| 46      | BVD1             | 0            | -STSCHG          | 0            | -PDIAG                                                  | I/O          |

| 47      | D8 <sup>1</sup>  | I/O          | D8 <sup>1</sup>  | I/O          | D8 <sup>1</sup>                                         | I/O          |

| 48      | D9 <sup>1</sup>  | I/O          | D9 <sup>1</sup>  | I/O          | D9 <sup>1</sup>                                         | I/O          |

| 49      | D10 <sup>1</sup> | I/O          | D10 <sup>1</sup> | I/O          | D10 <sup>1</sup>                                        | I/O          |

| 50      | GND              | -            | GND              | -            | GND                                                     | -            |

#### Notes:

- 1. These signals are required only for 16 bit accesses and not required when installed in 8 bit systems. Devices should allow for 3-state signals not to consume current.

- 2. The signals should be grounded by the host.

- 3. The signal should be tied to VCC by the host.

- 4. The mode is optional for CF+ cards, but required for CompactFlash storage cards

- 5. The -CSEL signal is ignored by the card in PC card modes. However, because it is not pulled up on the card in these modes, it should not be left floating by the host in PC card modes. In these modes, the pin should be connected by the host to PC card A25 or grounded by the host.

- 6. If DMA operations are not used, the signal should be held high or tied to VCC by the host. For proper operation in older hosts: while DMA operations are not active, the card shall ignore this signal, including a floating condition.

- 7. Signal usage in True IDE mode except when Ultra DMA mode protocol is active

- 8. Signal usage in True IDE mode when Ultra DMA mode protocol DMA write is active

- 9. Signal usage in True IDE mode when Ultra DMA mode protocol DMA read is active.

#### AP-CFxxxxE3NR-XXXXXQ

### 4. Product Specifications

#### 4.1 Capacity

Capacity specification of the Compact Flash Card series (CFC) is available as shown in Table 4-1. It lists the specific capacity and the default numbers of heads, sectors and cylinders for each product line.

Table 4-1: Capacity specifications

| Capacity | Total bytes <sup>1,2</sup> | Cylinders           | Heads | Sectors | Max LBA    |

|----------|----------------------------|---------------------|-------|---------|------------|

| 128 MB   | 128,450,560                | 980                 | 8     | 32      | 250,880    |

| 256 MB   | 256,901,120                | 980                 | 16    | 32      | 501,760    |

| 512 MB   | 512,483,328                | 993                 | 16    | 63      | 1,000,944  |

| 1GB      | 1,024,966,656              | 1,986               | 16    | 63      | 2,001,888  |

| 2GB      | 2,048,901,120              | 3,970               | 16    | 63      | 4,001,760  |

| 4GB      | 4,110,188,544              | 7,964               | 16    | 63      | 8,027,712  |

| 8GB      | 8,195,604,480              | 15,880              | 16    | 63      | 16,007,040 |

| 16GB     | 16,391,208,960             | 16,383 <sup>3</sup> | 16    | 63      | 32,014,080 |

Notes:

Display of total bytes varies from operating systems.

Cylinders, heads or sectors are not applicable for these capacities. Only LBA addressing applies

Notes: 1 GB = 1,000,000,000 bytes; 1 sector = 512 bytes.

LBA count addressed in the table above indicates total user storage capacity and will remain the same throughout the lifespan of the device. However, the total usable capacity of the SSD is most likely to be less than the total physical capacity because a small portion of the capacity is reserved for device maintenance usages.

### 4.2 Performance Specification

Performances of the CF cards are listed in Table 4-2

Table 4-2: Performance specifications

| Capacity Performance   | 128 MB | 256 MB | 512 MB | 1 GB | 2 GB | 4 GB | 8 GB | 16 GB |

|------------------------|--------|--------|--------|------|------|------|------|-------|

| Sustained read (MB/s)  | 17     | 29     | 19     | 21   | 20   | 21   | 21   | 20    |

| Sustained write (MB/s) | 4      | 8      | 7      | 12   | 11   | 11   | 13   | 15    |

Notes: performance may vary depending on flash configurations or host system settings.

#### AP-CFxxxxE3NR-XXXXXQ

### 4.3 Environmental Specifications

Environmental specification of the Compact Flash Card series (CFC) follows the MIL-STD-810F standards as shown in Table 4-3.

Table 4-3: Environmental specifications

| Environment               |           | Specification                                     |  |

|---------------------------|-----------|---------------------------------------------------|--|

| Taranavatura              | Operation | 0°C to 70°C; -40°C to 85°C (Extended Temperature) |  |

| Temperature               | Storage   | -40 ℃ to 100 ℃                                    |  |

| Humidity                  |           | 5% to 95% RH (Non-condensing)                     |  |

| Vibration (Non-Operation) |           | Sine wave : 10~2000Hz, 15G (X, Y, Z axes)         |  |

| , ,                       |           | Half sine wave 1,500G (X, Y, Z; All 6 axes)       |  |

### 4.4 Certification & Compliance

The CompactFlash card complies with the following global standards:

- CE

- FCC

- RoHS

#### 4.5 Endurance

The endurance of a storage device is predicted by TeraBytes Written based on several factors related to usage, such as the amount of data written into the drive, block management conditions, and daily workload for the drive. Thus, key factors, such as Write Amplifications and the number of P/E cycles, can influence the lifespan of the drive.

| Capacity | TeraBytes Written |

|----------|-------------------|

| 128 MB   | 3.3               |

| 256 MB   | 6.7               |

| 512 MB   | 12.9              |

| 1 GB     | 25.6              |

| 2 GB     | 38.4              |

| 4 GB     | 51.9              |

| 8 GB     | 69.8              |

| 16 GB    | 115.0             |

#### Notes:

- The measurement assumes the data written to the SSD for test is under a typical and constant rate.

- The measurement follows the standard metric: 1 TB (Terabyte) = 1000 GB.

# Compact Flash III series AP-CFxxxxE3NR-XXXXXQ

### 5. Flash Management

#### 5.1. Advanced wear-leveling algorithms

Flash memory devices differ from Hard Disk Drives (HDDs) in terms of how blocks are utilized. For HDDs, when a change is made to stored data, like erase or update, the controller mechanism on HDDs will perform overwrites on blocks. Unlike HDDs, flash blocks cannot be overwritten and each P/E cycle wears down the lifespan of blocks gradually. Repeatedly program/erase cycles performed on the same memory cells will eventually cause some blocks to age faster than others. This would bring flash storages to their end of service term sooner. Wear leveling is an important mechanism that level out the wearing of blocks so that the wearing-down of blocks can be almost evenly distributed. This will increase the lifespan of SSDs. Commonly used wear leveling types are Static and Dynamic.

#### 5.2 S.M.A.R.T. technology

S.M.A.R.T. is an acronym for Self-Monitoring, Analysis and Reporting Technology, an open standard allowing disk drives to automatically monitor their own health and report potential problems. It protects the user from unscheduled downtime by monitoring and storing critical drive performance and calibration parameters. Ideally, this should allow taking proactive actions to prevent impending drive failure. Apacer SMART feature adopts the standard SMART command B0h to read data from the drive. When the Apacer SMART Utility running on the host, it analyzes and reports the disk status to the host before the device is in critical condition.

#### 5.3 Built-in hardware ECC

The ATA-Disk Module uses BCH Error Detection Code (EDC) and Error Correction Code (ECC) algorithms which correct up to eight random single-bit errors for each 512-byte block of data. High performance is fulfilled through hardware-based error detection and correction.

### 5.4 Flash block management

Current production technology is unable to guarantee total reliability of NAND flash memory array. When a flash memory device leaves factory, it comes with a minimal number of initial bad blocks during production or out-of-factory as there is no currently known technology that produce flash chips free of bad blocks. In addition, bad blocks may develop during program/erase cycles. When host performs program/erase command on a block, bad block may appear in Status Register. Since bad blocks are inevitable, the solution is to keep them in control. Apacer flash devices are programmed with ECC, block mapping technique and S.M.A.R.T to reduce invalidity or error. Once bad blocks are detected, data in those blocks will be transferred to free blocks and error will be corrected by designated algorithms.

### 5.5 Power Failure Management

Power Failure Management plays a crucial role when experiencing unstable power supply. Power disruption may occur when users are storing data into the SSD. In this urgent situation, the controller would run multiple write-to-flash cycles to store the metadata for later block rebuilding. This urgent operation requires about several milliseconds to get it done. At the next power up, the firmware will perform a status tracking to retrieve the mapping table and resume previously programmed NAND blocks to check if there is any incompleteness of transmission.

# Compact Flash Ⅲ series AP-CFxxxxE3NR-XXXXXQ

## 6. Software Interface

#### 6.1 Command Set

Table 6-1 summarizes the command set with the paragraphs that follow describing the individual commands and the task file for each.

Table 6-1: Command set

| Command                      | Code       | FR <sup>1</sup> | SC <sup>2</sup> | SN <sup>3</sup> | CY <sup>4</sup> | DH⁵            | LBA <sup>6</sup> |

|------------------------------|------------|-----------------|-----------------|-----------------|-----------------|----------------|------------------|

| Check-Power-Mode             | E5h or 98h | -               | -               | -               | -               | D <sup>8</sup> | -                |

| Execute-Drive-Diagnostic     | 90h        | -               | -               | -               | -               | D              | -                |

| Erase Sector(s)              | C0h        | -               | Υ               | Υ               | Υ               | Υ              | Υ                |

| Flush-Cache                  | E7h        | -               | -               | -               | -               | D              | -                |

| Format Track                 | 50h        | -               | $Y^7$           | -               | Υ               | Y <sup>8</sup> | Υ                |

| Identify-Drive               | ECh        | -               | -               | -               | -               | D              | -                |

| Idle                         | E3h or 97h | -               | Υ               | -               | -               | D              | -                |

| Idle-Immediate               | E1h or 95h | -               | -               | -               | -               | D              | -                |

| Initialize-Drive-Parameters  | 91h        | -               | Υ               | -               | -               | Υ              | -                |

| NOP                          | 00h        | -               | -               | -               | -               | D              | -                |

| Read-Buffer                  | E4h        | -               | -               | -               | -               | D              | -                |

| Read-DMA                     | C8h or C9h | -               | Υ               | Υ               | Υ               | Υ              | Υ                |

| Read-Multiple                | C4h        | -               | Υ               | Υ               | Υ               | Υ              | Υ                |

| Read-Sector(s)               | 20h or 21h | -               | Υ               | Υ               | Υ               | Υ              | Υ                |

| Read-Verify-Sector(s)        | 40h or 41h | -               | Υ               | Υ               | Υ               | Υ              | Υ                |

| Recalibrate                  | 1Xh        | -               | -               | -               | -               | D              | -                |

| Request-Sense                | 03h        | -               | -               | -               | -               | D              | -                |

| Seek                         | 7Xh        | -               | -               | Υ               | Υ               | Υ              | Υ                |

| Set-Features                 | EFh        | Y <sup>7</sup>  | -               | -               | -               | D              | -                |

| SMART                        | B0h        | Υ               | Υ               | Υ               | Υ               | D              |                  |

| Set-Multiple-Mode            | C6h        | -               | Υ               | -               | -               | D              | -                |

| Set-Sleep-Mode               | E6h or 99h | -               | -               | -               | -               | D              | -                |

| Standby                      | E2h or 96h | -               | -               | -               | -               | D              | -                |

| Standby-Immediate            | E0h or 94h | -               | -               | -               | -               | D              | -                |

| Translate-Sector             | 87h        | -               | Υ               | Υ               | Υ               | Υ              | Υ                |

| Write-Buffer                 | E8h        | -               | -               | -               | -               | D              | -                |

| Write-DMA                    | CAh or CBh | -               | Υ               | Υ               | Υ               | Υ              | Υ                |

| Write-Multiple               | C5h        | -               | Υ               | Υ               | Υ               | Υ              | Υ                |

| Write-Multiple-Without-Erase | CDh        | -               | Υ               | Υ               | Υ               | Υ              | Υ                |

### **AP-CFxxxxE3NR-XXXXXXQ**

| Write-Sector(s)            | 30h or 31h | - | Υ | Υ | Υ | Υ | Υ |

|----------------------------|------------|---|---|---|---|---|---|

| Write-Sector-Without-Erase | 38h        | - | Υ | Υ | Υ | Υ | Υ |

| Write-Verify               | 3Ch        | - | Y | Y | Y | Y | Υ |

- 1. FR Features register

- 2. SC Sector Count register

- SC Sector Count register

SN Sector Number register

CY Cylinder registers

DH Drive/Head register

LBA Logical Block Address mode supported (see command descriptions for use)

Y The register contains a valid parameter for this command

For the Drive/Head register:

Y means both the CFC and Head parameters are used

D means only the CFC parameter is valid and not the Head parameter

### AP-CFxxxxE3NR-XXXXXXQ

## 7. Electrical Specification

Caution: Absolute Maximum Stress Ratings – Applied conditions greater than those listed under "Absolute Maximum Stress Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these conditions or conditions greater than those defined in the operational sections of this data sheet is not implied. Exposure to absolute maximum stress rating conditions may affect device reliability.

Table 7-1: Operating range

| <b>Standard Operating Temperature</b> | 0°C to +70°C             |

|---------------------------------------|--------------------------|

| <b>Extended Operating Temperature</b> | -40℃ to +85℃             |

| Supply voltage                        | 5V± 5% (4.75-5.25V)      |

|                                       | 3.3V ± 5% (3.135-3.465V) |

Table 7-2: Absolute maximum power pin stress ratings

| Parameter                                                     | Symbol   | Conditions                    |

|---------------------------------------------------------------|----------|-------------------------------|

| Input Power                                                   | $V_{DD}$ | -0.3V min. to 6.5V max.       |

| Voltage on any pin except V <sub>DD</sub> with respect to GND | V        | -0.5V min. to VDD + 0.5V max. |

Table 7-3: Recommended system power-up timing

| Symbol                             | Parameter                   | Typical | Maximum | Units |

|------------------------------------|-----------------------------|---------|---------|-------|

| T <sub>PU-READY</sub> 1            | Power-up to Ready Operation | 200     | 1000    | ms    |

| T <sub>PU-WRITE</sub> <sup>1</sup> | Power-up to Write Operation | 200     | 1000    | ms    |

<sup>1.</sup> This parameter is measured only for initial qualification and after a design or process change that could affect this parameter.

# Compact Flash Ⅲ series AP-CFxxxxE3NR-XXXXXXQ

### 7.1 DC Characteristics

Table 7-4: DC Characteristics

| Symbol                  | Туре   | Parameter                                               | Min  | Max  | Units   | Conditions                                                                        |

|-------------------------|--------|---------------------------------------------------------|------|------|---------|-----------------------------------------------------------------------------------|

| V <sub>IH1</sub>        |        | Input Voltage                                           | 2.0V |      | V       | V <sub>DDQ</sub> =V <sub>DDQ</sub> Max                                            |

| $V_{\rm IL1}^{\rm IL1}$ | l1     |                                                         |      | 0.8V |         | $V_{DDQ}=V_{DDQ}$ Min                                                             |

| I <sub>IL1</sub>        | I1Z    | Input Leakage Current                                   | -10  | 10   | $\mu$ A | $V_{IN}$ =GND to $V_{DDQ}$                                                        |

|                         | 112    |                                                         |      |      |         | $V_{DDQ} = V_{DDQ} Max$                                                           |

| l <sub>U1</sub>         | I1U    | Input Pull-Up Current                                   | -110 | -1   | $\mu$ A | V <sub>OUT</sub> =GND,                                                            |

| V                       |        | Input Voltage Schmitt Trigger                           |      | 2.0  | V       | $V_{DDQ} = V_{DDQ} Max$ $V_{DDQ} = V_{DDQ} Max$                                   |

| V <sub>T+2</sub>        | 12     | Input voltage Schmitt Higger                            |      | 2.0  | , v     | V <sub>DDQ</sub> =V <sub>DDQ</sub> Min                                            |

| V <sub>T-2</sub>        |        |                                                         | 0.8  |      |         | V DDQ - V DDQ VIIII                                                               |

| I <sub>IL2</sub>        | I2Z    | Input Leakage Current                                   | -10  | 10   | $\mu$ A | V <sub>IN</sub> =GND to V <sub>DDQ</sub>                                          |

|                         | 122    |                                                         |      |      |         | V <sub>DDQ</sub> = V <sub>DDQ</sub> Max                                           |

| l <sub>U2</sub>         | I2U    | Input Pull-Up Current                                   | -110 | -1   | $\mu A$ | V <sub>OUT</sub> =GND,                                                            |

| V                       |        | Output Voltage                                          | 2.4  |      | V       | V <sub>DDQ</sub> = V <sub>DDQ</sub> Max<br>I <sub>OH1</sub> =I <sub>OH1</sub> Min |

| V <sub>OH1</sub>        |        | Output voltage                                          | 2.7  | 0.4  | \ \ \   | I <sub>OL1</sub> =I <sub>OL1</sub> Max                                            |

| V <sub>OL1</sub>        | 01     | Output Current                                          | -4   |      | A       |                                                                                   |

| I <sub>OH1</sub>        |        |                                                         | -4   | 4    | mA      | V <sub>DDQ</sub> =V <sub>DDQ</sub> Min                                            |

| I <sub>OL1</sub>        |        | Output Current                                          |      | 4    | mA      | V <sub>DDQ</sub> =V <sub>DDQ</sub> Min                                            |

| V <sub>OH2</sub>        |        | Output Voltage                                          | 2.4  | 0.4  | V       | I <sub>OH2</sub> =I <sub>OH2</sub> Min                                            |

| $V_{OL2}$               |        |                                                         |      | 0.4  |         | I <sub>OL2</sub> =I <sub>OL2</sub> Max                                            |

| I <sub>OH2</sub>        | O2     | Output Current                                          | -6   |      | mA      | V <sub>DDQ</sub> =3.135V-3.465V                                                   |

| I <sub>OL2</sub>        | 02     | Output Current                                          |      | 6    | mA      | V <sub>DDQ</sub> =3.135V-3.465V                                                   |

| I <sub>OH2</sub>        |        | Output Current                                          | -8   |      | mA      | V <sub>DDQ</sub> =4.5V-5.5V                                                       |

| I <sub>OL2</sub>        |        | Output Current                                          |      | 8    | mA      | V <sub>DDQ</sub> =4.5V-5.5V                                                       |

| V <sub>OH6</sub>        |        | Output Voltage for DASP# pin                            | 2.4  |      | V       | I <sub>OH6</sub> =I <sub>OH6</sub> Min                                            |

| V <sub>OL6</sub>        |        |                                                         |      | 0.4  |         | I <sub>OL6</sub> =I <sub>OL6</sub> Max                                            |

| I <sub>OH6</sub>        | 1      | Output Current for DASP# pin                            | -3   |      | mA      | V <sub>DDQ</sub> =3.135V-3.465V                                                   |

| I <sub>OL6</sub>        | O6     | Output Current for DASP# pin                            |      | 8    | mA      | V <sub>DDQ</sub> =3.135V-3.465V                                                   |

| I <sub>OH6</sub>        |        | Output Current for DASP# pin                            | -3   |      | mA      | V <sub>DDQ</sub> =4.5V-5.5V                                                       |

| I <sub>OL6</sub>        |        | Output Current for DASP# pin                            |      | 12   | mA      | V <sub>DDQ</sub> =4.5V-5.5V                                                       |

| I <sub>DD</sub> 1,2     | DIME   | Power supply current                                    |      | 50   | mA      | V <sub>DD</sub> =V <sub>DD</sub> Max                                              |

|                         | PWR    | $(T_a = 0 \degree C \text{ to } +70 \degree C)$         |      |      | 1       | V <sub>DDQ</sub> =V <sub>DDQ</sub> Max                                            |

| I <sub>DD</sub> 1,2     | PWR    | Power supply current                                    |      | 100  | mA      | V <sub>DD</sub> =V <sub>DD</sub> Max                                              |

| טט                      | FVVI   | $(T_a = -40 \degree C \text{ to } +85 \degree C)$       |      |      |         | V <sub>DDQ</sub> =V <sub>DDQ</sub> Max                                            |

| I <sub>SP</sub>         | PWR    | Sleep/Standby/Idle current                              |      | 100  | $\mu$ A | $V_{DD}=V_{DD}$ Max                                                               |

|                         | 1 4411 | (T <sub>a</sub> = 0 °C to +70 °C)                       |      |      |         | V <sub>DDQ</sub> =V <sub>DDQ</sub> Max                                            |

| I <sub>SP</sub>         | PWR    | Sleep/Standby/Idle current                              |      | 200  | $\mu$ A | V <sub>DD</sub> =V <sub>DD</sub> Max                                              |

|                         | 1 4411 | $(T_a = -40 ^{\circ}\text{C to } +85 ^{\circ}\text{C})$ |      |      |         | V <sub>DDQ</sub> =V <sub>DDQ</sub> Max                                            |

### AP-CFxxxxE3NR-XXXXXXQ

#### 7.2 AC Characteristics

Figure 7-1: AC Input/Output Reference Waveforms

AC test inputs are driven at VIHT (0.9 VDD) for a logic "1" and VILT (0.1 VDD) for a logic "0". Measurement reference points for inputs and outputs are VIT (0.5 VDD) and VOT (0.5 VDD). Input rise and fall times ( $10\% \leftrightarrow 90\%$ ) are <10 ns.

Note: V<sub>IT</sub> - V<sub>INPUT</sub> Test

V<sub>OT</sub> - V<sub>OUTPUT</sub> Test V<sub>IHT</sub> - V<sub>INPUT HIGH</sub> Test V<sub>ILT</sub>- V<sub>INPUT LOW</sub> Test

### AP-CFxxxxE3NR-XXXXXXQ

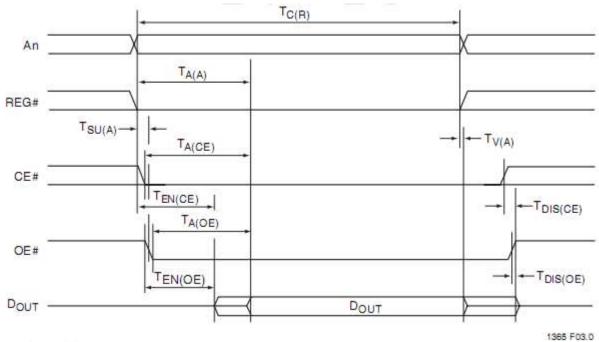

#### 7.2.1 Attribute Memory Read Timing Specification

The Attribute Memory access time is defined as 100 ns. Detailed timing specifications are shown in the table below.

Table 7-5 Attribute Memory Read Timing Specification

| Speed Version                  |                      |             | 100 ns           |                  |       |  |

|--------------------------------|----------------------|-------------|------------------|------------------|-------|--|

| Item                           | Symbol               | IEEE Symbol | Min <sup>1</sup> | Min <sup>1</sup> | Units |  |

| Read Cycle Time                | $T_{C(R)}$           | tAVAV       | 100              |                  | ns    |  |

| Address Access Time            | $T_{A(A)}$           | tAVQV       |                  | 100              | ns    |  |

| Card Enable Access Time        | T <sub>A(CE)</sub>   | tELQV       |                  | 100              | ns    |  |

| Output Enable Access Time      | T <sub>A(OE)</sub>   | tGLQV       |                  | 50               | ns    |  |

| Output Disable Time from CE#   | T <sub>DIS(CE)</sub> | tEHQZ       |                  | 50               | ns    |  |

| Output Disable Time from OE#   | T <sub>DIS(OE)</sub> | tGHQZ       |                  | 50               | ns    |  |

| Address Setup Time             | T <sub>SU(A)</sub>   | tAVGL       | 10               |                  | ns    |  |

| Output Enable Time from CE#    | T <sub>EN(CE)</sub>  | tELQNZ      | 5                |                  | ns    |  |

| Output Enable Time from OE#    | T <sub>EN(OE)</sub>  | tGLQNZ      | 5                |                  | ns    |  |

| Data Valid from Address Change | T <sub>V(A)</sub>    | tAXQZ       | 0                |                  | ns    |  |

<sup>1.</sup> D<sub>OUT</sub> signifies data provided by the Compact Flash card to the system. The CE# signal or both the OE# signal and the WE# signal must be de-asserted between consecutive cycle operations. All AC specifications are guaranteed by design.

Figure 7-2: Attribute Memory Read Timing Diagram

#### AP-CFxxxxE3NR-XXXXXQ

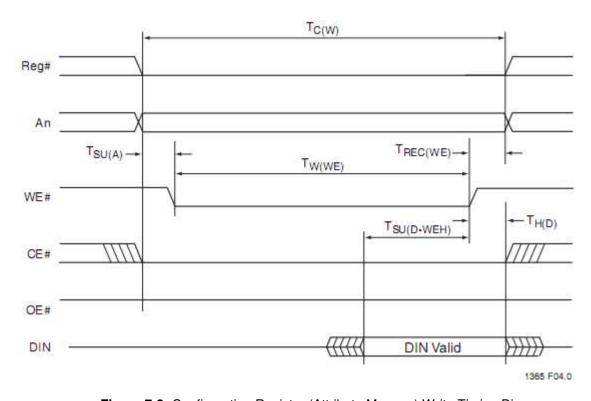

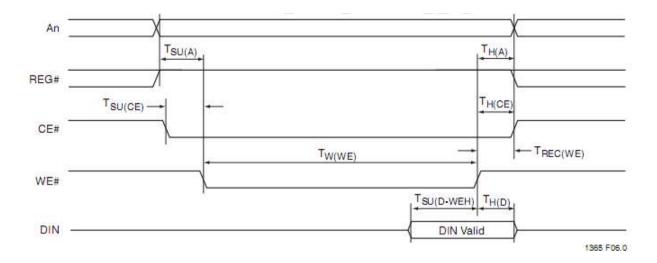

#### 7.2.2 Configuration Register (Attribute Memory) Write Specification

The card configuration write access time is defined as 100 ns. Detailed timing specifications are shown in the table below.

Table 7-6 Configuration Register (Attribute Memory) Write Timing

| Speed Version          |                        |             |                  | 100 ns           |       |  |

|------------------------|------------------------|-------------|------------------|------------------|-------|--|

| Item                   | Symbol                 | IEEE Symbol | Min <sup>1</sup> | Min <sup>1</sup> | Units |  |

| Write Cycle Time       | T <sub>C(W)</sub>      | tAVAV       | 100              |                  | ns    |  |

| Write Pulse Width      | T <sub>W(WE)</sub>     | tWLWH       | 60               |                  | ns    |  |

| Address Setup Time     | T <sub>SU(A)</sub>     | tAVWL       | 10               |                  | ns    |  |

| Write Recover Time     | T <sub>REC(WE)</sub>   | tWMAX       | 15               |                  | ns    |  |

| Data Setup Time for WE | T <sub>SU(DWE#H)</sub> | tDVWH       | 40               |                  | ns    |  |

| Data Hold Time         | T <sub>H(D)</sub>      | tWMDX       | 15               |                  | ns    |  |

<sup>1.</sup> D<sub>IN</sub> signifies data provided by the system to the Compact Flash card. All AC specifications are guaranteed by design.

Figure 7-3: Configuration Register (Attribute Memory) Write Timing Diagram

### AP-CFxxxxE3NR-XXXXXXQ

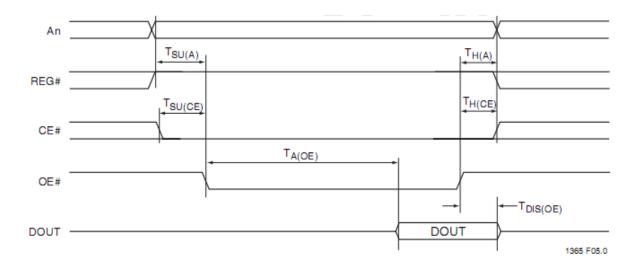

### 7.2.3 Common Memory Read Timing Specification

Table 7-7 Common Memory Read Timing

| Item                        | Symbol               | IEEE Symbol | Min <sup>1</sup> | Min <sup>1</sup> | Units |

|-----------------------------|----------------------|-------------|------------------|------------------|-------|

| Output Enable Access Time   | T <sub>A(OE)</sub>   | tGLQV       |                  | 50               | ns    |

| Output Disable Time from OE | T <sub>DIS(OE)</sub> | tGHQZ       |                  | 50               | ns    |

| Address Setup Time          | T <sub>SU(A)</sub>   | tAVGL       | 10               |                  | ns    |

| Address Hold Time           | T <sub>REC(WE)</sub> | tGHAX       | 15               |                  | ns    |

| CE Setup before OE          | T <sub>SU(CE)</sub>  | tELGL       | 0                |                  | ns    |

| CE Hold following OE        | T <sub>H(CE)</sub>   | tGHEH       | 15               |                  | ns    |

<sup>1.</sup> All AC specifications are guaranteed by design.

Figure 7-4: Common Memory Read Timing Diagram

### 7.2.4 Common Memory Write Timing Specification

Table 7-8 Common Memory Write Timing

| Item                   | Symbol                 | IEEE Symbol | Min <sup>1</sup> | Min <sup>1</sup> | Units |

|------------------------|------------------------|-------------|------------------|------------------|-------|

| Data Setup before WE   | T <sub>SU(DWE#H)</sub> | tDVWH       | 40               |                  | ns    |

| Data Hold following WE | T <sub>H(D)</sub>      | tWMDX       | 15               |                  | ns    |

| WE Pulse Width         | T <sub>W(WE)</sub>     | tWLWH       | 60               |                  | ns    |

| Address Setup Time     | T <sub>SU(A)</sub>     | tAVWL       | 10               |                  | ns    |

| CE Setup before WE     | T <sub>SU(CE)</sub>    | tELWL       | 0                |                  | ns    |

| Write Recovery Time    | T <sub>REC(WE)</sub>   | tWMAX       | 15               |                  | ns    |

| Address Hold Time      | T <sub>H(A)</sub>      | tGHAX       | 15               |                  | ns    |

| CE Hold following WE   | T <sub>H(CE)</sub>     | tGHEH       | 15               |                  | ns    |

<sup>1.</sup> All AC specifications are guaranteed by design.

Figure 7-5: Common Memory Write Timing Diagram

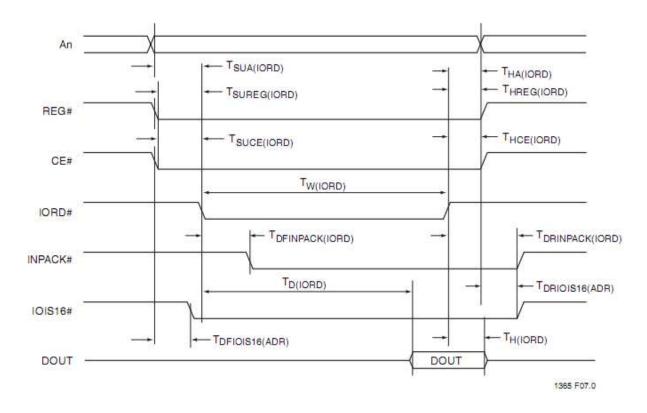

### 7.2.5 I/O Input (Read) Timing Specification

Table 7-9 I/O Read Timing

| Item                              | Symbol                      | IEEE Symbol | Min <sup>1</sup> | Min <sup>1</sup> | Units |

|-----------------------------------|-----------------------------|-------------|------------------|------------------|-------|

| Data Delay after IORD             | $T_{D(IORD)}$               | tIGLQV      |                  | 100              | ns    |

| Data Hold following IORD          | T <sub>H(IORD)</sub>        | tIGHQX      | 0                |                  | ns    |

| IORD Width Time                   | $T_{W(IORD)}$               | tIGLIGH     | 165              |                  | ns    |

| Address Setup before IORD         | T <sub>SUA(IORD)</sub>      | tAVIGL      | 70               |                  | ns    |

| Address Hold following IORD       | T <sub>HA(IORD)</sub>       | tIGHAX      | 20               |                  | ns    |

| CE Setup before IORD              | T <sub>SUCE(IORD)</sub>     | tELIGL      | 5                |                  | ns    |

| CE Hold following IORD            | T <sub>HCE(IORD)</sub>      | tIGHEH      | 20               |                  | ns    |

| REG Setup before IORD             | T <sub>SUREG(IORD)</sub>    | tRGLIGL     | 5                |                  | ns    |

| REG Hold following IORD           | T <sub>HREG(IORD)</sub>     | tIGHRGH     | 0                |                  | ns    |

| INPACK Delay Falling from IORD    | T <sub>DFINPACK(IORD)</sub> | tIGLIAL     | 0                | 45               | ns    |

| INPACK Delay Rising from IORD     | T <sub>DRINPACK(IORD)</sub> | tIGHIAH     |                  | 45               | ns    |

| IOIS16 Delay Falling from Address | T <sub>DFIOIS16(ARD)</sub>  | tAVISL      |                  | 35               | ns    |

| IOIS16 Delay Rising from Address  | T <sub>DRIOIS16(ADR)</sub>  | tAVISH      |                  | 35               | ns    |

All AC specifications are guaranteed by design.

Note: The maximum load on –INPACK and IOIS16# is 1 LSTTL with 50pF total load.

Figure 7-6: I/O Read Timing Diagram

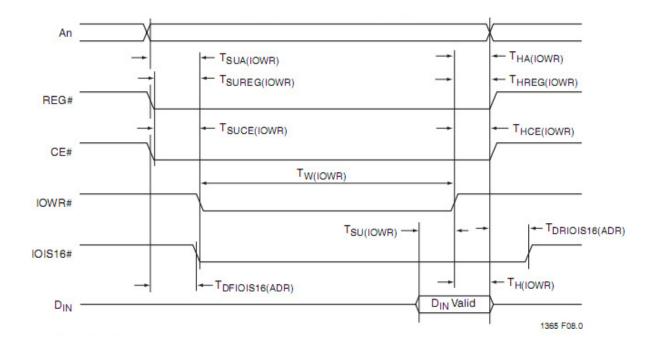

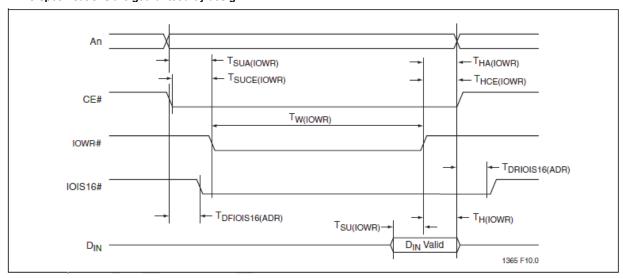

### 7.2.6 I/O Output (Write) Timing Specification

Table 7-10 I/O Write Timing

| Item                              | Symbol                     | IEEE Symbol | Min <sup>1</sup> | Min <sup>1</sup> | Units |

|-----------------------------------|----------------------------|-------------|------------------|------------------|-------|

| Data Setup before IOWR            | T <sub>SU(IOWR)</sub>      | tDVIWH      | 60               |                  | ns    |

| Data Hold following IOWR          | T <sub>H(IOWR)</sub>       | tlWHDX      | 30               |                  | ns    |

| IOWR Width Time                   | $T_{W(IOWR)}$              | tlWLlWH     | 165              |                  | ns    |

| Address Setup before IOWR         | T <sub>SUA(IOWR)</sub>     | tAVIWL      | 70               |                  | ns    |

| Address Hold following IOWR       | T <sub>HA(IOWR)</sub>      | tlWHAX      | 20               |                  | ns    |

| CE Setup before IOWR              | T <sub>SUCE(IOWR)</sub>    | tELIWL      | 5                |                  | ns    |

| CE Hold following IOWR            | T <sub>HCE(IOWR)</sub>     | tIWHEH      | 20               |                  | ns    |

| REG Setup before IOWR             | T <sub>SUREG(IOWR)</sub>   | tRGLIWL     | 5                |                  | ns    |

| REG Hold following IOWR           | T <sub>HREG(IOWR)</sub>    | tlWHRGH     | 0                |                  | ns    |

| IOIS16 Delay Falling from Address | T <sub>DFIOIS16(ARD)</sub> | tAVISL      |                  | 35               | ns    |

| IOIS16 Delay Rising from Address  | T <sub>DRIOIS16(ADR)</sub> | tAVISH      |                  | 35               | ns    |

1. All AC specifications are guaranteed by design.

Note: The maximum load on –INPACK and IOIS16# is 1 LSTTL with 50pF total load.

Figure 7-7: I/O Write Timing Diagram

## AP-CFxxxxE3NR-XXXXXXQ

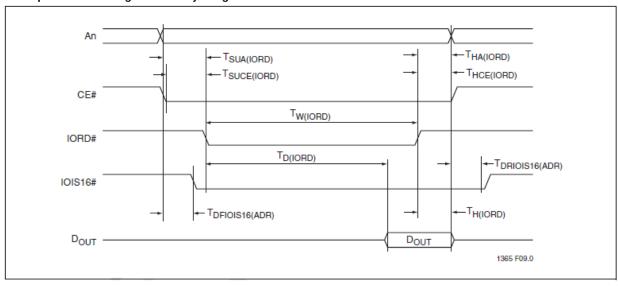

### 7.2.7 True IDE I/O Read Timing

| Item                              | Symbol                     | IEEE Symbol | Min | Max | Units |

|-----------------------------------|----------------------------|-------------|-----|-----|-------|

| Data Delay after IORD             | $T_{D(IORD)}$              | tIGLQV      |     | 50  | ns    |

| Data Hold following IORD          | T <sub>H(IORD)</sub>       | tIGHQX      | 5   |     | ns    |

| IORD Width Time                   | $T_{W(IORD)}$              | tIGLIGH     | 70  |     | ns    |

| Address Setup before IORD         | T <sub>SUA(IORD)</sub>     | tAVIGL      | 25  |     | ns    |

| Address Hold following IORD       | T <sub>HA(IORD)</sub>      | tIGHAX      | 10  |     | ns    |

| CE Setup before IORD              | T <sub>SUCE(IORD)</sub>    | tELIGL      | 10  |     | ns    |

| CE Hold following IORD            | T <sub>HCE(IORD)</sub>     | tIGHEH      | 5   |     | ns    |

| IOIS16 Delay Falling from Address | T <sub>DFIOIS16(ADR)</sub> | tAVISL      |     | 20  | ns    |

| IOIS16 Delay Rising from Address  | T <sub>DRIOIS16(ADR)</sub> | tAVISH      |     | 20  | ns    |

Note: The maximum load on IOIS16# is 1 LSTTL with 50pF total load.

#### All AC specifications are guaranteed by design.

### 7.2.8 True IDE I/O Write Timing

| Item                              | Symbol                     | IEEE Symbol | Min | Max | Units |

|-----------------------------------|----------------------------|-------------|-----|-----|-------|

| Data Setup before IOWR            | T <sub>SU(IOWR)</sub>      | tDVIWH      | 20  |     | ns    |

| Data Hold following IOWR          | $T_{H(IOWR)}$              | tIWHDX      | 10  |     | ns    |

| IOWR Width Time                   | $T_{W(IOWR)}$              | tlWLlWH     | 70  |     | ns    |

| Address Setup before IOWR         | T <sub>SUA(IOWR)</sub>     | tAVIWL      | 25  |     | ns    |

| Address Hold following IOWR       | $T_{HA(IOWR)}$             | tlWHAX      | 10  |     | ns    |

| CE Setup before IOWR              | T <sub>SUCE(IOWR)</sub>    | tELIWL      | 10  |     | ns    |

| CE Hold following IOWR            | T <sub>HCE(IOWR)</sub>     | tIWHEH      | 5   |     | ns    |

| IOIS16 Delay Falling from Address | T <sub>DFIOIS16(ADR)</sub> | tAVISL      |     | 20  | ns    |

| IOIS16 Delay Rising from Address  | T <sub>DRIOIS16(ADR)</sub> | tAVISH      |     | 20  | ns    |

Note: The maximum load on IOIS16# is 1 LSTTL with 50pF total load.

#### All AC specifications are guaranteed by design.

# Compact Flash Ⅲ series AP-CFxxxxE3NR-XXXXXQ

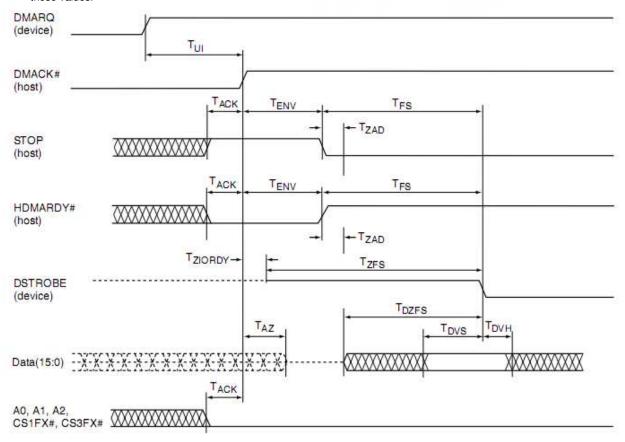

### 7.2.9 Ultra DMA Mode Data Transfer Input/Output (Read/Write) Timing

Table 7-11 Ultra DMA Data Burst Timing Specifications<sup>1</sup>

|                      | <b>5</b>                                                                                                                                 | Мо  | de 4 |      | Measurement           |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|-----------------------|

| Name                 | Descriptions                                                                                                                             | Min | Max  | Unit | Location <sup>2</sup> |

| T <sub>2CYCTYP</sub> | Typical sustained average two cycle time                                                                                                 | 60  |      | ns   | Sender                |

| T <sub>CYC</sub>     | Cycle time allowing for asymmetry and clock variations (from STROBE edge to STROBE edge)                                                 | 25  |      | ns   | Note <sup>3</sup>     |

| T <sub>2CYC</sub>    | Two cycle time allowing for clock variations (from rising edge to next rising edge or from falling edge to next falling edge of STROBE)  | 57  |      | ns   | Sender                |

| T <sub>DS</sub>      | Data setup time at recipient (from data valid until STROBE edge) <sup>4,5</sup>                                                          | 5.0 |      | ns   | Recipient             |

| T <sub>DH</sub>      | Data hold time at Recipient (from STROBE edge until data becomes invalid) <sup>1,2</sup>                                                 | 5.0 |      | ns   | Recipient             |

| T <sub>DVS</sub>     | Data valid setup time for Sender (from data valid until STROBE edge) <sup>6</sup>                                                        | 6.0 |      | ns   | Sender                |

| T <sub>DVH</sub>     | Data valid hold time at Sender (from STROBE edge until data becomes invalid) <sup>3</sup>                                                | 6.0 |      | ns   | Sender                |

| T <sub>CS</sub>      | CRC word setup time at device <sup>1</sup>                                                                                               | 5.0 |      | ns   | Device                |

| T <sub>CH</sub>      | CRC word hold time at device <sup>1</sup>                                                                                                | 5.0 |      | ns   | Device                |

| T <sub>CVS</sub>     | CRC word valid setup time at host (from CRC valid until DMACK negation) <sup>3</sup>                                                     | 6.7 |      | ns   | Host                  |

| T <sub>CVH</sub>     | CRC word valid hold time at Sender (from DMACK negation until CRC becomes invalid) <sup>3</sup>                                          | 6.2 |      | ns   | Host                  |

| T <sub>ZFS</sub>     | Time from STROBE output released-to-driving until the first transition of critical timing                                                | 0   |      | ns   | Device                |

| T <sub>DZFS</sub>    | Time from data output released-to-driving until the first transition of critical timing                                                  | 6.7 |      | ns   | Sender                |

| T <sub>FS</sub>      | First STROBE time (for device to first negate DSTROBE from STOP during a data in burst)                                                  |     | 120  | ns   | Device                |

| T <sub>LI</sub>      | Limited interlock time <sup>7</sup>                                                                                                      | 0   | 100  | ns   | Note <sup>8</sup>     |

| T <sub>MLI</sub>     | Interlock time with minimum <sup>4</sup>                                                                                                 | 20  |      | ns   | Host                  |

| T <sub>UI</sub>      | Unlimited interlock time <sup>4</sup>                                                                                                    | 0   |      | ns   | Host                  |

| T <sub>AZ</sub>      | Maximum time allowed for output drivers to release (from asserted to negated)                                                            |     | 10   | ns   | Note <sup>9</sup>     |

| T <sub>ZAH</sub>     | Minimum delay time required for output                                                                                                   | 20  |      | ns   | Host                  |

| T <sub>ZAD</sub>     | Drivers to assert or negate (from released)                                                                                              | 0   |      | ns   | Device                |

| T <sub>ENV</sub>     | Envelope time (from DMACK# to STOP and HDMARDY# during data in burst initiation and from DMACK to STOP during data our burst initiation) | 20  | 55   | ns   | Host                  |

| T <sub>RFS</sub>     | Ready-to-final STROBE time (no STROBE edge are sent this long after negation of DMARDY)                                                  |     | 60   | ns   | Sender                |

| T <sub>RP</sub>      | Ready-to-pause time (Recipient waits to pause until after negating DMARDY)                                                               | 100 |      | ns   | Recipient             |

| T <sub>IORDYZ</sub>  | Maximum time before releasing IORDY                                                                                                      |     | 20   | ns   | Device                |

| T ZIORDY             | Minimum time before driving IORDY <sup>10</sup>                                                                                          | 0   |      | ns   | Device                |

| TACK                 | Ŭ.                                                                                                                                       | 20  |      | ns   | Host                  |

| T <sub>SS</sub>      |                                                                                                                                          | 50  |      | ns   | Sender                |

#### AP-CFxxxxE3NR-XXXXXQ

- 1. All timing measurement switching points (low-to-high and high-to-low) are taken at 1.5V.

- 2. All signal transitions for a timing parameter are measured at the connector specified in the measurement location column. For example, in the case of TRFS, both STROBE and DMARDY Transitions are measured at the Sender connector.

- 3. The parameter TCYC is measured at the recipient's connector farthest from the Sender.

- 4. 80-Conductor cabling is required in order to meet sup (TDS, TCS) and hold (TDH, TCH) times in modes greater than two.

- 5. The parameters TDS and TDH for Mode 5 are defined for a Recipient at the end of the cable only in a configuration with a single device located at the end of the cable. This could result in the minimum values for TDS and TDH for mode 5 at the middle connector being 3.0 and 3.9 ns respectively.

- 6. Timing for TDVS, TDVH, TCVS, and TCVH are met for lumped capacitive loads of 15 and 50 pf at the connector where the Data and STROBE signals have the same capacitive load value. Due to reflections on the cable, these timing measurements are not valid in a normally functioning system.

- 7. The parameters TUI, TMLI, and TLI indicate Sender-to-Recipient or Recipient-to-Sender interlocks. For example, one agent (either Sender or Recipient) is waiting for the other agent to respond with a signal before proceeding; TUI is an unlimited interlock that has no maximum time value, TMLI is a limited time-out that has a defined maximum.

- 8. The parameter TLI is measured at the connector of the Sender or Recipient that is responding to an incoming transition from the Recipient or Sender respectively. Both the incoming signal and the outgoing response are measured at the same connector.

- 9. The parameter TAZ is measured at the connector of the Sender or Recipient that is driving the bus but must release the bus that allow for a bus turnaround.

- 10. For all modes the parameter TZIORDY may be greater than TENV because the host has a pull-on IORDY giving it a known state when released.

#### AP-CFxxxxE3NR-XXXXXQ

Table 7-12 Ultra DMA Sender and Recipient IC Timing Specifications<sup>1</sup>

| Nomo               | Name Descriptions                                                                |     | Mode 4 |      |  |

|--------------------|----------------------------------------------------------------------------------|-----|--------|------|--|

| ivaille            |                                                                                  |     | Max    | Unit |  |

| T <sub>DSIC</sub>  | Recipient IC data setup time (from data valid until STROBE edge) <sup>2</sup>    | 4.8 |        | ns   |  |

| T <sub>DHIC</sub>  | Recipient IC data hold time (from STROBE edge until data becomes                 | 4.8 |        | ns   |  |

|                    | invalid) <sup>1</sup>                                                            |     |        |      |  |

| T <sub>DVSIC</sub> | Sender IC data valid setup time (from data valid until STROBE edge) <sup>3</sup> | 9.5 |        | ns   |  |

| T <sub>DVHIC</sub> |                                                                                  | 9.0 |        | ns   |  |

- 1. All timing measurement switching point (low-to-high and high-to-low)

- 2. The correct data value is captured by the Recipient given input data with a slew rate of 0.4 V/ns rising and falling and the input STROBE with a slew rate of 0.4 V/ns rising and falling at TDSIC and TDHIC timing (as measured through 1.5 V).

- 3. The parameters TDVSIC and TDVHIC are met for lumped capacitive loads of 15 and 40 pf at the IC where all signals have the same capacitive load value. Noise that may couple onto the output signals from external sources has not been included in these values.

Figure 7-8: Initiating an Ultra DMA Data-In Burst

#### Notes:

The definitions for the DIOW-:STOP, DIOR-:HDMARDY-:HSTROBE, and IORDY:DDRARDY-: DSTROBE signal lines are not in effect until DMARQ and DMACK are asserted.