# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 56F8014

Data Sheet Technical Data

56F8000 16-bit Digital Signal Controllers

MC56F8014 Rev. 11 05/2008

freescale.com

\_\_\_\_\_

#### **Document Revision History**

| Version History | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Rev 0           | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| Rev 1           | Updates to Part 10, Specifications,<br>Table 10-1, added maximum clamp current, per pin<br>Table 10-11, clarified variation over temperature table and graph<br>Table 10-15, added LIN slave timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| Rev 2           | Added alternate pins to Figure 11-1 and Table 11-1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| Rev 3           | Corrected bit selects in Timer Channel 3 Input (TC3_INP) bit 9, Section 6.3.1.7, clarified Section 1.4.1, and simplified notes in Table 10-9,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| Rev 4           | Added clarification on sync inputs in Section 1.4.1, added voltage difference specification to Table 10-1 and Table 10-4, deleted formula for Ambient Operating Temperature in Table 10-4, and a note for pin group 3, corrected Table 8-1, error in Port C peripheral function configuration, updated notes in Table 10-9. Added RoHs and "pb-free" language to back cover.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| Rev 5           | Updates to Section 10<br>Table 10-5, corrected max values for ADC Input Current High and Low; corrected typ value for<br>pull-up disabled Digital Input Current Low (a)<br>Table 10-6, corrected typ and added max values for Standby > Stop and Powerdown modes<br>Table 10-7, corrected min value for Low-Voltage Interrupt for 3.3V<br>Table 10-11, corrected typ and max values and units for PLL lock time<br>Table 10-12, corrected typ values for Relaxation Oscillator output frequency and variation over<br>temperature (also increased temp range to 150 degreesC) and added variation over<br>temperature from 0—105 degreesC<br>Updated Figure 10-5<br>Table 10-19, updated max values for Integral Non-Linearity full input signal range, Negative<br>Differential Non-Linearity, ADC internal clock, Offset Voltage Internal Ref, Gain Error and Offset<br>Voltage External Ref; updated typ values for Negative Differential Non-Linearity, Offset Voltage<br>Internal Ref, Gain Error and Offset Voltage External Ref; added new min values and corrected<br>typ values for Signal-to-noise ratio, Total Harmonic Distortion, Spurious Free Dynamic Range,<br>Signal-to-noise plus distortion, Effective Number of Bits |  |  |  |  |  |  |

| Rev 6           | Added details to Section 1. Clarified language in State During Reset column in Table 2-3; corrected flash data retention temperature in Table 10-4; moved input current high/low toTable 10-19 and location of footnotes in Table 10-5; reorganized Table 10-19; clarified title of Figure 10-1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| Rev. 7          | <ul> <li>In Table 10-4, added an entry for flash data retention with less than 100 program/erase cycles (minimum 20 years).</li> <li>In Table 10-6, changed the device clock speed in STOP mode from 8MHz to 4MHz.</li> <li>In Table 10-12, changed the typical relaxation oscillator output frequency in Standby mode from 400kHz to 200kHz.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

| Rev. 8          | In Table 10-19, changed the maximum ADC internal clock frequency from 8MHz to 5.33MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| Version History | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Rev. 9          | Added the following note to the description of the TMS signal in Table 2-3:<br>Note: Always tie the TMS pin to $V_{DD}$ through a 2.2K resistor.                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

| Rev. 10         | <ul> <li>In Table 2-3, changed V<sub>CAP</sub> value from 4.7 μF to 2.2 μF.</li> <li>In Table 2-3, changed the input type for FAULT3 (was "Output", is "Input").</li> <li>In Table 2-3, changed the input type for FAULT2 (was "Input/Output", is "Input").</li> <li>Revised Section 7, Security Features.</li> <li>Added MC56F8014MFAE to Section 13, Ordering Information.</li> <li>Fixed miscellaneous errors.</li> </ul> |  |  |  |  |  |  |

| Rev.11          | Updated temperature information in Table 10-1 and Table 10-4.                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

#### **Document Revision History (Continued)**

Please see http://www.freescale.com for the most current data sheet revision.

## 56F8014 General Description

- Up to 32 MIPS at 32MHz core frequency

- DSP and MCU functionality in a unified, C-efficient architecture

- 16KB Program Flash

- 4KB Unified Data/Program RAM

- One 5-channel PWM module

- Two 4-channel 12-bit ADCs

- One Serial Communication Interface (SCI) with LIN slave functionality

- One Serial Peripheral Interface (SPI)

- One 16-bit Quad Timer

- One Inter-Integrated Circuit (I<sup>2</sup>C) Port

- Computer Operating Properly (COP)/Watchdog

- On-Chip Relaxation Oscillator

- Integrated Power-On Reset and Low-Voltage Interrupt Module

- JTAG/Enhanced On-Chip Emulation (OnCE™) for unobtrusive, real-time debugging

- Up to 26 GPIO lines

- 32-pin LQFP Package

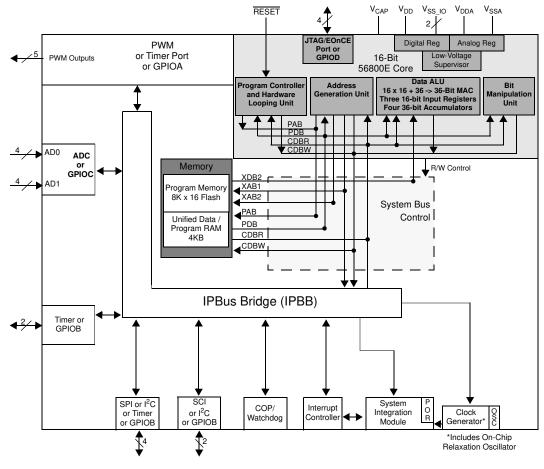

56F8014 Block Diagram

### 56F8014 Data Sheet Table of Contents

| Part 1: Overview                           |          | . 6 |

|--------------------------------------------|----------|-----|

| 1.1. 56F8014 Features                      | . 6      |     |

| 1.2. 56F8014 Description                   |          |     |

| 1.3. Award-Winning Development Environment | . 8      |     |

| 1.4. Architecture Block Diagram            | . 9      |     |

| 1.5. Synchronize ADC with PWM              |          |     |

| 1.6. Multiple Frequency PWM Output         |          |     |

| 1.7. Product Documentation                 | 13       |     |

| 1.8. Data Sheet Conventions                | 13       |     |

| Part 2: Signal/Connection Descriptions .   |          | 11  |

| 2.1. Introduction                          |          | 14  |

| 2.1. Introduction                          | 14<br>18 |     |

|                                            | 10       |     |

| Part 3: OCCS                               |          | 26  |

| 3.1. Overview                              | 26       |     |

| 3.2. Features                              | 26       |     |

| 3.3. Operating Modes                       | 26       |     |

| 3.4. Block Diagram                         | 28       |     |

| 3.5. Pin Descriptions                      | 29       |     |

| Part 4: Memory Map                         |          | 29  |

|                                            |          | 23  |

| 4.1. Introduction                          | 29       |     |

| 4.2. Interrupt Vector Table                | 29       |     |

| 4.3. Program Map                           | 31       |     |

| 4.4. Data Map                              | 32       |     |

| 4.5. EOnCE Memory Map                      | 32       |     |

| 4.6. Peripheral Memory Mapped Registers    | 33       |     |

| Part 5: Interrupt Controller (ITCN)        |          | 43  |

| 5.1. Introduction                          | 43       |     |

| 5.2. Features                              | 43       |     |

| 5.3. Functional Description                | 43       |     |

| 5.4. Block Diagram                         | 45       |     |

| 5.5. Register Descriptions                 | 45       |     |

| 5.6. Resets                                | 61       |     |

| Part 6: System Integration Module (SIM)    |          | ດວ  |

| 6.1. Introduction                          |          | 02  |

|                                            | 62       |     |

| 6.2. Features                              | 62       |     |

| 6.3. Register Descriptions                 | 64       |     |

| 6.4. Clock Generation Overview             | 77       |     |

| 6.5. Power-Down Modes                      | 77       |     |

| 6.6. Resets                                | 79       |     |

| 6.7. Clocks                                | 81       |     |

| 6.8. Interrupts                            | 82       |     |

| Part 7: Security Features                          |

|----------------------------------------------------|

| 7.1. Operation with Security Enabled               |

| 7.2. Flash Access Lock and Unlock Mechanisms 83    |

| 7.3. Product Analysis                              |

| Part 8: General Purpose Input/Output (GPIO)        |

|                                                    |

| 8.1. Introduction                                  |

| 8.3. Reset Values                                  |

|                                                    |

| Part 9: Joint Test Action Group (JTAG)91           |

| 9.1. 56F8014 Information91                         |

| Part 10: Specifications91                          |

| 10.1. General Characteristics                      |

| 10.2. DC Electrical Characteristics                |

| 10.3. AC Electrical Characteristics                |

| 10.4. Flash Memory Characteristics                 |

| 10.5. External Clock Operation Timing              |

| 10.6. Phase Locked Loop Timing                     |

| 10.7. Relaxation Oscillator Timing                 |

| 10.8. Reset, Stop, Wait, Mode Select, and          |

| Interrupt Timing                                   |

| 10.9. Serial Peripheral Interface (SPI) Timing 102 |

| 10.10. Quad Timer Timing                           |

| 10.11. Serial Communication Interface (SCI)        |

| Timing                                             |

|                                                    |

| 10.13. JTAG Timing                                 |

| 10.14. Analog-to-Digital Converter (ADC)           |

| Parameters                                         |

| 10.15. Equivalent Circuit for ADC Inputs 112       |

| 10.16. Power Consumption                           |

| Part 11: Packaging115                              |

| 11.1. 56F8014 Package and Pin-Out                  |

| Information                                        |

| Ded 40. Design Operations 440                      |

| Part 12: Design Considerations118                  |

| 12.1. Thermal Design Considerations 118            |

| 12.2. Electrical Design Considerations 119         |

| Part 13: Ordering Information121                   |

| Part 14: Appendix                                  |

# Part 1 Overview

### 1.1 56F8014 Features

#### 1.1.1 Digital Signal Controller Core

- Efficient 16-bit 56800E family Digital Signal Controller (DSC) engine with dual Harvard architecture

- As many as 32 Million Instructions Per Second (MIPS) at 32MHz core frequency

- Single-cycle 16 × 16-bit parallel Multiplier-Accumulator (MAC)

- Four 36-bit accumulators, including extension bits

- 32-bit arithmetic and logic multi-bit shifter

- Parallel instruction set with unique DSP addressing modes

- Hardware DO and REP loops

- Three internal address buses

- Four internal data buses

- Instruction set supports both DSP and controller functions

- Controller-style addressing modes and instructions for compact code

- Efficient C compiler and local variable support

- Software subroutine and interrupt stack with depth limited only by memory

- JTAG/Enhanced On-Chip Emulation (OnCE) for unobtrusive, processor speed-independent, real-time debugging

#### 1.1.2 Memory

- Dual Harvard architecture permits as many as three simultaneous accesses to program and data memory

- Flash security and protection that prevent unauthorized users from gaining access to the internal Flash

- On-chip memory

- 16KB of Program Flash

- 4KB of Unified Data/Program RAM

- EEPROM emulation capability using Flash

#### 1.1.3 Peripheral Circuits for 56F8014

- One multi-function five-output Pulse Width Modulator (PWM) module

- Up to 96MHz PWM operating clock

- 15 bits of resolution

- Center-aligned and Edge-aligned PWM signal mode

- Three programmable fault inputs with programmable digital filter

- Double-buffered PWM registers

- Each complementary PWM signal pair can output a different switching frequency by selecting PWM generation sources from:

- PWM generator

- External GPIO

- Internal timers

- ADC conversion result of over/under limits:

When conversion result is greater than high limit, deactivate PWM signal

When conversion result is less than low limit, activate PWM signal

- Two independent 12-bit Analog-to-Digital Converters (ADCs)

- 2 x 4 channel inputs

- Supports both simultaneous and sequential conversions

- ADC conversions can be synchronized by both PWM and timer modules

- Sampling rate up to 2.67MSPS

- 8-word result buffer registers

- ADC Smart Power Management (Auto-standby, auto-powerdown)

- One 16-bit multi-purpose Quad Timer module (TMR)

- Up to 96MHz operating clock

- Four independent 16-bit counter/timers with cascading capability

- Each timer has capture and compare capability

- Up to 12 operating modes

- One Serial Communication Interface (SCI) with LIN slave functionality

- Full-duplex or single-wire operation

- Two receiver wake-up methods:

- Idle line

- Address mark

- One Serial Peripheral Interface (SPI)

- Full-duplex operation

- Master and slave modes

- Programmable length transactions (two to sixteen bits)

- One Inter-Integrated Circuit (I<sup>2</sup>C) port

- Operates up to 400 kbps

- Supports both master and slave operation

- Computer Operating Properly (COP)/Watchdog timer capable of selecting different clock sources

- Up to 26 General-Purpose I/O (GPIO) pins with 5V tolerance

- Integrated Power-On Reset and Low-Voltage Interrupt Module

- Phase Lock Loop (PLL) provides a high-speed clock to the core and peripherals

- Clock Sources:

- On-chip relaxation oscillator

External clock source

- On-chip regulators for digital and analog circuitry to lower cost and reduce noise

- JTAG/EOnCE debug programming interface for real-time debugging

#### 1.1.4 Energy Information

- Fabricated in high-density CMOS with 5V-tolerant, TTL-compatible digital inputs

- On-chip regulators for digital and analog circuitry to lower cost and reduce noise

- Wait and Stop modes available

- ADC smart power management

- Each peripheral can be individually disabled to save power

## 1.2 56F8014 Description

The 56F8014 is a member of the 56800E core-based family of Digital Signal Controllers (DSCs). It combines, on a single chip, the processing power of a DSP and the functionality of a microcontroller with a flexible set of peripherals to create an extremely cost-effective solution. Because of its low cost, configuration flexibility, and compact program code, the 56F8014 is well-suited for many applications. The 56F8014 includes many peripherals that are especially useful for industrial control, motion control, home appliances, general purpose inverters, smart sensors, fire and security systems, switched-mode power supplies, power management, and medical monitoring applications.

The 56800E core is based on a dual Harvard-style architecture consisting of three execution units operating in parallel, allowing as many as six operations per instruction cycle. The MCU-style programming model and optimized instruction set allow straightforward generation of efficient, compact DSP and control code. The instruction set is also highly efficient for C compilers to enable rapid development of optimized control applications.

The 56F8014 supports program execution from internal memories. Two data operands can be accessed from the on-chip data RAM per instruction cycle. The 56F8014 also offers up to 26 General Purpose Input/Output (GPIO) lines, depending on peripheral configuration.

The 56F8014 Digital Signal Controller includes 16KB of Program Flash and 4KB of Unified Data/Program RAM. Program Flash memory can be independently bulk erased or erased in pages. Program Flash page erase size is 512 Bytes/256 Words.

A full set of programmable peripherals—PWM, ADCs, SCI, SPI, I<sup>2</sup>C, Quad Timer—support various applications. Each peripheral can be independently shut down to save power. Any pin in these peripherals can also be used as a General Purpose Input/Outputs (GPIO).

## **1.3 Award-Winning Development Environment**

Processor Expert<sup>TM</sup> (PE) provides a Rapid Application Design (RAD) tool that combines easy-to-use component-based software application creation with an expert knowledge system.

The CodeWarrior Integrated Development Environment is a sophisticated tool for code navigation, compiling, and debugging. A complete set of evaluation modules (EVMs), demonstration board kit and development system cards will support concurrent engineering. Together, PE, CodeWarrior and EVMs

create a complete, scalable tools solution for easy, fast, and efficient development.

#### 1.4 Architecture Block Diagram

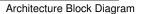

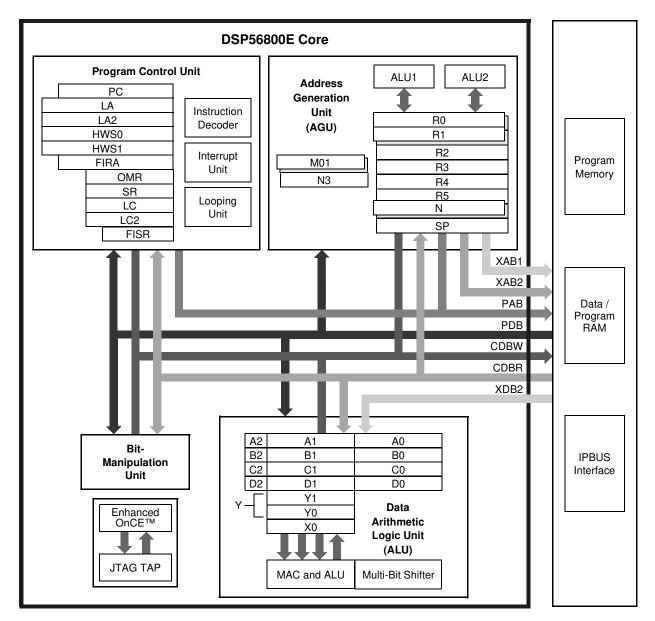

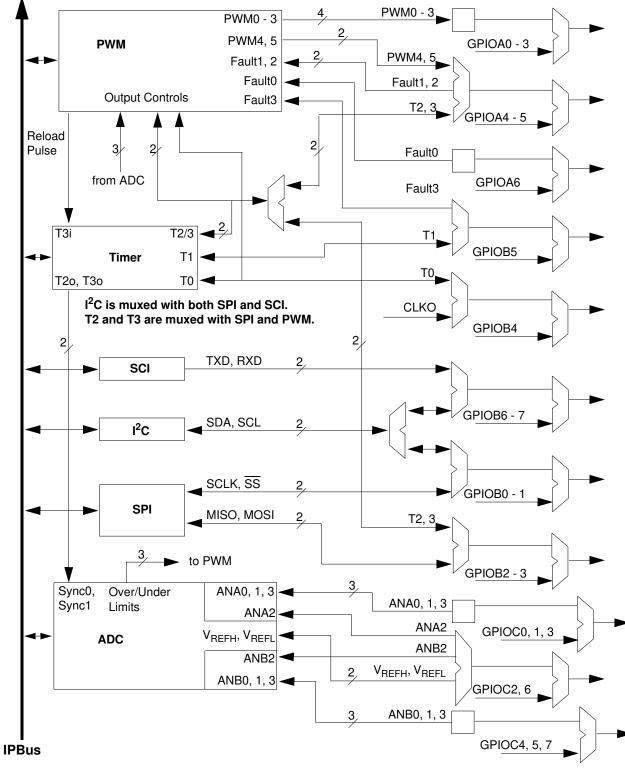

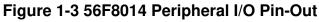

The 56F8014's architecture is shown in **Figure 1-1**, **Figure 1-2**, and **Figure 1-3**. **Figure 1-1** illustrates how the 56800E system buses communicate with internal memories and the IPBus Bridge, as well as showing the internal connections between each unit of the 56800E core. **Figure 1-2** shows the peripherals and control blocks connected to the IPBus Bridge. **Figure 1-3** details how the device's I/O pins are muxed. The figures do not show the on-board regulator and power and ground signals. They also do not show the multiplexing between peripherals or the dedicated GPIOs. Please see **Part 2 Signal/Connection Descriptions** to see which signals are multiplexed with those of other peripherals.

### **1.5 Synchronize ADC with PWM**

ADC conversion can be synchronized with the PWM module via Quad Timer channel 2 and 3 if needed. Internally, the PWM synch signal — which is generated at every PWM reload —can be connected to the timer channel 3 input, and the timer channel 2 and channel 3 outputs are connected to the ADC sync inputs. Timer channel 3 output is connected to SYNC0 and timer channel 2 is connected to SYNC1. The setting is controlled by the TC3\_INP bit in the SIM Control Register; see Section 6.3.1.

SYNC0 is the master ADC sync input, used to trigger both ADCA and ADCB in sequence and parallel mode. SYNC1 is used to trigger ADCB in parallel independent mode, while SYNC0 is used to trigger ADCA. See *MC56F8000RM*, the 56F801X Peripheral Reference Manual, for additional information.

## **1.6 Multiple Frequency PWM Output**

When both PWM channels of a complementary pair in software control mode and software control bits are set to 1, each complementary PWM signal pair — PWM 0 and 1; PWM 2 and 3; and PWM 4 and 5 — can select a PWM source from one of the following sources. This will enable each PWM pair and PWM2 to output PWM signals at different frequencies.

- External GPIO input:

- GPIOB2 input can be used to drive PWM 0 and 1

- GPIOB3 input can be used to drive PWM 2

- GPIOB4 input can be used to drive PWM 4 and 5

- Quad Timer output:

- Timer0 output can be used to drive PWM 0 and 1

- Timer2 output can be used to drive PWM 2

- Timer3 output can be used to drive PWM 4 and 5

- ADC conversion result:

- Signal of over/under limit of ADC sample 0 can be used to drive PWM 0 and 1

- Signal of over/under limit of ADC sample 1 can be used to drive PWM 2

- Signal of over/under limit of ADC sample 2 can be used to drive PWM 4 and 5

Figure 1-1 56800E Core Block Diagram

Figure 1-2 Peripheral Subsystem

#### (Continued from Figure 1-2) To/From IPBus Bridge

56F8014 Technical Data, Rev. 11

#### **1.7 Product Documentation**

The documents listed in **Table 1-1** are required for a complete description and proper design with the 56F8014. Documentation is available from local Freescale distributors, Freescale Semiconductor sales offices, Freescale Literature Distribution Centers, or online at:

#### http://www.freescale.com

| Торіс                                   | Description                                                                                                                            | Order Number |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Торіс                                   | Description                                                                                                                            |              |

| DSP56800E<br>Reference Manual           | Detailed description of the 56800E family architecture,<br>16-bit Digital Signal Controller core processor, and the<br>instruction set | DSP56800ERM  |

| 56F801X Peripheral<br>Reference Manual  | Detailed description of peripherals of the 56F801X family of devices                                                                   | MC56F8000RM  |

| 56F801x Serial<br>Bootloader User Guide | Detailed description of the Serial Bootloader in the 56F801x family of devices                                                         | 56F801xBLUG  |

| 56F8014<br>Technical Data Sheet         | Electrical and timing specifications, pin descriptions, and package descriptions (this document)                                       | MC56F8014    |

| 56F8014<br>Errata                       | Details any chip issues that might be present                                                                                          | MC56F8014E   |

Table 1-1 56F8014 Chip Documentation

### 1.8 Data Sheet Conventions

This data sheet uses the following conventions:

OVERBAR

This is used to indicate a signal that is active when pulled low. For example, the RESET pin is active when low.

"asserted" A high true (active high) signal is high or a low true (active low) signal is low.

"deasserted" A high true (active high) signal is low or a low true (active low) signal is high.

| Examples: | Signal/Symbol | Logic State | Signal State | Voltage <sup>1</sup>             |

|-----------|---------------|-------------|--------------|----------------------------------|

|           | PIN           | True        | Asserted     | $V_{IL}/V_{OL}$                  |

|           | PIN           | False       | Deasserted   | V <sub>IH</sub> /V <sub>OH</sub> |

|           | PIN           | True        | Asserted     | V <sub>IH</sub> /V <sub>OH</sub> |

|           | PIN           | False       | Deasserted   | V <sub>IL</sub> /V <sub>OL</sub> |

1. Values for  $V_{IL},\,V_{OL},\,V_{IH},$  and  $V_{OH}$  are defined by individual product specifications.

# Part 2 Signal/Connection Descriptions

## 2.1 Introduction

The input and output signals of the 56F8014 are organized into functional groups, as detailed in **Table 2-1**. **Table 2-2** summarizes all device pins. In **Table 2-2**, each table row describes the signal or signals present on a pin, sorted by pin number.

| Functional Group                                         | Number of Pins |

|----------------------------------------------------------|----------------|

| Power (V <sub>DD</sub> or V <sub>DDA</sub> )             | 2              |

| Ground (V <sub>SS</sub> or V <sub>SSA</sub> )            | 3              |

| Supply Capacitors                                        | 1              |

| Reset                                                    | 1              |

| Pulse Width Modulator (PWM) Ports <sup>1</sup>           | 5              |

| Serial Peripheral Interface (SPI) Ports <sup>2</sup>     | 4              |

| Analog-to-Digital Converter (ADC) Ports                  | 8              |

| Timer Module Ports <sup>3</sup>                          | 2              |

| Serial Communications Interface (SCI) Ports <sup>4</sup> | 2              |

| JTAG/Enhanced On-Chip Emulation (EOnCE)                  | 4              |

#### **Table 2-1 Functional Group Pin Allocations**

1. Pins in this section can function as TMR and GPIO.

2. Pins in this section can function as TMR,  $\ensuremath{I^2C}\xspace$  , and GPIO.

3. Pins can function as PWM and GPIO.

4. Pins in this section can function as  $I^2C$  and GPIO.

\_\_\_\_\_

|               |             |                                     | Perip      | nerals | :   |      |                                   |                 |               |                    |      |       |

|---------------|-------------|-------------------------------------|------------|--------|-----|------|-----------------------------------|-----------------|---------------|--------------------|------|-------|

| LQFP<br>Pin # | Pin<br>Name | Signal Name                         | GPIO       | I2C    | SCI | SPI  | ADC                               | PWM             | Quad<br>Timer | Power &<br>Ground  | JTAG | Misc. |

| 1             | GPIOB1      | GPIOB1, <del>SS</del> ,<br>SDA      | B1         | SDA    |     | SS   |                                   |                 |               |                    |      |       |

| 2             | GPIOB7      | GPIOB7, TXD,<br>SCL                 | B7         | SCL    | TXD |      |                                   |                 |               |                    |      |       |

| 3             | GPIOB5      | GPIOB5, T1,<br>FAULT3               | B5         |        |     |      |                                   | FAULT3          | T1            |                    |      |       |

| 4             | ANB0        | ANB0, GPIOC4                        | C4         |        |     |      | ANB0                              |                 |               |                    |      |       |

| 5             | ANB1        | ANB1, GPIOC5                        | C5         |        |     |      | ANB1                              |                 |               |                    |      |       |

| 6             | ANB2        | anb2, v <sub>refl</sub> ,<br>GPIOC6 | C6         |        |     |      | ANB2,<br>V <sub>REFL</sub>        |                 |               |                    |      |       |

| 7             | ANB3        | ANB3, GPIOC7                        | C7         |        |     |      | ANB3                              |                 |               |                    |      |       |

| 8             | VDDA        | V <sub>DDA</sub>                    |            |        |     |      |                                   |                 |               | V <sub>DDA</sub>   |      |       |

| 9             | VSSA        | V <sub>SSA</sub>                    |            |        |     |      |                                   |                 |               | V <sub>SSA</sub>   |      |       |

| 10            | ANA3        | ANA3, GPIOC3                        | C3         |        |     |      | ANA3                              |                 |               |                    |      |       |

| 11            | ANA2        | ANA2, V <sub>REFH</sub> ,<br>GPIOC2 | C2         |        |     |      | <b>ANA2,</b><br>V <sub>REFH</sub> |                 |               |                    |      |       |

| 12            | ANA1        | ANA1, GPIOC1                        | C1         |        |     |      | ANA1                              |                 |               |                    |      |       |

| 13            | ANA0        | ANA0, GPIOC0                        | C0         |        |     |      | ANA0                              |                 |               |                    |      |       |

| 14            | VSS_IO      | V <sub>SS_IO</sub>                  |            |        |     |      |                                   |                 |               | V <sub>SS_IO</sub> |      |       |

| 15            | тск         | TCK, GPIOD2                         | D2         |        |     |      |                                   |                 |               |                    | тск  |       |

| 16            | RESET       | RESET, GPIOA7                       | A7         |        |     |      |                                   |                 |               |                    |      | RESET |

| 17            | GPIOB3      | GPIOB3, MOSI,<br>T3                 | B3         |        |     | MOSI |                                   |                 | Т3            |                    |      |       |

| 18            | GPIOB2      | GPIOB2, MISO,<br>T2                 | B2         |        |     | MISO |                                   |                 | T2            |                    |      |       |

| 19            | GPIOB4      | GPIOB4, T0,<br>CLKO                 | B4         |        |     |      |                                   |                 | Т0            |                    |      | CLKO  |

| 20            | GPIOA5      | GPIOA5, PWM5,<br>FAULT2, T3         | A5         |        |     |      |                                   | PWM5,<br>FAULT2 | Т3            |                    |      |       |

| 21            | GPIOB0      | GPIOB0, SCLK,<br>SCL                | B0         | SCL    |     | SCLK |                                   |                 |               |                    |      |       |

| 22            | GPIOA4      | GPIOA4, PWM4,<br>FAULT1, T2         | <b>A</b> 4 |        |     |      |                                   | PWM4,<br>FAULT1 | T2            |                    |      |       |

| 23            | GPIOA2      | GPIOA2, PWM2                        | A2         |        |     |      |                                   | PWM2            |               |                    |      |       |

| 24            | VCAP        | V <sub>CAP</sub>                    |            |        |     |      |                                   |                 |               | V <sub>CAP</sub>   |      |       |

|               |               |                            |            |     | :   |     |     |      |               |                    |      |       |

|---------------|---------------|----------------------------|------------|-----|-----|-----|-----|------|---------------|--------------------|------|-------|

| LQFP<br>Pin # | Pin<br>Name   | Signal Name                | GPIO       | I2C | SCI | SPI | ADC | PWM  | Quad<br>Timer | Power &<br>Ground  | JTAG | Misc. |

| 25            | VDD_IO        | V <sub>DD_IO</sub>         |            |     |     |     |     |      |               | V <sub>DD_IO</sub> |      |       |

| 26            | VSS_IO        | V <sub>SS_IO</sub>         |            |     |     |     |     |      |               | V <sub>SS_IO</sub> |      |       |

| 27            | GPIOA1        | GPIOA1, PWM1               | A1         |     |     |     |     | PWM1 |               |                    |      |       |

| 28            | <b>GPIOA0</b> | GPIOA0, PWM0               | <b>A</b> 0 |     |     |     |     | PWM0 |               |                    |      |       |

| 29            | TDI           | TDI, GPIOD0                | D0         |     |     |     |     |      |               |                    | TDI  |       |

| 30            | TMS           | TMS, GPIOD3                | D3         |     |     |     |     |      |               |                    | TMS  |       |

| 31            | TDO           | TDO, GPIOD1                | D1         |     |     |     |     |      |               |                    | TDO  |       |

| 32            | GPIOB6        | GPIOB6, RXD,<br>SDA, CLKIN | B6         | SDA | RXD |     |     |      |               |                    |      | CLKIN |

#### Table 2-2 56F8014 Pins (Continued)

Figure 2-1 56F8014 Signals Identified by Functional Group (32-Pin LQFP)

#### 2.2 56F8014 Signal Pins

After reset, each pin is configured for its primary function (listed first). Any alternate functionality must be programmed.

| Signal<br>Name      | LQFP<br>Pin No. | Туре             | State During<br>Reset             | Signal Description                                                                                                                                                                                    |

|---------------------|-----------------|------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD_IO</sub>  | 25              | Supply           | Supply                            | I/O Power — This pin supplies 3.3V power to the chip I/O interface.                                                                                                                                   |

| V <sub>SS_IO</sub>  | 14              | Supply           | Supply                            | ${f V}_{SS}$ — These pins provide ground for chip logic and I/O drivers.                                                                                                                              |

| V <sub>SS_IO</sub>  | 26              |                  |                                   |                                                                                                                                                                                                       |

| V <sub>DDA</sub>    | 8               | Supply           | Supply                            | <b>ADC Power</b> — This pin supplies 3.3V power to the ADC modules. It must be connected to a clean analog power supply.                                                                              |

| V <sub>SSA</sub>    | 9               | Supply           | Supply                            | <b>ADC Analog Ground</b> — This pin supplies an analog ground to the ADC modules.                                                                                                                     |

| V <sub>CAP</sub>    | 24              | Supply           | Supply                            | $V_{CAP}$ — Connect a 2.2 $\mu$ F or greater bypass capacitor between this pin and VSS_IO, which is required by the internal voltage regulator for proper chip operation. See Section 10.2.1.         |

| GPIOB6              | 32              | Input/<br>Output | Input with<br>internal<br>pull-up | <b>Port B GPIO</b> — This GPIO pin can be individually programmed as an input or output pin.                                                                                                          |

| (RXD)               |                 | Input            | enabled                           | Receive Data — SCI receive data input.                                                                                                                                                                |

| (SDA <sup>1</sup> ) |                 | Input/<br>Output |                                   | Serial Data — This pin serves as the $I^2C$ serial data line.                                                                                                                                         |

| (CLKIN)             |                 | Input            |                                   | <b>Clock Input</b> — This pin serves as an optional external clock input.                                                                                                                             |

|                     |                 |                  |                                   | After reset, the default state is GPIOB6. The alternative peripheral functionality is controlled via the SIM (See <b>Section 6.3.8</b> ) and the CLKMODE bit of the OCCS Oscillator Control Register. |

| 1. This signal      | is also bro     | ought out on     | the GPIOB1 pin                    |                                                                                                                                                                                                       |

Table 2-3 56F8014 Signal and Package Information for the 32-Pin LQFP

#### Table 2-3 56F8014 Signal and Package Information for the 32-Pin LQFP (Continued)

| Signal<br>Name      | LQFP<br>Pin No. | Туре                          | State During<br>Reset                        | Signal Description                                                                                                                                                                                                                                                                                                                          |

|---------------------|-----------------|-------------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIOB7              | 2               | Input/<br>Output              | Input with<br>internal<br>pull-up            | <b>Port B GPIO</b> — This GPIO pin can be individually programmed as an input or output pin.                                                                                                                                                                                                                                                |

| (TXD)               |                 | Input/<br>Output              | enabled                                      | <b>Transmit Data</b> — SCI transmit data output or transmit / receive in single wire opeation.                                                                                                                                                                                                                                              |

| (SCL <sup>2</sup> ) |                 | Input/<br>Output              |                                              | Serial Clock — This pin serves as the I <sup>2</sup> C serial clock.                                                                                                                                                                                                                                                                        |

|                     |                 |                               |                                              | After reset, the default state is GPIOB7. The alternative peripheral functionality is controlled via the SIM. See <b>Section 6.3.8</b> .                                                                                                                                                                                                    |

| 2. This signal      | is also br      | ought out on                  | the GPIOB0 pin                               |                                                                                                                                                                                                                                                                                                                                             |

| RESET               | 16              | Input                         | Input with<br>internal<br>pull-up<br>enabled | <b>Reset</b> — This input is a direct hardware reset on the processor.<br>When RESET is asserted low, the chip is initialized and placed in the reset state. A Schmitt trigger input is used for noise immunity. The internal reset signal will be deasserted synchronous with the internal clocks after a fixed number of internal clocks. |

| (GPIOA7)            |                 | Input/Open<br>Drain<br>Output |                                              | <b>Port A GPIO</b> — This GPIO pin can be individually programmed as an input or open drain output pin. Note that RESET functionality is disabled in this mode and the chip can only be reset via POR, COP reset, or software reset.                                                                                                        |

|                     |                 |                               |                                              | After reset, the default state is RESET.                                                                                                                                                                                                                                                                                                    |

| GPIOB4              | 19              | Input/<br>Output              | Input with<br>internal<br>pull-up<br>enabled | <b>Port B GPIO</b> — This GPIO pin can be individually programmed as an input or output pin.                                                                                                                                                                                                                                                |

| (T0)                |                 | Input/<br>Output              | enabled                                      | <b>T0</b> — Timer, Channel 0                                                                                                                                                                                                                                                                                                                |

| (CLKO)              |                 | Output                        |                                              | <b>Clock Output</b> — This is a buffered clock signal. Using the SIM_CLKO Select Register (SIM_CLKOSR), this pin can be programmed as any of the following: disabled (logic 0), CLK_MSTR (system clock), IPBus clock, or oscillator output. See Section 6.3.7.<br>After reset, the default state is GPIOB4. The alternative peripheral      |

|                     |                 |                               |                                              | functionality is controlled via the SIM. See Section 6.3.8.                                                                                                                                                                                                                                                                                 |

#### Table 2-3 56F8014 Signal and Package Information for the 32-Pin LQFP (Continued)

| Signal<br>Name | LQFP<br>Pin No. | Туре             | State During<br>Reset                        | Signal Description                                                                                                                                                                                                                                     |

|----------------|-----------------|------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIOB5         | 3               | Input/<br>Output | Input with<br>internal<br>pull-up<br>enabled | <b>Port B GPIO</b> — This GPIO pin can be individually programmed as an input or output pin.                                                                                                                                                           |

| (T1)           |                 | Input/<br>Output | enabled                                      | <b>T1</b> — Timer, Channel 1                                                                                                                                                                                                                           |

| (FAULT3)       |                 | Input            |                                              | <b>FAULT3</b> — This fault input pin is used for disabling selected PWM outputs in cases where fault conditions originate off-chip.                                                                                                                    |

|                |                 |                  |                                              | After reset, the default state is GPIOB5. The alternative peripheral functionality is controlled via the SIM. See <b>Section 6.3.8</b> .                                                                                                               |

| тск            | 15              | Input            | Input with<br>internal<br>pull-up<br>enabled | <b>Test Clock Input</b> — This input pin provides a gated clock to synchronize the test logic and shift serial data to the JTAG/EOnCE port. The pin is connected internally to a pull-up resistor. A Schmitt trigger input is used for noise immunity. |

| (GPIOD2)       |                 | Input/<br>Output |                                              | <b>Port D GPIO</b> — This GPIO pin can be individually programmed as an input or output pin.                                                                                                                                                           |

|                |                 |                  |                                              | After reset, the default state is TCK.                                                                                                                                                                                                                 |

| TMS            | 30              | Input            | Input with<br>internal<br>pull-up            | <b>Test Mode Select Input</b> — This input pin is used to sequence the JTAG TAP controller's state machine. It is sampled on the rising edge of TCK and has an on-chip pull-up resistor.                                                               |

| (GPIOD3)       |                 | Input/<br>Output | enabled                                      | <b>Port D GPIO</b> — This GPIO pin can be individually programmed as an input or output pin.                                                                                                                                                           |

|                |                 |                  |                                              | After reset, the default state is TMS.                                                                                                                                                                                                                 |

|                |                 |                  |                                              | <b>Note:</b> Always tie the TMS pin to $V_{DD}$ through a 2.2K resistor if this pin is configured as TMS.                                                                                                                                              |

| TDI            | 29              | Input            | Input with<br>internal<br>pull-up<br>enabled | <b>Test Data Input</b> — This input pin provides a serial input data stream to the JTAG/EOnCE port. It is sampled on the rising edge of TCK and has an on-chip pull-up resistor.                                                                       |

| (GPIOD0)       |                 | Input/<br>Output |                                              | <b>Port D GPIO</b> — This GPIO pin can be individually programmed as an input or output pin.                                                                                                                                                           |

|                |                 |                  |                                              | After reset, the default state is TDI.                                                                                                                                                                                                                 |

#### Table 2-3 56F8014 Signal and Package Information for the 32-Pin LQFP (Continued)

| Signal<br>Name                                        | LQFP<br>Pin No. | Туре             | State During<br>Reset                        | Signal Description                                                                                                                                                                                                          |  |

|-------------------------------------------------------|-----------------|------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| TDO                                                   | 31              | Output           | Output                                       | <b>Test Data Output</b> — This tri-stateable output pin provides a serial output data stream from the JTAG/EOnCE port. It is driven in the shift-IR and shift-DR controller states, and changes on the falling edge of TCK. |  |

| (GPIOD1)                                              |                 | Input/<br>Output |                                              | <b>Port D GPIO</b> — This GPIO pin can be individually programmed as an input or output pin.                                                                                                                                |  |

|                                                       |                 |                  |                                              | After reset, the default state is TDO.                                                                                                                                                                                      |  |

| GPIOB0                                                | 21              | Input/<br>Output | Input with<br>internal<br>pull-up            | <b>Port B GPIO</b> — This GPIO pin can be individually programmed as an input or output pin.                                                                                                                                |  |

| (SCLK)                                                |                 | Input/<br>Output | enabled                                      | <b>SPI Serial Clock</b> — In the master mode, this pin serves as an output, clocking slaved listeners. In slave mode, this pin serves as the data clock input. A Schmitt trigger input is used for noise immunity.          |  |

| (SCL <sup>3</sup> )                                   |                 | Input/<br>Output |                                              | Serial Data — This pin serves as the I <sup>2</sup> C serial clock.                                                                                                                                                         |  |

|                                                       |                 |                  |                                              | After reset, the default state is GPIOB0. The alternative peripheral functionality is controlled via the SIM. See <b>Section 6.3.8</b> .                                                                                    |  |

| 3. This signal is also brought out on the GPIOB7 pin. |                 |                  |                                              |                                                                                                                                                                                                                             |  |

| GPIOB1                                                | 1               | Input/<br>Output | Input with<br>internal<br>pull-up<br>enabled | <b>Port B GPIO</b> — This GPIO pin can be individually programmed as an input or output pin.                                                                                                                                |  |

| ( <mark>SS</mark> )                                   |                 | Input            | enabled                                      | SPI Slave Select — $\overline{SS}$ is used in slave mode to indicate to the SPI module that the current transfer is to be received.                                                                                         |  |

| (SDA <sup>4</sup> )                                   |                 | Input/<br>Output |                                              | Serial Clock — This pin serves as the I <sup>2</sup> C serial data line.                                                                                                                                                    |  |

|                                                       |                 | •                |                                              | After reset, the default state is GPIOB1. The alternative peripheral functionality is controlled via the SIM. See <b>Section 6.3.8</b> .                                                                                    |  |

| 4. This signal is also brought out on the GPIOB6 pin. |                 |                  |                                              |                                                                                                                                                                                                                             |  |

#### Table 2-3 56F8014 Signal and Package Information for the 32-Pin LQFP (Continued)

| Signal<br>Name     | LQFP<br>Pin No.                                       | Туре             | State During<br>Reset                        | Signal Description                                                                                                                                                                                                                                                                                                                                            |  |  |

|--------------------|-------------------------------------------------------|------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                    |                                                       |                  |                                              |                                                                                                                                                                                                                                                                                                                                                               |  |  |

| GPIOB2             | 18                                                    | Input/<br>Output | Input with<br>internal<br>pull-up<br>enabled | <b>Port B GPIO</b> — This GPIO pin can be individually programmed as an input or output pin.                                                                                                                                                                                                                                                                  |  |  |

| (MISO)             |                                                       | Input/<br>Output |                                              | <b>SPI Master In/Slave Out</b> — This serial data pin is an input to a master device and an output from a slave device. The MISO line of a slave device is placed in the high-impedance state if the slave device is not selected. The slave device places data on the MISO line a half-cycle before the clock edge the master device uses to latch the data. |  |  |

| (T2 <sup>5</sup> ) |                                                       | Input/<br>Output |                                              | <b>T2</b> — Timer, Channel 2                                                                                                                                                                                                                                                                                                                                  |  |  |

|                    |                                                       | Calpar           |                                              | After reset, the default state is GPIOB2. The alternative peripheral functionality is controlled via the SIM. See <b>Section 6.3.8</b> .                                                                                                                                                                                                                      |  |  |

| 5. This signal     | 5. This signal is also brought out on the GPIOA4 pin. |                  |                                              |                                                                                                                                                                                                                                                                                                                                                               |  |  |

| GPIOB3             | 17                                                    | Input/<br>Output | Input with<br>internal<br>pull-up<br>enabled | <b>Port B GPIO</b> — This GPIO pin can be individually programmed as an input or output pin.                                                                                                                                                                                                                                                                  |  |  |

| (MOSI)             |                                                       | Input/<br>Output | chabled                                      | <b>SPI Master Out/Slave In</b> — This serial data pin is an output from a master device and an input to a slave device. The master device places data on the MOSI line a half-cycle before the clock edge the slave device uses to latch the data.                                                                                                            |  |  |

| (T3 <sup>6</sup> ) |                                                       | Input/<br>Output |                                              | <b>T3</b> — Timer, Channel 3                                                                                                                                                                                                                                                                                                                                  |  |  |

|                    |                                                       | Output           |                                              | After reset, the default state is GPIOB3. The alternative peripheral functionality is controlled via the SIM. See <b>Section 6.3.8</b> .                                                                                                                                                                                                                      |  |  |

| 6. This signal     | 6. This signal is also brought out on the GPIOA5 pin. |                  |                                              |                                                                                                                                                                                                                                                                                                                                                               |  |  |

| GPIOA0             | 28                                                    | Input/<br>Output | Input with<br>internal<br>pull-up            | <b>Port A GPIO</b> — This GPIO pin can be individually programmed as an input or output pin.                                                                                                                                                                                                                                                                  |  |  |

| (PWM0)             |                                                       | Output           | enabled                                      | <b>PWM0</b> — This is one of the six PWM output pins.                                                                                                                                                                                                                                                                                                         |  |  |

|                    |                                                       |                  |                                              | After reset, the default state is GPIOA0.                                                                                                                                                                                                                                                                                                                     |  |  |

#### Table 2-3 56F8014 Signal and Package Information for the 32-Pin LQFP (Continued)

| Signal<br>Name                                        | LQFP<br>Pin No. | Туре             | State During<br>Reset                        | Signal Description                                                                                                                       |  |  |

|-------------------------------------------------------|-----------------|------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| GPIOA1                                                | 27              | Input/<br>Output | Input with<br>internal<br>pull-up            | <b>Port A GPIO</b> — This GPIO pin can be individually programmed as an input or output pin.                                             |  |  |

| (PWM1)                                                |                 | Output           | enabled                                      | <b>PWM1</b> — This is one of the six PWM output pins.<br>After reset, the default state is GPIOA1.                                       |  |  |

|                                                       |                 |                  |                                              |                                                                                                                                          |  |  |

| GPIOA2                                                | 23              | Input/<br>Output | Input with<br>internal<br>pull-up            | <b>Port A GPIO</b> — This GPIO pin can be individually programmed as an input or output pin.                                             |  |  |

| (PWM2)                                                |                 | Output           | enabled                                      | <b>PWM2</b> — This is one of the six PWM output pins.                                                                                    |  |  |

|                                                       |                 |                  |                                              | After reset, the default state is GPIOA2.                                                                                                |  |  |

| GPIOA4                                                | 22              | Input/<br>Output | Input with<br>internal<br>pull-up<br>enabled | <b>Port A GPIO</b> — This GPIO pin can be individually programmed as an input or output pin.                                             |  |  |

| (PWM4)                                                |                 | Output           | enabled                                      | <b>PWM4</b> — This is one of the six PWM output pins.                                                                                    |  |  |