# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## AS3701 Micro-PMIC

## **General Description**

The AS3701 is a small compact PMU for small size and low power applications.

AS3701 features one 500mA DCDC buck converter operating from 1MHz up to 4MHz, two 200mA LDOs, two 40mA current sinks and offers additional GPIO functions. Further, the device contains an integrated linear battery charger with constant current and constant voltage operation. The wide charging current range going from 11mA up to 500mA and the integrated battery temperature monitoring with selectable NTC beta values make this device suitable for a great variety of applications.

The single supply voltage may vary from 2.7V to 5.5V and all functionalities of AS3701 can be controlled via the l<sup>2</sup>C interface.

Ordering Information and Content Guide appear at end of datasheet.

## **Key Benefits & Features**

The benefits and features of AS3701, Micro-PMIC are listed below:

Figure 1: Added Value of Using AS3701

| Benefits                                                                                                                                       | Features                                                                                                                                                                                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| • Multiple rails in a compact design for low power applications                                                                                | <ul> <li>2 x 200mA universal LDO (1.2V to 3.3V)</li> <li>500mA Step-down DCDC (0.6125V to 3.35V)</li> <li>2 programmable current sources up to 40mA</li> <li>Possible external PWM dimming input</li> </ul>                                                          |

| • Self-contained Li-lon battery charger with power path                                                                                        | <ul> <li>Linear charger with internal transistor</li> <li>500mA max charging current</li> <li>Trickle-, Constant Current and Constant Voltage operation (3.82V to 4.44V)</li> <li>Charger timeout and temperature supervision</li> <li>NTC beta selection</li> </ul> |

| <ul> <li>Flexible multi-purpose IOs for general control<br/>tasks and for standalone operation without<br/>I<sup>2</sup>C interface</li> </ul> | <ul> <li>Wake-up / Stand-by / Power-down input</li> <li>PWM input/output</li> <li>Interrupt input/output</li> <li>Low battery and Power Good output</li> <li>Charging and USB current setting input</li> <li>Charger control input/output</li> </ul>                 |

| Benefits                                                                        | Features                                                                                                                        |

|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Flexible and fast adaption to different processors/applications                 | OTP programmable Boot sequence                                                                                                  |

| <ul> <li>Power saving control according to the<br/>processor's needs</li> </ul> | Stand-by function with programmable voltages                                                                                    |

| Self-contained start-up and safety shutdown feature                             | <ul> <li>I<sup>2</sup>C control interface</li> <li>ON-key with 4/8s emergency power-down</li> <li>POR with Reset I/O</li> </ul> |

| Cost effective, small package optimized for<br>PCB cost or size                 | <ul> <li>17-balls WL-CSP with 0.4mm pitch</li> <li>20-balls WL-CSP with 0.4mm pitch</li> </ul>                                  |

## Applications

The device is a PMU for low power applications like sport watches, smart watches, handheld GPS devices, mobile phones and any other 1-cell Li+ powered devices.

## **Block Diagram**

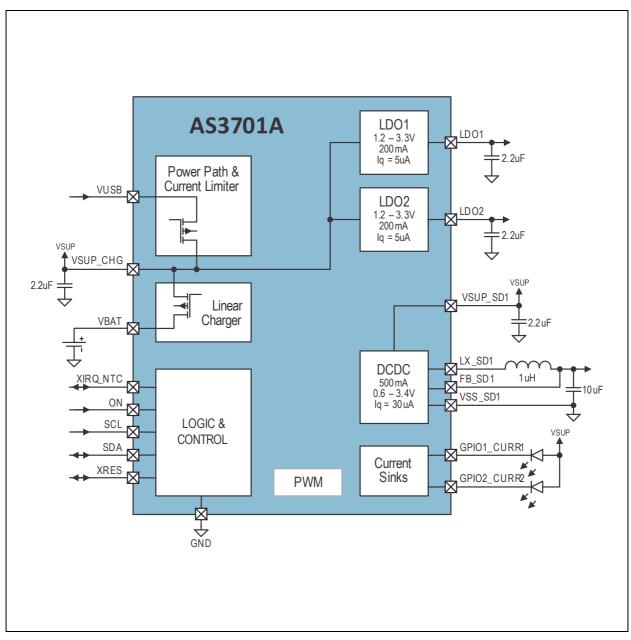

The functional blocks of this device are shown below:

Block Diagram: This figure shows the block diagram of the AS3701A

## Figure 3:

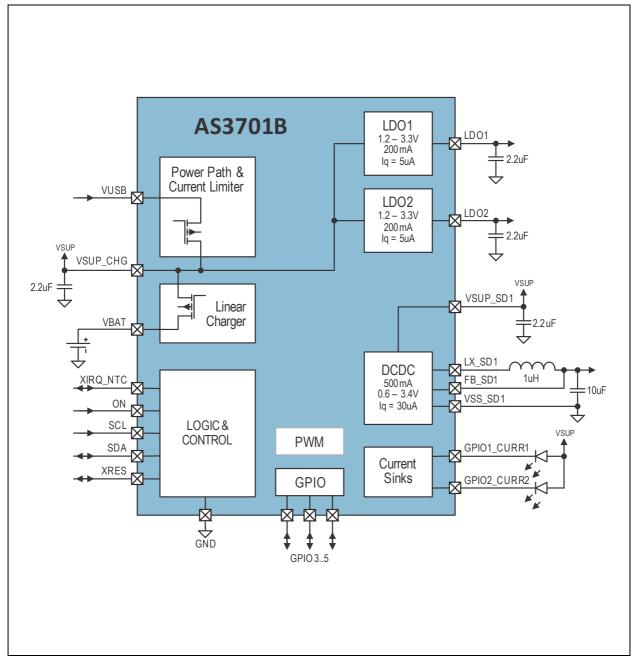

Functional Blocks of AS3701B

Block Diagram: This figure shows the block diagram of the AS3701B

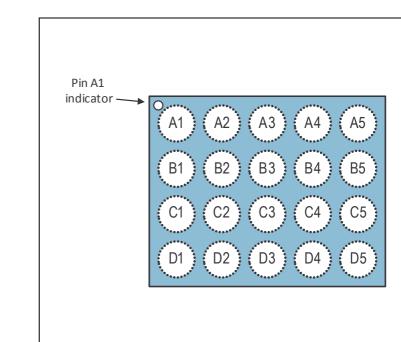

**Pin Assignments:** Shows the top view pin assignment of the AS3701A

Figure 4: 17-balls WL-CSP Pin Assignment for AS3701A

Pin A1 indicator - $\square$ A1 A2 A3 A4 A5 B2 B3 B5 **B**1 C4 C5 C1 D2 **D**3 D1 D4 D5 -

Figure 5: 20-balls WL-CSP Pin Assignment for AS3701B

**Pin Assignments:** Shows the top view pin assignment of the AS3701B

Figure 6: Pin Description

| Pin N       | umber       | Pin             |     |                                                             | Max.    | If Not              |

|-------------|-------------|-----------------|-----|-------------------------------------------------------------|---------|---------------------|

| 17<br>Balls | 20<br>Balls | Name            | I/O | Description                                                 | Voltage | Used                |

| A2          | A2          | VUSB            | S   | Wall adapter or USB Bus Power input<br>(before protection)  | 5.5V    | pull-down to<br>GND |

| A1          | A1          | VSUP_CHG        | SIO | Current limiter output,<br>LDO1 & LDO2 pos. supply terminal | VSUP    | Mandatory           |

| D2          | D2          | VSUP_SD1        | S   | DCDC pos. supply terminal                                   | VSUP    | Mandatory           |

| B1          | B1          | VBAT            | S   | Li-Ion Battery Terminal                                     | 5.5V    | Open                |

| A5          | A5          | GND             | AIO | Reference GND                                               | -       | Mandatory           |

| A4          | A4          | LDO1            | AO  | LDO1 Output                                                 | 3.3V    | Open                |

| A3          | A3          | LDO2            | AO  | LDO2 Output                                                 | 3.3V    | Open                |

| D1          | D1          | LX_SD1          | AIO | DCDC Step Down Switch Output to 5.5V                        |         | Open                |

| B2          | B2          | FB_SD1          | AI  | DCDC Step Down Feedback Pin                                 | 3.6V    | Open                |

| D4          | D4          | XRES            | DIO | Reset IO                                                    | VSUP    | Open                |

| D3          | D3          | ON              | DI  | Power Up Input                                              | 5.5V    | Open                |

| B3          | B3          | XIRQ_NTC        | AIO | Interrupt Output or NTC Input                               | VSUP    | Open                |

| D5          | D5          | SCL             | DI  | 2-wire Serial IF Clock Input                                | VSUP    | pull-up to<br>VSUP  |

| C4          | C4          | SDA             | DIO | 2-wire Serial IF Data I/O                                   | VSUP    | pull-up to<br>VSUP  |

| C5          | C5          | GPIO1_<br>CURR1 | DIO | General Purpose IO1 or LED Channel 1                        | VSUP    | Open                |

| B5          | B5          | GPIO2_<br>CURR2 | DIO | General Purpose IO2 or LED Channel 2                        | VSUP    | Open                |

| -           | B4          | GPIO3           | DIO | General Purpose IO3                                         | VSUP    | Open                |

| -           | C2          | GPIO4           | DIO | General Purpose IO4                                         | VSUP    | Open                |

| -           | C3          | GPIO5           | DIO | General Purpose IO5                                         | VSUP    | Open                |

| C1          | C1          | VSS_SD1         | AIO | GND connector of DCDC                                       | -       | Mandatory           |

## Absolute Maximum Ratings

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under Electrical Characteristics is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### Figure 7: Absolute Maximum Ratings

| Symbol             | Parameter                                     | Min          | Max      | Units                 | Comments                                                                                                                                                |    |  |    |                    |

|--------------------|-----------------------------------------------|--------------|----------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|----|--------------------|

|                    | Elec                                          | trical Pa    | rameter  | s                     |                                                                                                                                                         |    |  |    |                    |

| V <sub>GND</sub>   | Supply voltage to ground 5V pins              | -0.5         | 7.0      | V                     | Applicable for pins<br>VSUP_CHG, VSUP_SD1, VBAT,<br>VUSB, LX_SD1, SCL, SDA, ON,<br>XRES, XIRQ_NTC, GPIO3, GPIO4,<br>GPIO5, GPIO1_CURR1, GPIO2_<br>CURR2 |    |  |    |                    |

| V <sub>GND</sub>   | Supply voltage to ground 3V pins              | -0.5         | 5.0      | V                     | Applicable for pins<br>LDO1, LDO2, FB_SD1                                                                                                               |    |  |    |                    |

|                    | Voltage difference between ground terminals   | -0.5         | 0.5      | V                     | Applicable for pins<br>GND, VSS_SD1                                                                                                                     |    |  |    |                    |

| I <sub>SCR</sub>   | Input current<br>(latch-up immunity)          | -100         | 100      | mA                    | JEDEC JESD78                                                                                                                                            |    |  |    |                    |

|                    | Continuous Po                                 | wer Dis      | sipation | (T <sub>A</sub> = 70° | C)                                                                                                                                                      |    |  |    |                    |

| P <sub>T</sub>     | Continuous power dissipation                  | ation 0.96 W |          | W                     | $P_T^{(1)}$ for WL-CSP20<br>( $R_{THJA} \sim 57K/W$ )                                                                                                   |    |  |    |                    |

|                    | Electrostatic Discharge                       |              |          |                       |                                                                                                                                                         |    |  |    |                    |

| ESD <sub>HBM</sub> | Electrostatic discharge<br>(human body model) | ±2           |          | ±2                    |                                                                                                                                                         | ±2 |  | kV | JEDEC JESD22-A114F |

| Symbol            | Parameter                              | Min      | Max      | Units     | Comments                                |

|-------------------|----------------------------------------|----------|----------|-----------|-----------------------------------------|

|                   | Temperature Rai                        | nges and | d Storag | e Conditi | ons                                     |

| T <sub>A</sub>    | Operating temperature                  | -40      | 85       | °C        |                                         |

| R <sub>THJA</sub> | Junction to ambient thermal resistance |          |          | °C/W      | R <sub>THJA</sub> typ. 57K/W            |

| Τj                | Junction temperature                   |          | 125      | °C        |                                         |

| T <sub>STRG</sub> | Storage temperature range              | -55      | 125      | °C        |                                         |

| T <sub>BODY</sub> | Package body temperature               |          | 260      | °C        | IPC/JEDEC J-STD-020 <sup>(2)</sup>      |

| RH <sub>NC</sub>  | Relative humidity<br>(non-condensing)  | 5        | 85       | %         |                                         |

| MSL               | Moisture sensitivity level             |          | 1        |           | Represents an unlimited floor life time |

#### Note(s):

1. Depending on actual PCB layout and PCB used

2. The reflow peak soldering temperature (body temperature) is specified according IPC/JEDEC J-STD-020 "Moisture/Reflow Sensitivity Classification for Non hermetic Solid State Surface Mount Devices"

## **Electrical Characteristics**

All limits are guaranteed. The parameters with min and max values are guaranteed with production tests or SQC (Statistical Quality Control) methods.

Figure 8: Electrical Characteristics

| Symbol                | Parameter                                    | Conditions                                  | Min  | Тур | Мах | Unit |

|-----------------------|----------------------------------------------|---------------------------------------------|------|-----|-----|------|

| V <sub>IN</sub>       | Input voltage range                          | Pin VSUP                                    | 2.7  |     | 5.5 | V    |

| I <sub>Q_ACTIVE</sub> | Active mode<br>quiescent current             | Normal operating current                    |      | 26  |     |      |

|                       | Stand-by                                     | Normal operating current<br>(Oscillator ON) |      | 26  |     |      |

| quiescent current     | Normal operating current<br>(Oscillator OFF) |                                             | 11.5 |     | uA  |      |

| IPOWEROFF             | Shutdown current                             | power_off = 1                               |      | 1.2 |     |      |

**Electrical Characteristics:**  $V_{SUP} = 3.7V$ ,  $V_{OUT} < V_{IN} - 0.5V$ ,  $T_{AMB} = -40^{\circ}C$  to  $85^{\circ}C$ , typ. values @  $T_{AMB} = 25^{\circ}C$  (unless otherwise specified)

## Detailed Description – Power Management Functions

## **Step Down Converter**

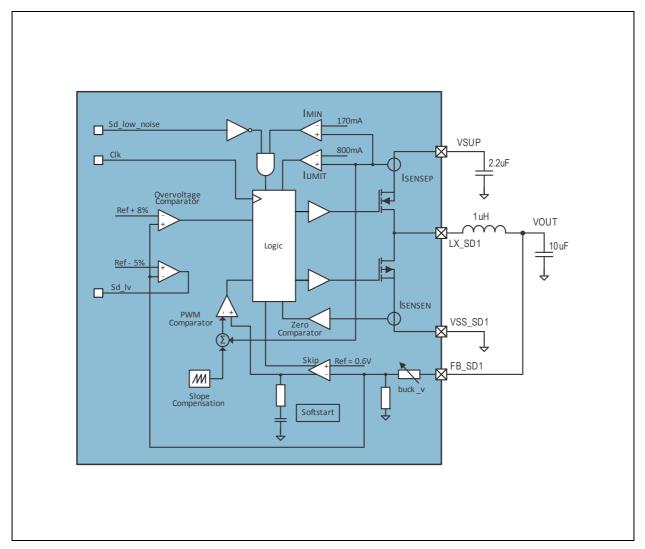

The step-down converter is a high-efficiency fixed frequency current mode regulator. By using low resistance internal PMOS and NMOS switches, efficiency up to 95% can be achieved. The fast switching frequency allows using small inductors, without increasing the current ripple. The unique feedback and regulation circuit guarantees optimum load and line regulation over the whole output voltage range, up to the maximum output current, with an output capacitor of only 10µF. The implemented current limitation protects the DCDC Converter and the coil during overload condition.

## Figure 9: DCDC Step-Down Converter Block Diagram

## Mode Settings

To allow optimized performance in different applications, there are bit settings possible, to get the best compromise between high efficiency and low input/output ripple.

Figure 10: DCDC Step-Down Converter Mode Settings

100 3 90 5 80 Efficiency (%) Δ 70 60 ---- Vout = 2.5V, low noise 50 Vout = 2.5V 40 0.001 0.01 0.1 1 Output Current (A)

**Mode Setting:** This graph shows the difference of the efficiency curves for high efficiency and low noise mode setting.  $V_{SUP} = 3.7V$ ,  $V_{OUT} = 2.5V$ ,  $f_{SW} = 3MHz$ ,  $T_{AMB} = 25^{\circ}C$ .

#### Low-Ripple, Low-Noise Operation

Low-ripple, low-noise operation can be enabled by setting the bit *sd\_low\_noise* [*SD\_control1*] to 1.

In this mode there is no minimum coil current necessary before switching OFF the PMOS. As long as the load current is superior to the ripple current, the device operates in continuous mode. When the load current gets lower, the discontinuous mode is triggered. Resultant the auto-zero comparator stops the NMOS conduction to avoid load discharger and the duty cycle is reduced down to  $t_{MIN_ON}$  to keep the regulation loop stable. This results in a very low ripple and noise, but decreased efficiency at light loads, especially at low input to output voltage differences.

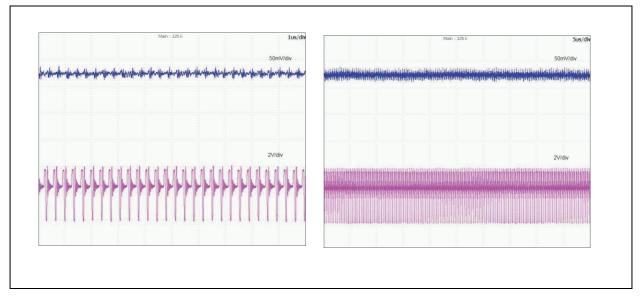

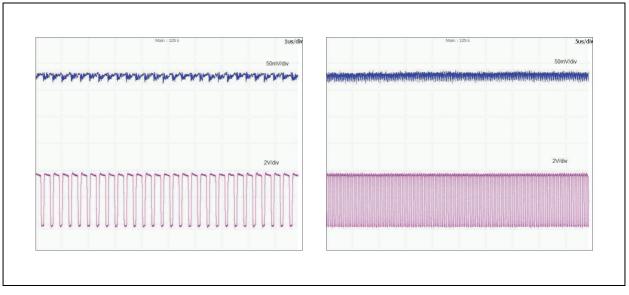

### Figure 11: Switching Behavior at Operating Point 4

**Operating Point 4:** These graphs show the switching behavior referring to the operating point 4 from figure 10. Here the mode is set to low noise/low ripple operation and the DCDC is continuously switching at 10mA load current.

Only in the case the load current gets so small, that less than the minimum on time of the PMOS would be needed to keep the loop in regulation, the regulator will enter low power mode operation.

### Figure 12: Switching Behavior at Operating Point 2

**Operating Point 2:** These graphs show the switching behavior referring to the operating point 2 from figure10. Here the mode is set to low noise/low ripple operation and the DCDC has already started to skip pulses, as the minimum PMOS ON time of 40ns has been reached and the load current is further decreasing down to 2mA.

#### High-Efficiency Operation (Default Setting)

High-efficiency operation is enabled by setting the bit sd\_low\_ noise [SD\_control1] to 0.

In this mode there is a minimum coil current necessary before switching OFF the PMOS. Resultant there are less pulses necessary at low output loads, and therefore the efficiency increases. As drawback, this mode increases the ripple up to a higher output current.

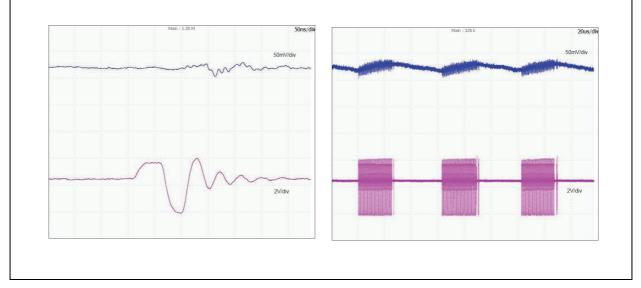

## Figure 13: Switching Behavior at Operating Point 1

**Operating Point 1:** These graphs show the switching behavior referring to the operating point 1 from figure10. Here the mode is set to high efficiency operation and the DCDC is in skipping mode at 2mA load current. Here a minimum coil current during the PMOS ON time is needed, hence more energy can be stored, the duration between the bursts is longer and the efficiency increases.

#### Figure 14:

#### **Output Voltage Ripple Measurement at Operating Point 3**

**Operating Point 3:** These graphs show the switching behavior referring to the operating point 3 from figure10. Here the mode is set to high efficiency operation and comparing to operating point 4 the DCDC is still in skipping mode at 10mA load current and keeps the efficiency higher.

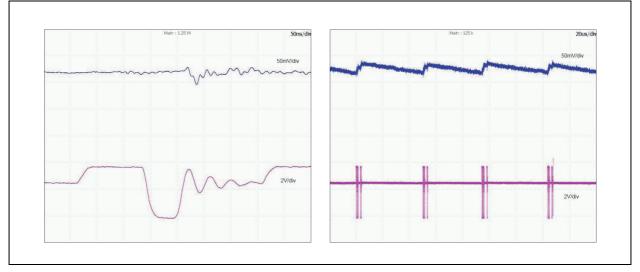

## Figure 15:

**Operating Point 5:** These graphs show the switching behavior referring to the operating point 5 from figure 10. Here the load current is 100mA and high enough to keep the DCDC always in a continuous switching operation regardless of the mode setting.

## Low Power Mode Operation (Automatically Controlled)

As soon as the output voltage stays above the desired target value for a certain time, some internal blocks will be powered down leaving the output floating to lower the power consumption. Normal operation starts as soon as the output drops below the target value for a similar amount of time. To minimize the accuracy error some internal circuits are kept powered to assure a minimized output voltage ripple.

Two addition guard bands, based on comparators, are set at  $\pm 5\%$  of the target value to react quickly on large over/undershoots by immediately turning ON the output drivers without the normal time delays. This ensures a minimized ripple also in very extreme load conditions.

## Dynamic Voltage Management

To minimize the over-/undershoot during a change of the output voltage, the DVM can be enabled with *dvm\_enable* [SD\_ control2]. With DVM the output voltage will ramp up/down with a selectable slope after the new value was written to the registers. The DVM time can be chosen between 8us and 16us by setting the bit *dvm\_time* [SD\_control2]. Without DVM the slew rate of the output voltage is only determined by external components like the coil and load capacitor as well as the load current.

#### **Fast Regulation Mode**

This mode can be used to react faster on sudden load changes and thus minimize the over-/undershoot of the output voltage. This mode needs a 22uF output capacitor instead the 10uF one to guarantee the stability of the regulator.

The mode is enabled by setting the bit *sd\_fast* [*SD\_control1*] to 1.

#### Selectable Frequency Operation

Especially for very low load conditions, e.g. during a sleep mode of a processor, the switching frequency can be reduced to achieve a higher efficiency. The frequency can be set to 1, 2, 3 or 4MHz and this mode is selected by setting *sd1\_freq* [*SD1Voltage*] and *sd1\_fsel* [*SD\_control1*] to the appropriate values.

## Parameters

Figure 16: DCDC Step-Down Converter Electrical Characteristics

| Symbol                | Parameter                | Note                              | Min    | Тур  | Max  | Unit |

|-----------------------|--------------------------|-----------------------------------|--------|------|------|------|

| V <sub>IN</sub>       | Input Voltage            | Pin VSUP                          | 2.7    |      | 5.5  | V    |

| V <sub>OUT</sub>      | Regulated Output Voltage |                                   | 0.6125 |      | 3.35 | V    |

| V <sub>OUT_TOL</sub>  | Output Voltage Tolerance | min. 40mV                         | -3     |      | +3   | %    |

| I <sub>LIMIT</sub>    | Current Limit            |                                   |        | 800  |      | mA   |

| R <sub>PMOS</sub>     | P-switch ON resistance   |                                   |        | 0.36 | 1    | Ω    |

| R <sub>NMOS</sub>     | N-switch ON resistance   |                                   |        | 0.33 | 1    | Ω    |

| f <sub>SW</sub>       | Switching Frequency      |                                   | 1      | 3    | 4    | MHz  |

| I <sub>LOAD</sub>     | Load Current             |                                   |        | 500  |      | mA   |

| I <sub>SUP_DCDC</sub> | Current Consumption      | Operating Current<br>without Load |        | 27   |      | uA   |

|                       |                          | Shutdown Current                  |        | 0.1  |      |      |

| t <sub>MIN_ON</sub>   | Minimum ON Time          |                                   |        | 40   |      | ns   |

#### Figure 17: DCDC Step-Down Converter Ext

DCDC Step-Down Converter External Components

| Symbol                | Parameter        | Note               | Min | Тур | Max | Unit |

|-----------------------|------------------|--------------------|-----|-----|-----|------|

| C <sub>FB_SD1</sub>   | Output Capacitor | Ceramic X5R or X7R | 8   | 10  |     | μF   |

| C <sub>VSUP_SD1</sub> | Input Capacitor  | Ceramic X5R or X7R |     | 2.2 |     | μF   |

|                       | Inductor         | 4MHz operation     |     | 1   |     |      |

| lose                  |                  | 3MHz operation     |     | 1   |     | μH   |

| L <sub>SD1</sub>      |                  | 2MHz operation     |     | 1   |     | μπ   |

|                       |                  | 1MHz operation     |     | 2.2 |     |      |

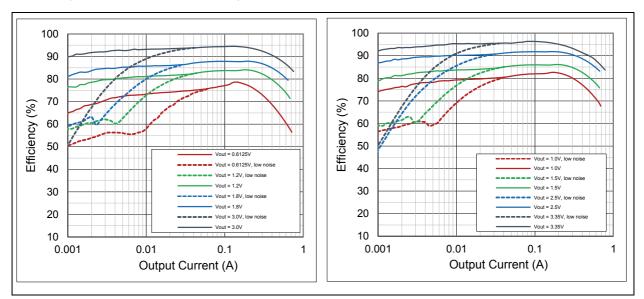

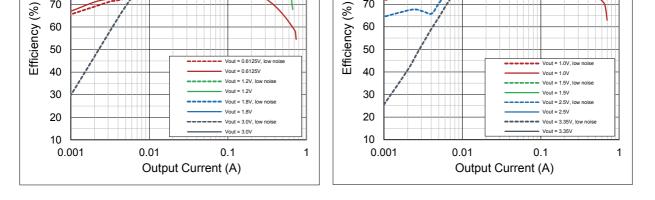

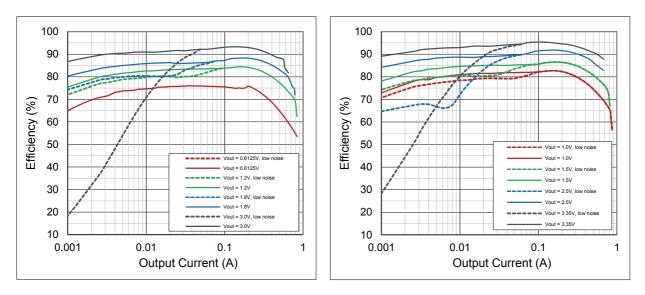

## Figure 18:

DCDC Step Down Converter Efficiency vs. Load Current at 1MHz

**DCDC Efficiency vs. Output Current:**  $V_{SUP} = 3.7V$ ,  $f_{SW} = 1$ MHz, Murata LQM2HPN2R2MG0L 2.2µH coil,  $T_{AMB} = 25^{\circ}$ C.

100

90

80

70

60

# 100 90 80 70

60

**DCDC Efficiency vs. Output Current:**  $V_{SUP} = 3.7V$ ,  $f_{SW} = 2MHz$ , Murata LQM2HPN1R0MG0L 1uH coil,  $T_{AMB} = 25^{\circ}C$ .

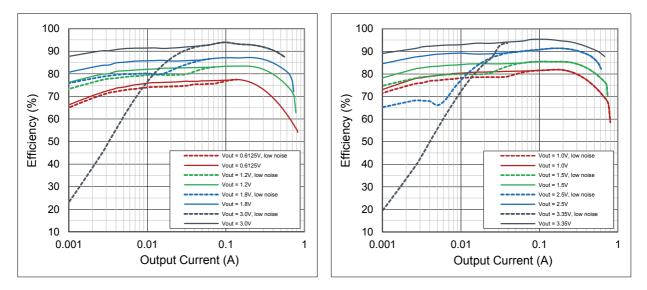

Figure 20: DCDC Step Down Converter Efficiency vs. Load Current at 3MHz

**DCDC Efficiency vs. Output Current:**  $V_{SUP} = 3.7V$ ,  $f_{SW} = 3MHz$ , Murata LQM2HPN1R0MG0L 1uH coil,  $T_{AMB} = 25^{\circ}C$ .

Figure 21: DCDC Step Down Converter Efficiency vs. Load Current at 4MHz

**DCDC Efficiency vs. Output Current:**  $V_{SUP} = 3.7V$ ,  $f_{SW} = 4MHz$ , Murata LQM2HPN1R0MG0L 1uH coil,  $T_{AMB} = 25^{\circ}C$ .

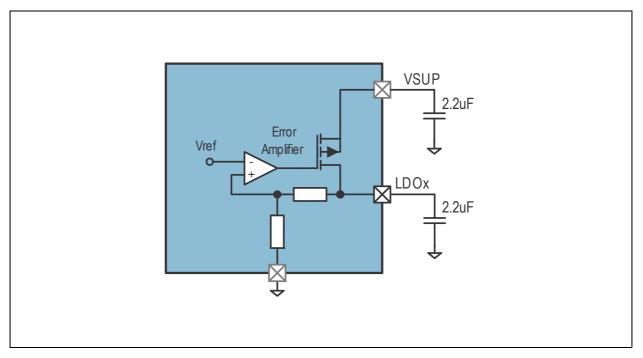

## **Universal IO LDO Regulator**

This LDO is a low-power and low-quiescent current linear-regulator specifically designed for space-limited applications. This device can supply loads up to 200mA and consist of an error amplifier, and a P-channel MOSFET pass transistor.

## Figure 22: Universal IO LDO Regulator Block Diagram

## Parameters

Figure 23: Universal IO LDO Regulator Electrical Characteristics

| Symbol                                       | Parameter                                                                 | Note                                                       | Min | Тур | Max | Unit |

|----------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------------|-----|-----|-----|------|

| V <sub>IN</sub>                              | Input voltage                                                             | Pin VSUP                                                   | 2.7 |     | 5.5 | V    |

| ΔV <sub>OUT</sub> Output voltage<br>accuracy | $I_{OUT} = 1$ mA, $V_{OUT} > 2V T_{AMB} = 25$ °C                          | -2                                                         |     | +2  |     |      |

|                                              | Output valtage                                                            | I <sub>OUT</sub> = 100uA to 200mA<br>V <sub>OUT</sub> > 2V | -3  |     | +3  | %    |

|                                              | $I_{OUT} = 1 \text{mA}, V_{OUT} \le 2V$<br>$T_{AMB} = 25^{\circ}\text{C}$ | -20                                                        |     | +20 | mV  |      |

|                                              |                                                                           | $I_{OUT} = 100$ uA to 200mA<br>$V_{OUT} \le 2V$            | -50 |     | +50 | mv   |

| V <sub>OUT</sub>                             | Output voltage range                                                      |                                                            | 1.2 |     | 3.3 | V    |

| Symbol                | Parameter                  | Note                                                                 | Min | Тур   | Max | Unit |

|-----------------------|----------------------------|----------------------------------------------------------------------|-----|-------|-----|------|

| V <sub>LNR</sub>      | Line regulation static     | $V_{IN} = 2.7V$ to 5.5V<br>$I_{OUT} = 1$ mA                          |     | 0.07  |     | %/V  |

| * LNR                 | Line regulation<br>dynamic | V <sub>IN</sub> = 2.7V to 5.5V within 15us<br>I <sub>OUT</sub> = 1mA |     | 20    |     | mV   |

|                       | Load regulation static     | I <sub>OUT</sub> = 100uA to 200mA                                    |     | 0.014 |     | %/mA |

| V <sub>LDR</sub>      | Load regulation<br>dynamic | I <sub>OUT</sub> = 100uA to 200mA within 15us                        |     | 30    |     | mV   |

| R <sub>ON</sub>       | ON resistance              |                                                                      |     | 0.5   | 1   | Ω    |

| I <sub>OUT</sub>      | Guaranteed load<br>current | RMS                                                                  | 200 |       |     | mA   |

| I <sub>LIMIT</sub>    | Short-circuit              | V <sub>OUT</sub> = 0V                                                |     | 230   |     | mA   |

|                       |                            | no Load                                                              |     | 5     |     |      |

| Ι <sub>Q</sub>        | Quiescent current          | I <sub>OUT</sub> = 100μA                                             |     | 5     |     | uA   |

|                       |                            | I <sub>OUT</sub> = 200mA                                             |     | 15    |     |      |

| I <sub>OFF</sub>      | Shutdown supply current    | LDO disabled                                                         |     | 0.1   | 1   | uA   |

| t <sub>START</sub>    | Startup time               |                                                                      |     | 750   |     | us   |

| t <sub>SHUTDOWN</sub> | Shutdown time              |                                                                      |     | 500   |     | us   |

Figure 24: Universal IO LDO Regulator External Components

| Symbol            | Parameter        | Note               | Min | Тур | Max | Unit |

|-------------------|------------------|--------------------|-----|-----|-----|------|

| C <sub>LDOx</sub> | Output capacitor | Ceramic X5R or X7R | 2.2 | 10  |     | μF   |

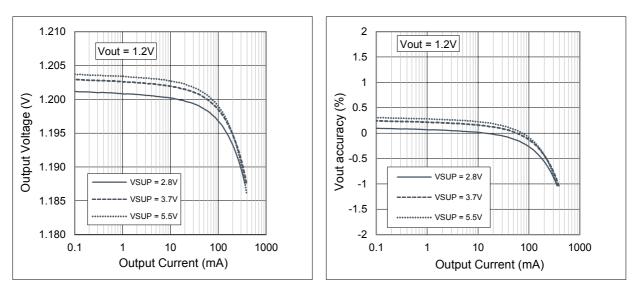

## Figure 25: LDO Output Voltage vs. Output Current 1/2

**LDO Output Voltage vs. Output Current:**  $V_{OUT} = 1.2V$ ,  $T_{AMB} = 25^{\circ}C$ .

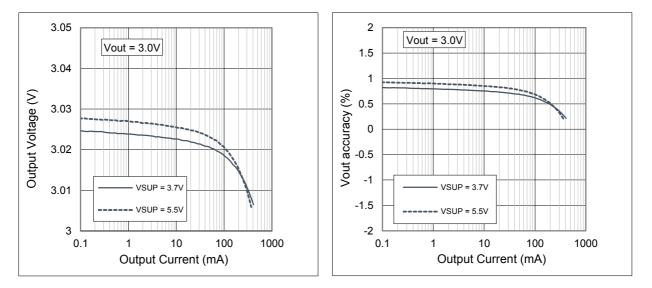

Figure 26: LDO Output Voltage vs. Output Current 2/2

**LDO Output Voltage vs. Output Current:**  $V_{OUT} = 3.0V$ ,  $T_{AMB} = 25^{\circ}C$ .

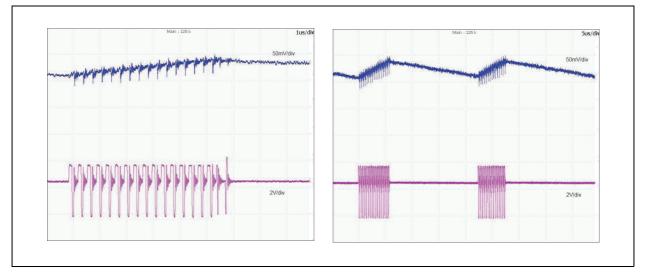

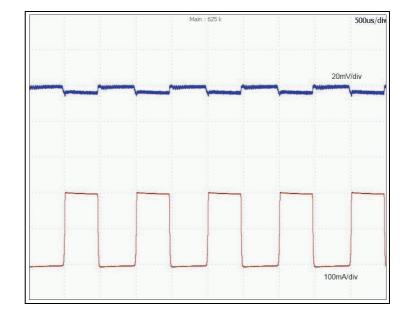

## Figure 27: LDO Load Transient Response 1/2

## LDO Load Transient Response:

$$\begin{split} V_{SUP} &= 3.7V, V_{OUT} = 1.2V, t_{RISE} = 15us, \\ I_{OUT} &= 100uA \text{ to } 200mA, T_{AMB} = 25^{\circ}\text{C}. \\ (Blue channel: V_{OUT}; Red channel: I_{OUT}) \end{split}$$

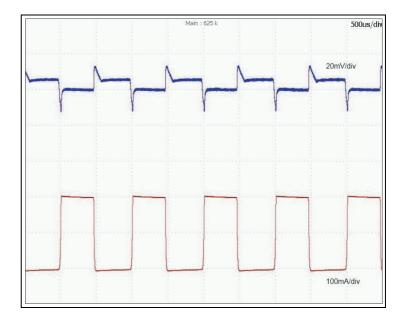

Figure 28: LDO Load Transient Response 2/2

#### LDO Load Transient Response:

$V_{SUP} = 3.7V, V_{OUT} = 3.0V, t_{RISE} = 15us,$  $I_{OUT} = 100uA to 200mA, T_{AMB} = 25^{\circ}C.$ (Blue channel:  $V_{OUT}$ ; Red channel:  $I_{OUT}$ )

## Linear Charger

This block can be used to charge Li-Ion batteries. Requiring less external components, a full-featured battery charger with a high degree of flexibility can easily be realized. The main features of the controller are:

- Charge adapter detection

- Power Path management for dead battery startup

- Low current Trickle charging

- Constant current charging

- Constant voltage charging

- Operation without battery

- Battery presence indication

- NTC temperature supervision

- Input current limitation

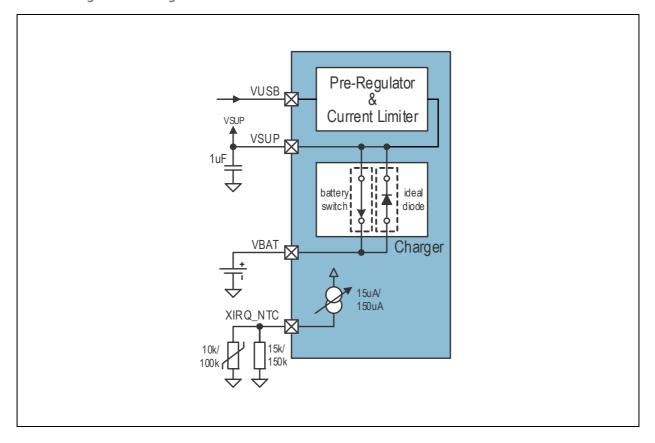

Figure 29: Linear Charger Block Diagram

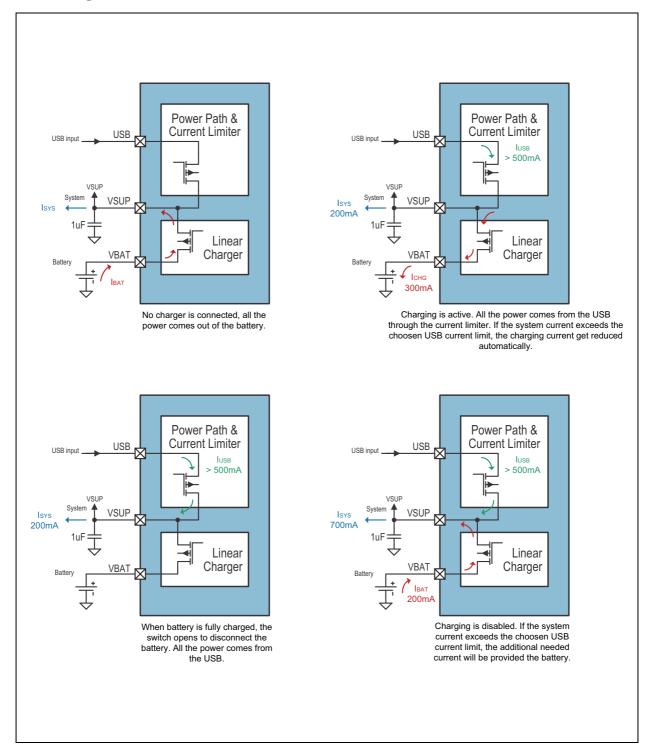

## Figure 30: Linear Charger Modes

Charging Modes: This figure describes the 4 different charger modes.

## **Charging Cycle Description**

### **Charge Adapter Detection**

The charge controller uses an integrated detection circuit to determine if an external charge adapter has been applied to the VUSB pin. If the adapter voltage exceeds the battery voltage at pin VBAT by  $V_{CHDET}$  the *ChDet [ChargerStatus2]* will be set. The detection circuit will reset the charge controller (bit *ChDet* is cleared) as soon as the voltage at the VUSB pin drops to only  $V_{CHMIN}$  above the battery voltage. In case the AS3701 device is reset the charge controller will also be reset, even if a charge adapter is applied to the VUSB pin. The Charger detection can be disabled by setting the bit *chdet\_off [ChargerStatus2]* to "1", which results in a further decrease of internal power consumption.

### Low Current (Trickle) Charging

Trickle charge mode is started when an external charge adapter has been detected, the bit *bat\_charging\_enable* [*ChargerControl*] is set and the battery voltage at pin VBAT is below the V<sub>TRICKLE</sub> threshold; bits *ChDet* and *Trickle* [*ChargerStatus1*] will be set. In this mode the charge current will be limited to TrickleCurrent [*ChargerCurrentControl*] to prevent undue stress in case of deeply discharged batteries. Once V<sub>TRICKLE</sub> has been exceeded, the charger will change over to constant current charging (Trickle is cleared).

#### **Constant Current Charging**

Constant current charging is initiated when *bat\_charging\_ enable* [*ChargerControl*] and the battery voltage at pin VBAT is above the V<sub>TRICKLE</sub> and below V<sub>CHOFF</sub>. The bit *CCM* [*ChargerStatus1*] is set when the charger has started, and the charge current will be limited by the battery charge controller. The current for the Constant Current Charging can be selected out of the range defined in *ConstantCurrent* [*ChargerCurrentControl*] if the bit *cc\_range\_select* [*ChargerControl*] is set to "0" or out of the range defined in *TrickleCurrent* [*ChargerCurrentControl*] if the bit *cc\_range\_select* [*ChargerControl*] is set to "1". When the battery approaches full charge, its voltage will reach the charge termination threshold V<sub>CHOFF</sub>. V<sub>CHOFF</sub> depends on the *ChVoltEOC*

[ChargerVoltageControl] bits settings. Top-OFF charge will be started and the bit CVM [ChargerStatus1] will be set.

#### Constant Voltage Charging

Constant voltage charge mode is initiated and the bit *CVM* [*ChargerStatus1*] will be set when the  $V_{CHOFF}$  threshold has been reached. The charge current is monitored during constant voltage charging. It will be decreasing from its initial value during constant current charging and eventually drops below 5% or 50% of the Constant Current value (depends on the