Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

AS3990/AS3991

UHF RFID Single Chip Reader EPC Class1 Gen2 Compatible

## 1 General Description

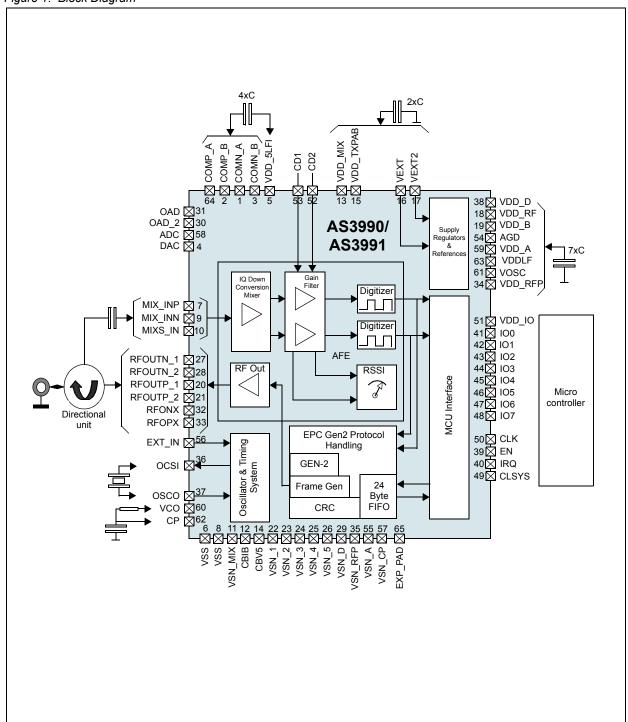

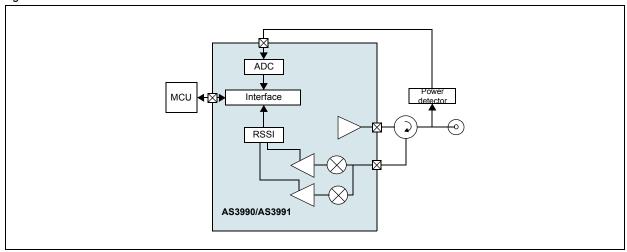

The AS3990/AS3991 UHF reader chip is an integrated analog front end and protocol handling systems for a ISO18000-6C 900MHz RFID reader system.

Equipped with built-in programming options, the device is suitable for a wide range of UHF RFID applications. The AS3990/AS3991 includes improved on-board VCO and internal PA.

The reader configuration is achieved by selecting the desired protocol in control registers. Direct access to all control registers allows fine tuning of different reader parameters.

Parallel or serial interface can be selected for communication between the host system (MCU) and the reader IC. When hardware coders and decoders are used for transmission and reception, data is transferred via 24 bytes FIFO register.

In case of direct transmission or reception, coders and decoders are bypassed and the host system can service the analog front end in real time.

The transmitter generates 20dBm output power into  $50\Omega$  load and is capable of ASK or PR-ASK modulation. The integrated supply voltage regulators ensure supply rejection of the complete reader system.

The transmission system comprises low level data coding. Automatic generation of FrameSync, Preamble, and CRC is supported.

The receiver system allows AM and PM demodulation. The receiver also comprises automatic gain control option (patent pending) and selectable gain and signal bandwidth to cover a range of input link frequency and bit rate options.

The signal strength of AM and PM modulation is measured and can be accessed in RSSI register.

The receiver output is selectable between digitized subcarrier signal and any of integrated sub-carrier decoders. Selected decoders deliver bit stream and data clock as outputs.

The receiver system also comprises framing system. This system performs the CRC check and organizes the data in bytes. Framed data is accessible to the host system through a 24 byte FIFO register.

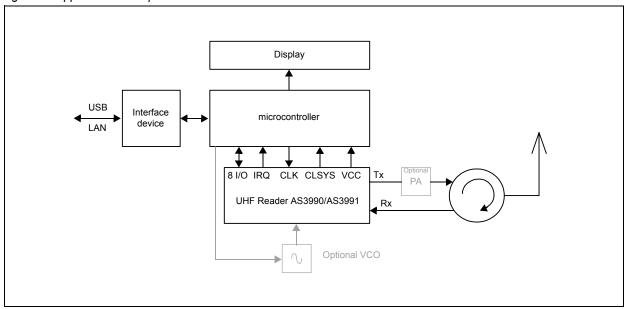

To support external MCU and other circuitry a 3.3V regulated supply and clock outputs are available. The regulated supply has 20mA current capability.

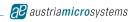

The AS3990/AS3991 is available in a 64-pin QFN (9mm x 9mm), ensuring the smallest possible footprint.

## 2 Key Features

- ISO18000-6C (EPC Gen2) full protocol support

- ISO18000-6A,B compatibility in direct mode

- Integrated low level transmission coding

- Integrated low level decoders

- Integrated data framing

- Integrated CRC checking

- Parallel 8-bit or serial 4-pin SPI interface to MCU using 24 bytes FIFO

- Voltage range for communication to MCU between 1.8V and 5.5V

- Selectable clock output for MCU

- Integrated supply voltage regulator (20mA), which can be used to supply MCU and other external circuitry

- Integrated supply voltage regulator for the RF output stage, providing rejection to supply noise

- Internal power amplifier (20dBm) for short range applications

- Modulator using ASK or PR-ASK modulation

- Adjustable ASK modulation index

- AM & PM demodulation ensuring no "communication holes" with automatic I/Q selection

- Built-in reception low-pass and high-pass filters having selectable corner frequencies

- Selectable reception gain

- Reception automatic gain control

- AD converter for measuring TX power using external RF power detector

- DA converter for controlling external power amplifier

- Frequency hopping support

- On-board VCO and PLL covering complete RFID frequency range 840MHz to 960MHz

- Oscillator using 20MHz crystal

- Power down, standby and active mode

- Can be powered by USB with no need for step conversion

## 3 Applications

The device is an ideal solution for UHF RFID reader systems and hand-held UHF RFID readers.

Figure 1. Block Diagram

### **Contents**

| 1 | General Description                                                   | 1  |

|---|-----------------------------------------------------------------------|----|

| 2 | Key Features                                                          | 1  |

| 3 | Applications                                                          | 1  |

| 4 | Pin Assignments                                                       | 5  |

|   | Pin Descriptions                                                      | 5  |

| 5 | Absolute Maximum Ratings                                              | 8  |

|   | Electrical Characteristics                                            |    |

|   | Detailed Description                                                  |    |

|   | Supply                                                                |    |

|   | Power Modes                                                           |    |

|   | Host Communication                                                    |    |

|   | VCO and PLL                                                           |    |

|   | VCO and External RF Source                                            |    |

|   | PLL                                                                   |    |

|   | Chip Status Control                                                   | 14 |

|   | Protocol Control                                                      | 14 |

|   | Option Registers Preset                                               | 14 |

|   | Transmitter                                                           | 14 |

|   | Normal Mode                                                           | 14 |

|   | Direct Mode                                                           |    |

|   | Modulator                                                             |    |

|   | Amplifier                                                             |    |

|   | Receiver                                                              |    |

|   | Input Mixer                                                           |    |

|   | RX FilterRX Gain                                                      |    |

|   | Received Signal Strength Indicator (RSSI)                             |    |

|   | Reflected RF Level Indicator                                          |    |

|   | Normal Mode                                                           |    |

|   | Direct Mode                                                           | 21 |

|   | Normal Mode With Mixer DC Level Output And Enable RX Output Available | 21 |

|   | ADC / DAC                                                             | 21 |

|   | DA Converter                                                          | 21 |

|   | AD Converter                                                          |    |

|   | Reference Oscillator                                                  |    |

| 8 | Application Information                                               | 23 |

|   | Configuration Registers Address Space                                 | 23 |

|   | Main Configuration Registers                                          |    |

|   | Control Registers - Low Level Configuration Registers                 | 25 |

|   | Status Registers                                                      |    |

|   | Test Registers                                                        |    |

|   | PLL, Modulator, DAC, and ADC Registers                                |    |

|   | RX Length Registers                                                   |    |

|   | FIFO Control Registers                                                |    |

|   | Direct Commands                                                       | 38 |

| Idle (80)                                       | 39 |

|-------------------------------------------------|----|

| Soft Init (83)                                  | 39 |

| Hop to Main Frequency (84)                      | 39 |

| Hop to Auxiliary Frequency (85)                 | 39 |

| Trigger AD Conversion (87)                      | 39 |

| Reset FIFO (8F)                                 | 39 |

| Transmission With CRC (90)                      | 39 |

| Transmission With CRC Expecting Header Bit (91) | 40 |

| Transmission Without CRC (92)                   | 40 |

| Delayed Transmission With CRC (93)              | 40 |

| Delayed Transmission Without CRC (94)           | 40 |

| Block RX (96)                                   | 40 |

| Enable RX (97)                                  | 40 |

| EPC GEN2 Specific Commands                      | 40 |

| Query (98)                                      | 40 |

| QueryRep (99)                                   | 40 |

| QueryAdjustUp (9A)                              | 40 |

| QueryAdjustNic (9B)                             | 41 |

| QueryAdjustDown (9C)                            | 41 |

| ACK (9D)                                        | 41 |

| NAK (9E)                                        | 41 |

| ReqRN (9F)                                      | 41 |

| Reader Communication Interface                  | 41 |

| Parallel Interface Communication                | 43 |

| Serial Interface Communication                  | 45 |

| Timing Diagrams                                 | 46 |

| Timing Parameters                               |    |

| FIFO                                            |    |

| 9 Package Drawings and Markings                 |    |

| 10 Ordering Information                         |    |

| TO Ordering information                         |    |

# 4 Pin Assignments

Figure 2. Pin Assignments (Top View)

### **Pin Descriptions**

Table 1. Pin Descriptions

| Pin Name | Pin Number | Pin Type | Description                                                                            |

|----------|------------|----------|----------------------------------------------------------------------------------------|

| COMN_A   | 1          | BID      |                                                                                        |

| COMP_B   | 2          | BID      | Connect de-coupling capacitor to VDD_5LFI                                              |

| COMN_B   | 3          | BID      |                                                                                        |

| DAC      | 4          | OUT      | DAC output for external amplifier support, Output Resistance of DAC pin is $1 k\Omega$ |

| VDD_5LFI | 5          | SUPI     | Positive supply for LF input stage, connect to VDD_MIX                                 |

| VSS      | 6          | SUPI     | Substrate                                                                              |

| MIX_INP  | 7          | INP      | Differential mixer positive input                                                      |

| VSS      | 8          | SUPI     | Substrate                                                                              |

| MIX_INN  | 9          | INP      | Differential mixer negative input                                                      |

| MIXS_IN  | 10         | INP      | Single ended mixer input                                                               |

| VSN_MIX  | 11         | SUPI     | Mixer negative supply                                                                  |

| CBIB     | 12         | BID      | Internal node de-coupling capacitor to GND                                             |

| VDD_MIX  | 13         | SUPO     | Mixer positive supply, internally regulated to 4.8V                                    |

Table 1. Pin Descriptions

| Pin Name  | Pin Number      | Pin Type | Description                                                                           |

|-----------|-----------------|----------|---------------------------------------------------------------------------------------|

| CBV5      | 14              | BID      | Internal node de-coupling capacitor to VDD_MIX                                        |

| VDD_TXPAB | 15              | SUPI     | Power Amplifier Bias positive supply. Connect to VDD_MIX                              |

| VEXT      | 16              | SUPI     | Main positive supply input (55.5V)                                                    |

| VEXT2     | 17              | SUPI     | PA positive supply regulator input (2.5 5.5V)                                         |

| VDD_RF    | 18              | SUPO     | PA positive supply regulator output, internally regulated to 23.5V                    |

| VDD_B     | 19              | SUPO     | PA buffer positive supply. Internally regulated to 3.4V                               |

| RFOUTP_1  | 20 <sup>1</sup> | OUT      | PA positive RF output                                                                 |

| RFOUTP_2  |                 |          | RFOUT1 and RFOUT2 must be tied together                                               |

| VSN_1     | 22 <sup>1</sup> | SUPI     |                                                                                       |

| VSN_2     | 23 <sup>1</sup> | SUPI     |                                                                                       |

| VSN_3     | 24 <sup>1</sup> | SUPI     | PA negative supply                                                                    |

| VSN_4     | 25 <sup>1</sup> | SUPI     |                                                                                       |

| VSN_5     | 26 <sup>1</sup> | SUPI     |                                                                                       |

| RFOUTN_1  | 27 <sup>1</sup> | OUT      | PA negative RF output or used in single ended mode.                                   |

| RFOUTN_2  | 28 <sup>1</sup> | OUT      | RFOUT1 and RFOUT2 must be tied together                                               |

| VSN_D     | 29              | SUPO     | Digital negative supply                                                               |

| OAD2      | 30              | BID      | Analog or digital received signal output and MCU support mode sense input             |

| OAD       | 31              | BID      | Analog or digital received signal output                                              |

| RFONX     | 32              | OUT      | Low power linear negative RF output (~0dBm)                                           |

| RFOPX     | 33              | OUT      | Low power linear positive RF output (~0dBm)                                           |

| VDD_RFP   | 34              | SUPO     | RF path positive supply, internally regulated to 3.4V                                 |

| VSN_RFP   | 35              | SUPI     | RF path negative supply                                                               |

| OSCI      | 36              | INP      | Crystal oscillator input                                                              |

| OSCO      | 37              | BID      | Crystal oscillator output or external 20MHz clock input                               |

| VDD_D     | 38              | SUPO     | Digital part positive supply, internally regulated to 3.4V                            |

| EN        | 39              | INP      | Enable input                                                                          |

| IRQ       | 40              | OUT      | Interrupt output                                                                      |

| 100       | 41              | BID      | l/O pin for parallel communication                                                    |

| IO1       | 42              | BID      | "O pin for parallel communication                                                     |

| IO2       | 43              | BID      | I/O pin for parallel communication EnableRX input in case of direct mode              |

| 103       | 44              | BID      | I/O pin for parallel communication  Modulation input in case of direct mode           |

| IO4       | 45              | BID      | I/O pin for parallel communication Slave select in case of serial communication (SPI) |

| IO5       | 46              | BID      | I/O pin for parallel communication Sub-carrier output in case of direct mode          |

Table 1. Pin Descriptions

| Pin Name | Pin Number | Pin Type | Description                                                                                                              |

|----------|------------|----------|--------------------------------------------------------------------------------------------------------------------------|

| 106      | 47         | BID      | I/O pin for parallel communication. MISO in case of serial communication (SPI) Sub-carrier output in case of direct mode |

| 107      | 48         | BID      | I/O pin for parallel communication. MOSI in case of serial communication (SPI)                                           |

| CLSYS    | 49         | OUT      | Clock output for MCU operation                                                                                           |

| CLK      | 50         | INP      | Clock input for MCU communication (parallel and serial)                                                                  |

| VDD_IO   | 51         | SUPI     | Positive supply for peripheral communication, connect to host positive supply                                            |

| CD2      | 52         | BID      | Internal node de-coupling capacitor                                                                                      |

| CD1      | 53         | BID      | - Internal riode de-coupling capacitor                                                                                   |

| AGD      | 54         | BID      | Analog reference voltage                                                                                                 |

| VSN_A    | 55         | SUPI     | Analog part negative supply                                                                                              |

| EXT_IN   | 56         | INP      | RF input in case external VCO is used                                                                                    |

| VSN_CP   | 57         | SUPI     | Charge pump negative supply                                                                                              |

| ADC      | 58         | IN       | ADC input for external power detector support                                                                            |

| VDD_A    | 59         | SUPO     | Analog part positive supply, internally regulated to 3.4V                                                                |

| VCO      | 60         | INP      | VCO input                                                                                                                |

| VOSC     | 61         | BID      | Internal node de-coupling capacitor                                                                                      |

| CP       | 62         | OUT      | Charge pump output                                                                                                       |

| VDDLF    | 63         | SUPI     | Positive supply for LF processing, internally regulated to 3.4                                                           |

| COMP_A   | 64         | BID      | Internal node, connect de-coupling capacitor to VDD_5LFI                                                                 |

| EXP_PAD  | 65         | SUPI     | Exposed paddle, must be tied to GND                                                                                      |

<sup>1.</sup> Internal Power amplifier is not available on AS3990.

### Notes:

1. BID: Bidirectional pin

INP: Input pin

OUT: Output pin

4. **SUPI:** Supply Input pin

5. **SUPO:** Supply Output pin

## 5 Absolute Maximum Ratings

Stresses beyond those listed in Table 2 may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in Electrical Characteristics on page 9 is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Table 2. Absolute Maximum Ratings

| Parameter                    |                                 | Min | Max           | Units                                                                                                                                                                                                 | Comments |

|------------------------------|---------------------------------|-----|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Supply v                     |                                 | 5.5 | V             | -                                                                                                                                                                                                     |          |

| Positive vol                 | tage other pads                 |     | $V_S \pm 0.3$ | V                                                                                                                                                                                                     | -        |

| Negative vo                  | tage other pads                 |     | -0.3          | V                                                                                                                                                                                                     | -        |

| Output                       | current, I <sub>O</sub>         |     | ±100          | mA                                                                                                                                                                                                    | -        |

| Maximum junct                |                                 | 125 | °C            | The maximum junction temperature for continuous operation is limited by package constraints.                                                                                                          |          |

| Storage tempe                | erature range, T <sub>stg</sub> | -55 | +150          | °C                                                                                                                                                                                                    | -        |

| Lead temperatur<br>from case |                                 | 260 | °C            | The reflow peak soldering temperature (body temperature) is specified according IPC/JEDEC J-STD-020C "Moisture/Reflow Sensitivity Classification for non-hermetic Solid State Surface Mount Devices". |          |

| FOD :: 1                     | IO pins, HBM                    |     | 2             | kV                                                                                                                                                                                                    |          |

| ESD rating '                 | RF pins, HBM                    |     | 1             | kV                                                                                                                                                                                                    | _        |

<sup>1.</sup> This integrated circuit can be damaged by ESD. We recommend that all integrated circuits are handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet the published specifications. RF integrated circuits are also more susceptible to damage due to use of smaller protection devices on the RF pins, which are needed for low capacitive load on these pins.

## **6 Electrical Characteristics**

VEXT = 5.3V, typical values at 25°C, unless otherwise noted.

Table 3. Electrical Characteristics

| Symbol                                | Parameter                                                    | Conditions                                                                                | Min | Тур | Max       | Units        |  |

|---------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----|-----|-----------|--------------|--|

| I <sub>VEXT</sub>                     | Supply current without PA driver current                     | V <sub>EXT</sub> Consumption                                                              |     | 80  |           | mA           |  |

| I <sub>VEXT</sub> +I <sub>VEXT2</sub> | Supply Current for AS3991 and internal PA <sup>1</sup>       | $V_{EXT2}$ Consumption,<br>$V_{EXT2}$ = 2.5V                                              |     | 310 |           | mA           |  |

| I <sub>STBY</sub>                     | Standby current                                              | -                                                                                         |     | 3   |           | mA           |  |

| I <sub>PD</sub>                       | Supply current in power-down mode                            | All system disabled including supply voltage regulators                                   |     | 20  | 100<br>10 | μA           |  |

| V <sub>AGD</sub>                      | AGD voltage                                                  | -                                                                                         | 1.5 | 1.6 | 1.7       | V            |  |

| V <sub>POR</sub>                      | Power on reset voltage (POR)                                 | -                                                                                         | 1.4 | 2.0 | 2.5       | V            |  |

| V <sub>VDD</sub>                      | Regulated supply for internal circuitry and for external MCU | -                                                                                         | 3.2 | 3.4 | 3.6       | V            |  |

| V <sub>DD RF</sub>                    | Regulated supply for internal PA                             | -                                                                                         | 1.9 | 2   | 2.1       | V            |  |

| V <sub>VDD</sub> MIX1                 | Regulated supply for mixers, bit vext_low=L                  | The difference between the external supply and the regulated voltage is higher than 250mV | 4.5 | 4.8 | 5.1       | V            |  |

| V <sub>VDD MIX2</sub>                 | Regulated supply for mixers, bit vext_low=H                  | The difference between the external supply and the regulated voltage is higher than 250mV | 3.5 | 3.7 | 3.9       | V            |  |

| P <sub>PSSR</sub>                     | Rejection of external supply noise on the supply regulators  | The difference between the external supply and the regulated voltage is higher than 250mV |     | 26  |           | dB           |  |

| P <sub>RFAUX</sub>                    | Auxiliary output power                                       | -                                                                                         |     | 0   |           | dBm          |  |

| P <sub>RFOUT</sub>                    | Internal PA output power <sup>1</sup>                        | -                                                                                         |     | 20  |           | dBm          |  |

| R <sub>RFIN</sub>                     | RFIN input resistance                                        | -                                                                                         |     | 100 |           | Ω            |  |

| $V_{SENS}$                            | Input sensitivity                                            | -                                                                                         |     | -66 |           | dBm          |  |

| 1dB <sub>CP</sub>                     | Input 1dB compression point                                  | -                                                                                         |     | 10  |           | dBm          |  |

| IP3                                   | Third order intercept point                                  | -                                                                                         |     | 21  |           | dBm          |  |

| T <sub>REC</sub>                      | Recovery time after modulation                               | Maximum LF selected                                                                       |     | 10  |           | μs           |  |

| Logic Input/Output                    |                                                              |                                                                                           |     |     |           |              |  |

| -                                     | Max. CLK frequency                                           | -                                                                                         |     |     | 1         | MHz          |  |

| $V_{LOW}$                             | Input logic low                                              | -                                                                                         |     |     | 0.2       | $V_{DD\_IO}$ |  |

| V <sub>HIGH</sub>                     | Input logic high                                             | -                                                                                         | 8.0 |     |           | $V_{DD\_IO}$ |  |

| R <sub>IO</sub>                       | Output resistance IO0IO7                                     | low_io = H for VDD_IO<2.7V                                                                |     | 400 | 800       | Ω            |  |

| R <sub>CL SYS</sub>                   | SYS Output resistance CL SYS low_io = H for VDD_IO<2.7V      |                                                                                           |     | 200 |           | Ω            |  |

<sup>1.</sup> Internal PA is available on AS3991only.

Table 4. Recommended Operating Conditions

| Symbol | Parameter                                    | Parameter Conditions |     | Тур | Max | Units |

|--------|----------------------------------------------|----------------------|-----|-----|-----|-------|

| -      | Supply Voltage                               | -                    | 5.0 | 5.3 | 5.5 | ٧     |

| -      | Supply voltage (bit vext_low set)            | -                    | 4.1 |     |     | V     |

| TJ     | Operating virtual junction temperature range | -                    | -40 |     | 125 | °C    |

| Тамв   | Ambient temperature                          | -                    | -40 |     | 85  | °C    |

| -      | Rth junction to exposed die pad              | -                    |     |     |     | °/W   |

## 7 Detailed Description

The RFID reader IC comprises complete analog and digital functionality for reader operation including transmitter and receiver section with complete EPC Gen2 or ISO18000-6C digital protocol support. To integrate as many components as possible, the device also comprises an on-board PLL section with integrated VCO, supply section, DAC and ADC section, and host interface section. In order to cover a wide range of possibilities, there is also Configuration registers section that configures operation of all blocks.

For operation, the device needs to be correctly supplied via. VEXT and VEXT2 pins and enabled via. EN pin (Refer Supply on page 11 for connecting to supply and Power Modes on page 12 about operation of the EN pin). At power-up the configuration registers are preset to a default operation mode. The preset values are described in the Configuration Registers Address Space on page 23 below each register description table. It is possible to access and change registers to choose other options.

The communication between the reader and the transponder follows the reader talk first method. After power-up and configuring IC, the host system starts communication by turning on the RF field by setting option bit rf\_on in the 'Chip status control register' (00) (see Table 13) and transmitting the first protocol command (Select in EPC Gen2). Transmitting and receiving is possible in the following two modes:

- 1. **Normal Data Mode:** In this mode, the TX and RX data is transferred through the FIFO register and all protocol data processing is done internally.

- 2. Direct Data Mode: In this mode, the data processing is done by the host system.

### Supply

The effective supply system of the chip decreases the influence of the supply noise and interference and thus improves de-coupling between different building blocks. A set of 3.4V regulators is used for supplying the reference block, AD and DA converters, low frequency receiver cells, the RF part, and digital part. It is possible to use the digital part supply VDD\_D for supplying the external MCU with a current consumption up to 20mA. The input pin for the regulators is VEXT. The output pins for regulators are VDD\_A, VDD\_LF, VDD\_D, VDD\_RFP and VDD\_B. Each of the pins require stabilizing capacitors to connected ground (2.2...10µF and 10...100nF) in parallel. Depending on quality of the capacitors, 100pF could be required.

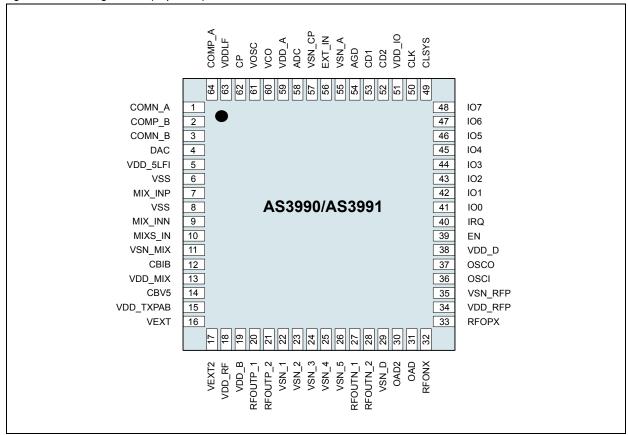

Figure 3. Mixer Supply

An additional 4.8V regulator is used for the input RF mixers supply. The input of this regulator is VEXT, output is VDD\_MIX pin. For correct operation of the 4.8V regulator, the VEXT voltage needs to be between 5.3V and 5.5V. VDD\_MIX needs de-coupling capacitors to VDD\_MIX like other VDD pins.

In case lower VEXT supply voltage is used (down to 4.1V), two option bits have to be set to optimize the chip performance to the lower supply. The vext\_low in the 'TRcal high and misc register' (05) bit decreases VDD\_MIX voltage to 3.7V to maintain the regulators PSSR and the ir<1> bit in the 'RX special setting 2' (0A) adapts mixer's internal operating point to lower supply. Adaptation to low supply is implemented in differential mixer only. The consequence of the decreased supply is lower mixer's input range.

VDD\_5LFI and VDD\_TXPAB pins are supply input pins and should be connected to VDD\_MIX. The internal 20dBm power amplifier<sup>1</sup> has an internal regulator from 2...3.5V. The output voltage selection is done by reg2v1:0 option bits in the 'Regulator and IO control register' (0B) (see Table 24).

The input pin is VEXT2 and output is VDD\_RF. For optimum noise rejection performance, the input voltage at VEXT2 pin needs to be at least 0.5V above the regulated supply output. Connecting VEXT2 directly to VEXT is possible only at the expense of increasing IC's power dissipation and decreasing the maximum operating temperature.

A separate I/O supply pin (VDD\_IO) is used to supply the internal level shifters for communication interface to the host system (MCU). VDD\_IO should be connected to MCU supply to ensure proper communication between the chip and MCU. In case the MCU is supplied by VDD\_D from the reader IC also VDD\_IO should be connected to VDD\_D.

#### **Power Modes**

The chip has three power modes.

- **Power Down Mode:** The power down mode is activated by EN pin low (EN=L). For correct operation, the OAD2 pin should not be connected.

- **Normal Mode:** The normal mode is entered by EN=H. In this case all supply regulators, reference voltage system, crystal oscillator, RF oscillator and PLL are enabled. After the crystal oscillator stabilizes, the CLSYS clock becomes active (default frequency is 5MHz) and the chip is ready to move to transmit or receive operation.

- **Standby Mode:** The standby mode is entered from normal mode by option bit stby=H. In the standby mode the regulators, reference voltage system, and crystal oscillator are operating in low power mode; but the PLL, transmitter output stages and receiver are switched off. All the register settings are kept while switching between standby and normal mode.

Power Down with **MCU Support mode** intends to support the MCU if the majority of the reader IC is in power down. This mode is enabled by connecting  $10k\Omega$  resistor between OAD2 pin and ground. During EN=L period, the VDD\_D regulator is enabled in low power mode and the CLSYS frequency is 60kHz typically.

It is also possible to trigger **temporary normal mode** from power down mode (EN=L) by pulling shortly the OAD2 pin low via  $10k\Omega$  or less. After the crystal oscillator is stable and the CLSYS clock output is active, the chip waits for approximately 200 $\mu$ s and then changes back to the power down mode. Using this function, the superior system can wake up the reader IC and MCU that are both in the power down mode. If the MCU during 200 $\mu$ s period finds out that the RFID system must react, it confirms the normal mode by setting EN high.

| Table 5. | AS3990/AS3991    | Power    | Modes |

|----------|------------------|----------|-------|

| rabio o. | , 100000, 10000, | , 0,,,,, | moacc |

| Power mode                    | EN | OAD2                 | Std by |

|-------------------------------|----|----------------------|--------|

| Power down                    | L  | -                    | X      |

| Power down<br>SYSCLK of 60kHz | L  | 10k to GND           | ×      |

| Normal power                  | Н  | X                    | X      |

| Stand by                      | -  | X                    | Н      |

| Listen mode                   | L  | 10k and falling edge | X      |

<sup>1.</sup> Internal PA is available on AS3991only.

#### **Host Communication**

An 8-bit parallel interface (pins IO0 to IO7) with two control signals (CLK, IRQ) forms the main communication system. It can also be changed (by hardwiring some of the 8 I/O pins) to a serial interface. The data handling is done by a 24 byte FIFO register used in both directions, transmission and reception. For more details, refer Reader Communication Interface on page 41.

The signal level for communication between the host system (MCU) is defined by the supply voltage connected to VDD\_IO pin. Communication is possible in wide range between 1.8V and 5.5V. In case the pull-up output resistance at VDD\_IO below 2.7V is to high, it can be decreased by setting option bit vdd\_io\_low in the 'TRcal High and Misc register' (05). In case the MCU is supplied from the reader IC, then both the MCU supply and VDD\_IO pin need to be connected to VDD\_D.

CLSYS output level is defined by the VDD\_IO voltage. It is also possible to configure CLSYS to open drain N-MOS output by setting the option bit open\_dr in the in the 'TRcal high and misc register' (05), (see Table 18). This function can be used to decrease amplitude and harmonic content of the CLSYS signal and decrease the cross-talk effects that could corrupt operation of other parts of the circuit.

#### VCO and PLL

The PLL section is composed of a voltage control oscillator (VCO), prescaler, main and reference divider, phase-frequency detector, charge pump, and loop filter. All building blocks excluding the loop filter are completely integrated. Operating range is 860MHz to 960MHz.

#### VCO and External RF Source

Instead of the internal PLL signal, an external RF source can be used. The external source needs to be connected to EXT\_IN pin and option bit eext\_in in the 'PLL A/B divider auxiliary register' (17) (see Table 36) needs to be set high. The EXT\_IN input optimum level is 0dBm with a DC level between 0V and 2V.

It is also possible to use external VCO and internal PLL circuitry. In this case, the output of the external VCO (0dBm) needs to be connected to EXT\_IN, option bits eext\_in and epresc in the 'PLL A/B divider auxiliary register' (17) both need to be set high. The charge pump output pin CP needs to be connected to the external loop filter input and loop filter output to the external VCO input. This configuration is useful in case the application demands better phase noise performance than the completely integrated oscillator offers.

The internal on-board VCO is completely integrated including the variable capacitor and inductor. The control input is pin VCO; input range is between 0 and 3.3V. The option bits eosc<2:0> in the 'CLSYS, analog out and CP control' (14) (Table 33) can be used for oscillator noise and current consumption optimization. Option bit lev\_vco in the 'PLL A/B divider auxiliary register' (17) (see Table 36) is used to optimize the internal VCO output level to other RF circuitry demands. VCO and CP pin valid range is between 0.5V and 2.9V.

AS3991 and above have internal VCO set to a frequency range around 1800MHz, later internally divided by two for decreasing the VCO pulling effect. The tuning curve of 1800MHz VCO is divided into 16 segments to decrease VCO gain and attain lowest possible phase noise.

Configuration of the 1800MHz VCO tuning range can be manual using option bits vco\_r<3:0> in the 'CL\_SYS, analog out and CP control' register (14) or automatic using L-H transition on option bit auto in the same register. The device allows measurement of the VCO voltage using option bit mvco and reading out the 4 bits result of the automatic segment selection procedure, both in the same register.

#### **PLL**

The divide by 32/33 prescaler is controlled by the main divider. The main divider ratio is defined by the 'PLL A/B divider main register' (16). The low ten bits in the three bytes deep register define A value and the next ten bits define B value. The A and B values define the main divider division ratio to N=B\*32+A\*33. The reference clock is selectable by RefFreq<2:0> bits in the 'PLL R, A/B divider main register' (16) (see Table 35). The available values are 500 kHz, 250 kHz, 200 kHz, 100 kHz, 50 kHz, 25 kHz. Charge pump current is selectable between 150μA and 1200μA using option bits cp1:0 in the 'CL\_SYS, analog out and CP control register' (14) (see Table 33). The cp<3> is used to change the polarity (direction) of the charge pump output.

The frequency hopping is supported by direct commands 'Hop to main frequency' (84) and 'Hop to auxiliary frequency' (85). The hopping is controlled by host system (MCU) using two configuration registers for two frequencies. Before enabling the RF field, the host system needs to configure the PLL by writing the 'CL\_SYS, analog out and PLL register' (09) and the 'PLL R, A/B divider main' (16) registers. Any time during operating at the first selected frequency, the external system can configure the three bytes deep 'PLL A/B divider auxiliary (17)' register.

Hopping to the second frequency is triggered, if direct command 'Hop to auxiliary frequency' is sent. Hop to the third frequency is similar: the register 'PLL A/B divider main (16)' can be written any time the external system has free resources and actual hop is triggered by direct command 'Hop to main frequency'.

### **Chip Status Control**

In the 'Chip status control register' (00) (see Table 13), main functionality of the chip is defined. By setting the rf\_on bit in the 'Chip control register' (00), the transmit and receive part are enabled. The initial RF field ramp-up is defined with the Tari1:0 option bits in the 'Protocol control register' (01) (see Table 14). It is also possible to slow down the initial RF field ramp by option bits trfon1:0 in the 'Modulator control register' (15) (see Table 34). The available values are 100µs, 200µs, and 400µs.

The host system can check whether the field ramp-up is finished via the rf\_ok bit in the 'AGC and internal status register' (0E) (see Table 27), which is set high when ramp-up is finished. By setting the rf\_on bit low, the field will ramp-down similarly to the ramp-up transient. It is also possible to enable receiver operation by setting rec\_on bit. The agc\_on and agl\_on bits enables the (Automatic Gain Control) AGC and (Automatic Gain Leveling) AGL functionality, dac\_on enables DA converter, bit direct enables the direct data mode, and stby bit moves chip to the stand-by power mode.

#### **Protocol Control**

In the 'Protocol control register' (01) (see Table 14), the main protocol parameters are selected (Tari value and RX coding for EPC Gen2 protocol). The Gen2 Protocol is configured by setting Prot<1:0> bits to low. The dir\_mode<6> bit defines type of output signals in case the direct mode is used. The rx\_crc\_n<7> bit high defines reception in case the user does not want to check CRC internally. In this case, the CRC is not checked but is just passed to the FIFO like other data bytes. In the EPC Gen2, this function is useful in case of truncated EPC reply where the 'CRC' transponder transmits is not valid CRC calculated over actual transmitted data.

### **Option Registers Preset**

After power up (EN low to high transition), the option registers are preset to values that allow default reader operation. Default transmission uses Tari 25µs, PW length is 0.5Tari, TX one length is 2 Tari, and RTcal is 133µs. Default reception uses FM0 coding with long preamble, link frequency 160kHz. Default operation is set to internal PLL with internal VCO, differential input mixers, low power output (RFOPX, RFONX), and DSB-ASK transmit modulation.

#### **Transmitter**

Transmitter section comprises of protocol processing digital part, shaping, modulator and amplifier circuitry. The RF carrier is modulated with the transmit data and amplified for transmission.

#### **Normal Mode**

In normal mode, all signal processing (protocol coding, adding preamble or frame-sync and CRC, signal shaping, and modulation) is done internally.

The external system (MCU) triggers the transmission and loads the transmit data into the FIFO register. The transmission is started by sending the transmit command followed by information on the number of bytes that should be transmitted and the data. The number of bytes needs to be written in the 'TX length' registers and the data to the FIFO register. Both can be done by a single continuous write. The transmission actually starts when the first data byte is written into the FIFO.

The second possibility is to start transmission with one of the direct Gen2 commands (Query, QueryRep, QueryAdjust, ACK, NAK, ReqRN). In this case, the transmission is started after receiving the command.

In case the transmission data length is longer than the size of the FIFO, the host system (MCU) should initially fill the FIFO register with up to 24 bytes. The reader chip starts transmission and sends an interrupt request when only 3 bytes are left in the FIFO. When interrupt is received, the host system needs to read the 'IRQ status register' (0C) (see Table 25). By reading this register, the host system is notified by the cause of the interrupt and the same reading also clears the interrupt. In case the cause of the interrupt is low FIFO level and the host system did not put all data to the FIFO, the remaining data needs to be sent to FIFO, again according to the available FIFO size. In case all transmission data was already sent to the FIFO, the host system waits until the transmission runs out. At the end of the transmit operation, the external system is notified by another interrupt request with a flag in the IRQ register that signals the end of transmission.

The two 'TX length' registers support in-complete bytes transmission. The high two nibbles in register 1D and the nibble composed of bits B4 ~ B7 in 'TX length byte 2' (1E) register (see Table 43) store the number of complete bytes that should be transmitted. Bit B0 (in register 1E) is a flag that signals the presence of additional bits that do not form a complete byte. The number of bits are stored in bits B1~B3 of the same register (1E).

The protocol selection is done by the 'Protocol control register' (01) (see Table 14). As defined by selected protocol, the reader automatically adds all the special signals like Preamble, Frame-Sync, and CRC bytes. The data is then coded to the modulation pulse level and sent to the modulator. This means that the external system only has to load the FIFO with data and all the micro-coding is done automatically.

The EPC Gen 2 protocol allows some adjustment in transmission parameters. The reader IC supports three Tari values (25µs, 12.5µs, 6.25µs) by changing Tari<1:0> option bits in the 'Protocol control register' (01). PW length and length of the logical one in the transmission protocol can be adjusted by TxPW<1:0> and TxOne<1:0> option bits in the 'TX options' (02) register. Session that should be used in direct commands is defined in the S1and S0 bits in the same register. The back scatter link frequency is defined by TRcal in the Query command transmission. The TRcal is defined by option bits TRcal<11:0> in the 'TRcal registers' (04, 05).

Table 6. Register Bits Settings

| Protocol setting  | Register<br>Bits      |                  | Individual settings |                   |                     |                   |                   |                   |  |

|-------------------|-----------------------|------------------|---------------------|-------------------|---------------------|-------------------|-------------------|-------------------|--|

| TARI              | Protocol control<1:0> | 6,25µs (00)      |                     | 12,5µs (01)       |                     | 25μs              |                   |                   |  |

| PW length control | TX option <7:6>       | 0,27TARI<br>(00) | 0,35TARI(01)        |                   | 0,44TARI(10)        |                   | 0,5TARI(11)       |                   |  |

| Data1 Tx          | TX option <5:4>       | 1,5TARI(00)      | 1,66TARI(01)        |                   | 1,83TARI(10)        |                   | 2TARI(11)         |                   |  |

| Coding            | Protocol control<4:3> | FMO(00)          | M2(01)              |                   | M4(10)              |                   | M8(11)            |                   |  |

| Link frequency    | RX option <7:4>       | 40 kHz<br>(0000) | 80 kHz<br>(0011)    | 160 kHz<br>(0110) | 213,3 kHz<br>(1000) | 256 kHz<br>(1001) | 320 kHz<br>(1100) | 640 kHz<br>(1111) |  |

The software designer needs to take care that actual TRcal (reg. 04, 05) and RxLF<3:0> (reg. 03) bits and DR bit in the transmission of the Query command are matched. Precise description is in the EPC Gen2 or ISO18000-6C protocol description.

The Transmit section contains a timer. The timer is used to issue a command in a specified time window after a transponder's response. The timer's time is defined in 'TX replay in slot' (06) register. The timer is enabled by using the command 'Delayed transmission without CRC' (92) or 'Delayed transmission with CRC' (93) and is actually started at the end of the reception.

Table 7. EPC\_gen2 - Tari Combinations

| Link        |       |          |                | 25µs   |        | 12.5µs |        | 6.25µs |   |

|-------------|-------|----------|----------------|--------|--------|--------|--------|--------|---|

| Forward     |       |          |                | 2.5    | 3      | 2.5    | 3      | 2.5    | 3 |

|             | LF    | Division | TR cal         |        |        |        |        |        |   |

|             | (kHz) | Ratio    | (microseconds) |        |        |        |        |        |   |

| Link        | 40    | 8        | 200.00         | 3.2    | 2.6667 | -      | -      | -      | - |

|             | 80    | 8        | 100.00         | 1.6    | 1.3333 | -      | ı      | ı      | - |

| Backscatter | 160   | 64/3     | 133.33         | 2.1333 | 1.7778 | -      | -      | -      | - |

| ack         | 213.3 | 64/3     | 100.02         | 1.6003 | 1.3335 | -      | 1      | ı      | - |

| Δ           | 256   | 64/3     | 83.33          | 1.3333 | 1.1111 | 2.6667 | 2.2222 | -      | - |

|             | 320   | 64/3     | 66.67          | -      | -      | 2.1333 | 1.7778 | -      | - |

Table 7. EPC\_gen2 - Tari Combinations

| Link             | TARI settings |             | 25          | μs     | 12.    | 5µs    | 6.2    | 5µs    |        |

|------------------|---------------|-------------|-------------|--------|--------|--------|--------|--------|--------|

| Forward Link     | Zero aı       | nd one leng | th (RT CAL) | 2.5    | 3      | 2.5    | 3      | 2.5    | 3      |

|                  | 640           | 64/3        | 33.33       | -      | -      | -      | -      | 2.1333 | 1.7778 |

|                  |               | •           |             |        |        |        |        |        |        |

|                  | 40            | 8           | 200.00      | -      | -      | -      | -      | -      | -      |

|                  | 80            | 8           | 100.00      | 1.6    | 1.3333 | -      | -      | -      | -      |

|                  | 160           | 8           | 50.00       | -      | -      | 1.6    | 1.3333 | -      | -      |

|                  | 213.3         | 8           | 37.51       | -      | -      | -      | -      | 2.4004 | 2.0003 |

| ä                | 256           | 8           | 31.25       | -      | -      | -      | -      | 2      | 1.6667 |

| er L             | 320           | 8           | 25.00       | -      | -      | -      | -      | 1.6    | 1.3333 |

| catt             | 640           | 8           | 12.50       | -      | -      | -      | -      | -      | -      |

| Backscatter Link |               |             | _           |        |        |        |        |        |        |

| Ba               | 40            | 64/3        | 533.33      | -      | -      | -      | -      | -      | -      |

|                  | 80            | 64/3        | 266.67      | -      | -      | -      | -      | -      | -      |

|                  | 160           | 64/3        | 133.33      | 2.1333 | 1.7778 | -      | -      | -      | -      |

|                  | 213.3         | 64/3        | 100.02      | 1.6003 | 1.3335 | -      | -      | -      | -      |

|                  | 256           | 64/3        | 83.33       | 1.3333 | 1.1111 | 2.6667 | 2.2222 | -      | -      |

|                  | 320           | 64/3        | 66.67       | -      | -      | 2.1333 | 1.7778 | -      | ı      |

|                  | 640           | 64/3        | 33.33       | -      | -      | -      | -      | 2.1333 | 1.7778 |

#### **Direct Mode**

Direct mode is applied if the user wants to use analog functions only and bypass the protocol handling supported in the reader IC.

#### **Direct Mode Using Parallel Interface**

The reader IC enters the direct mode when option bit 'direct' is set to high in the 'Chip status control register' (00). As the direct mode starts immediately, all the register settings that help to configure the operation of the chip needs to be done prior to entering the direct mode. The 'write' command for direct mode should not be terminated by stop condition since the stop condition terminates the direct mode. This is necessary as direct mode uses four IO pins (IO2, IO3, IO5, IO6) and normal parallel or serial communication is not possible in direct mode. To terminate the direct mode, the user needs to send the stop condition. After stop condition, normal communication via. interface and access to the registers are possible.

#### Direct Mode Using Serial Interface (SPI)

To enter direct mode via SPI, bit direct should be set to high in the 'Chip status control register' (00) and stop condition (IO4 L-to-H transition) has to be sent. As the direct mode starts immediately, all the register settings that help to configure the operation of the chip needs to be done prior to entering the direct mode. The direct mode persists till writing bit direct to low (IO4 H-to-L, SPI write to reg00). Since the direct mode uses four IO pins (IO2, IO3, IO5, IO6), it is not possible to read registers during the direct mode (IO6 which is MISO in SPI mode is used as direct mode data or subcarrier output). It is possible to write register 00 to terminate the direct mode. After direct mode termination, normal communication via SPI interface and access to the registers are possible.

For more information on transmit modulation input signal possibilities, refer to Modulator on page 17.

For more information on the receive output signal possibilities, refer to Receiver on page 18.

The digital modulation input in direct mode is IO3. RF field is set to high level if IO3 is high, and to low level if IO3 is low. IO2 is used as RX enable. For correct operation, follow the instructions given below:

- 1. Configuration registers should be defined, starting from reg01

- 2. Direct command Enable RX (97) should be sent

- 3. Bit direct should be written to reg00

- 4. IO2 should be low during data transmission via IO3

- 5. IO2 should be changed to high level just before the reception is expected

- 6. IO3 should be maintained high during reception

#### Modulator

For the modulation signal source, there are three possibilities:

- Normal data mode Internally coded and internally shaped.

- Externally coded and internally shaped modulation enabled by entering direct mode. For more information on entering and terminating the direct mode, refer to Direct Mode on page 16.

- Externally coded and externally shaped modulation is enabled by setting option bit e\_amod in the 'Modulator control register' (15) and entering direct mode. For more information on entering and terminating the direct mode, refer to Direct Mode on page 16. In this case, ADC and DAC pins are differential modulator input. The DC level should be 2.2V, amplitude 600mVp. It is also possible to use CD1 and CD2 pins as high and low reference for the external modulation shape circuitry.

The internal modulator is capable of DSB-ASK and PR-ASK modulation. Modulation shape is controlled with a double D/A converter. The first one defines the upper (un-modulated) signal level while the second one generates the modulation transient. The level defined by the first converter is filtered by capacitors on CD1 and CD2 pins to decrease the noise level. The two levels are used as a reference for the shaping circuitry that transforms the digital modulation signal to shaped analog modulation signal. Sinusoidal and linear shapes are available. The output of the shaping circuit is interpolated and connected to the modulator input.

The output level and modulation shape properties are controlled by the 'Modulator control register' (15). The level of the output signal is adjusted by option bits tx\_lev<4:0>. Modulation depth for ASK is adjusted by mod\_dep<5:0> bits. Valid values for DSB-ASK are 01 to 3F. PR-ASK modulation is selected by pr-ask bit high. In case of PR-ASK, the mod\_dep<5:0> bits are used to adjust the delimiter/first zero timing. Linear modulation shape is selected by lin\_mod bit. The rate of the modulation transient is automatically adjusted to selected Tari and can be adjusted by ask\_rate<1:0> bits. For smoother transition of the modulation signal, an additional low pass filter can be used. The Filter will be enabled by e lpf bit. The adjustment step is 1.6%, 3F gives 100% ASK modulation depth.

PR-ASK modulation is selected by pr-ask bit high. In case of PR-ASK the mod\_dep<5:0> bits are used to adjust the delimiter/first zero timing in a range 9.6µs to 15.9µs. Linear modulation shape is selected by lin\_mod bit. The rate of the modulation transient is automatically adjusted to selected Tari and can be adjusted by ask\_rate<1:0> bits. For smoother transition of the modulation signal, additional low pas filter can be used by e\_lpf bit.

In ASK modulation it is possible to adjust delimiter length by setting option bit ook\_ask in the 'Modulator control register' (15). In this case, ook\_ask defines 100% ask modulation and the mod\_dep<5:0> bits are used for delimiter length setting similar to the PR-ASK mode.

Bits aux\_mod and main\_mod define whether the modulation signal will be connected to the auxiliary low power output or to the main PA output. In case one of the outputs are enabled by the etxp<3:0> bits and appropriate aux\_mod or main mod bit is low, the output is enabled but not modulated.

#### **Amplifier**

The following two outputs are available:

■ Low power high linear output ( $\sim$ 0dBm) can be used for driving an external amplifier. This output uses RFOPX and RFONX pins and it has nominal output impedance of  $50\Omega$ . It needs an external RF choke and de-coupling capacitor for operation. It is also possible to use differential output for driving balanced loads. The output is enabled by etx<1:0> bits in the 'Regulator an IO control' (0B) register (see Table 24). With the help of these bits, it is also possible to adjust current capability of the output.

■ **Higher output power output** (~20dBm) can be used for antenna driving in case of short range applications. Internal higher power amplifier<sup>2</sup> is enabled by etx<3:2> bits in the 'Regulator an IO control' (0B) register (see Table 24). For operation it needs external RF choke and correct impedance matching for operation in 50Ω system. It is also possible to use differential output by setting etx<4>. The differential outputs are RFOUTP\_1, RFOUTP\_2 and RFOUTN 1, RFOUTN 2. Single ended output is RFOUTN 1, RFOUTN 2.

#### Receiver

Receiver section comprises two input mixers followed by gain and filtering stages. The two receiving signals are fed to decision circuitry, bit decoder and framer where preamble is removed and CRC is checked. The clean framed data is accessible to the host system (MCU) via. 24 byte FIFO.

#### **Input Mixer**

The two input mixers are driven with 90° shifted LO signals and form IQ demodulator circuit. Using IQ architecture, the amplitude modulated input signals are demodulated in the in-phase channel (I) while the phase modulated input signals are demodulated in the quadrature phase (Q) channel. Mixed input modulation is demodulated in both receiving channels. This configuration allows reliable operation regardless the transponders. Modulation presents amplitude or phase modulation at receiver's input and suppresses communication holes that are caused by modulation alternation.

To optimize the receiver's noise and input range properties, the mixers have adjustable input range. Depending on the reflectivity of the environment or antenna, the receiver's input RF voltage can increase to a level that corrupts mixer operation. In such a case, the input range can be widened by internal input attenuator setting option bit ir<0>.

In case lower supply voltage is used, the ir<1> option bit adapts mixer's operation point to decreased supply. The ir<1:0> bits are in the 'RX special setting2 register' (0A) (see Table 23). Single ended input mixer should be used only with 4.8V VDD MIX supply (option bit low vext=0) and accordingly high VEXT voltage.

By default differential mixers input is chosen. The differential input is formed by pins MIX\_INP and MIX\_INN. Input should be AC coupled. Besides a differential input, it is possible to use single ended mixers input. It is chosen by s\_mix bit in the 'Rx special setting registers' (0A) (see Table 23). The single ended mixers input MIXS\_IN pin. Input should be AC coupled also. The unused input doesn't need to be connected.

#### **RX Filter**

The high pass filter corner frequency is adjustable in the range between 6 kHz and 150 kHz. Filter low pass corner frequency is adjustable in the range between 160 kHz and 1200 kHz. The appropriate combinations for different link are selected by the If<2:1> option bits in the 'RX special setting' (09) register. The following table presents typical filter characteristics.

| fl<2:1> | 3dB bandwidth | Attenuation at 10kHz | Attenuation at 600kHz | Attenuation at 1200kHz |

|---------|---------------|----------------------|-----------------------|------------------------|

| 00      | 6.5 –160kHz   | NA                   | 17dB                  | 31dB                   |

| 01      | 20 – 320kHz   | 7dB                  | 9dB                   | 20dB                   |

| 10      | 55 – 830kHz   | 16dB                 | NA                    | 6dB                    |

| 11      | 145 – 1200kHz | 24dB                 | NA                    | NA                     |

For the better reception of the FM0 coded signals, it is possible to decrease the high pass corner frequency by the factor of two by option bit fl<3>. This improves passthrough of the FM0 preamble.

It is possible to additionally speed up the first AC coupling time constant by setting option bit fl<4> in the 'RX special setting' (09) register (see Table 22).

The internal (patent pending) feedback AC coupling system prior to the start of transmit modulation stores the DC operating points and after data transmission progressively adjusts the high pass time constant to allow very fast settling time prior to beginning of reception. Such system is needed to accommodate the short TX to RX time used at the highest bit rates in the EPC Gen-2 protocol.

<sup>2.</sup> Internal PA is available on AS3991 only.

#### **RX** Gain

Gain in the receiving chain can be adjusted to optimize the signal to noise and interference ratio. There are three ways of adjusting: manual adjustment, AGC, and AGL.

- Manual Adjustment is gain adjustable by setting option bits gain<5:1> in the 'RX special setting 2 registers' (0A) (see Table 23). The low two bits decrease digitizer hysteresis by 5dB (3steps), the high three bits decrease the amplifier gain by 3dB (7 steps).

- AGC is automatic gain control. It can be enabled by option bit agc\_on in the 'Chip status control' register (00) (see Table 13). AGC comprises of a system that decreases gain during the first periods of the incoming preamble. Gain is decreased equally for both channels to a level that results the stronger signal is just in the range. In this case, the ratio between I and Q channel amplitude is maintained. The resulted status of the AGC can be seen in the 'AGC and internal status' register (0E) (see Table 27).

- AGL is another possibility for adjusting the gain. AGL bit needs to be set high at the moment when there is no actual transponder response at receiver input. It automatically decreases gain for each channel to the level that is just below the noise and interference level. The gain of the two channels is independent. The resulted status of the AGL for both channels can be seen in the 'AGL status 'register (10) (see Table 29).

Difference between the AGC and AGL functionality is that AGC is done each time at beginning of the receive telegram; while AGL is done only at the moment when agl on bit is set high, stored, and is valid till the agl on bit is set low.

The two receiving signals are digitized and evaluated. The decision circuit selects the in-phase signal or quadrature signal for further processing, whichever presents the better received signal. Which of the signals is chosen can be seen in the in\_select bit in the 'AGC and internal status' register (0E). Bit is valid from preamble end till start of the next transmission.

#### Received Signal Strength Indicator (RSSI)

The receiver section includes a double RSSI meter. The RSSI meters are connected to the outputs of both receiver chains to measure in real time the peak to peak demodulated voltage of each receiving channel during the reception of each transponder response (from the end of RX wait timer till the end of reception). The peak value of each RSSI meter is stored and presented in the 'RSSI levels' (0F) register (see Table 28). The RSSI register is valid till start of next transmission.

#### Reflected RF Level Indicator

The receiver also comprises the input RF level indicator. It is used for diagnostic of circuitry or environment difficulties.

The reflection of poor antenna, reflection of reflective antenna's environment, or directional device leakage (circulator) can cause that input mixers are overdriven with the transmitting signal.

Overloading of the input mixers by reflected transmitting carrier can be notified by the host system (MCU) by measuring the RF input level via internal AD converter. The reflected carrier that is seen on the two mixers input is down converted to zero frequency. The two DC levels on the mixers outputs are proportional to the input RF level and dependant on the input phase and can be used for measuring the level of the reflected carrier. They can be connected to the on-board ADC converter by setting option bits msel<2:0> in the 'Test setting and measurement selection register' (11). The appropriate settings for connecting two mixers' DC levels to AD converter are 001 and 002. Conversion is started by direct command 'Trigger AD conversion' (87). Result in register 19 is valid 20µs after triggering.

#### **Normal Mode**

In the normal mode, the digitized output after decision circuit is connected to the input of the digital portion of the receiver. This input signal is the sub-carrier coded signal, which is a digital representation of modulation signal on the RF carrier.

The digital part of the receiver consists of two sections, which partly overlap. The first section comprises the bit decoders for the various protocols. The bit decoders convert the sub-carrier coded signal to a bit stream and the data's clock according to the protocol defined by option bits Rx-cod<1:0> in the 'Protocol control' (01) register (see Table 14) and Rx\_LF<3:0> option bits in the 'RX options' (03) register. Preamble is truncated. The decoder logic is designed for maximum error tolerance. This enables the decoders to successfully decode even partly corrupted sub-carrier signals due to noise or interference. The receiver also supports transfer of incomplete bytes. The number of valid bits in the last received byte is reported by Bb<2:0> bits in the 'TX length byte 2' (1E) register (see Table 43).

The second section comprises the framing logic for the protocols supported by the bit decoder section. In the framing section, the serial bit stream data is formatted in bytes. The preamble, FrameSync, and CRC bytes are checked and removed. The result is 'clean' data, which is sent to the 24-byte FIFO register where it can be read out by the host system (MCU).

In the EPC Gen2 protocol, the decoder supports long RX preamble (TRext=1) for FM0, and all Miller coded signals and short RX preamble (Trext=0) for Miller4 and Miller8 coded signals. In the EPC Gen2 protocol, the timing between transponders response and the subsequent reader's command is quite short. To relieve the host system (MCU) of reading RN16 (or handle) out of the FIFO and then writing it back into the FIFO, there is a special register for storing last received RN16 during the Query, QueryRep, QueryAdjust or RegRN commands. The last stored RN16 is automatically used in ACK command.

The start of the receive operation (successfully received preamble) sets the flags in the 'IRQ and status' register. The end of the receive operation is signalled to the host system (MCU) by sending an interrupt request (pin IRQ). If the receive data packet is longer than 8 bytes, an interrupt is sent to the MCU when the 18<sup>th</sup> byte is received to signal that the data should be removed from the FIFO.

In case an error in data format or in CRC is detected, the external system is made aware of the error by an interrupt request pulse. The nature of the interrupt request pulse is available in the 'IRQ and status register' (0C) (see Table 25).

The receive part comprises two timers.

- The RX wait time timer setting is controlled by the value in the 'RX wait time' (08) (see Table 21). This timer defines the time after the end of transmit operation in which the receive decoders are not active (held in reset state). This prevents any incorrect detection that could be caused as a result of transients that are caused by transmit operation or transients that are caused by noise or interference. The value of the 'RX wait time register' defines this time with increments of 6.4µs. This register is preset at every write to the "Protocol control" register (01) according to the minimum tag response time defined by default register definition.

- The RX no response timer setting is controlled by the 'RX no response wait time' (07) (see Table 20). This timer measures the time from the start of slot in the anti-collision sequence until the start of tag response. If there is no tag response in the defined time, an interrupt request is sent and a flag is set in 'IRQ status control' register. This enables the external controller to be aware of empty slots. The wait time is stored in the register with increments of 25.6µs. This register is automatically preset for every new protocol selection.

RX length register' (1A, 1B) defines the number of bits that the receiver should receive. The number of bits is taken into account only in case the value is different than 0 00, otherwise receiver stops on pause at the end of reception. Since in noisy environment, the end of transponders transmission is not precisely defined using the RX length registers improves the probability for successful receiving. For direct commands 98 to 9C, the RX length is internally set to 16 to receive RN16. For direct command 9F, the RX length is internally set to 32 to receiveRN16 and CRC. For other commands when the host system knows the expected RX length, it is recommended to write it in the RX length register. The only case when RX length is not known in advance is reception of the PC+EPC.

AS3991 and above handle the afore mentioned issue by using special RX mode. The idea is that reader chip generates an additional interrupt after two bytes (PC part of the PC+EPC field) are received. MCU reads out the two bytes that define the length of the on going telegram and writes it in the RX length register.

To use IRQ after the two received bytes, the fifo\_dir\_irq2 bit in the reg1A should be set and non-zero length (typical PC+EPC length) should be written in the 1B register before start of reception. The fifo\_dir\_irq2 performs the following changes in the behavior of the logic:

- All received bytes are directly transferred to FIFO. Normally the receiving data is pipelined, causing that the two CRC bytes are not seen in the FIFO. If dir\_fifo=1, then all bytes including CRC are seen in the FIFO.

- Additional interrupt is generated after two bytes are received. In the IRQ status register, the 'header/2byte' (B3) bit is set. If the reception is still in progress, IRQ status value is 48.

At this moment, the MCU needs to read out the first two bytes (PC part of the PC+EPC field) and set RX length accordingly. The fifo\_dir\_irq2 bit should be maintained high.

- At the end of reception, another IRQ is generated. Additional IRQ status bit 'Irq\_err3 preamble/end' (B1) is set. IRQ status is 42 if the intermediate 2nd\_byte interrupt was read out and cleared, or 4A if the reception was over before the intermediate interrupt was read out and cleared.

#### **Direct Mode**

The direct mode is applied in case the user wants to use analog functions only and bypass the protocol handling supported in the reader IC. (Refer to Transmitter on page 14 for information on entering direct mode.)

Regarding receiving tag data in direct data mode, there are three possibilities depending on setting of option bits:

- Internally decoded bit stream and bit clock according to the protocol defined by option bits Rx-cod<1:0> in the 'Protocol control' (01) register and Rx\_LF<3:0> option bits in the 'RX options' (03) register is enabled by low level of option bit dir\_mode in the 'Protocol control' (01) register. Outputs are IO5 and IO6.

- Digitized sub-carrier signals of both receiving channels are enabled by high level of option bit dir\_mode in the 'Protocol control' (01) register. Outputs are IO5 and IO6.