Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

Page 1

# **AS5510**

# Linear Hall Sensor with I<sup>2</sup>C Output

## **General Description**

The AS5510 is a Linear Hall Sensor with 10 bit resolution and I<sup>2</sup>C interface. It can measure absolute position of lateral movement of a simple 2-pole magnet. Depending on the magnet size, a lateral stroke of 0.5~2mm can be measured with air gaps around 1.0mm. To conserve power, the AS5510 may be switched to a power down state when it is not used. It is available in a WLCSP and SOIC8 package and qualified for an ambient temperature range from -30°C to 85°C.

Ordering Information and Content Guide appear at end of datasheet.

## **Key Benefits & Features**

The benefits and features of AS5510, Linear Hall sensor with I<sup>2</sup>C output are listed below:

Figure 1: **Added Value of Using AS5510**

| Benefits                           | Features                                                 |

|------------------------------------|----------------------------------------------------------|

| Highest reliability and durability | Contactless position measurement                         |

| Ideal for battery powered devices  | Power down mode                                          |

| Easy to use                        | Simple configuration over the I <sup>2</sup> C interface |

| High-resolution output             | 10bit resolution                                         |

| Operates in wide magnetic range    | Programmable sensitivity                                 |

| Smallest form factor               | Available in two different packages: WLCSP & SOIC8       |

#### **Applications**

The AS5510 is ideal for:

- · Position sensing

- Servo drive feedback

- · Camera lens control

- · Closed loop position control.

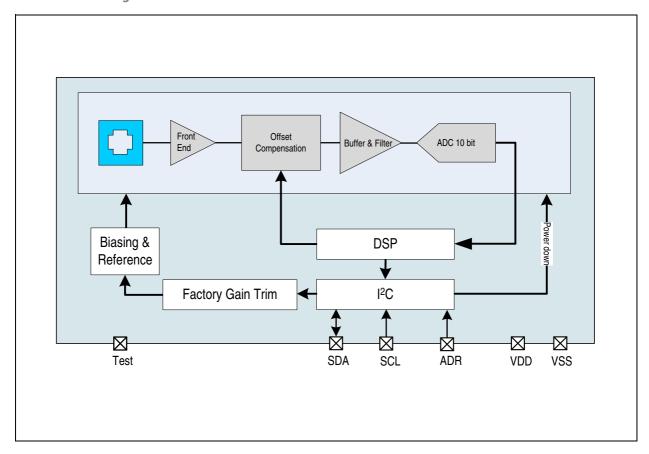

# **Block Diagram**

The functional blocks of this device for reference are shown below:

Figure 2: AS5510 Block Diagram

Page 2ams DatasheetDocument Feedback[v1-07] 2015-Feb-27

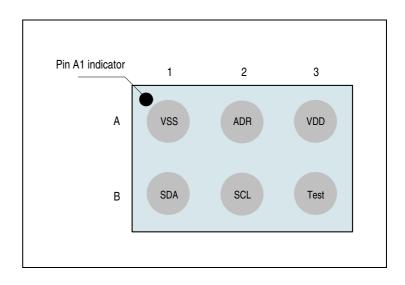

# **Pin Assignment**

#### The AS5510 pin assignments are described below.

Figure 3: Pin Diagram for WLCSP Package

# Pin Configuration of AS5510 in WLCSP Package(Top view):

The AS5510 is available in a 6-pin Chip Scale Package with a ball pitch of  $400\mu m$ .

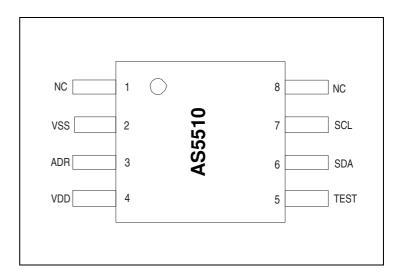

Figure 4: Pin Diagram for SOIC8 Package

# Pin Configuration of AS5510 in SOIC8 Package(Top view):

Package drawing not to scale.

ams Datasheet Page 3

[v1-07] 2015-Feb-27

Document Feedback

## Figure 5: Pin Description

| Pin  | Pin N | umber | Pin Type                                     | Description                                                                        |

|------|-------|-------|----------------------------------------------|------------------------------------------------------------------------------------|

| Name | WLCSP | SOIC8 | i iii iype                                   | Description                                                                        |

| NC   | -     | 1     | -                                            | Not Connected                                                                      |

| VSS  | A1    | 2     | Supply pin                                   | Negative supply pin, analog and digital ground                                     |

| ADR  | A2    | 3     | Digital input                                | I <sup>2</sup> C address selection pin<br>Connect to either VSS (56h) or VDD (57h) |

| VDD  | А3    | 4     | Supply pin                                   | Positive supply pin. A capacitor of 100nF should be connected to this pin and VSS  |

| Test | В3    | 5     | Digital input/output                         | Test pin, must be connected to VSS during operation                                |

| SDA  | B1    | 6     | Digital input / Digital<br>output open drain | I <sup>2</sup> C data I/O, 20mA driving capability                                 |

| SCL  | B2    | 7     | Digital input                                | I <sup>2</sup> C clock                                                             |

| NC   | -     | 8     | -                                            | Not Connected                                                                      |

Page 4ams DatasheetDocument Feedback[v1-07] 2015-Feb-27

# **Absolute Maximum Ratings**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in Electrical Characteristics is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Figure 6: Absolute Maximum Ratings

| Parameter                                      | Min                          | Max     | Units | Comments                                                                                                      |

|------------------------------------------------|------------------------------|---------|-------|---------------------------------------------------------------------------------------------------------------|

| DC supply voltage at pin VDD                   | -0.3                         | 5       | V     |                                                                                                               |

| Input pin voltage                              | -0.3                         | VDD+0.3 | V     |                                                                                                               |

| Input current (latchup immunity)               | -100                         | 100     | mA    | Norm: JEDEC 78                                                                                                |

| Electrostatic discharge                        | ±2                           |         | kV    | Norm: MIL 883 E method 3015                                                                                   |

| Storage temperature                            | -55                          | 125     | °C    |                                                                                                               |

| Body temperature (Lead-free package) for WLCSP |                              | 260     |       | The reflow peak soldering temperature (body temperature) specified is in accordance with IPC/ JEDEC J-STD-020 |

| Body temperature (Lead-free package) for SOIC8 | T <sub>Body</sub>            | 260     | °C    | "Moisture/Reflow Sensitivity Classification for Non-Hermetic Solid State Surface Mount Devices".              |

| Relative Humidity non-condensing               | 5                            | 85      | %     |                                                                                                               |

| Moisture Sensitivity Level for WLCSP           | 1                            |         |       | Represents a max. floor life time of                                                                          |

| Moisture Sensitivity Level for SOIC8           | ensitivity Level for SOIC8 3 |         |       | unlimited                                                                                                     |

ams Datasheet Page 5

[v1-07] 2015-Feb-27

Document Feedback

# **Electrical Characteristics**

Figure 7: Operating Conditions

| Symbol            | Parameter                 | Conditions                 | Min | Тур | Max | Units |

|-------------------|---------------------------|----------------------------|-----|-----|-----|-------|

| VDD               | Supply voltage at pin VDD |                            | 2.5 | 3   | 3.6 | V     |

| I <sub>supp</sub> | Supply current            | @ 25°C ambient temperature |     | 3.5 |     | mA    |

| I <sub>pd</sub>   | Power down current        | @ 25 Cambient temperature  |     | 25  |     | μА    |

| T <sub>amb</sub>  | Ambient temperature       |                            | -30 |     | 85  | °C    |

# DC Characteristics for Digital Inputs and Outputs

**CMOS Input: ADR**

Operating conditions:  $T_{amb} = -30^{\circ}\text{C}$  to  $85^{\circ}\text{C}$ , VDD = 2.5V to 3.6V (3V operation) unless otherwise noted.

Figure 8: Electrical Characteristics ADR Input

| Symbol            | Parameter                | Min       | Тур | Max       | Units |

|-------------------|--------------------------|-----------|-----|-----------|-------|

| V <sub>IH</sub>   | High level input voltage | 0.7 * VDD |     | VDD       | V     |

| V <sub>IL</sub>   | Low level input voltage  | 0         |     | 0.3 * VDD | V     |

| I <sub>LEAK</sub> | Input leakage current    | -1        |     | 1         | μΑ    |

Page 6ams DatasheetDocument Feedback[v1-07] 2015-Feb-27

## CMOS I<sup>2</sup>C: SDA, SCL

Operating conditions: Tamb = -30°C to 85°C, VDD = 2.5V to 3.6V (3V operation) unless otherwise noted.

Figure 9: **Electrical Characteristics I<sup>2</sup>C**

| Symbol           | Parameter                                                                         | Conditions | Min        | Max                | Units |

|------------------|-----------------------------------------------------------------------------------|------------|------------|--------------------|-------|

| V <sub>IL</sub>  | LOW-level input voltage                                                           |            | -0.5       | 0.3 * VDD          | V     |

| V <sub>IH</sub>  | HIGH-level input voltage                                                          |            | 0.7 * VDD  | VDD +0.5V          | V     |

| V <sub>hys</sub> | Hysteresis of Schmitt Trigger inputs                                              | VDD > 2.5V | 0.05 * VDD |                    | V     |

| V <sub>OL</sub>  | LOW-level output voltage<br>(open-drain or open-collector) at<br>3mA sink current | VDD > 2.5V |            | 0.4V               | V     |

| I <sub>OL</sub>  | LOW-level output current                                                          | VOL = 0.4V | 20         |                    | mA    |

| t <sub>of</sub>  | Output fall time from $V_{IHmax}$ to $V_{ILmax}$                                  |            |            | 120 <sup>(1)</sup> | ns    |

| t <sub>SP</sub>  | Pulse width of spikes that must be suppressed by the input filter                 |            |            | 50 <sup>(2)</sup>  | ns    |

| l <sub>i</sub>   | Input current at each I/O pin                                                     |            | -10        | +10 (3)            | μΑ    |

| C <sub>B</sub>   | Total capacitive load for each bus line                                           |            |            | 550                | pF    |

| C <sub>I/O</sub> | I/O capacitance (SDA, SCL) (4)                                                    |            |            | 10                 | pF    |

#### Note(s) and/or Footnote(s):

- 1. In Fast-mode Plus, fall time is specified the same for both output stage and bus timing. If series resistors are used this has to be considered for bus timing.

- 2. Input filters on the SDA and SCL inputs suppress noise spikes of less than 50 ns.  $\,$

- 3. I/O pins of Fast-mode and Fast-mode plus devices must not obstruct the SDA and SCL lines if VDD is switched OFF.

- 4. Special purpose devices such as multiplexers and switches may exceed this capacitance due to the fact that they connect multiple paths together.

ams Datasheet Page 7 **Document Feedback**

# **Electrical and Magnetic Specifications**

Figure 10: Electrical and Magnetic Specifications

| Symbol                | Parameter                                 | Conditions                                                                                                                              | Тур    | Max  | Units |

|-----------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------|------|-------|

| RES                   | Resolution                                |                                                                                                                                         | 10     |      | bit   |

|                       |                                           | Default Setting                                                                                                                         | ±50    |      | mT    |

| Bin                   | Magnetic Input Range                      |                                                                                                                                         | ±25    |      | mT    |

| Dill                  | Magnetic input hange                      | Configurable via I <sup>2</sup> C or factory trimming option                                                                            | ±12.5  |      | mT    |

|                       |                                           |                                                                                                                                         | ±18.75 |      | mT    |

| Offset <sub>inp</sub> | Input related offset (1)                  |                                                                                                                                         |        | 0.45 | mT    |

|                       | Linearity error (2)                       |                                                                                                                                         |        | 3    | %     |

| t <sub>PwrUp</sub>    | Initial Power up time from cold start (3) | This time is needed for the first power-up of the device until the offset compensation is finished; Includes readout of the PPROM fuses |        | 1.5  | ms    |

| t <sub>PwrOn</sub>    | Power-on time <sup>(4)</sup>              | Time after switching from power-down mode into active mode until the offset compensation is finished                                    | 250    |      | μs    |

Page 8ams DatasheetDocument Feedback[v1-07] 2015-Feb-27

| Symbol               | Parameter                                     | Conditions                                | Тур | Max  | Units |  |  |  |

|----------------------|-----------------------------------------------|-------------------------------------------|-----|------|-------|--|--|--|

|                      | Fast Mode (Default setting)                   |                                           |     |      |       |  |  |  |

| f <sub>S</sub>       | ADC sampling frequency                        | After offset compensation finished        |     | 50   | KHz   |  |  |  |

| t <sub>delay</sub>   | System propagation delay                      | Arter offset compensation imistica        |     | 20   | μs    |  |  |  |

| Noise <sub>inp</sub> | Input related noise (5)                       | Equivalent to 8 * rms                     |     | 0.8  | mTpp  |  |  |  |

|                      | SI                                            | ow Mode (I <sup>2</sup> C command option) |     |      |       |  |  |  |

| f <sub>S</sub>       | ADC sampling frequency                        | After offset compensation finished        |     | 12.5 | KHz   |  |  |  |

| t <sub>delay</sub>   | System propagation delay                      | , act office compensation infinited       |     | 50   | μs    |  |  |  |

| Noise <sub>inp</sub> | Input related noise (5) Equivalent to 8 * rms |                                           |     | 0.5  | mTpp  |  |  |  |

#### Note(s) and/or Footnote(s):

$1.\ Offset_{inp} = 0.35mT\ residual\ offset + 0.1mT\ earth\ magnetic\ field.$

2. Linearity error =

$$\lim_{n \to \infty} error = 1 - \left(\frac{\text{adc}_{\text{out}}(\text{maxB}) - \text{adc}_{\text{out}}(\text{zeroB})}{2 \times \left(\text{adc}_{\text{out}}\left(\frac{\text{maxB}}{2}\right) - \text{adc}_{\text{out}}(\text{zeroB})\right)}\right) \times 100$$

- 3. This time is needed for the first power-up of the device until the offset compensation is finished; Includes readout of the PPROM fuses; It depends on the sensitivity setting.

- 4. Time after switching from power-down mode into active mode until the offset compensation is finished.

- 5. Input related Noise (Noise  $_{\mbox{\scriptsize lnp}})$  is the repeatability of the measurement.

ams Datasheet Page 9

[v1-07] 2015-Feb-27

Document Feedback

# **Detailed Description**

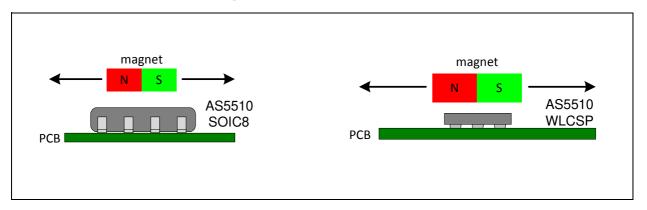

Figure 11: Linear Position Sensor AS5510 + Magnet

**Linear Position Sensor AS5510 + Magnet:** The AS5510 can measure the absolute position of lateral movement in combination with a diametrical two pole magnet.

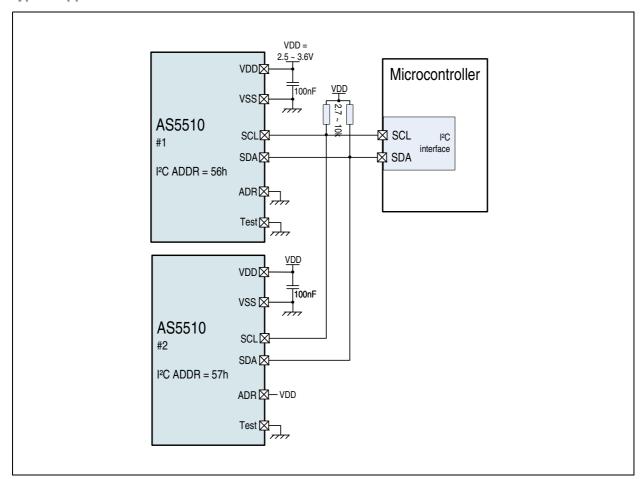

## **Typical Application**

The typical application circuit of AS5510 is shown below:

Figure 12:

Typical Application Circuit

Page 10

Document Feedback

[v1-07] 2015-Feb-27

#### I<sup>2</sup>C Interface

The AS5510 includes an I<sup>2</sup>C slave according to the NXP specification UM10204.

- 7-bit slave address **101011x**, the last address bit x is set by the ADR pin (0 or 1)

- · Random/Sequential Read

- Byte/Page Write

- Fast-mode plus with 20mA SDA drive strength

- Internal hold time of 120ns for SDA signal is included (Start/Stop detection)

#### Not implemented:

- 10-bit Slave Address

- · Clock Stretching

- General Call Address

- General Call Software Reset

- Read of Device ID

The communication from the AS5510 includes:

- Reading the magnetic field strength in 10-bit data

- Reading the status bits

**Note(s):** The I<sup>2</sup>C address of the chip is selected by hardware (pin ADR). Depending on the state of this pin, the I<sup>2</sup>C address is either:

- Pin ADR = LOW  $\rightarrow$  I<sup>2</sup>C address = 1010110b(56h)

- Pin ADR = HIGH  $\rightarrow$  I<sup>2</sup>C address = 1010111b(57h)

ams Datasheet Page 11

[v1-07] 2015-Feb-27 Document Feedback

#### I<sup>2</sup>C Interface Data

Operating conditions: Tamb = -30 to 85°C, VDD=2.5 to 3.6V (3V operation) unless otherwise noted.

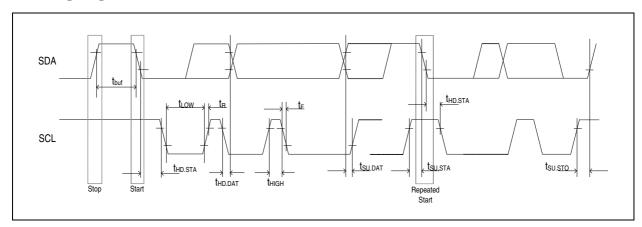

Figure 13: I<sup>2</sup>C Timings

| Symbol              | Parameter                                            | Min  | Тур | Max  | Units |

|---------------------|------------------------------------------------------|------|-----|------|-------|

| f <sub>SCLK</sub>   | SCL clock frequency                                  |      |     | 1    | MHz   |

| t <sub>BUF</sub>    | Bus free time; time between STOP and START condition | 0.5  |     |      | μs    |

| t <sub>HD.STA</sub> | Hold time; (repeated) START condition <sup>(1)</sup> | 0.26 |     |      | μs    |

| t <sub>LOW</sub>    | LOW period of SCL clock                              | 0.5  |     |      | μs    |

| t <sub>HIGH</sub>   | HIGH period of SCL clock                             | 0.26 |     |      | μs    |

| t <sub>SU.STA</sub> | Setup time for a repeated START condition            | 0.26 |     |      | μs    |

| t <sub>HD.DAT</sub> | Data hold time <sup>(2)</sup>                        |      |     | 0.45 | μs    |

| t <sub>SU.DAT</sub> | Data setup time <sup>(3)</sup>                       | 50   |     |      | ns    |

| t <sub>R</sub>      | Rise time of SDA and SCL signals                     |      |     | 120  | ns    |

| t <sub>F</sub>      | Fall time of SDA and SCL signals <sup>(4)</sup>      |      |     | 120  | ns    |

| t <sub>SU.STO</sub> | Setup time for STOP condition                        | 0.26 |     |      | μs    |

#### Note(s) and/or Footnote(s):

- 1. After this time the first clock is generated.

- $2.\ A\ device\ must internally\ provide\ a\ hold\ time\ of\ at\ least\ 120ns\ (Fast-mode\ Plus)\ for\ the\ SDA\ signal\ (referred\ to\ the\ V_{IHmin}\ of\ the\ SCL)$ to bridge the undefined region of the falling edge of SCL.

- $3.\,A fast-mode\,device\,can\,be\,used\,in\,standard-mode\,system, but\,the\,requirement\,t_{SU,DAT}=250 ns\,must\,then\,be\,met.\,This\,is\,automatically$ the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line  $t_{Rmax} + T_{SU.DAT} = 1000 + 250 = 1250$ ns before the SCL line is released.

- 4. In Fast-mode Plus, fall time is specified the same for both output stage and bus timing. If series resistors are used this has to be considered for bus timing.

Page 12 ams Datasheet [v1-07] 2015-Feb-27

Figure 14: I<sup>2</sup>C Timing Diagram

#### I<sup>2</sup>C Modes

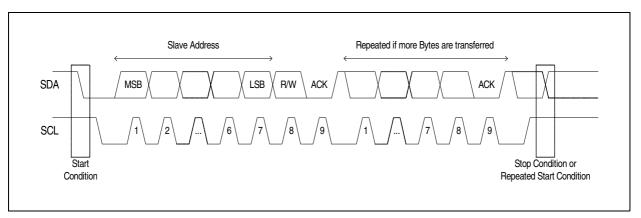

The AS5510 supports the I<sup>2</sup>C bus protocol. A device that sends data onto the bus is defined as a transmitter and a device receiving data as a receiver. The device that controls the message is called a master. The devices that are controlled by the master are referred to as slaves. A master device that generates the serial clock (SCL), controls the bus access and generates the START and STOP conditions must control the bus. The AS5510 operates as a slave on the I<sup>2</sup>C bus. Within the bus specifications a standard mode (100 kHz maximum clock rate) a fast mode (400 kHz maximum clock rate) and fast mode plus (1MHz maximum clock rate) are defined. The AS5510 works in all three modes. Connections to the bus are made through the open-drain I/O lines SDA and the input SCL. Clock stretching is not included.

The following bus protocol has been defined:

- Data transfer may be initiated only when the bus is not busy

- During data transfer, the data line must remain stable whenever the clock line is HIGH. Changes in the data line while the clock line is HIGH are interpreted as start or stop signals.

Accordingly, the following bus conditions have been defined:

#### **Bus Not Busy**

Both data and clock lines remain HIGH.

#### Start Data Transfer

A change in the state of the data line, from HIGH to LOW, while the clock is HIGH, defines a START condition.

#### Stop Data Transfer

A change in the state of the data line, from LOW to HIGH, while the clock line is HIGH, defines the STOP condition.

ams Datasheet Page 13

[v1-07] 2015-Feb-27 Document Feedback

#### Data Valid

The state of the data line represents valid data when, after a START condition, the data line is stable for the duration of the HIGH period of the clock signal. The data on the line must be changed during the LOW period of the clock signal. There is one clock pulse per bit of data. Each data transfer is initiated with a START condition and terminated with a STOP condition. The number of data bytes transferred between START and STOP conditions are not limited, and are determined by the master device. The information is transferred byte-wise and each receiver acknowledges with a ninth bit.

#### Acknowledge

Each receiving device, when addressed, is obliged to generate an acknowledge bit after the reception of each byte. The master device must generate an extra clock pulse that is associated with this acknowledge bit. A device that acknowledges must pull down the SDA line during the acknowledge clock pulse in such a way that the SDA line is stable LOW during the HIGH period of the acknowledge-related clock pulse. Of course, setup and hold times must be taken into account. A master must signal an end of READ access to the slave by not generating an acknowledge bit on the last byte that has been clocked out of the slave. In this case, the slave must leave the data line HIGH to enable the master to generate the STOP condition.

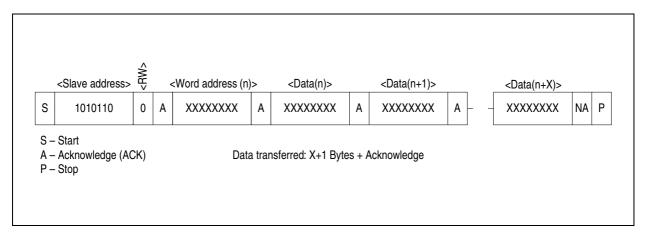

Figure 15:

Data Read (Write Pointer, Then Read) - Slave Receive and Transmit

Depending upon the state of the R/W bit, two types of data transfer are possible:

# Data transfer from a Master Transmitter to a Slave Receiver.

The first byte transmitted by the master is the slave address, followed by R/W=0. Next follows a number of data bytes. The slave returns an acknowledge bit after each received byte. If the slave does not understand the command or data it sends a "not acknowledge". Data is transferred with the most significant bit (MSB) first.

Page 14

Document Feedback [v1-07] 2015-Feb-27

# Data transfer from a Slave Transmitter to a Master Receiver.

The master transmits the first byte (the slave address). The slave then returns an acknowledge bit, followed by the slave transmitting a number of data bytes. The master returns an acknowledge bit after all received bytes other than the last byte. At the end of the last received byte, a "not acknowledge" is returned. The master device generates all of the serial clock pulses and the START and STOP conditions. A transfer is ended with a STOP condition or with a repeated START condition. Since a repeated START condition is also the beginning of the next serial transfer, the bus is not released. Data is transferred with the most significant bit (MSB) first.

The AS5510 can operate in the following two modes:

#### Slave Receiver Mode (Write Mode)

Serial data and clock are received through SDA and SCL. Each byte is followed by an acknowledge bit (or by a not acknowledge depending on the address-pointer pointing to a valid position). START and STOP conditions are recognized as the beginning and end of a serial transfer. Address recognition is performed by hardware after reception of the slave address and direction bit (see Figure 16). The slave address byte is the first byte received after the START condition. The slave address byte contains the 7-bit AS5510 address. The 7-bit slave address is followed by the direction bit (R/W), which, for a write, is 0. After receiving and decoding the slave address byte the device outputs an acknowledge on the SDA. After the AS5510 acknowledges the slave address + write bit, the master transmits a register address to the AS5510. This sets the address pointer on the AS5510. If the address is a valid readable address the AS5510 answers by sending an acknowledge. If the address-pointer points to an invalid position a "not acknowledge" is sent. The master may then transmit zero or more bytes of data. In case of the address pointer pointing to an invalid address the received data are not stored. The address pointer will increment after each byte transferred independent from the address being valid. If the address-pointer reaches a valid position again, the AS5510 answers with an acknowledge and stores the data. The master generates a STOP condition to terminate the data write.

ams Datasheet Page 15

[v1-07] 2015-Feb-27 Document Feedback

Figure 16:

Data Write - Slave Receiver Mode

Page 16ams DatasheetDocument Feedback[v1-07] 2015-Feb-27

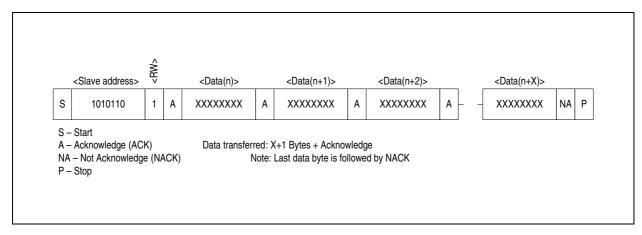

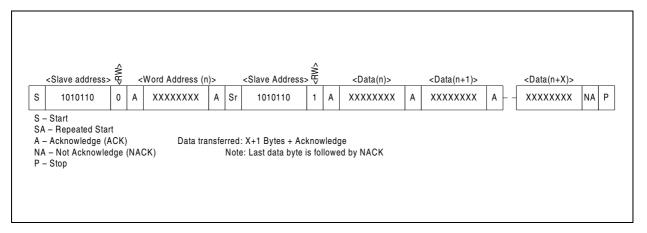

#### Slave Transmitter Mode (Read Mode)

The first byte is received and handled as in the slave receiver mode. However, in this mode, the direction bit indicates that the transfer direction is reversed. Serial data is transmitted on SDA by the AS5510 while the serial clock is input on SCL. START and STOP conditions are recognized as the beginning and end of a serial transfer (Figure 17 and Figure 18). The slave address byte is the first byte received after the master generates a START condition. The slave address byte contains the 7-bit AS5510 address. The 7-bit slave address is followed by the direction bit (R/W), which, for a read, is 1. After receiving and decoding the slave address byte the device outputs an acknowledge on the SDA line. The AS5510 then begins to transmit data starting with the register address pointed to by the register pointer. If the register pointer is not written to before the initiation of a read mode the first address that is read is the last one stored in the register pointer. The AS5510 must receive a "not acknowledge" to end a read.

Figure 17:

Data Read (from Current Pointer Location) - Slave Transmitter Mode

Figure 18:

Data Read (Write Pointer, Then Read) - Slave Receive and Transmit

ams Datasheet Page 17

[v1-07] 2015-Feb-27 Document Feedback

#### **Automatic Increment of Address Pointer**

The AS5510 slave automatically increments the address pointer after each byte transferred. The increase of the address pointer is independent from the address being valid or not.

#### **Invalid Addresses**

If the user sets the address pointer to an invalid address, the address byte is not acknowledged. Nevertheless a read or write cycle is possible. The address pointer is increased after each byte.

#### Reading

When reading from a wrong address, the AS5510 slave returns all zero. The address pointer is increased after each byte. Sequential read over the whole address range is possible including address overflow.

#### Write

A write to a wrong address is not acknowledged by the AS5510 slave, although the address pointer is increased. When the address pointer points to a valid address again, a successful write accessed is acknowledged. Page write over the whole address range is possible including address overflow.

#### **SDA, SCL Input Filters**

Input filters for SDA and SCL inputs are included to suppress noise spikes of less than 50ns. Furthermore the SDA line is delayed by 120ns to provide an internal hold time for Start/Stop detection to bridge the undefined region of the falling edge of SCL. The delay needs to be smaller than tHD.STA 260ns. For Standard-mode and Fast-mode an internal hold time of 300ns is required, which is not covered by the AS5510 slave.

Page 18

Document Feedback

[v1-07] 2015-Feb-27

# **Register Description**

Figure 19: Register Map (1)

| Register | Bit   |       |       |       |       |                             | Access      |        |      |

|----------|-------|-------|-------|-------|-------|-----------------------------|-------------|--------|------|

| Address  | 7     | 6     | 5     | 4     | 3     | 2                           | 1           | 0      | Type |

| 00h      | D7    | D6    | D5    | D4    | D3    | D2                          | D1          | D0     | R    |

| 01h      |       |       |       |       | OCF   | Parity<br>(even)            | D9          | D8     | R    |

| 02h      |       |       |       |       |       | Fast(0)<br>Slow<br>mode (1) | Polarity(0) | PD(0)  | R/W  |

| 03h      | Offs7 | Offs6 | Offs5 | Offs4 | Offs3 | Offs2                       | Offs1       | Offs0  | R/W  |

| 04h      |       |       |       |       |       |                             | Offs9       | Offs8  | R/W  |

| 0Bh      |       |       |       |       |       |                             | Sens 1      | Sens 0 | R/W  |

#### Note(s) and/or Footnote(s):

ams Datasheet Page 19 Document Feedback

<sup>1.</sup> Blank or not listed fields may contain factory settings. To change a configuration, read out the register, modify only the desired bits and write the new configuration.

## Figure 20: Register Description

| Register Address | Name             | Description                                                                                                                                                                                                                                                                                                                      |

|------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00h, 01h         | D9 to D0         | 10 Bit ADC output value that corresponds to the magnetic field input                                                                                                                                                                                                                                                             |

| 01h              | Parity           | Even parity bit calculated from D9 to D0                                                                                                                                                                                                                                                                                         |

| 01h              | OCF              | Offset compensation loop status  0 = Offset compensation loop in use  1 = Offset compensation loop has finished                                                                                                                                                                                                                  |

| 02h              | PD               | Power down mode 0 = Normal operation (Default) 1 = Power Down mode.                                                                                                                                                                                                                                                              |

| 02h              | Polarity         | Output signal polarity 0 = Normal polarity (Default) 1 = Reversed polarity (reversed magnet)                                                                                                                                                                                                                                     |

| 02h              | Fast / Slow mode | 0 = Fast mode (Default) 1 = Slow mode. Enables averaging of the output values (reduced noise, better repeatability slower sampling frequency. See Electrical and Magnetic Specifications                                                                                                                                         |

| 03h, 04h         | Offs9 to Offs0   | Contains the offset compensation value. For read access only.  Don't modify the register values.                                                                                                                                                                                                                                 |

| 0Bh              | Sensitivity      | Sensitivity setting $0h = Input \ range \pm 50mT \rightarrow Sensitivity = 97.66\mu T/LSB \ (Default)$ $1h = Input \ range \pm 25mT \rightarrow Sensitivity = 48.83\mu T/LSB$ $2h = Input \ range \pm 12.5mT \rightarrow Sensitivity = 24.41\mu T/LSB$ $3h = Input \ range \pm 18.75mT \rightarrow Sensitivity = 36.62\mu T/LSB$ |

Page 20ams DatasheetDocument Feedback[v1-07] 2015-Feb-27

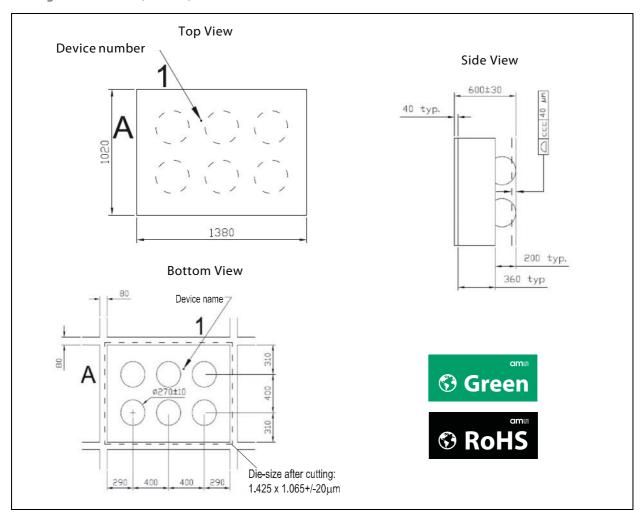

# **Package Drawings & Markings**

# **WLCSP Package**

The WLCSP package drawings and markings are shown below:

Figure 21: Package Dimensions (WLCSP)

#### Note(s) and/or Footnote(s):

- 1. ccc Coplanarity

- 2. All dimensions in  $\mu\text{m}$

ams Datasheet Page 21

[v1-07] 2015-Feb-27 Document Feedback

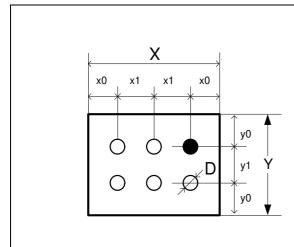

Figure 22: Recommended Footprint

| Package Dimensions |            |    |  |  |  |  |

|--------------------|------------|----|--|--|--|--|

| Symbol             | Symbol Typ |    |  |  |  |  |

| Х                  | 1460       | μm |  |  |  |  |

| х0                 | 330        | μm |  |  |  |  |

| x1                 | 400        | μm |  |  |  |  |

| Y                  | 1100       | μm |  |  |  |  |

| y0                 | 350        | μm |  |  |  |  |

| у1                 | 400        | μm |  |  |  |  |

| D                  | 270        | μm |  |  |  |  |

Figure 23: Package Marking (WLCSP)

Figure 24: Package Code XXXX

| XXXX      |  |

|-----------|--|

| Tracecode |  |

Page 22ams DatasheetDocument Feedback[v1-07] 2015-Feb-27

# **SOIC8 Package**

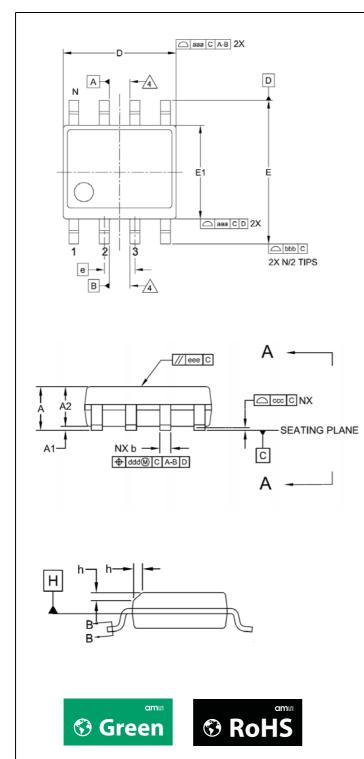

The SOIC8 package drawings and markings are shown below:

Figure 25: Package Dimensions SOIC8

| Symbol | Min  | Nom      | Max  |

|--------|------|----------|------|

| A      | _    | _        | 1.75 |

| A1     | 0.10 | _        | 0.25 |

|        |      | -        | 0.25 |

| A2     | 1.25 | -        | -    |

| b      | 0.31 | -        | 0.51 |

| С      | 0.17 | -        | 0.25 |

| D      | -    | 4.90 BSC | -    |

| E      | -    | 6.00 BSC | -    |

| E1     | -    | 3.90 BSC | -    |

| е      | -    | 1.27 BSC | -    |

| L      | 0.40 | -        | 1.27 |

| L1     | -    | 1.04 REF | -    |

| L2     | =    | 0.25 BSC | -    |

| R      | 0.07 | -        | -    |

| R1     | 0.07 | -        | -    |

| h      | 0.25 | -        | 0.50 |

| Θ      | 0°   | -        | 8°   |

| Θ1     | 5°   | -        | 15°  |

| Θ2     | 0°   | -        | -    |

| aaa    | =    | 0.10     | -    |

| bbb    | =    | 0.20     | -    |

| ccc    | -    | 0.10     | -    |

| ddd    | -    | 0.25     | -    |

| eee    | -    | 0.10     | -    |

| fff    | -    | 0.15     | -    |

| ggg    | -    | 0.15     | -    |

| N      |      | 8        |      |

Figure 26: Package Marking (SOIC8)

Figure 27:

Package Code XXX@

| XXX       | @                 |  |

|-----------|-------------------|--|

| Tracecode | Sublot Identifier |  |

Page 24ams DatasheetDocument Feedback[v1-07] 2015-Feb-27

## **Ordering & Contact Information**

The devices are available as the standard products shown in the figure below.

Figure 28: Ordering Information

| Ordering Code | Package               | Marking | Delivery Form | Delivery Quantity |

|---------------|-----------------------|---------|---------------|-------------------|

| AS5510-DWLT   | 6pin WL-CSP 1.4x1.1mm | AS5510  | Tape & Reel   | 12.000pcs         |

| AS5510-DWLM   | 6pin WL-CSP 1.4x1.1mm | AS5510  | Mini Reel     | 1000pcs           |

| AS5510-DSOT   | 8pin SOIC             | AS5510  | Tape & Reel   | 2.500pcs          |

| AS5510-DSOM   | 8pin SOIC             | AS5510  | Mini Reel     | 500pcs            |

D → Temperature Range: -30°C to 85°C

$WL \rightarrow Package: WL-CSP Wafer Level - Chip Scale Package$

$SO \rightarrow Package: SOIC 8$

$T \rightarrow$  Delivery Form: Tape & Reel  $M \rightarrow$  Delivery Form: Mini Reel

Buy our products or get free samples online at:

www.ams.com/ICdirect

Technical Support is available at: www.ams.com/Technical-Support

Provide feedback about this document at:

www.ams.com/Document-Feedback

For further information and requests, e-mail us at:

ams\_sales@ams.com

For sales offices, distributors and representatives, please visit: www.ams.com/contact

#### Headquarters

ams AG Tobelbaderstrasse 30 8141 Unterpremstaetten Austria, Europe

Tel: +43 (0) 3136 500 0 Website: www.ams.com

ams Datasheet Page 25

[v1-07] 2015-Feb-27 Document Feedback