# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# AS7262

6-Channel Visible *Spectral\_ID* Device with Electronic Shutter and Smart Interface

### **General Description**

The AS7262 is a cost-effective multi-spectral sensor-on-chip solution designed to address spectral ID applications. This highly integrated device delivers 6-channel multi-spectral sensing in the visible wavelengths from approximately 430nm to 670nm with full-width half-max (FWHM) of 40nm. An integrated LED driver with programmable current is provided for electronic shutter applications.

The AS7262 integrates Gaussian filters into standard CMOS silicon via nano-optic deposited interference filter technology and is packaged in an LGA package that provides a built in aperture to control the light entering the sensor array.

Control and spectral data access is implemented through either the I<sup>2</sup>C register set, or with a high level AT Spectral Command set via a serial UART.

Ordering Information and Content Guide appear at end of datasheet.

#### **Key Benefits & Features**

The benefits and features of AS7262, 6-Channel Visible *Spectral\_ID* Device with Electronic Shutter and Smart Interface are listed below:

Figure 1: Added Value of Using AS7262

| Benefits                                                                                                                                                            | Features                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

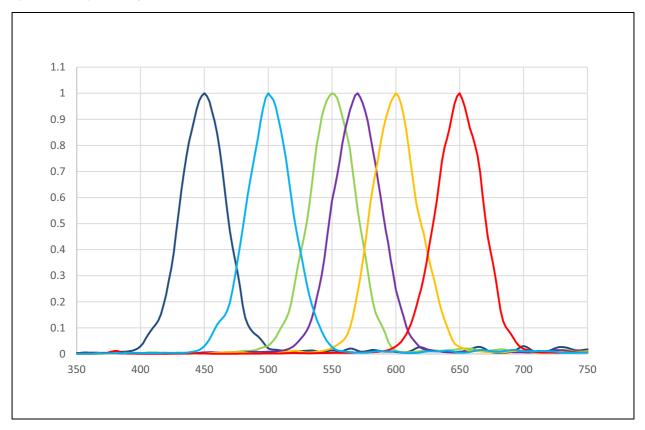

| Compact 6-channel spectrometry solution                                                                                                                             | <ul> <li>6 visible channels: 450nm, 500nm, 550nm, 570nm,<br/>600nm and 650nm, each with 40nm FWHM</li> </ul> |

| <ul> <li>Simple text-based command interface via<br/>UART, or direct register read and write with<br/>interrupt on sensor ready option on I<sup>2</sup>C</li> </ul> | UART or I <sup>2</sup> C slave digital Interface                                                             |

| Lifetime-calibrated sensing with minimal drift over time or temperature                                                                                             | Visible filter set realized by silicon interference filters                                                  |

| No additional signal conditioning required                                                                                                                          | 16-bit ADC with digital access                                                                               |

| Electronic shutter control/synchronization                                                                                                                          | Programmable LED drivers                                                                                     |

| Low voltage operation                                                                                                                                               | • 2.7V to 3.6V with I <sup>2</sup> C interface                                                               |

| Small, robust package, with built-in aperture                                                                                                                       | <ul> <li>20-pin LGA package 4.5mm x 4.7mm x 2.5mm</li> <li>-40°C to 85°C temperature range</li> </ul>        |

### Applications

The AS7262 applications include:

- Portable spectrometry

- Horticulture

- Color matching and identification

- Authentication and brand protection

- Precision color tuning/calibration

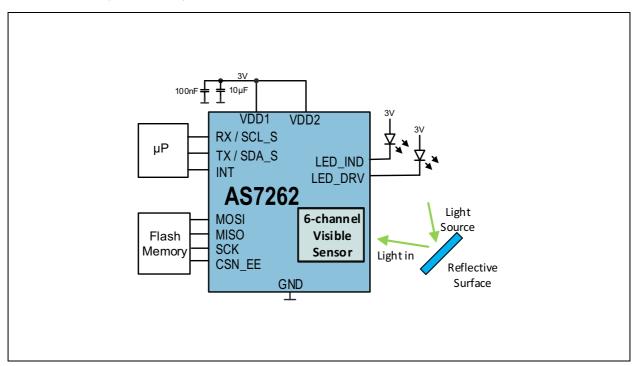

### **Block Diagram**

The system blocks of this device are shown below.

Figure 2: AS7262 Visible *Spectral\_ID* System

## **Pin Assignments**

#### The device pin assignments are described below.

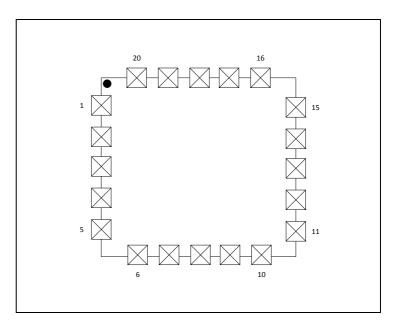

Figure 3: Pin Diagram of AS7262 (Top View)

#### Figure 4: Pin Description of AS7262

| Pin Number | Pin Name             | Description                                                                   |

|------------|----------------------|-------------------------------------------------------------------------------|

| 1          | NF                   | Not Functional. Do not connect.                                               |

| 2          | RESN                 | Reset, Active LOW                                                             |

| 3          | SCK                  | SPI Serial Clock                                                              |

| 4          | MOSI                 | SPI Master Out Slave In                                                       |

| 5          | MISO                 | SPI Master In Slave Out                                                       |

| 6          | CSN_EE               | Chip Select for external serial Flash memory, Active LOW                      |

| 7          | CSN_SD               | Chip Select for SD Card Interface, Active LOW                                 |

| 8          | I <sup>2</sup> C_ENB | Select UART (Low) or I <sup>2</sup> C (High) Operation                        |

| 9          | NF                   | Not Functional. Do not connect.                                               |

| 10         | NF                   | Not Functional. Do not connect.                                               |

| 11         | RX/SCL_S             | RX (UART) or SCL_S (I <sup>2</sup> C Slave) Depending on I <sup>2</sup> C_ENB |

| 12         | TX/SDA_S             | TX (UART) or SDA_S (I <sup>2</sup> C Slave) Depending on I <sup>2</sup> C_ENB |

| 13         | INT                  | Interrupt, Active LOW                                                         |

| 14         | VDD2                 | Voltage Supply                                                                |

| Pin Number | Pin Name | Description                                       |

|------------|----------|---------------------------------------------------|

| 15         | LED_DRV  | LED Driver Output for Driving LED, Current Sink   |

| 16         | GND      | Ground                                            |

| 17         | VDD1     | Voltage Supply                                    |

| 18         | LED_IND  | LED Driver Output for Indicator LED, Current Sink |

| 19         | NF       | Not Functional. Do not connect.                   |

| 20         | NF       | Not Functional. Do not connect.                   |

### Absolute Maximum Ratings

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under Electrical Characteristics is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

The device is not designed for high energy UV (ultraviolet) environments, including upward looking outdoor applications, which could affect long term optical performance.

#### Figure 5:

Absolute Maximum Ratings of AS7262

| Symbol               | Parameter                             | Min          | Max         | Units     | Comments                                                                                                                                                                                                                                            |    |         |  |  |

|----------------------|---------------------------------------|--------------|-------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|---------|--|--|

|                      | E                                     | lectrical Pa | rameters    |           |                                                                                                                                                                                                                                                     |    |         |  |  |

| V <sub>DD1_MAX</sub> | Supply Voltage VDD1                   | -0.3         | 5           | V         | Pin VDD1 to GND                                                                                                                                                                                                                                     |    |         |  |  |

| V <sub>DD2_MAX</sub> | Supply Voltage VDD2                   | -0.3         | 5           | V         | Pin VDD2 to GND                                                                                                                                                                                                                                     |    |         |  |  |

| V <sub>DD_IO</sub>   | Input/Output Pin Voltage              | -0.3         | VDD+0.3     | V         | Input/Output Pin to GND                                                                                                                                                                                                                             |    |         |  |  |

| I <sub>SCR</sub>     | Input Current<br>(latch-up immunity)  | ± 100        |             | ± 100     |                                                                                                                                                                                                                                                     | mA | JESD78D |  |  |

|                      | Electrostatic Discharge               |              |             |           |                                                                                                                                                                                                                                                     |    |         |  |  |

| ESD <sub>HBM</sub>   | Electrostatic Discharge HBM           | ± 1          | 000         | V         | JS-001-2014                                                                                                                                                                                                                                         |    |         |  |  |

| ESD <sub>CDM</sub>   | Electrostatic Discharge CDM           | ±            | 500         | V         | JSD22-C101F                                                                                                                                                                                                                                         |    |         |  |  |

|                      | Temperature                           | Ranges an    | d Storage C | onditions |                                                                                                                                                                                                                                                     |    |         |  |  |

| T <sub>STRG</sub>    | Storage Temperature Range             | -40          | 85          | °C        |                                                                                                                                                                                                                                                     |    |         |  |  |

| T <sub>BODY</sub>    | Package Body Temperature              |              | 260         | °C        | IPC/JEDEC J-STD-020<br>The reflow peak soldering<br>temperature (body<br>temperature) is specified<br>according to IPC/JEDEC<br>J-STD-020 "Moisture/Reflow<br>Sensitivity Classification for<br>Non-hermetic Solid State<br>Surface Mount Devices." |    |         |  |  |

| RH <sub>NC</sub>     | Relative Humidity<br>(non-condensing) | 5            | 85          | %         |                                                                                                                                                                                                                                                     |    |         |  |  |

| MSL                  | Moisture Sensitivity Level            | 3            |             |           | Maximum floor life time of<br>168 hours                                                                                                                                                                                                             |    |         |  |  |

## **Electrical Characteristics**

All limits are guaranteed with VDD = VDD1 = VDD2 = 3.3V,  $T_{AMB} = 25^{\circ}$ C. The parameters with min and max values are guaranteed with production tests or SQC (Statistical Quality Control) methods.

Figure 6:

**Electrical Characteristics of AS7262**

| Symbol                             | Parameter                                                       | Conditions                 | Min  | Тур | Max  | Unit |  |  |  |  |

|------------------------------------|-----------------------------------------------------------------|----------------------------|------|-----|------|------|--|--|--|--|

|                                    | Genera                                                          | l Operating Conditior      | าร   |     |      |      |  |  |  |  |

| VDD1 /VDD2                         | Voltage Operating Supply                                        | UART Interface             | 2.97 | 3.3 | 3.6  | V    |  |  |  |  |

| VDD1 /VDD2                         | Voltage Operating Supply                                        | I <sup>2</sup> C Interface | 2.7  | 3.3 | 3.6  | V    |  |  |  |  |

| T <sub>AMB</sub>                   | Operating Temperature                                           |                            | -40  | 25  | 85   | °C   |  |  |  |  |

| I <sub>VDD</sub>                   | Operating Current                                               |                            |      |     | 5    | mA   |  |  |  |  |

|                                    | Internal RC Oscillator                                          |                            |      |     |      |      |  |  |  |  |

| F <sub>OSC</sub>                   | Internal RC Oscillator<br>Frequency                             |                            | 15.7 | 16  | 16.3 | MHz  |  |  |  |  |

| t <sub>JITTER</sub> <sup>(1)</sup> | Internal Clock Jitter                                           | @25°C                      |      |     | 1.2  | ns   |  |  |  |  |

|                                    | Те                                                              | mperature Sensor           | 1    | 1   | 1    | 1    |  |  |  |  |

| D <sub>TEMP</sub>                  | Absolute Accuracy of the<br>Internal Temperature<br>Measurement |                            | -8.5 |     | 8.5  | °C   |  |  |  |  |

|                                    | •                                                               | Indicator LED              | 1    | 1   | I    | 1    |  |  |  |  |

| I <sub>IND</sub>                   | LED Current                                                     |                            | 1    | 4   | 8    | mA   |  |  |  |  |

| I <sub>ACC</sub>                   | Accuracy of Current                                             |                            | -30  |     | 30   | %    |  |  |  |  |

| V <sub>LED</sub>                   | Voltage Range of Connected<br>LED                               | Vds of current sink        | 0.3  |     | VDD  | V    |  |  |  |  |

|                                    | LED_DRV                                                         |                            |      |     |      |      |  |  |  |  |

| I <sub>LED1</sub>                  | LED Current                                                     | 12.5, 25, 50 or 100        | 12.5 |     | 100  | mA   |  |  |  |  |

| I <sub>ACC</sub>                   | Accuracy of Current                                             |                            | -10  |     | 10   | %    |  |  |  |  |

| V <sub>LED</sub>                   | Voltage Range of Connected<br>LED                               | Vds of current sink        | 0.3  |     | VDD  | V    |  |  |  |  |

| Symbol                            | Parameter                      | Conditions    | Min      | Тур | Мах      | Unit |  |  |  |  |

|-----------------------------------|--------------------------------|---------------|----------|-----|----------|------|--|--|--|--|

|                                   | Digital Inputs and Outputs     |               |          |     |          |      |  |  |  |  |

| I <sub>IH</sub> , I <sub>IL</sub> | Logic Input Current            | Vin=0V or VDD | -1       |     | 1        | μΑ   |  |  |  |  |

| I <sub>IL RESN</sub>              | Logic Input Current (RESN pin) | Vin=0V        | -1       |     | -0.2     | mA   |  |  |  |  |

| V <sub>IH</sub>                   | CMOS Logic High Input          |               | 0.7* VDD |     | VDD      | V    |  |  |  |  |

| V <sub>IL</sub>                   | CMOS Logic Low Input           |               | 0        |     | 0.3* VDD | V    |  |  |  |  |

| V <sub>OH</sub>                   | CMOS Logic High Output         | l=1mA         |          |     | VDD-0.4  | V    |  |  |  |  |

| V <sub>OL</sub>                   | CMOS Logic Low Output          | l=1mA         |          |     | 0.4      | V    |  |  |  |  |

| t <sub>RISE</sub> (1)             | Current Rise Time              | C(Pad)=30pF   |          |     | 5        | ns   |  |  |  |  |

| t <sub>FALL</sub> <sup>(1)</sup>  | Current Fall Time              | C(Pad)=30pF   |          |     | 5        | ns   |  |  |  |  |

#### Note(s):

1. Guaranteed, not tested in production

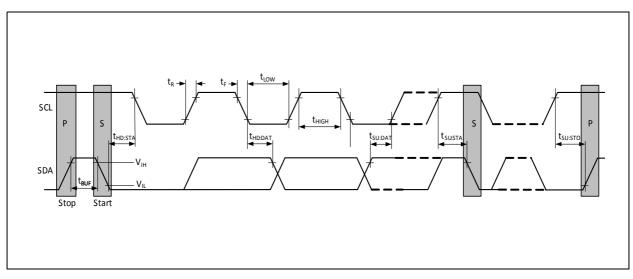

## **Timing Characteristics**

Figure 7:

AS7262 I<sup>2</sup>C Slave Timing Characteristics

| Symbol              | Parameter Conditions                      |                                              | Min | Тур | Мах | Unit |  |  |  |  |

|---------------------|-------------------------------------------|----------------------------------------------|-----|-----|-----|------|--|--|--|--|

|                     | l <sup>2</sup> C Interface                |                                              |     |     |     |      |  |  |  |  |

| f <sub>SCLK</sub>   | SCL Clock Frequency                       |                                              | 0   |     | 400 | kHz  |  |  |  |  |

| t <sub>BUF</sub>    | Bus Free Time Between a STOP<br>and START |                                              | 1.3 |     |     | μs   |  |  |  |  |

| t <sub>HS:STA</sub> | Hold Time (Repeated) START                |                                              | 0.6 |     |     | μs   |  |  |  |  |

| t <sub>LOW</sub>    | LOW Period of SCL Clock                   |                                              | 1.3 |     |     | μs   |  |  |  |  |

| t <sub>HIGH</sub>   | HIGH Period of SCL Clock                  |                                              | 0.6 |     |     | μs   |  |  |  |  |

| t <sub>SU:STA</sub> | Setup Time for a Repeated START           |                                              | 0.6 |     |     | μs   |  |  |  |  |

| t <sub>HS:DAT</sub> | Data Hold Time                            |                                              | 0   |     | 0.9 | μs   |  |  |  |  |

| t <sub>SU:DAT</sub> | Data Setup Time                           |                                              | 100 |     |     | ns   |  |  |  |  |

| t <sub>R</sub>      | Rise Time of Both SDA and SCL             |                                              | 20  |     | 300 | ns   |  |  |  |  |

| t <sub>F</sub>      | Fall Time of Both SDA and SCL             |                                              | 20  |     | 300 | ns   |  |  |  |  |

| t <sub>SU:STO</sub> | Setup Time for STOP Condition             |                                              | 0.6 |     |     | μs   |  |  |  |  |

| C <sub>B</sub>      | Capacitive Load for Each Bus Line         | CB — total capacitance of one bus line in pF |     |     | 400 | pF   |  |  |  |  |

| C <sub>I/O</sub>    | I/O Capacitance (SDA, SCL)                |                                              |     |     | 10  | pF   |  |  |  |  |

#### Figure 8:

I<sup>2</sup>C Slave Timing Diagram

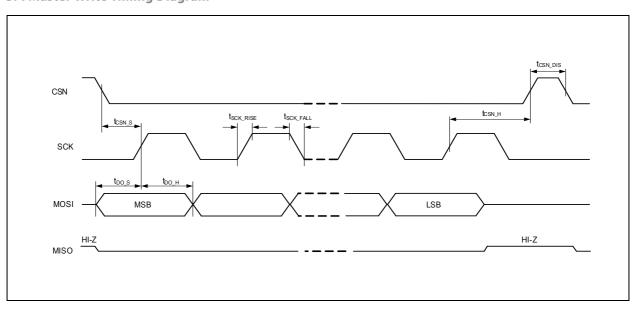

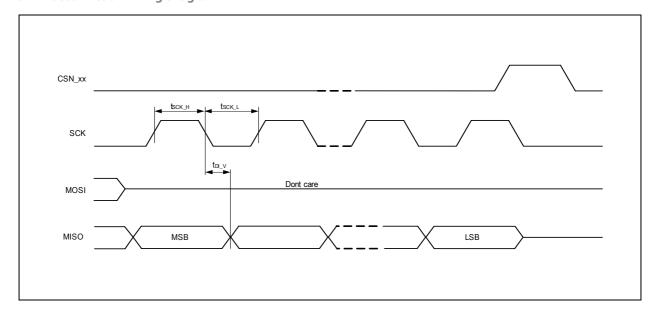

#### Figure 9: AS7262 SPI Timing Characteristics

| Symbol                | Parameter           | Conditions                                                           | Min | Тур | Мах | Unit |  |  |  |

|-----------------------|---------------------|----------------------------------------------------------------------|-----|-----|-----|------|--|--|--|

|                       | SPI Interface       |                                                                      |     |     |     |      |  |  |  |

| f <sub>SCK</sub>      | Clock Frequency     |                                                                      | 0   |     | 16  | MHz  |  |  |  |

| t <sub>SCK_H</sub>    | Clock High Time     |                                                                      | 40  |     |     | ns   |  |  |  |

| t <sub>SCK_L</sub>    | Clock Low Time      |                                                                      | 40  |     |     | ns   |  |  |  |

| t <sub>SCK_RISE</sub> | SCK Rise Time       |                                                                      | 5   |     |     | ns   |  |  |  |

| t <sub>SCK_FALL</sub> | SCK Fall Time       |                                                                      | 5   |     |     | ns   |  |  |  |

| t <sub>CSN_S</sub>    | CSN Setup Time      | Time between CSN high-low<br>transition to first SCK high transition | 50  |     |     | ns   |  |  |  |

| t <sub>CSN_H</sub>    | CSN Hold Time       | Time between last SCK falling edge<br>and CSN low-high transition    | 100 |     |     | ns   |  |  |  |

| t <sub>CSN_DIS</sub>  | CSN Disable Time    |                                                                      | 100 |     |     | ns   |  |  |  |

| t <sub>DO_S</sub>     | Data-Out Setup Time |                                                                      | 5   |     |     | ns   |  |  |  |

| t <sub>DO_H</sub>     | Data-Out Hold Time  |                                                                      | 5   |     |     | ns   |  |  |  |

| t <sub>DI_V</sub>     | Data-In Valid       |                                                                      | 10  |     |     | ns   |  |  |  |

#### Figure 10: SPI Master Write Timing Diagram

#### Figure 11: SPI Master Read Timing Diagram

## **Optical Characteristics**

Figure 12: Optical Characteristics of AS7262 (Pass Band) <sup>(1)</sup>

| Symbol | Parameter             | Test Conditions                     | Channel<br>(nm) | Min | Тур                    | Max | Unit                             |

|--------|-----------------------|-------------------------------------|-----------------|-----|------------------------|-----|----------------------------------|

| V      | Channel V             | 5700K White LED <sup>(2), (4)</sup> | 450             |     | 45 <sup>(3), (4)</sup> |     | counts/<br>(µW/cm <sup>2</sup> ) |

| В      | Channel B             | 5700K White LED <sup>(2), (4)</sup> | 500             |     | 45 <sup>(3), (4)</sup> |     | counts/<br>(µW/cm <sup>2</sup> ) |

| G      | Channel G             | 5700K White LED <sup>(2), (4)</sup> | 550             |     | 45 <sup>(3), (4)</sup> |     | counts/<br>(µW/cm <sup>2</sup> ) |

| Y      | Channel Y             | 5700K White LED <sup>(2), (4)</sup> | 570             |     | 45 <sup>(3), (4)</sup> |     | counts/<br>(µW/cm <sup>2</sup> ) |

| 0      | Channel O             | 5700K White LED <sup>(2), (4)</sup> | 600             |     | 45 <sup>(3), (4)</sup> |     | counts/<br>(µW/cm <sup>2</sup> ) |

| R      | Channel R             | Incandescent <sup>(2), (4)</sup>    | 650             |     | 45 <sup>(3), (4)</sup> |     | counts/<br>(µW/cm <sup>2</sup> ) |

| FWHM   | Full Width Half Max   |                                     | 40              |     | 40                     |     | nm                               |

| Wacc   | Wavelength Accuracy   |                                     |                 |     | ±5                     |     | nm                               |

| dark   | Dark Channel Counts   | GAIN=64, T <sub>AMB</sub> =25°C     |                 |     |                        | 5   | counts                           |

| PFOV   | Package Field of View |                                     |                 |     | ±20.0                  |     | deg                              |

#### Note(s):

1. Calibration and measurements are made using diffused light

2. Each channel is tested with GAIN = 16x, Integration Time (INT\_T) = 166ms and VDD = VDD1 = VDD2 = 3.3V,  $T_{AMB}=25^{\circ}C$

3. The accuracy of the channel counts/ $\mu W/cm^2$  is  $\pm 12\%$

4. The light source is either a 5700K white LED with an irradiance of ~600µW/cm<sup>2</sup>, or an incandescent light with an irradiance of ~1500 µW/cm<sup>2</sup> (300-1000nm). The energy at each channel (V, B, G, Y, O, R) is calculated with a ±40nm bandwidth around the center wavelengths (450nm, 500nm, 550nm, 570nm, 600nm, 650nm).

## **Typical Optical Characteristics**

Figure 13: Spectral Responsivity

## **Detailed Description**

Figure 14: AS7262 Functional Block Diagram

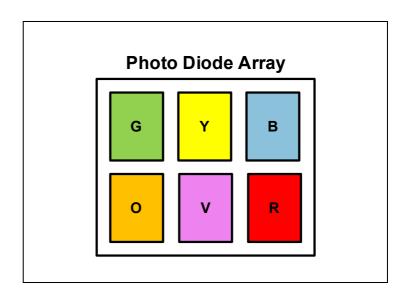

#### 6-Channel Visible Spectral\_ID Detector

The AS7262 6-channel *Spectral\_ID* is a next-generation digital spectral sensor device. Each channel has a Gaussian filter characteristic with a full width half maximum (FWHM) bandwidth of 40nm.

The sensor contains analog-to-digital converters (16-bit resolution ADC), which integrate the current from each channel's photodiode. Upon completion of the conversion cycle, the integrated result is transferred to the corresponding data registers. The transfers are double-buffered to ensure that the integrity of the data is maintained.

Interference filters enable high temperature stability and minimal lifetime drift. Filter accuracy will be affected by the angle of incidence which itself is limited by integrated aperture and internal micro-lens structure. The aperture-limited field of view is  $\pm 20.0^{\circ}$  to deliver specified accuracy.

#### **Data Conversion Description**

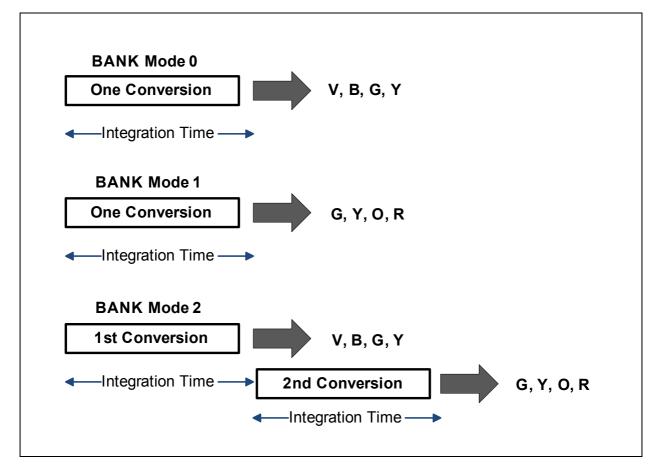

AS7262 spectral conversion is implemented via two photodiode banks per device. Bank 1 consists of data from the V, G, B, Y photodiodes. Bank 2 consists of data from the G, Y, O, R photodiodes. Spectral conversion requires the integration time (IT in ms) set to complete. If both photodiode banks are

required to complete the conversion, the 2<sup>nd</sup> bank requires an additional IT ms. Minimum IT for a single bank conversion is 2.8 ms. If data is required from all 6 photodiodes then the device must perform 2 full conversions (2 x Integration Time).

The spectral conversion process is controlled with BANK Mode settings as follows:

**BANK Mode 0:** Data will be available in registers V, B, G & Y (O and R registers will be zero) with conversions occurring continuously.

**BANK Mode 1:** Data will be available in registers G, Y, O & R (V and B registers will be zero) with conversions occurring continuously.

**BANK Mode 2:** Data will be available in registers V, B, G, Y, O & R with conversions occurring continuously.

When the bank setting is Mode 0, Mode 1, or Mode 2, the spectral data conversion process operates continuously, with new data available after each IT ms period. In the continuous modes, care should be taken to assure prompt interrupt servicing so that integration values from both banks are all derived from the same spectral conversion cycle.

**BANK Mode 3:** Data will be available in registers V, B, G, Y, O & R in One-Shot mode

When the bank setting is set to Mode 3 the device initiates One-Shot operation. The DATA\_RDY bit is set to 1 once data is available, indicating spectral conversion is complete. One-Shot mode is intended for use when it is critical to ensure spectral conversion results are obtained contemporaneously. An example use for one-shot mode is when a digitally controlled illumination source is briefly turned on for the purpose of taking a set of filter readings.

Figure 15: Photo Diode Array

#### Figure 16: Bank Mode and Data Conversion

#### **RC Oscillator**

The timing generation circuit consists of an on-chip 16MHz, temperature compensated oscillator, which provides the master clock for the AS7262.

#### **Temperature Sensor**

The temperature sensor is constantly measuring the on-chip temperature and enables temperature compensation procedures.

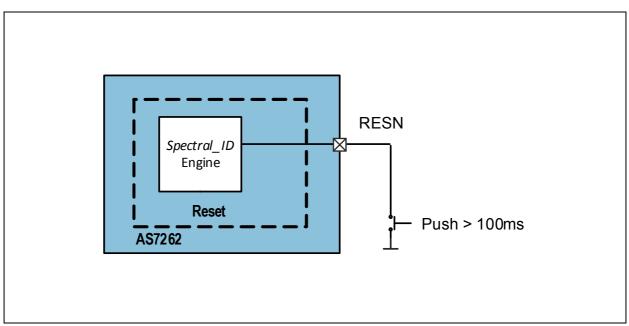

#### Reset

Pulling down the RESN pin for longer than 100ms resets the AS7262.

Figure 17: Reset Circuit

#### **Indicator LED**

The LED, connected to pin LED\_IND, can be used to indicate programming progress of the device.

While programming the AS7262 via the external SD card the indicator LED starts flashing (500ms pulses). When programming is completed the indicator LED is switched off. The LED (LED0) can be turned ON/OFF via AT commands or via I<sup>2</sup>C register control. The LED sink current is programmable from 1mA, 2mA, 4mA and 8mA.

#### Electronic Shutter with LED\_DRV Driver Control

There are two LED driver outputs that can be used to control up to 2 LEDs. This will allow different wavelength light sources to be used in the same system. The LED output sink currents are programmable and can drive external LED sources: LED\_IND from 1mA, 2mA, 4mA and 8mA and LED\_DRV from 12.5mA, 25mA, 50mA and 100mA. The sources can be turned off and on via I<sup>2</sup>C registers control or AT commands and provides the device with an electronic shutter.

#### **Interrupt Operation**

If BANK is set to Mode 0 or Mode 1 then the data is ready after the 1<sup>st</sup> integration time. If BANK is set to Mode 2 or Mode 3 then the data is ready after two integration times. If the interrupt is enabled (INT = 1) then when the data is ready, the INT line is pulled low and DATA\_RDY is set to 1. The INT line is released (returns high) when the control register is read. DATA\_RDY is cleared to 0 when any of the sensor registers V, B, G, Y, O & R are read. For multi-byte sensor data (2 or 4 bytes), after the 1st byte is read the remaining get shadow buffer protected in case an integration cycle completes just after the 1st byte is read.

In continuous spectral conversion mode (BANK setting of Mode 0, 1, or 2), the sensors continue to gather information at the rate of the integration time, hence if the sensor registers are not read when the interrupt line goes low, it will stay low and the next cycle's sensor data will be available in the registers at the end of the next integration cycle.

When the control register BANK bits are written with a value of Mode 3, One-Shot Spectral Conversion mode is entered. When a single set of contemporaneous sensor readings is desired, writing BANK Mode 3 to the control register immediately triggers exactly two spectral data conversion cycles. At the end of these two conversion cycles, the DATA\_RDY bit is set as for the other BANK modes. To perform a new One-Shot sequence, the control register BANK bits should be written with a value of Mode 3 again. This process may continue until the user writes a different value into the BANK bits.

#### I<sup>2</sup>C Slave Interface

If selected by the I<sup>2</sup>C\_ENB pin setting, interface and control can be accomplished through an I<sup>2</sup>C compatible slave interface to a set of registers that provide access to device control functions and output data. These registers on the AS7262 are, in reality, implemented as *virtual* registers in software. The actual I<sup>2</sup>C slave hardware registers number only three and are described in the table below. The steps necessary to access the virtual registers defined in the following are explained in pseudocode for external I<sup>2</sup>C master writes and reads below.

## I<sup>2</sup>C Feature List

- Fast mode (400kHz) and standard mode (100kHz) support.

- 7+1-bit addressing mode.

- Write format: Byte.

- Read format: Byte.

- SDA input delay and SCL spike filtering by integrated RC-components.

Figure 18: I<sup>2</sup>C Slave Device Address and Physical Registers

| Entity               | Description                                                      | Note                                                                                                                                                                                                                                                                                                           |

|----------------------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device Slave Address | 8-bit Slave Address                                              | Byte = 1001001x (device address = 49 hex)<br>x= 1 for Master Read (byte = 93 hex)<br>x= 0 for Master Write (byte = 92 hex)                                                                                                                                                                                     |

| STATUS Register      | l <sup>2</sup> C slave interface<br>STATUS register<br>Read-only | Register Address = 0x00<br>Bit 1: TX_VALID<br>$0 \rightarrow$ New data may be written to WRITE register<br>$1 \rightarrow$ WRITE register occupied. Do NOT write.<br>Bit 0: RX_VALID<br>$0 \rightarrow$ No data is ready to be read in READ register.<br>$1 \rightarrow$ Data byte available in READ register. |

| WRITE Register       | l <sup>2</sup> C slave interface<br>WRITE register<br>Write-only | Register Address = 0x01<br>8-Bits of data written by the I <sup>2</sup> C Master intended<br>for receipt by the I <sup>2</sup> C slave. Used for both <i>virtual</i><br>register addresses and write data.                                                                                                     |

| READ Register        | l <sup>2</sup> C slave interface<br>READ register<br>Read-only   | Register Address = 0x02<br>8-Bits of data to be read by the I <sup>2</sup> C Master.                                                                                                                                                                                                                           |

### I<sup>2</sup>C Virtual Register Write Access

I<sup>2</sup>C Virtual Register Byte Write shows the pseudocode necessary to write virtual registers on the AS7262. Note that, because the actual registers of interest are realized as virtual registers, a means of indicating whether there is a pending read or write operation of a given virtual register is needed. To convey this information, the most significant bit of the virtual register address is used as a marker. If it is 1, then a write is pending, otherwise the slave is expecting a virtual read operation. The pseudocode illustrates the proper technique for polling of the I<sup>2</sup>C slave status register to ensure the slave is ready for each transaction.

#### I<sup>2</sup>C Virtual Register Byte Write

#### Pseudocode

Poll I<sup>2</sup>C slave STATUS register;

If TX\_VALID bit is 0, a write can be performed on the interface;

Send a virtual register address and set the MSB of the register address to 1 to indicate the pending write; Poll I<sup>2</sup>C slave STATUS register;

If TX\_VALID bit is 0, the virtual register address for the write has been received and the data may now be written; Write the data.

#### Sample Code:

| #define I2C_AS72XX_SLAVE_STATUS_REG | 0x00 |

|-------------------------------------|------|

| #define I2C_AS72XX_SLAVE_WRITE_REG  | 0x01 |

| #define I2C_AS72XX_SLAVE_READ_REG   | 0x02 |

| #define I2C_AS72XX_SLAVE_TX_VALID   | 0x02 |

| #define I2C_AS72XX_SLAVE_RX_VALID   | 0x01 |

void i2cm\_AS72xx\_write(uint8\_t virtualReg, uint8\_t d)

#### {

```

volatile uint8_t status;

while (1)

{

// Read slave l<sup>2</sup>C status to see if the write buffer is ready.

status = i2cm_read(I2C_AS72XX_SLAVE_STATUS_REG);

if ((status & I2C_AS72XX_SLAVE_TX_VALID) == 0)

// No inbound TX pending at slave. Okay to write now.

break;

}

// Send the virtual register address (setting bit 7 to indicate a pending write).

i2cm_write(I2C_AS72XX_SLAVE_WRITE_REG, (virtualReg | 0x80));

while (1)

{

```

// Read the slave l<sup>2</sup>C status to see if the write buffer is ready.

status = i2cm\_read(I2C\_AS72XX\_SLAVE\_STATUS\_REG);

```

if ((status & I2C_AS72XX_SLAVE_TX_VALID) == 0)

// No inbound TX pending at slave. Okay to write data now.

break;

```

}

// Send the data to complete the operation.

i2cm\_write(I2C\_AS72XX\_SLAVE\_WRITE\_REG, d);

}

### I<sup>2</sup>C Virtual Register Read Access

I<sup>2</sup>C Virtual Register Byte Read shows the pseudocode necessary to read virtual registers on the AS7262. Note that in this case, reading a virtual register, the register address is not modified.

#### I<sup>2</sup>C Virtual Register Byte Read

Pseudocode

Poll I<sup>2</sup>C slave STATUS register; If TX\_VALID bit is 0, the virtual register address for the read may be written; Send a virtual register address; Poll I<sup>2</sup>C slave STATUS register; If RX\_VALID bit is 1, the read data is ready; Read the data.

#### Sample Code:

```

uint8_t i2cm_AS72xx_read(uint8_t virtualReg)

{

volatile uint8_t status, d;

while (1)

{

// Read slave I<sup>2</sup>C status to see if the read buffer is ready.

status = i2cm_read(I2C_AS72XX_SLAVE_STATUS_REG);

if ((status & I2C_AS72XX_SLAVE_TX_VALID) == 0)

// No inbound TX pending at slave. Okay to write now.

break;

}

// Send the virtual register address (setting bit 7 to indicate a pending write).

i2cm_write(I2C_AS72XX_SLAVE_WRITE_REG, virtualReg);

while (1)

{

// Read the slave I<sup>2</sup>C status to see if our read data is available.

status = i2cm_read(I2C_AS72XX_SLAVE_STATUS_REG);

if ((status & I2C_AS72XX_SLAVE_RX_VALID) != 0)

// Read data is ready.

break:

}

// Read the data to complete the operation.

d = i2cm_read(I2C_AS72XX_SLAVE_READ_REG);

return d; s

The details of the i2cm read() and i2cm write()

functions in previous Figures are dependent upon the nature

```

and implementation of the external I<sup>2</sup>C master device.

#### **4-Byte Floating-Point (FP) Registers**

Several 4-byte registers (hex) are used by the AS7262. Here is an example of how these registers are used to represent floating point data (based on the IEEE 754 standard):

#### byte 2 byte 3 byte 1 byte 0 3E (hex) 20 (hex) 00 (hex) 00 (hex) 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 0 0 0 0 0 16 15 8 31 24 23 7 0 sign exponent (8 bits) fraction (23 bits) 0 = 0.15625 0 1 1 1 1 1 0 31 30 23 22

Figure 19: Example of the IEEE 754 Standard

The floating point (FP) value assumed by 32 **bit binary32 data** with a biased exponent **e** (the 8 bit unsigned integer) and a **23 bit fraction** is (for the above example):

FP value=

$$(-1)^{\text{sign}} \cdot \left(1 + \sum_{i=1}^{23} b_{23-i} 2^{-i}\right) \times 2^{(e-127)}$$

FP value=

$$(-1)^{0} \cdot \left(1 + \sum_{i=1}^{23} b_{23-i} 2^{-i}\right) \times 2^{(124-127)}$$

FP value=

$$1 \times (1 + 2^{-2}) \times 2^{-3} = 0.15625$$

### I<sup>2</sup>C Virtual Register Set

Figure 20 provides a summary of the AS7262 I<sup>2</sup>C register set. Figures after that provide additional register details. All register data is hex, and all multi-byte entities are Big Endian (most significant byte is situated at the lowest register address).

Multiple byte registers (2 byte integer, or, 4 byte floating point) must be read in the order of ascending register addresses (low to high). And if capable of being written to, must also be written in the order of ascending register addresses.

Figure 20: I<sup>2</sup>C Virtual Register Set Overview

| Addr      | Name              | <d7></d7> | <d6></d6>               | <d5> <d4></d4></d5> | <d3></d3>     | <d2></d2> | <d1></d1> | <d0></d0> |  |  |  |

|-----------|-------------------|-----------|-------------------------|---------------------|---------------|-----------|-----------|-----------|--|--|--|

|           | Version Registers |           |                         |                     |               |           |           |           |  |  |  |

| 0x00:0x01 | HW_Version        |           |                         | Har                 | dware Versio  | n         |           |           |  |  |  |

| 0x02:0x03 | FW_Version        |           |                         | Firn                | nware Versio  | n         |           |           |  |  |  |

|           | Control Registers |           |                         |                     |               |           |           |           |  |  |  |

| 0x04      | Control_Setup     | RST       | INT                     | GAIN                | Ban           | k         | DATA_RDY  | RSVD      |  |  |  |

| 0x05      | INT_T             |           | <u>+</u>                | Inte                | egration Time | e         |           | <u>+</u>  |  |  |  |

| 0x06      | Device_Temp       |           |                         | Devie               | e Temperati   | ure       |           |           |  |  |  |

| 0x07      | LED_Control       | RS        | VD                      | ICL_DRV             | LED_DRV       | IC        | CL_IND    | LED_IND   |  |  |  |

|           |                   |           | Senso                   | or Raw Data Regist  | ers           |           |           | 1         |  |  |  |

| 0x08      | V_High            |           |                         | Channe              | l V High Data | a Byte    |           |           |  |  |  |

| 0x09      | V_Low             |           |                         | Channe              | l V Low Data  | Byte      |           |           |  |  |  |

| 0x0A      | B_High            |           |                         | Channe              | l B High Data | a Byte    |           |           |  |  |  |

| 0x0B      | B_Low             |           |                         | Channe              | l B Low Data  | Byte      |           |           |  |  |  |

| 0x0C      | G_High            |           |                         | Channe              | l G High Data | a Byte    |           |           |  |  |  |

| 0x0D      | G_Low             |           |                         | Channe              | l G Low Data  | Byte      |           |           |  |  |  |

| 0x0E      | Y_High            |           |                         | Channe              | l Y High Data | a Byte    |           |           |  |  |  |

| 0x0F      | Y_Low             |           |                         | Channe              | l Y Low Data  | Byte      |           |           |  |  |  |

| 0x10      | O_High            |           |                         | Channe              | O High Data   | a Byte    |           |           |  |  |  |

| 0x11      | O_Low             |           | Channel O Low Data Byte |                     |               |           |           |           |  |  |  |

| 0x12      | R_High            |           |                         | Channe              | l R High Data | a Byte    |           |           |  |  |  |

| 0x13      | R_Low             |           |                         | Channe              | IR Low Data   | Byte      |           |           |  |  |  |

| Addr                             | Name  | <d7></d7>                                  | <d6></d6> | <d5></d5> | <d4></d4> | <d3></d3> | <d2></d2> | <d1></d1> | <d0></d0> |

|----------------------------------|-------|--------------------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| Sensor Calibrated Data Registers |       |                                            |           |           |           |           |           |           |           |

| 0x14:0x17                        | V_Cal | Channel V Calibrated Data (floating point) |           |           |           |           |           |           |           |

| 0x18:0x1B                        | B_Cal | Channel B Calibrated Data (floating point) |           |           |           |           |           |           |           |

| 0x1C:0x1F                        | G_Cal | Channel G Calibrated Data (floating point) |           |           |           |           |           |           |           |

| 0x20:0x23                        | Y_Cal | Channel Y Calibrated Data (floating point) |           |           |           |           |           |           |           |

| 0x24:0x27                        | O_Cal | Channel O Calibrated Data (floating point) |           |           |           |           |           |           |           |

| 0x28:0x2B                        | R_Cal | Channel R Calibrated Data (floating point) |           |           |           |           |           |           |           |

## **Detailed Register Description**

Figure 21: HW Version Registers

| Addr: 0x00 |             | HW_Version |        |                    |  |

|------------|-------------|------------|--------|--------------------|--|

| Bit        | Bit Name    | Default    | Access | Bit Description    |  |

| 7:0        | Device Type | 01000000   | R      | Device type number |  |

|            | Addr: 0x01  | HW_Version |        |                    |  |

|            |             | Defeult    |        | Dit Description    |  |

| Bit        | Bit Name    | Default    | Access | Bit Description    |  |

Figure 22: FW Version Registers

| Addr: 0x02 |                        | FW_Version |             |                               |  |

|------------|------------------------|------------|-------------|-------------------------------|--|

| Bit        | Bit Name               | Default    | Access      | Bit Description               |  |

| 7:6        | Minor Version          |            | R           | Minor version [1:0]           |  |

| 5:0        | Sub Version            |            | R           | Sub version                   |  |

| Addr: 0x03 |                        | FW_Version |             |                               |  |

|            | Addr: 0x03             |            |             | FW_Version                    |  |

| ,<br>Bit   | Addr: 0x03<br>Bit Name | Default    | Access      | FW_Version<br>Bit Description |  |

|            |                        | Default    | Access<br>R |                               |  |

#### Figure 23: Control Setup Register

| Addr: 0x04/0x84 |          | Control_Setup |        |                                                                                                       |  |

|-----------------|----------|---------------|--------|-------------------------------------------------------------------------------------------------------|--|

| Bit             | Bit Name | Default       | Access | Bit Description                                                                                       |  |

| 7               | RST      | 0             | R/W    | Soft Reset, Set to 1 for soft reset, goes to 0 automatically after the reset                          |  |

| 6               | INT      | 0             | R/W    | Enable interrupt pin output (INT),<br>1: Enable, 0: Disable                                           |  |

| 5:4             | GAIN     | 0             | R/W    | Sensor Channel Gain Setting (all channels)<br>'b00=1x; 'b01=3.7x; 'b10=16x; 'b11=64x                  |  |

| 3:2             | BANK     | 10            | R/W    | Data Conversion Type (continuous)<br>'b00=Mode 0; 'b01=Mode 1; 'b10=Mode 2;<br>'b11=Mode 3 One-Shot   |  |

| 1               | DATA_RDY | 0             | R/W    | 1: Data Ready to Read, sets INT active if interrupt is<br>enabled.<br>Can be polled if not using INT. |  |

| 0               | RSVD     | 0             | R      | Reserved; Unused                                                                                      |  |

#### Figure 24: Integration Time Register

| Addr: 0x05/0x85 |          | INT_T   |        |                                            |  |

|-----------------|----------|---------|--------|--------------------------------------------|--|

| Bit             | Bit Name | Default | Access | Bit Description                            |  |

| 7:0             | INT_T    | 0xFF    | R/W    | Integration time = <value> * 2.8ms</value> |  |

Figure 25: Device Temperature Register

| Addr: 0x06 |             | Device_Temp |        |                                   |  |

|------------|-------------|-------------|--------|-----------------------------------|--|

| Bit        | Bit Name    | Default     | Access | Bit Description                   |  |

| 7:0        | Device_Temp |             | R      | Device temperature data byte (°C) |  |