Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# AS8500 Universal multi pupose data aquisition system

**Data Sheet**

#### 1 Features

- 16 bits resolution

- differential inputs

- Single + 5V supply

- Low power 15 mW

- SOIC16 package

- 16 kHz maximum sampling frequency

- internal temperature measurement

- internal reference

- programmable current sources

- digital comparator

- active wake-up

- PGA gains 6, 24, 50, 100

- Zero offset

- Zero offset TC

- Extremely low noise

- Internal oscillator with comparator for active wake up

- 3-wire serial interface, μP compatible

- temperature range 40 to + 125 °C

# 2 Applications

- battery management for automotive systems

- power management

- mV/u V-meter

- thermocouple temperature measurement

- RTD precision temperature measurement

- high-precision voltage and current measurement

# 3 General description

The AS8500 is a complete, low power data acquisition system for very small signals (i.e. voltages from shunt resistors, thermocouples) that operates on a single 5 V power supply. The chip powers up with a set of default conditions at which time it can be operated as a read-only-converter. Reprogramming is at any time possible by just writing into two internal registers via the serial interface.

The AS8500 has four ground refering inputs which can be switched separately to the internal PGA. Two input channels can also be operated as a fully differential ground free input. The system can measure both positive and negative input signals.

The PGA amplification ranges from 6 to 100 which enables the system to measure signals from 7mV to 120 mV full scale range with high accuracy, linearity and speed.

The chip contains a high precision bandgap reference and an active offset compensation that makes the system offset free (better than 0,5  $\mu$ V) and the offset-TC value negligible. The built-in programmable digital filter allows an effective noise suppression if the high speed is not necessary in the application. The input noise density is only 35 nV  $/\sqrt{H_{\rm Z}}$  and due to

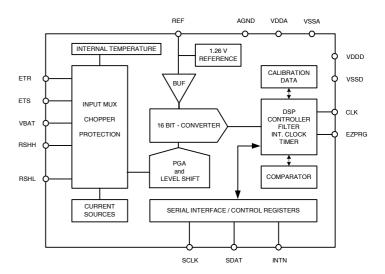

Figure 1: Functional Block Diagram

the high internal chopping frequency the system is free of 1/f-noise down to DC.The 0-10 Hz noise is typical below 1  $\mu$ V i.e. as good or better than any other available chopper amplifier.

For high speed synchronous measurements the chip can run in an automatic switching mode between two input channels with preprogrammed parameter sets.

The circuit has been optimised for the application in battery management systems in automotive systems. As a front end data acquisition system it allows an high quality measurement of current, voltage and temperature of the battery.

With a high quality 100  $\mu\Omega$  resistor the system can handle the starter current of up to 1500 A, a continuous current of  $\pm$  300 A as well as the very low idle current of a few mA in the standby mode.

For external temperature measurement the chip can use a wide variety of different temperature sensors such as RTD, PTC, NTC, thermocouples or even diodes or transistors. A built-in programmable current source can be switched to any input and activate these sensors without the need of other external components.

The measurement of the chip temperature with the integrated internal temperature sensor allows in addition the temperature compensation of sensitive parameters which increases the total accuracy considerably.

The flexibility of the system is further increased by a digital comparator that can be assigned to any measured property

(current, voltage, temperature) and an active wake-up in the sleep-mode. All analog input-terminals can be checked for wire break via the SDI-interface.

# **CONTENTS**

| 1  | F          | EATURES                                                                             |     |

|----|------------|-------------------------------------------------------------------------------------|-----|

| 2  | A          | APPLICATIONS                                                                        |     |

| 3  | G          | GENERAL DESCRIPTION                                                                 |     |

| 4  | Р          | PIN FUNCTION DESCRIPTION FOR SOIC 16 PACKAGE                                        | . : |

| 5  |            | ABSOLUTE MAXIMUM RATINGS                                                            |     |

| 6  |            | ELECTRICAL CHARACTERISTICS                                                          |     |

|    |            |                                                                                     |     |

| 7  |            | UNCTIONAL DESCRIPTION                                                               |     |

|    | 7.1<br>7.2 | Power on ResetAnalog part, general description                                      |     |

|    |            | 7.2.1 Reference voltage                                                             |     |

|    |            | 7.2.2 Current sources                                                               |     |

|    |            | 7.2.3 Internal temperature sensor                                                   |     |

|    |            | DIGITAL PART                                                                        |     |

|    | -          | 7.3.1 Sampling rate                                                                 |     |

|    | 7.4        | 7.3.2 Calibration                                                                   |     |

|    | 7.5        | REGISTER DESCRIPTION                                                                |     |

|    |            | 7.5.1 OPM operation mode register ( 4 bits )                                        |     |

|    |            | 7.5.2 CRG general configuration register ( 28 bits )                                | 17  |

|    |            | 7.5.3 CRA measurement channel A configuration register (17 bits)                    | 18  |

|    |            | 7.5.4 CRB measurement channel B configuration register (17 bits)                    |     |

|    |            | 7.5.5 ZZR Zener-Zap register (188 bits): 7.5.6 CAR calibration register (110 bits). |     |

|    |            | 7.5.7 TRR trimming register ( 20 bits )                                             |     |

|    |            | 7.5.8 THR alarm (Wake-up) threshold register (17 bits)                              |     |

|    | 7          | 7.5.9 MSR measurement result register (18 bits)                                     |     |

| 8  | D          | DIGITAL INTERFACE DESCRIPTION                                                       | 2(  |

|    | 8.1        | CLK                                                                                 |     |

|    | 8.2        | INTN                                                                                |     |

|    | 8.3        | SDI BUS OPERATION                                                                   |     |

|    | 8.4<br>8.5 | Data transfers                                                                      |     |

|    | 8.6        | SDI ACCESS TO OTP MEMORY.                                                           |     |

|    |            | 3.6.1 ZZR register bit mapping                                                      |     |

|    | 8          | 3.6.2 Stored ZZR-register mapping                                                   | 34  |

| 9  | G          | GENERAL APPLICATION HINTS                                                           | 3!  |

|    | 9.1        | GROUND CONNECTION, ANALOG COMMON                                                    | 3!  |

|    | 9.2        | THERMAL EMF                                                                         |     |

|    | 9.3        | Noise considerations                                                                |     |

|    | 9.4        | Shielding, guarding                                                                 |     |

| 10 |            | TYPICAL PERFORMANCE CHARACTERISTICS                                                 |     |

| 11 | l P        | PACKAGE DIMENSIONS                                                                  | 39  |

| 12 | 2 R        | REVISION HISTORY                                                                    | 3   |

| 13 | 3 0        | ORDERING INFORMATION                                                                | 39  |

| 14 | ı c        | CONTACT                                                                             | 4(  |

|    | 14.1       |                                                                                     |     |

|    | 14.2       |                                                                                     |     |

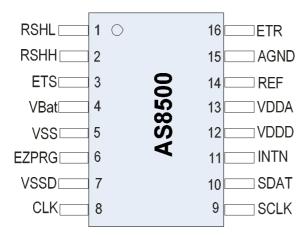

# 4 PIN function description for SOIC 16 package

| PIN | Name  | description                                                     | Comment                                                                                                                                                   |

|-----|-------|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | RSHL  | anlalog input from shunt resistor low side                      | analog common for VBAT, ETS and ETR; return for internal current source                                                                                   |

| 2   | RSHH  | anlalog input from shunt resistor high side                     |                                                                                                                                                           |

| 3   | ETS   | analog input with reference to RSHL                             |                                                                                                                                                           |

|     |       | analog input for differential input ETS-VBAT                    |                                                                                                                                                           |

|     |       | analog output for current-source                                |                                                                                                                                                           |

| 4   | VBAT  | analog input with reference to RSHL                             |                                                                                                                                                           |

|     |       | analog input for differential input ETS-VBAT                    |                                                                                                                                                           |

|     |       | analog output for current-source                                |                                                                                                                                                           |

| 5   | VSS   | 0V-power supply for analog part                                 |                                                                                                                                                           |

| 6   | EZPRG | digital power input for programming Zener fuses.                | This input must be open or connected to VDDD. It is not intended, that OTP content is modified by the user.                                               |

| 7   | VSSD  | 0V-power supply and ground reference point for digital part     |                                                                                                                                                           |

| 8   | CLK   | digital input for external clock, master clock input            | external clock typical 8.192 MHz; during MWU-mode (see 7.4) external connection must be high impedance or connected to VDDD to reduce current consumption |

| 9   | SCLK  | serial port clock input for SDI-port                            | the user must provide a serial clock on this input                                                                                                        |

| 10  | SDAT  | serial data in- and output                                      |                                                                                                                                                           |

| 11  | INTN  | Digital I/O for interrupt from comparator                       | signal wake-up to external μC                                                                                                                             |

|     |       | conversion ready flag for external interupt and synchronisation | in normal mode                                                                                                                                            |

| 12  | VDDD  | + 5V digital power supply                                       |                                                                                                                                                           |

| 13  | VDDA  | + 5V analog power supply                                        |                                                                                                                                                           |

| 14  | REF   | reference input/output                                          | must be connected to VSS with a 30 nF capacitor                                                                                                           |

| 15  | AGND  | analog ground, ground reference for ADC                         | this PIN must be connected with a 50-100nF-capacitor to VSS; no direct connection to VSSD/VSS allowed                                                     |

| 16  | ETR   | analog input with reference to RSHL                             |                                                                                                                                                           |

|     |       | analog output for current-source                                |                                                                                                                                                           |

Table 1: Pin Description

Figure 2: Schematic Package outline SOIC 16

# 5 Absolute Maximum Ratings

Stress beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under "Operating Conditions" is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. All voltages are defined with respect to VSS and VSSD. Positive currents flow into the IC.

Absolute maximum ratings ( $T_A = -40^{\circ}$ C to  $125^{\circ}$ C unless otherwise specified)

| Nr. | PARAMETER                      | SYMBOL            | MIN  | TYP | MAX      | UNIT | NOTE                          |

|-----|--------------------------------|-------------------|------|-----|----------|------|-------------------------------|

| 0   | Supply voltage                 | VDD               | -0.3 |     | 7.0      | ٧    | Polarity inversion externally |

|     | Analogue VDDA and digital VDDD |                   |      |     |          |      | protected                     |

| 1   | Input pin voltage              | $v_{in}$          | -0.3 |     | VDD +0.3 | ٧    |                               |

| 2   | Input current                  | I <sub>SCR</sub>  | -100 |     | 100      | mA   | JEDEC 17                      |

|     | (latch-up immunity)            |                   |      |     |          |      |                               |

| 3   | Electrostatic discharge        | ESD               | -2   |     | 2        | kV   | 1)                            |

| 4   | Ambient temperature            | T <sub>A</sub>    | -40  |     | 125      | οС   | (Tj = 150°C)                  |

| 5   | Storage temperature            | T <sub>STRG</sub> | -55  |     | 150      | οС   |                               |

| 6   | Soldering conditions           | $T_{LEAD}$        |      |     | 260      | °C   | 2)                            |

| 7   | Humidity, non-condensing       |                   | 5    |     | 85       | %    |                               |

| 8   | Thermal resistance             | $R_{\text{thJA}}$ |      |     | 75       | K/W  |                               |

| 9   | Power dissipation              | P <sub>TOT</sub>  |      |     | 350      | mW   |                               |

$<sup>^{1)}</sup>$  MIL 883 E method 3015, HBM: R =1.5 k $\Omega,$  C =100pF.

<sup>2)</sup> Jedec Std - 020C, lead free

#### 6 Electrical characteristics

VDDA=5V +/-0.1 V, fclk=8.192 MHz, chopping ratio MM=4 (see 7.5.3), oversampling frequency=2.048 MHz, oversampling ratio=128 temperature range: -40 to 125°C if not otherwise noted

| symbol       | parameter                            | conditions              | min                | typ                 | max              | units     |       |

|--------------|--------------------------------------|-------------------------|--------------------|---------------------|------------------|-----------|-------|

| input charac | teristics                            |                         |                    |                     |                  |           |       |

| G1           | for gain 1 the input signal is input | connected directly to t | h input of the con | verter, this is not | possible for the | RSHH-RSHL |       |

| Gain         | gains of PGA                         |                         |                    | 6, 24, 50, 100      |                  |           | 1)    |

| AC_g6        | Accuracy at gain 6                   | 0 to 85 °C              |                    | 0.4                 |                  | % @-120mV | 2)    |

| -            |                                      | -40 to 125°C            |                    | 1.0                 |                  | % @-120mV | 2),3) |

| AC_g24       | Accuracy at gain 24                  | 0 to 85 °C              |                    | 0.2                 |                  | % @+-20mV | 2)    |

| -            |                                      | -40 to 125°C            |                    | 0.6                 |                  | % @+-20mV | 2) 3) |

| AC_g50       | Accuracy at gain 50                  | 0 to 85 °C              |                    | 1                   |                  | % @+-10mV | 2)4)  |

| AC_g100      | Accuracy at gain 100                 | 0 to 85 °C              |                    | 1                   |                  | % @+-5mV  | 2)4)  |

| Vin          | input voltage ranges                 | G1                      |                    | -300 to + 800       |                  | mV        | 5)    |

|              | (with reference to RSHL)             | G6                      |                    | +/- 120             |                  | mV        | 6)    |

|              | ,                                    | G24                     |                    | +/- 30              |                  | mV        | 6)    |

|              |                                      | G50                     |                    | +/- 15              |                  | mV        | 7)    |

|              |                                      | G100                    |                    | +/- 7.5             |                  | mV        | 7)    |

#### Notes

therefore it is recommended to use these gain settings only for applications in the temperature range 0 to 85°C.

It has been designed mainly for positive input voltages up to 0.8 V i.e. for measurements of temperature with transistors and diodes.

The limitation for negative input voltages is due to the onset of conduction of the input protection diodes.

<sup>1)</sup> the absolute gain values are subjected to a manufacturing spread of +/-30%

<sup>&</sup>lt;sup>2)</sup> Accuracy relies on bandgap characteristic, on the gain variation over temperature and on the trimm information. To achieve optimum performance, the circuit may be trimmed by the user for best temperature stability by writting aproportiate data to the TRR register (see sections 7.4 and 7.5) Default content of TRR register is 17.

<sup>&</sup>lt;sup>3)</sup> due to a nonlinear behaviour of the gain and reference voltage over temperature the accuracy is lower for the extended temperature range.

<sup>4)</sup> It is recommended to use these gain settings only for applications in the temperature range 0 to 85°C

<sup>5)</sup> this gain range is not using the internal PGA, the input is directely connected to the AD-converter. Therefore the input resistance is lower then for other gain ranges.

<sup>6)</sup> the ASSP is optimised for G6 and G24 concerning linearity, speed and TC, therefore these ranges are recommended whenever possible.

<sup>7)</sup> because of higher TC value at elevated temperature G50 and G100 are recommended for applications in the temperature range 0 to 85°C

# **Electrical characteristics (continued)**

VDDA=5V +/-0.1 V, fclk=8.192 MHz, chopping ratio MM=4 (see 7.5.3), oversampling frequency=2.048 MHz, oversampling ratio=128 temperature range: -40 to 125°C if not otherwise noted

| symbol    | parameter                                                      | conditions                                                                               | min      | typ                              | max    | units                                                                   |          |

|-----------|----------------------------------------------------------------|------------------------------------------------------------------------------------------|----------|----------------------------------|--------|-------------------------------------------------------------------------|----------|

| cal_err   | calibration error<br>for 30 000 digits output at<br>full range | G1, 720 mV<br>G6, 120 mV<br>G24, 30 mV<br>G50, 15 mV<br>G100, 7.5 mV                     |          | Device is not factory calibrated | mux    | %                                                                       | 1)       |

| lin_err   | nonlinearity                                                   | gain 6 @ room temp<br>gain 24 @ room temp<br>gain 50 @ room temp<br>gain 100 @ room temp |          | 0.1<br>0.03<br>0.05<br>0.05      | -      | % or 30 digits 2) % or 10 digits 2) % or 15 digits 2) % or 20 digits 2) | 3)       |

| lin_errTC | TC of linearity error                                          | all gains                                                                                |          | 1                                | 5      | ppm/K                                                                   | 3)       |

| Vos       | offset voltage: RSHH_RSHL offset voltage: ETS, ETR,            | -40 to 125°C                                                                             | -0.5     | 0.2                              | 0.5    | μV                                                                      | 4)       |

|           | VBAT                                                           | -40 to 85°C<br>85 to 125°C                                                               | -2<br>-4 | 0.5<br>1                         | 1<br>2 | μV<br>μV                                                                | 4)<br>4) |

| dVos/dT   | Offset voltage drift: RSHH-<br>RSHL                            | -40 to 85 °C                                                                             |          | 0.002                            |        | μV/K                                                                    |          |

| lb        | input bias/leakage current, all channels                       | room temperature                                                                         | -1000    | 0.2                              | 1000   | nA                                                                      | 5)       |

| Vndin     | voltage noise density<br>(G=24)                                | f=0 to 1 kHz                                                                             |          | 35                               | 50     | nV//Hz                                                                  | 6)       |

| Indin     | current noise density<br>(G=24)                                | f=10 Hz                                                                                  |          | 20                               |        | fA//Hz                                                                  | 6)       |

| en p_p    | voltage noise, peak (G=24)                                     | 0 to 100 Hz<br>0 to 10 Hz                                                                |          | 3<br>1                           |        | μV<br>μV                                                                | 6)<br>6) |

| en_RMS    | voltage noise, RMS (G=24)                                      | 1000 Hz                                                                                  |          | 1.5                              |        | μV                                                                      | 6)       |

| SNR       | signal to noise (G=24, G=6)                                    | room temperature                                                                         |          | 100                              |        | dBmin                                                                   |          |

| SDR       | signal to distortion (G=24, G=6)                               | room temperature                                                                         | _        | 100                              |        | dBmin                                                                   |          |

| CCI       | chanel to chanel insulation                                    | room temperature                                                                         |          | -90                              |        | dBmax                                                                   |          |

| PSRR      | power supply rejection ratio                                   | 4.9 to 5.1 V                                                                             |          | -60                              |        | dBmax                                                                   |          |

<sup>1)</sup> The output response might be calibrated by the user by writing appropriate calibration constants to the CAR register (see 7.5. ). The default values are 1548 dec

<sup>2)</sup> whatever is lower

<sup>3)</sup> max limit is derived fromdevice characterization and not tested

<sup>4)</sup> Min/Maximum limits over temperature range are derived from device characterization and not etsted. In normal operation a termperature independent digital offset of -0.7 digits is present due to internal raunding.

<sup>5)</sup> Typical leakage current is valid for all gain settings except G=1 for positive input voltages below 200 mV. In the temperature range 85-125°C it may be as high as 5 nA. In normal operation a temperature independent digital offset of -0.7 digits is present due to internal rounding.

<sup>6)</sup> This parameter is not measured directly. It is measured indirectly via gain measurement of the whole path at room temperature

# **Electrical characteristics (continued)**

VDDA=5V +/-0.1 V, fclk=8.192 MHz, chopping ratio MM=4 (see 7.5.3), oversampling frequency=2.048 MHz, oversampling ratio =128 temperature range: -40 to 125°C if not otherwise noted

|                    | temperature                      | e lange40 to 125 t | יוו ווטניטנוופו | WISE HOLEG |       |             |       |

|--------------------|----------------------------------|--------------------|-----------------|------------|-------|-------------|-------|

| symbol             | parameter                        | conditions         | min             | typ        | max   | units       |       |

| data conversion    |                                  |                    |                 |            |       |             |       |

| RES                | resolution                       | all channels       |                 | 16         |       | bits        | 1) 2) |

| Vref               | reference voltage                | room temperature   |                 | 1.21       |       | V           |       |

|                    |                                  | 0-85°C,box         |                 |            |       |             |       |

| Vref_TC            | temperature coefficient of Vref  | method             |                 | 20         |       | ppm/K       | 3)    |

| Vref_Ri            | internal resistance of Vref      | Rload > 50 kOhm    |                 | 200        |       | Ohm         |       |

| fovs               | clock frequency                  |                    |                 | 4.096      |       | MHz         |       |

| R1                 | oversamplig ratio                |                    | 64              | 128        |       |             |       |

| MM                 | conversions during chopper cycle |                    |                 | 4          | 8     |             |       |

| BW                 | bandwidth                        |                    | 7.8             | 1000       | 16000 | Hz          |       |

| av                 | internal averaging               |                    | 1               | 4          | 1024  | cycles      |       |

| fclk               | external clock frequency         |                    | 0.05            | 8.192      | 10    | MHz         | 4)    |

| CLK_extdiv         | clock division factor            |                    |                 | 2          | 4     |             |       |

| DR_clk             | duty ratio of external clock     |                    |                 | 50         |       | %           |       |

| int_fclk           | internal clock frequency         |                    | 180             | 250        | 330   | kHz         |       |

| analog inputs      |                                  | RSHH, VBAT, ETS    | , ETS           |            |       |             |       |

| Rin                | input resistance                 | Ue < 150 mV        | 50              | 100        |       | MOhm        |       |

| Cin                | input capacitance at gain 24     |                    | 8               | 15         | 30    | pF          |       |

| internal temperatu | re sensor                        |                    |                 |            |       |             |       |

| T_out20            | output at 23°C                   | G 6, typical       |                 | 23 000     |       | digits      | •     |

| T_sl               | slope                            | -20 to 100°C       |                 | 75         |       | digits/degC |       |

| current source     |                                  | output to RSHH, RS | SHL             |            |       |             |       |

| lcurr_rshh         |                                  |                    |                 | 2          |       | μA          |       |

<sup>1)</sup> with external averaging the resolution can be increased up to 21 bits with an effective sampling rate below 10 Hz

<sup>2)</sup> the system works in overflow condition without degradation of accuracy up to 1.4 \* range width. This means that the overflow bit can work as bit no.17 in this range.

<sup>3)</sup> TC- value of the reference voltage may be set through trimm bits intentionally higher to minimize TC of the entire measurement path for gain 24

<sup>4)</sup> in the temperature range 0 - 85°C the clock frequency can be increased to 12 MHz

# **Electrical characteristics (continued)**

| symbol           | parameter                             | conditions           | min          | typ         | max | units |    |

|------------------|---------------------------------------|----------------------|--------------|-------------|-----|-------|----|

| programmable     | current source                        | output to Vbat, ETS. | or ETR       |             |     |       |    |

| lcurr_ON         | current level                         |                      | 0            |             | 248 | μA    |    |

| I_steps          | current steps                         |                      | 6            | 8           | 10  | μA    |    |

| TC_CS            | temperature coefficient               |                      |              | 900         |     | ppm/K |    |

| lcurr_OFF        | current when off                      | room temperature     |              | 0.001       |     | μA    |    |

| lcurr_Ri         | internal resistance of current source | Ua < 2 V             |              | 10          |     | MOhm  |    |

| digital CMOS in  | puts with pull up and schmidt-trigger |                      | input PINs C | LK and SCLK |     |       |    |

| Vih              | high level input voltage              | VDDD=5V              | 3.5          |             |     | V     |    |

| Vil              | low level input voltage               | VDDD=5V              |              |             | 1.5 | V     |    |

| lih              | current level                         | VDDD=5V, Vih=5V      | -1           |             | 1   | μA    |    |

| lil              | current level                         | VDDD=5V, Vil=0       | 30           |             | 120 | μA    |    |

| digital CMOS o   | utputs                                | output PINs SDAT a   | ind INTN     |             |     |       |    |

| Voh              | high level output voltage             | VDDD=5V, -633uA      | 4.5          |             |     | V     |    |

| Vol              | low level output voltage              | VDDD=5V, 564uA       |              |             | 0.4 | V     |    |

| CI               | capacitive load                       |                      |              |             | 20  | pF    |    |

| Tristate digital | 1/0                                   |                      |              |             |     |       |    |

| Voh              | high level output voltage             | VDDD=5V, -633uA      | 4.5          |             |     | V     |    |

| Vol              | low level output voltage              | VDDD=5V, 564uA       |              |             | 0.4 | V     |    |

|                  | tristate leakage current to           |                      |              |             |     |       |    |

| loz              | VDDD,VSSD                             | VDDD=5V              | -1           |             | 1   | μA    |    |

| Vih              | high level input voltage              | VDDD=5V              | 3.5          |             |     | V     |    |

| Vil              | low level input voltage               | VDDD=5V              |              |             | 1.5 | V     |    |

| supply current   |                                       |                      |              |             |     |       |    |

| Isup             | normal operation                      | VDDD=VDDA=5V         |              | 3           | 5   | mA    |    |

| law              | active wake-up                        | VDDD=VDDA=5V         |              | 40          | 100 | μA    | 1) |

| supply voltage   |                                       |                      |              |             |     |       |    |

| VDDA             | positive analog supply voltage        |                      | 4.7          | 5.0         | 5.3 | V     | 2) |

| VDDD             | positive digital supply voltage       |                      | 4.5          | 5.0         | 5.5 | V     |    |

| VSS, VSSD        | negative supply voltage               |                      |              | 0           |     | V     |    |

| Power On Rese    | t                                     |                      |              |             |     |       |    |

| Vporhi           | Power on reset Hi                     | _                    |              | 3.1         |     | V     |    |

| Vhyst            | Hysteresis                            | 1                    |              | 0.2         |     | V     |    |

<sup>1)</sup> the average current is dependent on the on-time of the measurement system i.e. it can be programed via the CRA register 2) dynamic stability of analog supply should be within +/- 0.1 V

## 7 Functional Description

#### 7.1 Power on Reset

The power on reset is iniciated during each power up of the ASSP and can be triggered purpously by reducing the analog supply voltage (VDDA) to a value lower than Vporlo for a time interval longer than 0.5 µsec.

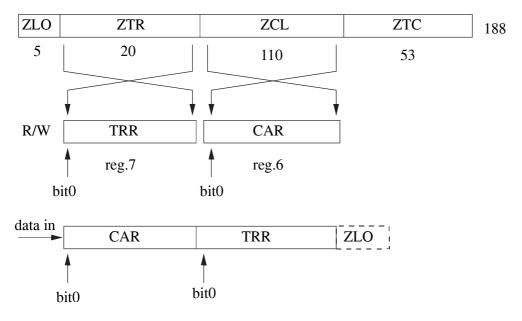

During power on reset sequence the following steps are performed automatically:

- The chip goes to mode MZL (see 7.4)

- Internal clock is enabled

- The calibration constants are loaded from Zener-zap memory to the appropriate registers (ZTR=>TRR, ZCL=>CAR). The load procedure is directed by the internal clock and can be monitored on INTN pin. 188 clock pulses are generated from the internal oscillator source. Pulse period is equal to internal clock period.

After the power-on reset sequence is finished:

- the operation continues with internal clock if no external clock is detected. In this case the ASSPs switches to mode MWU with default value of threshold register ( 214 )

- If external clock is available the ASSP switches to mode current measurement MMS (default measurement with default configuration: gain=100, fovs=4.096MHz, R1=64, MM=4, R2=1, N<sub>TH</sub>=2<sup>14</sup>).

- The microcontroller can communicate via SDI interface whenever appropriate, i.e. CAR and TRR register can be rewritten from the μC if necessary.

- Because the automatic selected calibration factor (CGI4) is loaded with zeros, the ASSP delivers constant zero at the output to allow the μC to check for an unwanted POR. To bring the ASSP back into normal operation for current measurement with gain100 the μC has to copy the CAU4 default content or a customer specific calibration factor into the CAR-register. (see also 7.5.5 and 8.6.2)

# 7.2 Analog part, general description

The input signals are level shifted to AGND (+ 2.5 V) then switched by the special high quality MUX- which contains also the chopper – to the input of the programmable gain amplifier (PGA). This low noise amplifier is optimised for best linearity, TC- value and speed at gain 24.

The systems contains an internal bandgap reference with high stability, low noise and low TC-value. The output of a programmable current source can be switched to the analog inputs VBAT, ETS and ETR for testing the sensor connections

or for external activation of resistors, bridges or sensors (RTD, NTC). The voltage drop generated by the current is measured at the corresponding input/output PIN.

For the wire break test of the RSHH and RSHL inputs special low noise current sources are implemented.

The integrated temperature sensor can also be switched to the PGA by the MUX and measured any time. The chip temperature can be used for the temperature compensation of

the gain of the different channels in the external  $\mu$  C, which increases the absolute accuracy considerably.

The offset of the amplifier itself is already fairly low, but to guarantee the full dynamic range it can be trimmed via the digital interface to nearly zero independent of the autozero chopping function.

In the same way the manufacturing spread of the absolute value of the reference voltage can be eliminated and the TC-value set to nearly zero by a trimming process via the SDI interface.

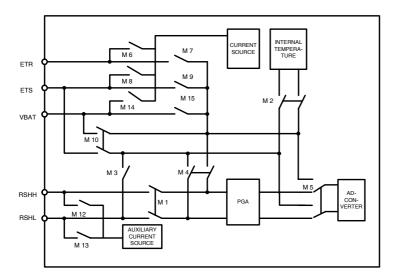

For more details of the input multiplexer see the following schematic. The position of all switches is defined by writing into the registers CRA, CRB and CRG via the SDI bus, which is explained in 7.5.2 through 7.5.4.

Figure 3: Multiplexer

# 7.2.1 Reference voltage

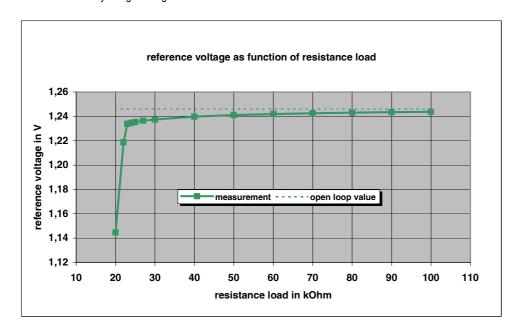

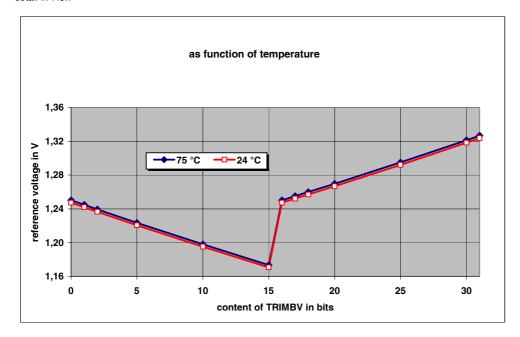

The ASSP contains a highly sophisticated precision reference voltage. Its typical temperature dependence is a slight parabola shaped curve and is shown in figure 14. This reference voltage is used mainly for the internal AD-converter, but can also be used for external purposes if the impedance of the external circuitry is high enough.

The absolute value and its temperature coefficient (TC) is given by the content of the TRR register. This opens the possibility to calibrate the reference voltage to the optimum absolute value (i.e. 1.28 V) and the TC value to zero thus eliminating fully the production spread.

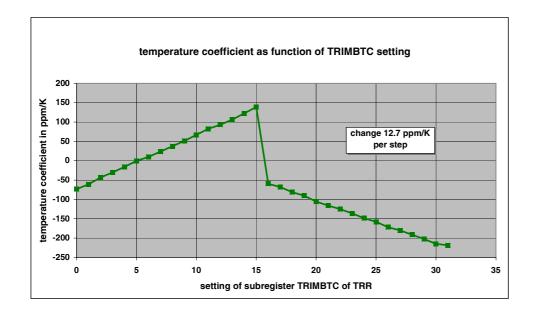

Writing into subregister TRIMBV of TRR changes the absolute value linearly by 5.1 mV per digit as shown in the following graph and described in full detail in 7.5.7

Trimming the TC value is similarly done by writing into subregister TRIMBTC. Since the TC trimming is also changing the absolute value it is important to trim the TC first and then the absolute value.

The TC trimming also opens the unique possibility to change the TC-value within the time of reprogramming of the TRR-register (i.e. within µ sec) to allow the compensation of different TC-values of the external circuitry for different channels.

In addition it can be used for very fast autocalibration of the total TC of a given channel. An external reference voltage is applied to the channel to be checked. Then all numbers from 0 to 31 are written into subregister TRIMBTC and a reading is done for the input voltage and the internal temperature as well. The same is repeated at any temperature above RT. From these data the TRIMBTC setting for a minimum drift can be easily calculated.

#### 7.2.2 Current sources

The AS8500 contains several current sources which can be used for checking all input lines for wire brake, to control external circuitry or to activate external sensors.

#### Main current source

The main current source can be digitally controlled via the content of the CRG register in 31 steps of 8  $\mu$ A in the range of 0 to 248  $\mu$ A. Its absolute value can be calibrated by writing in the subregister TRIMC of TRR.

The current source can be switched to the inputs VBAT, ETR or ETS to activate external sensors like RTDs, NTCs or resistance briges and strain gages. It can also be used to detect a wire breake of external connected sensors. Performing a measurement with a high and a low (or zero) current opens the possibility to eliminate thermal EMF voltages in external sensors.

# Secondary current sources

The ASSP contains two other high quality current sources supplying a current of approx.  $2\mu$  A at the inputs RSHL and RSHH. These current sources can be switched on and off at any time to check the correct connection of both terminals. During off state they must not interfere with the high sensitive voltage inputs, especially the noise level should not be increased. If one of the terminals is an open connection the amplifier goes into saturation and the overflow bit is set.

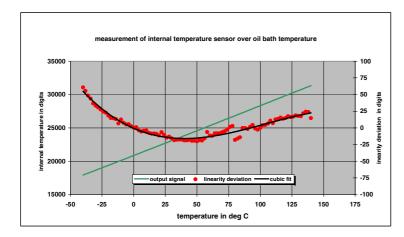

## 7.2.3 Internal temperature sensor

The ASSP contains a high sensitive precision temperature sensor which can be used at any time. The sensor supplies a very linear voltage with temperature. The voltage can be measured using the internal circuitry with gain 6, with free selection of all other parameters defining the sampling rate.

The slope of the curve is approx. 75 digits per degC.

The calculation of the temperature has to be done in the external  $\mu$  C acc. to the following simple formula:

Tint=

$$(Uint(T)-Uint(23))/75 + 23^{\circ}C$$

Uint(T) is the measured result and Uint(23) is the reference value at 23°C, which is stored as an 11 bit-word in the ZZR-register.

#### 7.3 Digital part

In the digital part the result of the AD-converter is processed, i.e. calibration, active offset cancellation and filtering is done. In addition the communication via the serial SDI interface is handled and all circuit functions (like voltage and current path settings, chopping, dechopping) are controlled.

Whenever the power supply line returns from below POR threshold a power-up circuitry is activated which loads the internal calibration registers from the Zener-Zap memory into the working register and starts the chip in a special default mode.

#### 7.3.1 Sampling rate

the sampling rate (SR) is defined by the setting of parameters in register CRA or CRB. The oversampling frequency (OSF), the oversampling ratio (OSR), the chopping ratio (MM) and the averaging number (AV). The sampling rate can be calculated acc. to the following formula:

SR= OSF/(OSR\*MM\*AV)

For an clock frequency of 8.192 MHz it can vary between 16 000 Hz and 1.95 Hz.

In the dual mode (see 7.4 mode 2) the ASSP is switching automatically between the two channels and it needs at least one measurement for each polarity to get a valid measurement. In addition the ASSP needs some time to reprogram the internal registers and switches. Therefore the maximum sampling frequency is limited to 7.5 kHz for the above given clock frequency. The internal averaging is not working in the dual mode, but the sampling frequency can be different for each channel.

#### 7.3.2 Calibration

The calibration of the ASSP is done by a test setup as follows:

- room temperature calibration of the internal temperature sensor

- absolute input-output calibration for all gain settings

- TC calibration for the measurement path for gain 24

The absolute input-output calibration of the gain ranges can be done that way that for a given input voltage 30 000 digits at the output are produced:

Table 7.2.2

| gain | input/mV | output/digits |

|------|----------|---------------|

| 1    | 720      | 30 000        |

| 6    | 120      | 30 000        |

| 24   | 30       | 30 000        |

| 50   | 15       | 30 000        |

| 100  | 7.5      | 30 000        |

The TC-value of the output (total measurement path) for G24 can be trimmed to a minimum value by selecting the best setting of the TRIMBTC subregister of the TRR register (see 7.5.7).

A factory calibration is done for the amplifier offset (TRIMA).

This data is stored in the ZZR register. ZZR-register mapping is given in 8.6.2

#### 7.4 Modes of operation

The AS8500 can run in different operation modes, which are selected and activated via the serial interface.

#### **Detailed description:**

#### Mode 0: MZL

In power-on reset sequence, which is initiated by the on-chip power-on reset circuit whenever the power is connected, the registers are loaded from the Zener-Zap memory.

#### Mode 1: MMS

Measurement mode where the definition is taken from the registers CRA and CRG defined later on. The measurements are continuous and measured results are available after the ready flag (INTN pin) is set to LO. The result can be read by the  $\mu$ C any time after this bit is set to LO. However, to obtain the best noise performances the result should be read when INTN pin is at LO state. All modules are in power-up.

#### Mode 2: MMD

Dual channel measurement mode. Two consecutive different measurements are performed according to the settings in the configuration registers CRA, CRB and CRG defined later (usually CRA defining current measurements and CRB voltage measurement). One complete measurement is performed with each setting. CRG register holds common settings.

The measurements are continuous (A,B,A,B). The 17<sup>th</sup> bit in the output register defines, which measurement has been executed according to the definition LO=A, HI=B.

The number of consecutive measurements with equal configuration is defined in register CRG (bits s3,s2,s1,s0). All modules are in power-up.

#### Mode 3: MWU

In this wake-up mode the internal clock finclk=256kHz is running and one complete measurement is performed in the period from 1 to 1.5 s with the parameter settings of the CRA register. Before the actual measurement is performed the logic powers up all internal circuits especially the AGND and the Vref. If the external load is higher than 70 kOhms both signals can be used for external triggering or even as interrupt for the  $\mu$ C.

If the external clock is not running, this input should be high impedance. To achieve a stable low idle current the oversampling ratio should be set to R1=128 and the CFG register must be programmed to x00003, see also 7.4 'Register description'. It is assumed that the threshold level in the THR register is defined within the 16 bit range, if not the default value is 210

After one measurement is finished all modules except the on- board oscillator and divider are switched into power down condition to save power. The MSR register is updated with the last measurement result. Whenever this value exceeds the digital threshold the (wake-up) INTN pin goes LO for one clock cycle to trigger the wake-up event in the external µC.

After that the circuit returns in power-down for approximately 1s. During this time the last measurement (MSR register) is available on the SDI interface.

In this intermediate sleep-mode all modules except internal oscillator and divider are in power-down mode. The SDI interface works independent which means that the measurement result is available by reading the MSR register. At any time the microprocessor can start any other mode via SDI. In such a case the external clock must be switched on first.

The chip goes in MWU mode (mode 3) after it received the command for that. After that command 6 or more additional CLK pulses are needed before external clock may go to power down mode (no CLK pulses, high level because of internal pull-up resistors). This 6 CLK pulses are needed for synchronisation. On the way back to normal mode this restriction is not needed.

# Mode 4: MAM

In this alarm mode the measurement defined in CRA is going on. The channel bit in the THR register must be cleared (channel A). The threshold value may be positive or negative. Whenever the measured value exceeds the digital threshold value in the THR register the pin INTN (in this mode its function is to signal alarm-condition) goes LO for one clock cycle. For negative threshold value the signed measurement result must be more negative than the THR value to activate the alarm. During measurements the signal INTN is high. All modules are in power-up, measurements are continuously going on.

# Mode 5: MZP

Zener-Zap programming/reading. This mode for factory programming only and should not be used by the customer.

#### Mode 6: MPD

Power down mode. Individual analog blocks can be disabled/enabled. The data acquisition system is not running during this mode is activated.

# Mode 7: MSI

The operation in this mode is exactly the same as in MMS mode except that the internal clock is used.

The SDI interface signals can become active whenever appropriate. This mode can be used if no external clock CLK is available. The measuring speed is reduced by a factor of 16.

**Modes 8-15**: These modes are reserved for testing purposes and should not be used by the customer. Reading and writing of some registers is only possible in these higher modes. Write to registers CAR (calibration register) and TRR (trimming register) is allowed only in test modes.

Modes of operation, register OPM

| Mode | Name | Description                             | mo3 | mo2 | mo1 | mo0 |

|------|------|-----------------------------------------|-----|-----|-----|-----|

| 0    | MZL  | Power on, loading from Zener-Zap memory | 0   | 0   | 0   | 0   |

| 1    | MMS  | Single measurement                      | 0   | 0   | 0   | 1   |

| 2    | MMD  | Double measurement (A,B,A,B)            | 0   | 0   | 1   | 0   |

| 3    | MWU  | Wake-up                                 | 0   | 0   | 1   | 1   |

| 4    | MAM  | Alarm                                   | 0   | 1   | 0   | 0   |

| 5    | MZP  | Zener program/read                      | 0   | 1   | 0   | 1   |

| 6    | MPD  | Power down                              | 0   | 1   | 1   | 0   |

| 7    | MSI  |                                         | 0   | 1   | 1   | 1   |

| 8-15 |      | Reserved for testing 1)                 | 1   | Х   | Х   | Х   |

#### Notes:

1) Register addresses 12, 13, 14 and 15 are reserved for testing and future options; operations on these registers must be avoided

# 7.5 Register description

In the following sections the register contents and their functions are described in detail. Since the length of some registers is too long to present clearly, the registers are logically subdivided according to their functions and described separately.

All internal functions are controlled by the contents of these registers which can be reloaded via the serial SDI interface at any time. The AS8500 contains the following registers:

| REGISTER | ADDRESS | SIZE | Contents                                | Detailled description see |

|----------|---------|------|-----------------------------------------|---------------------------|

| OPM      | 0       | 4    | Operating mode register                 | 7.5.1                     |

| CRA      | 1       | 17   | Measurement A configuration register    | 7.5.3                     |

| CRB      | 2       | 17   | Measurement B configuration register    | 7.5.4                     |

| CRG      | 3       | 28   | General configuration register          | 7.5.2                     |

| MSR      | 4       | 18   | Measurement result register             | 7.5.9                     |

| ZZR      | 5       | 188  | Zener-Zap register                      | 7.5.5                     |

| CAR      | 6       | 110  | Calibration register                    | 7.5.6                     |

| TRR      | 7       | 20   | Trimming register                       | 7.5.7                     |

| THR      | 8       | 17   | Alarm or wake-up threshold register     | 7.5.8                     |

| CFG      | 9       | 20   | Test and special configuration register | 1)                        |

| reserved | 10-12   |      | Test registers                          |                           |

Note: 1) This register is reserved for testing modes. Writing is possible only in mode 8. In order to assure stable conditions in power-down modes MWU(3), MPD(6), TMSS(8) and MSI(13) the default setting of the CFG register must be changed to x00003. It is not necessary to change this value during normal operation.

Write commands not supported in a certain mode can be released immediately after the register address. The ASSP will resume operation with the next start condition. Registers CAR and TRR are not buffered. Any read operation of the CAR or TRR register may generate transients in the analog circuitry; further accurate measurements require a delay time for settling.

# 7.5.1 OPM operation mode register (4 bits)

|   | no. | Bit     | mo3 | mo2 | mo1 | mo0 | Note |

|---|-----|---------|-----|-----|-----|-----|------|

| I | 0   | default | 0   | 0   | 0   | 0   | 1)   |

<sup>1)</sup> This register has been described in detail under 7.4

# 7.5.2 CRG general configuration register (28 bits)

| no. | CRG bits | 27-22 | 21-11 | 10-7 | 6-0 | NOTE |

|-----|----------|-------|-------|------|-----|------|

| 0   |          | CRS   | CRI   | CRV  | CRP |      |

#### subregister CRS: Sequence length, dechop and chop (6 bits)

| Nr. | Bits    | 5  | 4  | 3  | 2  | 1 | 0 | NOTE |

|-----|---------|----|----|----|----|---|---|------|

| 0   | CRS bit | s3 | s2 | s1 | s0 | d | С | 1)   |

|     | names   |    |    |    |    |   |   |      |

| 1   | Default | 0  | 0  | 0  | 1  | 1 | 1 | 2)   |

#### Notes:

## Sequence length bits (4bits)

| Nr. | No. of measurements | s3 | s2 | s1 | s0 | NOTE    |

|-----|---------------------|----|----|----|----|---------|

| 0   | 16                  | 0  | 0  | 0  | 0  | 1)      |

| 1   | 1                   | 0  | 0  | 0  | 1  | default |

|     |                     |    |    |    |    |         |

| 14  | 14                  | 1  | 1  | 1  | 0  |         |

| 15  | 15                  | 1  | 1  | 1  | 1  |         |

#### Notes:

#### **DECHOPPING BIT**

| Nr. | Dechopping    | d | NOTE |

|-----|---------------|---|------|

| 0   | No dechopping | 0 |      |

| 1   | Dechopping    | 1 |      |

#### **CHOPPING BIT**

| Nr. | Chopping    | С | NOTE |

|-----|-------------|---|------|

| 0   | No chopping | 0 |      |

| 1   | chopping    | 1 |      |

# subregister CRI: Current configuration (11 bits)

|     | gistor Orii. t | - WILL O | gu.u.uo. | ון וו טונט |     |     |     |    |    |    |    |    |       |

|-----|----------------|----------|----------|------------|-----|-----|-----|----|----|----|----|----|-------|

| Nr. | Bits           | 10       | 9        | 8          | 7   | 6   | 5   | 4  | 3  | 2  | 1  | 0  | NOTE  |

| 0   | CRI bit        | M14      | M13      | M12        | M11 | M8  | M6  | i4 | i3 | 12 | i1 | i0 | 1),3) |

|     | names          |          |          |            |     |     |     |    |    |    |    |    |       |

| 1   | Default        | 0        | 0        | 0          | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 2)    |

| 2   | output         | VBAT     | RSHL     | RSHH       | no  | ETS | ETR |    |    |    |    |    |       |

<sup>1)</sup> This register defines the sequence length, chopping (c) and dechopping (d) of the input signal

<sup>2)</sup> Default power-up state before any setting

<sup>&</sup>lt;sup>1)</sup>Number of consecutive measurements of A and B with settings defined in CRA,CRB and other settings in CRG register. This setting is used only for mode MMD.

<sup>1)</sup> whenever M1=1 in (CRA,CRB) it is good practice to set all M6 to M14 to zero, but it is not mandatory

$<sup>^{\</sup>rm 2)}$  default logic state after power up and before any setting

<sup>&</sup>lt;sup>3)</sup> All bits with names M14 to M1 represent control signals of the multiplexer with positive logic (for example M14=1 means that corresponding switch is closed).

# Current source setting bits (5 bits)

| Nr. | Current [uA] | i4 | i3 | i2 | i1 | i0 | NOTE |

|-----|--------------|----|----|----|----|----|------|

| 0   | 0            | 0  | 0  | 0  | 0  | 0  |      |

| 1   | 8            | 0  | 0  | 0  | 0  | 1  |      |

| 2   | 16           | 0  | 0  | 0  | 1  | 0  |      |

| 3   | 24           | 0  | 0  | 0  | 1  | 1  |      |

| 4   | 32           | 0  | 0  | 1  | 0  | 0  |      |

|     |              |    |    |    |    |    |      |

| 31  | 248          | 1  | 1  | 1  | 1  | 1  |      |

subregister CRV: Voltage configuration (4 bits )

|     | <b></b>  |       |              |          |      |       |

|-----|----------|-------|--------------|----------|------|-------|

| Nr. | Bits     | 3     | 2            | 1        | 0    | NOTE  |

| 0   | CRV bit  | M15   | M10          | M9       | M7   | 1),3) |

|     | names    |       |              |          |      |       |

| 1   | Defaults | 0     | 0            | 0        | 0    | 2)    |

| 2   | channel  | VBAT- | VBAT-ETS     | ETS-RSHL | ETR- |       |

|     |          | RSHL  | differential |          | RSHL |       |

#### Notes:

- 1) This register defines the connection of the analog voltage- bus to the input-PINs and to the A/D converter

- 2) Default logic state after power-up and before any setting

#### subregister CRP: Power down configuration (7 bits)

| Nr. | Bits     | p6         | p5        | p4    | р3        | p2      | p1       | p0     | NOTE  |

|-----|----------|------------|-----------|-------|-----------|---------|----------|--------|-------|

| 0   | CRP bit  | pdosc      | pda       | pdm   | pdb       | pdc     | pdi      | pdg    | 1),3) |

|     | names    |            |           |       |           |         |          |        |       |

| 1   | Defaults | 0          | 0         | 0     | 0         | 1       | 0        | 0      | 2)    |

| 2   | block    | oscillator | amplifier | modu- | ref. bias | current | internal | analog |       |

|     |          |            |           | lator |           | source  | temp.    | GND    |       |

# Notes:

- 1) This register defines the power-down signals of the building blocks

- 2) Default power-up state before any setting

- 3) The logic is positive (pdosc=1 means the corresponding block is in power-down)

# 7.5.3 CRA measurement channel A configuration register (17 bits)

| Nr. | Bits     | 16  | 15  | 14  | 13  | 12 | 11 | 10 | 9  | 8   | 7   | 6  | 5 | 4  | 3   | 2  | 1  | 0  | NOTE   |

|-----|----------|-----|-----|-----|-----|----|----|----|----|-----|-----|----|---|----|-----|----|----|----|--------|

| 0   | CRA bit  | cu2 | cu1 | cu0 | M5  | M4 | МЗ | M2 | M1 | g1  | g0  | f  | r | mm | n3  | n2 | n1 | n0 | 1), 3) |

|     | names    |     |     |     |     |    |    |    |    |     |     |    |   |    |     |    |    |    |        |

| 1   | Defaults | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 1  | 1   | 1   | 1  | 0 | 0  | 0   | 0  | 0  | 0  | 2)     |

| 2   | subreg.  |     | CRU |     | CRM |    |    | G  | N  | OSF | OSR | MM |   | C  | CRN |    |    |    |        |

- 1) This register defines the measurement channel A configuration

- 2) Default power-up state before any setting

- <sup>3)</sup> Bit M1 is control signal of the multiplexer for current input (for example M1=1 means that corresponding switch is closed).

subregister CRU: calibration constant selection for voltage path (3 bits) in registers CRA,CRB

| Nr. | Calibration const. U | cu2 | cu1 | cu0 | NOTE |

|-----|----------------------|-----|-----|-----|------|

| 0   | CAU0                 | 0   | 0   | 0   |      |

| 1   | CAU1                 | 0   | 0   | 1   |      |

| 2   | CAU2                 | 0   | 1   | 0   |      |

| 3   | CAU3                 | 0   | 1   | 1   |      |

| 4   | CAU4                 | 1   | 0   | 0   |      |

| 5   | CAU5                 | 1   | 0   | 1   |      |

| 6   | 1548                 | 1   | 1   | 0   |      |

| 7   | 1548                 | 1   | 1   | 1   |      |

subregister CRM: measurement path for registers CRA,CRB

| Nr. | Bits     | 13 | 12 | 11 | 10 | 9  | NOTE                                     |

|-----|----------|----|----|----|----|----|------------------------------------------|

|     | CRA bit  | M5 | M4 | М3 | M2 | M1 | 1), 2)                                   |

|     | names    |    |    |    |    |    |                                          |

| 1   | Defaults | 0  | 0  | 0  | 0  | 1  | measurement RSHH-RSHL                    |

| 2   |          | 0  | 1  | 0  | 0  | 0  | voltage bus                              |

| 3   |          | 0  | 1  | 0  | 1  | 0  | voltage bus, internal temperature        |

| 4   |          | 0  | 1  | 1  | 0  | 0  | voltage bus, reference low=RSHL          |

| 5   |          | 1  | 0  | 0  | 0  | 0  | voltage bus, gain=1                      |

| 6   |          | 1  | 0  | 0  | 1  | 0  | voltage bus,gain=1, internal temperature |

| 7   |          | 1  | 0  | 1  | 0  | 0  | voltage bus, gain=1, reference low=RSHL  |

## Notes:

- 1) these bits define the inner part of the voltage path settings

- 2) only the listed combinations are allowed

subregister GN: gain definition bits, Registers CRA,CRB

| Nr. | GAIN | g1 | g0 | NOTE |

|-----|------|----|----|------|

| 0   | 6    | 0  | 0  |      |

| 1   | 24   | 0  | 1  |      |

| 2   | 50   | 1  | 0  |      |

| 3   | 100  | 1  | 1  |      |

subregister OSF: oversampling frequency bit, Registers CRA,CRB

| Nr. | Fovs (fclk=8MHz) | Fovs (internal osc) | f | NOTE |

|-----|------------------|---------------------|---|------|

| 0   | 2.048MHz         | 132kHz              | 0 | 1)   |

| 1   | 4.096MHz         | 264kHz              | 1 | 1)   |

# Notes:

subregister OSR: oversampling ratio bit, Registers CRA, CRB

| Nr. | R1  | r | NOTE |

|-----|-----|---|------|

| 0   | 64  | 0 |      |

| 1   | 128 | 1 |      |

<sup>1)</sup> For internal oscillator typical values

subregister MM: chopping ratio bit, Registers CRA, CRB

| - care egictor initia | onepping radio and mognetore | • • • • • • • • • • • • • • • • • • • • | <b></b> |

|-----------------------|------------------------------|-----------------------------------------|---------|

| Nr.                   | MM                           | mm                                      | NOTE    |

| 0                     | 4                            | 0                                       |         |

| 1                     | 8                            | 1                                       |         |

| 2                     | 1                            | Χ                                       | 1)      |

#### Notes:

1) For c=0 and d=0, chopping and dechopping is switched off and every cycle is active regardless of mm, i.e. the sampling frequency is higher by a factor of 4

subregister CRN: averaging bits (4 bits), registers CRA,CRB

| Nr.   | R2                | n3 | n2 | n1 | n0 | NOTE |

|-------|-------------------|----|----|----|----|------|

| 0     | 1                 | 0  | 0  | 0  | 0  |      |

| 1     | 2                 | 0  | 0  | 0  | 1  |      |

| 2     | 4                 | 0  | 0  | 1  | 0  |      |

| 3     | 8                 | 0  | 0  | 1  | 1  |      |

| 4     | 16                | 0  | 1  | 0  | 0  |      |

| 5     | 32                | 0  | 1  | 0  | 1  |      |

| 6     | 64                | 0  | 1  | 1  | 0  |      |

| 7     | 128               | 0  | 1  | 1  | 1  |      |

| 8     | 256               | 1  | 0  | 0  | 0  |      |

| 9     | 512               | 1  | 0  | 0  | 1  |      |

| 10    | 1024              | 1  | 0  | 1  | 0  |      |

| 11-14 | Reserved for test | 1  | Х  | Х  | Х  | 1)   |

| 15    | raw mode          | 1  | 1  | 1  | 1  | 2)   |

#### Note:

The ratio between raw result (Nr) and normal result (Nn) is given by:  $Nr/Nn = 2^{(11+x)/CAL}$  where x=6 for R=128 and x=3 for R=64. CAL is the calibration constant used.

# 7.5.4 CRB measurement channel B configuration register (17 bits)

| Nr. | Bits     | 16  | 15  | 14  | 13 | 12 | 11  | 10 | 9  | 8  | 7  | 6   | 5   | 4  | 3  | 2  | 1  | 0  | NOTE   |

|-----|----------|-----|-----|-----|----|----|-----|----|----|----|----|-----|-----|----|----|----|----|----|--------|

| 0   | CRB bit  | cu2 | cu1 | cu0 | M5 | M4 | МЗ  | M2 | M1 | g1 | g0 | f   | r   | mm | n3 | n2 | n1 | n0 | 1), 3) |

|     | names    |     |     |     |    |    |     |    |    |    |    |     |     |    |    |    |    |    |        |

| 1   | Defaults | 0   | 0   | 0   | 0  | 1  | 1   | 0  | 0  | 0  | 1  | 1   | 0   | 0  | 0  | 0  | 0  | 0  | 2)     |

| 2   | subreg.  |     | CRU |     |    |    | CRM |    |    | (  | ЭΝ | OSF | OSR | MM |    | CF | RN |    |        |

<sup>1)</sup> combinations from B to E are reserved for test

<sup>&</sup>lt;sup>2)</sup> this mode delivers the AD-values without calibration and averaging but multiplied by a factor which is dependent on the setting of the oversampling ratio. It can be used for high resolution measurements of very low signals since it eliminates the internal rounding error.

<sup>&</sup>lt;sup>1)</sup> This register defines the measurement channel B configuration, the functions of the subregisters are the same as described above for measurement channel A

<sup>2)</sup> Default power-up state before any setting

<sup>3)</sup> In this mode the chip cannot measure the current sensing input RSHH-RSHL, therefore M1=0 for all settings

# 7.5.5 ZZR Zener-Zap register (188 bits ):

For the AS8500 the zener zap registers are set to a predefined default value. As an exception the TRIMA bits in the ZTR subregister is factory adjusted for minimum amplifier offset to ensure optimum linearity over input range.

| Nr. | ZZR bits | 183-187 | 163-182 | 53-162 | 0-52              | NOTE |

|-----|----------|---------|---------|--------|-------------------|------|

| 0   |          | ZLO     | ZTR     | ZCL    | ZTC <sup>1)</sup> | 2)   |

#### Notes:

1) 5 bits are reserved for:

- 1 bit eventually destroyed during testing,

- 2 bits for testing programmed 0 and 1

- 2 bits reserved for locking

# subregister ZLO: Zener spare bits (5 bits)

| Nr. | Name          | SYMBOL | WORD WIDTH | Default Hex |  |

|-----|---------------|--------|------------|-------------|--|

| 1   | Reserved bits | ZLO    | 5          | F           |  |

## subregister ZTR: trimming bits (20 bits)

| Nr. | PARAMETER                               | SYMBOL  | WORD<br>WIDTH | UNIT |

|-----|-----------------------------------------|---------|---------------|------|

| 0   | TC of reference                         | TRIMBTC | 5             | Bits |

| 1   | absolute value of reference             | TRIMBV  | 5             | Bits |

| 2   | amplifier offset                        | TRIMA   | 5             | Bits |

| 3   | current source for external temperature | TRIMC   | 5             | Bits |

| 4   | $\Sigma$ trim bits                      | TRIMREG | 20            | Bits |

# subregister ZCL: calibration bits (110 bits)

| Nr. | PARAMETER            | SYMBOL | WORD<br>WIDTH | UNIT |

|-----|----------------------|--------|---------------|------|

| 0   | Calibration G=6, I   | CGI1   | 11            | Bits |

| 1   | Calibration G=24, I  | CGI2   | 11            | Bits |

| 2   | Calibration G=50, I  | CGI3   | 11            | Bits |

| 3   | Calibration G=100, I | CGI4   | 11            | Bits |

| 4   | Calibration U0       | CAU0   | 11            | Bits |

| 5   | Calibration U1       | CAU1   | 11            | Bits |

| 6   | Calibration U2       | CAU2   | 11            | Bits |

| 7   | Calibration U3       | CAU3   | 11            | Bits |

| 8   | Calibration U4       | CAU4   | 11            | Bits |

| 9   | Calibration U5       | CAU5   | 11            | Bits |

| 10  | $\Sigma$ cal. Bits   | ZCL    | 110           | Bits |

Calibration constants are selected dependent on state of M1 ( see table below). For M1=1 one of CGI1 to CGI4 is selected according to selected gain of amplifier. For M1=0 the selection of the calibration constants is defined by bits (cu2,cu1,cu0), which are part of CRA and CRB registers and are defined via SDI interface independently of any other selection.

<sup>2)</sup> due to a limited driving capability of the ZZR-cells the maximum reading speed is limited to 500 kHz

# Calibration constant selection truth table

| Nr. | cu2 | cu1 | cu0 | M1 | g1 | g0 | CAL CONST | NOTE |

|-----|-----|-----|-----|----|----|----|-----------|------|

| 0   | Х   | Х   | Х   | 1  | 0  | 0  | CGI1      | 1)   |

| 1   | Х   | Х   | Х   | 1  | 0  | 1  | CGI2      | 1)   |

| 2   | Х   | Х   | Х   | 1  | 1  | 0  | CGI3      | 1)   |

| 3   | Х   | Х   | Х   | 1  | 1  | 1  | CGI4      | 1)   |

| 4   | 0   | 0   | 0   | 0  | Х  | Х  | CAU0      | 2)   |

| 5   | 0   | 0   | 1   | 0  | Х  | Х  | CAU1      | 2)   |

| 6   | 0   | 1   | 0   | 0  | Х  | Х  | CAU2      | 2)   |

| 7   | 0   | 1   | 1   | 0  | Х  | Х  | CAU3      | 2)   |

| 8   | 1   | 0   | 0   | 0  | Х  | Х  | CAU4      | 2)   |

| 9   | 1   | 0   | 1   | 0  | Х  | Х  | CAU5      | 2)   |

| 10  | 1   | 1   | 0   | 0  | Х  | Х  | 1548      |      |

| 11  | 1   | 1   | 1   | 0  | Х  | Х  | 1548      |      |

#### Notes:

# subregister ZTC:

These bits are spare bits and can be used on special request (e.g. ID number).

<sup>1)</sup> CGIx calibration constants are selected when M1=1 according to selected gain

<sup>&</sup>lt;sup>2)</sup> CGUx calibration constants are selected when M1=0 according to bits cu2 to cu0 defined via SDI in CRA and/or CRB registers.

# 7.5.6 CAR calibration register (110 bits)

The aim of the calibration register is to hold the calibration constants that are used by the internal DSP for the correction of each measurement (for the factory calibrated version AS8501). At power-up sequence the Zener-Zap subregister ZCL default setting is copied into the CAR register. The register can be read or written in mode 8 via the SDI bus at any time. In particular for the AS8500, which is not factory calibrated it is intended to overwrite the default setting with external data defined by the user.

| Nr. | CAR bits    | 109-99 | 98-88 | 87-77 | 76-66 | 65-55 | 54-44 | 43-33 | 32-22 | 21-11 | 10-0 | NOTE |

|-----|-------------|--------|-------|-------|-------|-------|-------|-------|-------|-------|------|------|

| 0   | Subregister | CGI1   | CGI2  | CGI3  | CGI4  | CAU0  | CAU1  | CAU2  | CAU3  | CAU4  | CAU5 | 1)   |

| 1   | default     | 1548   | 1548  | 1548  | 0     | 1548  | 2047  | 2047  | 1548  | 1548  | 1548 | 2)   |

#### Notes:

- Calibration register is composed of the following constants each having 11 bits: CGI1, CGI2, CGI3, CGI4, CAU0, CAU1, CAU2, CAU3, CAU4, CAU5

- <sup>2)</sup> Decimal default value of the calibration constant for voltage and current is calculated using formula: CG<sub>def</sub>=N<sub>max</sub>/N<sub>ADdef</sub>=(V<sub>ref</sub>\*1024)/(V<sub>in</sub>\*G<sub>max</sub>)=1548

#### 7.5.7 TRR trimming register (20 bits)

In the TRR register the calibration constants for the reference voltage, for the amplifier-offset trim and for the current source setting are stored. At power-up sequence the Zener-Zap subregister ZTR is loaded into the TRR register. This register can be read or written in mode 8 via the SDI bus. In particular it is possible to write preliminary calibration constants into TRR or overwrite the loaded ZTR data, if a calibration has been changed. The trimming of the TRR-registors is usually done at the factory before supplying the part.

| Nr. | TRR bits    | 19-15 | 14-10      | 9-5    | 4-0     | NOTE |

|-----|-------------|-------|------------|--------|---------|------|

| 0   | Subregister | TRIMC | TRIMA      | TRIMBV | TRIMBTC | 1)   |

| 1   | default     | 4     | typ 0 or 1 | 16     | 17      |      |

#### Notes:

# subregister TRIMC

change of current source output with TRIMC bits

| Nr. | trimcs | trimc3 | trimc2 | trimc1 | trimc0 | dl/lo   | Notes |

|-----|--------|--------|--------|--------|--------|---------|-------|

|     |        |        |        |        |        | %       |       |

| 0   | 0      | 0      | 0      | 0      | 0      | 0       | 1),2) |

| 1   | 0      | 0      | 0      | 0      | 1      | -1*2.3  | 1),2) |

| 2   | 0      | 0      | 0      | 1      | 0      | -2*2.3  | 1),2) |

|     |        |        | :      | :      | :      |         |       |

| 14  | 0      | 1      | 1      | 1      | 0      | -14*2.3 | 1),2) |

| 15  | 0      | 1      | 1      | 1      | 1      | -15*2.3 | 1),2) |

| 16  | 1      | 0      | 0      | 0      | 0      | 16*2.3  | 1),2) |

| 17  | 1      | 0      | 0      | 0      | 1      | 15*2.3  |       |

| 18  | 1      | 0      | 0      | 1      | 0      | 14*2.3  | 1),2) |

|     |        |        |        |        | :      |         |       |