### imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

### Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### 128K X 36, 256K X 18 3.3V Svnchronous SRAMs 3.3V I/O, Flow-Through Outputs **Burst Counter, Single Cycle Deselect**

### AS8C403625 AS8C401825

### Features

- 128K x 36, 256K x 18 memory configurations ٠

- Supports fast access times: Commercial:

- 7.5ns up to 117MHz clock frequency

- LBO input selects interleaved or linear burst mode

- Self-timed write cycle with global write control (GW), byte write enable ( $\overline{BWE}$ ), and byte writes ( $\overline{BWx}$ )

- 3.3V core power supply

- Power down controlled by ZZ input

- 3.3V I/O

- **Optional Boundary Scan JTAG Interface (IEEE 1149.1** compliant)

- Packaged in a JEDEC Standard 100-pin plastic thin quad flatpack(TQFP),

### Description

TheAS8C403625/1825 are high-speed SRAMs organized as 128K x 36/256K x 18. The AS8C403625/1825 SRAMs contain write, data, address and control registers. There are no registers in the data output path (flow-through architecture). Internal logic allows the SRAM to generate a self-timed write based upon a decision which can be left until the end of the write cycle.

The burst mode feature offers the highest level of performance to the system designer, as the AS8C403625/1825 can provide four cycles of data for a single address presented to the SRAM. An internal burst address counter accepts the first cycle address from the processor, initiating the access sequence. The first cycle of output data will flow-through from the array after a clock-to-data access time delay from the rising clock edge of the same cycle. If burst mode operation is selected (ADV=LOW), the subsequent three cycles of output data will be available to the user on the next three rising clock edges. The order of these three addresses are defined by the internal burst counter and the LBO input pin.

The AS8C403625/1825 SRAMs utilize IDT's latest high-performance CMOS process and are packaged in a JEDEC standard 14mm x 20mm 100-pin thin plastic guad flatpack (TQFP)

|                                                                                             | ion Summary                       |        |              |

|---------------------------------------------------------------------------------------------|-----------------------------------|--------|--------------|

| A0-A17                                                                                      | Address Inputs                    | Input  | Synchronous  |

| CE                                                                                          | Chip Enable                       | Input  | Synchronous  |

| CS0, CS1                                                                                    | Chip Selects                      | Input  | Synchronous  |

| ŌĒ                                                                                          | Output Enable                     | Input  | Asynchronous |

| GW                                                                                          | Global Write Enable               | Input  | Synchronous  |

| BWE                                                                                         | Byte Write Enable                 | Input  | Synchronous  |

| $\overline{BW}_{1}$ , $\overline{BW}_{2}$ , $\overline{BW}_{3}$ , $\overline{BW}_{4}^{(1)}$ | Individual Byte Write Selects     | Input  | Synchronous  |

| CLK                                                                                         | Clock                             | Input  | N/A          |

| ADV                                                                                         | Burst Address Advance             | Input  | Synchronous  |

| ADSC                                                                                        | Address Status (Cache Controller) | Input  | Synchronous  |

| ADSP                                                                                        | Address Status (Processor)        | Input  | Synchronous  |

| LBO                                                                                         | Linear / Interleaved Burst Order  | Input  | DC           |

| TMS                                                                                         | Test Mode Select                  | Input  | Synchronous  |

| TDI                                                                                         | Test Data Input                   | Input  | Synchronous  |

| ТСК                                                                                         | Test Clock                        | Input  | N/A          |

| TDO                                                                                         | Test Data Output                  | Output | Synchronous  |

| TRST                                                                                        | JTAG Reset (Optional)             | Input  | Asynchronous |

| Z                                                                                           | Sleep Mode                        | Input  | Asynchronous |

| /O0 <b>-I</b> /O31, <b>I</b> /OP1 <b>-I</b> /OP4                                            | Data Input / Output               | I/O    | Synchronous  |

| Vdd, Vddq                                                                                   | Core Power, I/O Power             | Supply | N/A          |

| Vss                                                                                         | Ground                            | Supply | N/A          |

1.  $\overline{BW}_3$  and  $\overline{BW}_4$  are not applicable for the AS8C401825.

### SEPTEMBER 2010

5280 tbl 02

### **Pin Definitions**<sup>(1)</sup>

| Symbol                    | Pin Function                         | I/O | Active | Description                                                                                                                                                                                                                                                                                                                                              |

|---------------------------|--------------------------------------|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0-A17                    | Address Inputs                       | 1   | N/A    | Synchronous Address inputs. The address register is triggered by a combi-nation of the rising edge of CLK                                                                                                                                                                                                                                                |

|                           |                                      |     |        | and ADSC Low or ADSP Low and CE Low.                                                                                                                                                                                                                                                                                                                     |

| ADSC                      | Address Status<br>(Cache Controller) | I   | LOW    | Synchronous Address Status from Cache Controller. ADSC is an active LOW input that is used to load the address registers with new addresses.                                                                                                                                                                                                             |

| ADSP                      | Address Status<br>(Processor)        | I   | LOW    | Synchronous Address Status from Processor. ADSP is an active LOW input that is used to load the address registers with new addresses. ADSP is gated by CE.                                                                                                                                                                                               |

| ĀDV                       | Burst Address<br>Advance             | I   | LOW    | Synchronous Address Advance. ADV is an active LOW input that is used to advance the internal burst counter, controlling burst access after the initial address is loaded. When the input is HIGH the burst counter is not incremented; that is, there is no address advance.                                                                             |

| BWE                       | Byte Write Enable                    | I   | LOW    | Synchronous byte write enable gates the byte write inputs $\overline{BW_1}$ - $\overline{BW_4}$ . If $\overline{BWE}$ is LOW at the rising edge of CLK then $\overline{BWx}$ inputs are passed to the next stage in the circuit. If $\overline{BWE}$ is HIGH then the byte write inputs are blocked and only $\overline{GW}$ can initiate a write cycle. |

| B₩1-B₩4                   | Individual Byte<br>Write Enables     | Ι   | LOW    | Synchronous byte write enables. $\overline{BW_1}$ controls I/O0-7, I/OP1, $\overline{BW_2}$ controls I/O8-15, I/OP2, etc. Any active byte write causes all outputs to be disabled.                                                                                                                                                                       |

| CE                        | Chip Enable                          | I   | LOW    | Synchronous chip enable. $\overline{CE}$ is used with CSo and $\overline{CS}_1$ to enable AS8C403625/1825. $\overline{CE}$ also gates $\overline{ADSP}$ .                                                                                                                                                                                                |

| CLK                       | Clock                                | I   | N/A    | This is the clock input. All timing references for the device are made with respect to this input.                                                                                                                                                                                                                                                       |

| CS0                       | Chip Select 0                        | I   | HIGH   | Synchronous active HIGH chip select. CSo is used with $\overline{CE}$ and $\overline{CS}$ I to enable the chip.                                                                                                                                                                                                                                          |

| $\overline{CS}_1$         | Chip Select 1                        | I   | LOW    | Synchronous active LOW chip select. $\overline{CS}_1$ is used with $\overline{CE}$ and CSo to enable the chip.                                                                                                                                                                                                                                           |

| GW                        | Global Write<br>Enable               | I   | LOW    | Synchronous global write enable. This input will write all four 9-bit data bytes when LOW on the rising edge of CLK. GW supersedes individual byte write enables.                                                                                                                                                                                        |

| I/O0-I/O31<br>I/Op1-I/Op4 | Data Input/Output                    | I/O | N/A    | Synchronous data input/output (I/O) pins. The data input path is registered, triggered by the rising edge of CLK. The data output path is flow-through (no output register).                                                                                                                                                                             |

| LBO                       | Linear Burst Order                   | I   | LOW    | Asynchronous burst order selection input. When $\overline{\text{LBO}}$ is HIGH, the inter-leaved burst sequence is selected.<br>When $\overline{\text{LBO}}$ is LOW the Linear burst sequence is selected. $\overline{\text{LBO}}$ is a static input and must not change state while the device is operating.                                            |

| ŌĒ                        | Output Enable                        | I   | LOW    | Asynchronous output enable. When $\overline{OE}$ is LOW the data output drivers are enabled on the I/O pins if the chip is also selected. When $\overline{OE}$ is HIGH the I/O pins are in a high-impedance state.                                                                                                                                       |

| TMS                       | Test ModeSelect                      | I   | N/A    | Gives input command for TAP controller. Sampled on rising edge of TDK. This pin has an internal pullup.                                                                                                                                                                                                                                                  |

| TDI                       | Test Data Input                      | I   | N/A    | Serial input of registers placed between TDI and TDO. Sampled on rising edge of TCK. This pin has an internal pullup.                                                                                                                                                                                                                                    |

| TCK                       | Test Clock                           | I   | N/A    | Clock input of TAP controller. Each TAP event is clocked. Test inputs are captured on rising edge of TCK, while test outputs are driven from the falling edge of TCK. This pin has an internal pullup.                                                                                                                                                   |

| TDO                       | Test DataOutput                      | 0   | N/A    | Serial output of registers placed between TDI and TDO. This output is active depending on the state of the TAP controller.                                                                                                                                                                                                                               |

| TRST                      | JTAG Reset<br>(Optional)             | I   | LOW    | Optional Asynchronous JTAG reset. Can be used to reset the TAP controller, but not required. JTAG reset occurs automatically at power up and also resets using TMS and TCK per IEEE 1149.1. If not used TRST can be left floating. This pin has an internal pullup. Only available in BGA package.                                                       |

| ZZ                        | Sleep Mode                           | I   | HIGH   | Asynchronous sleep mode input. ZZ HIGH will gate the CLK internally and power down the AS8C403625/1825 to its lowest power consumption level. Data retention is guaranteed in Sleep Mode. This pin has an internal pull down.                                                                                                                            |

| Vdd                       | Power Supply                         | N/A | N/A    | 3.3V core power supply.                                                                                                                                                                                                                                                                                                                                  |

| VDDQ                      | Power Supply                         | N/A | N/A    | 3.3V I/O Supply.                                                                                                                                                                                                                                                                                                                                         |

| Vss                       | Ground                               | N/A | N/A    | Ground.                                                                                                                                                                                                                                                                                                                                                  |

| NC                        | No Connect                           | N/A | N/A    | NC pins are not electrically connected to the device.                                                                                                                                                                                                                                                                                                    |

NOTE:

1. All synchronous inputs must meet specified setup and hold times with respect to CLK.

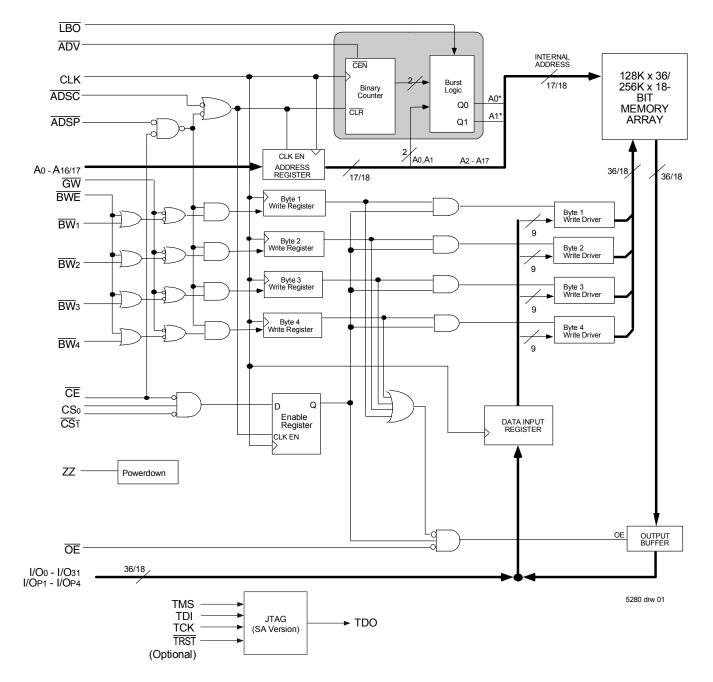

### **Functional Block Diagram**

### Absolute Maximum Ratings<sup>(1)</sup>

| Symbol               | Rating                                     | Commercial &<br>Industrial Values | Unit |

|----------------------|--------------------------------------------|-----------------------------------|------|

| VTERM <sup>(2)</sup> | Terminal Voltage with<br>Respect to GND    | -0.5 to +4.6                      | V    |

| $VTERM^{(3,6)}$      | Terminal Voltage with<br>Respect to GND    | -0.5 to VDD                       | V    |

| $VTERM^{(4,6)}$      | Terminal Voltage with<br>Respect to GND    | -0.5 to VDD +0.5                  | V    |

| $VTERM^{(5,6)}$      | Terminal Voltage with<br>Respect to GND    | -0.5 to VDDQ +0.5                 | V    |

| TA <sup>(7)</sup>    | <b>Commercial</b><br>Operating Temperature | -0 to +70                         | °C   |

|                      | Industrial<br>Operating Temperature        | -40 to +85                        | ٥c   |

| TBIAS                | Temperature<br>Under Bias                  | -55 to +125                       | °C   |

| Tstg                 | Storage<br>Temperature                     | -55 to +125                       | °C   |

| Рт                   | Power Dissipation                          | 2.0                               | W    |

| lout                 | DC Output Current                          | 50                                | mA   |

### NOTES:

1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- 2. VDD terminals only.

- 3. VDDQ terminals only.

- 4. Input terminals only.

- 5. I/O terminals only.

- 6. This is a steady-state DC parameter that applies after the power supplies have ramped up. Power supply sequencing is not necessary; however, the voltage on any input or I/O pin cannot exceed VDDQ during power supply ramp up.

- 7. TA is the "instant on" case temperature.

### **100 Pin TQFP Capacitance**

$(T_A = +25^{\circ} C_1 f = 1.0 mhz)$

| Symbol | Parameter <sup>(1)</sup> | Conditions | Max. | Unit |  |

|--------|--------------------------|------------|------|------|--|

| CIN    | Input Capacitance        | Vıℕ = 3dV  | 5    | pF   |  |

| Cvo    | I/O Capacitance          | Vout = 3dV | 7    | pF   |  |

5280 tbl 07

### 165 fBGA Capacitance (TA = +25° C, f = 1.0mhz)

| Symbol | Parameter <sup>(1)</sup> | Conditions | Max. | Unit         |

|--------|--------------------------|------------|------|--------------|

| CIN    | Input Capacitance        | Vıℕ = 3dV  | 7    | pF           |

| Cıvo   | I/O Capacitance          | Vout = 3dV | 7    | pF           |

| NOTE   |                          |            | 5    | 5280 tbl 07b |

NOTE:

1. This parameter is guaranteed by device characterization, but not production tested.

| Grade      | Temperature <sup>(1)</sup> | Vss | Vdd     | VDDQ    |

|------------|----------------------------|-----|---------|---------|

| Commercial | 0°C to +70°C               | 0V  | 3.3V±5% | 3.3V±5% |

| Industrial | -40°C to +85°C             | 0V  | 3.3V±5% | 3.3V±5% |

NOTES:

1. TA is the "instant on" case temperature.

### **Recommended DC Operating** Conditions

| Symbol | Parameter                   | Min.                | Тур. | Max.                     | Unit       |

|--------|-----------------------------|---------------------|------|--------------------------|------------|

| Vdd    | Core Supply Voltage         | 3.135               | 3.3  | 3.465                    | ۷          |

| Vddq   | I/O Supply Voltage          | 3.135               | 3.3  | 3.465                    | ۷          |

| Vss    | Supply Voltage              | 0                   | 0    | 0                        | ۷          |

| Viн    | Input High Voltage - Inputs | 2.0                 | _    | VDD +0.3                 | ۷          |

| Vін    | Input High Voltage - I/O    | 2.0                 |      | VDDQ +0.3 <sup>(1)</sup> | ۷          |

| VIL    | Input Low Voltage           | -0.3 <sup>(2)</sup> |      | 0.8                      | ۷          |

| NOTEO  |                             |                     |      | 54                       | 000 Hol 00 |

NOTES:

5280 tbl 03

5280 tbl 06

5280 tbl 04

1. VIH (max) = VDDQ + 1.0V for pulse width less than tcyc/2, once per cycle.

2. VIL (min) = -1.0V for pulse width less than  $t_{CYC/2}$ , once per cycle.

### **119 BGA Capacitance** $(T_A = +25^{\circ} C, f = 1.0 mhz)$

| Symbol | Parameter <sup>(1)</sup> | Conditions | Max. | Unit |

|--------|--------------------------|------------|------|------|

| Cin    | Input Capacitance        | Vıℕ = 3dV  | 7    | pF   |

| Cvo    | I/O Capacitance          | Vout = 3dV | 7    | pF   |

5280 tbl 07a

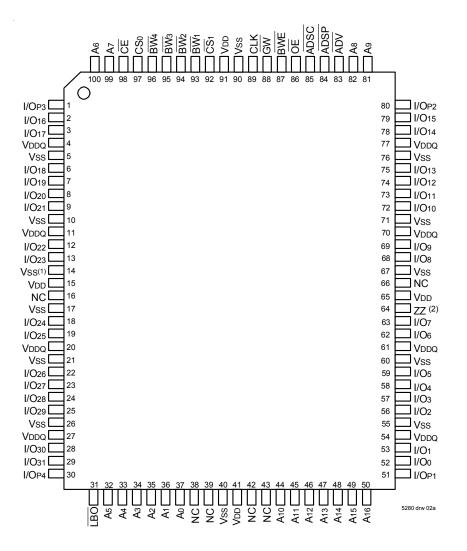

### Pin Configuration – 128K x 36

100 TQFP Top View

- 1. Pin 14 does not have to be directly connected to Vss as long as the input voltage is  $\leq$  VIL.

- 2. Pin 64 can be left unconnected and the device will always remain in active mode.

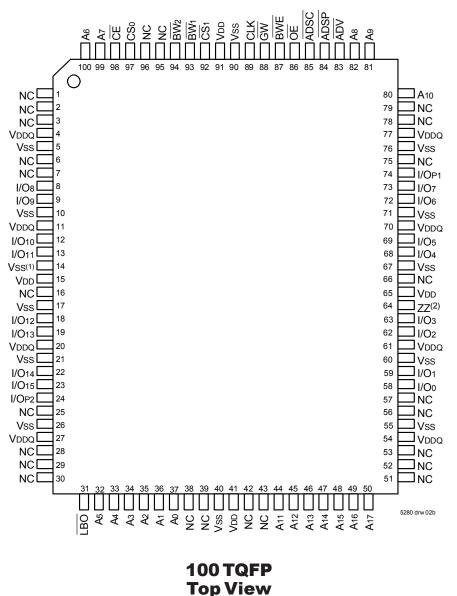

### Pin Configuration – 256K x 18

- 1. Pin 14 does not have to be directly connected to Vss as long as the input voltage is < VIL.

- 2. Pin 64 can be left unconnected and the device will always remain in active mode.

### **DC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range** (VDD = 3.3V ± 5%)

| Symbol | Parameter                                                        | Test Conditions                          | Min. | Max. | Unit        |

|--------|------------------------------------------------------------------|------------------------------------------|------|------|-------------|

| llul   | Input Leakage Current                                            | $V_{DD} = Max., V_{IN} = 0V$ to $V_{DD}$ | _    | 5    | μA          |

| lLi    | $Z\!Z$ , $\overline{LBO}$ and JTAG Input Leakage $Current^{(1)}$ | VDD = Max., Vℕ = 0V to VDD               | _    | 30   | μA          |

| lliol  | Output Leakage Current                                           | Vout = 0V to VDDa, Device Deselected     | _    | 5    | μA          |

| Vol    | Output Low Voltage                                               | IOL = +8mA, VDD = Min.                   | _    | 0.4  | V           |

| Vон    | Output High Voltage                                              | IOH = -8mA, $VDD = Min$ .                | 2.4  |      | V           |

|        |                                                                  |                                          |      |      | 5280 tbl 08 |

NOTE:

1. The LBO, TMS, TDI, TCK and TRST pins will be internally pulled to Vod and the ZZ in will be internally pulled to Vss if they are not actively driven in the application.

### **DC Electrical Characteristics Over the Operating** Temperature and Supply Voltage Range (1)

|        |                                       |                                                                                                                                                                                                     | 7.5ns      | 8ns   |     | 8.5ns |     |           |

|--------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------|-----|-------|-----|-----------|

| Symbol | Parameter                             | Test Conditions                                                                                                                                                                                     | Com'l Only | Com'l | Ind | Com'l | Ind | Unit      |

| ldd    | Operating Power Supply Current        | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                | 255        | 200   | 210 | 180   | 190 | mA        |

| ISB1   | CMOS Standby Power<br>Supply Current  | Device Deselected, Outputs Open, VDD = Max., VDD = Max., VDD = Max., VIN $\geq$ VHD or $\leq$ VLD, f = 0 <sup>(2,3)</sup>                                                                           | 30         | 30    | 35  | 30    | 35  | mA        |

| ISB2   | Clock Running Power<br>Supply Current | $\begin{array}{l} \mbox{Device Deselected, Outputs Open, Vdd} = Max., \\ \mbox{Vdd} = Max., \ \mbox{Vin} \geq \mbox{VHd} \ \mbox{or} \leq \mbox{VLD}, \ \mbox{f} = \mbox{fmax}^{(2,3)} \end{array}$ | 90         | 85    | 95  | 80    | 90  | mA        |

| lzz    | Full Sleep Mode Supply Current        | $ZZ \ge VHD$ , $VDD = Max$ .                                                                                                                                                                        | 30         | 30    | 35  | 30    | 35  | mA        |

| NOTES: |                                       |                                                                                                                                                                                                     |            |       |     |       | 528 | 30 tbl 09 |

NOTES:

1. All values are maximum guaranteed values.

2. At f = fMAX, inputs are cycling at the maximum frequency of read cycles of 1/tcyc while ADSC = LOW; f=0 means no input lines are changing.

3. For I/Os VHD = VDDQ - 0.2V, VLD = 0.2V. For other inputs VHD = VDD - 0.2V, VLD = 0.2V.

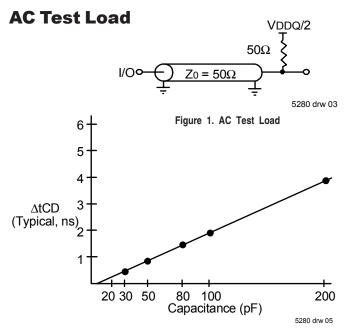

### **AC Test Conditions** (VDDQ = 3.3V)

| <u>(</u>                       |              |

|--------------------------------|--------------|

| Input Pulse Levels             | 0 to 3V      |

| Input Rise/Fall Times          | 2ns          |

| Input Timing Reference Levels  | 1.5V         |

| Output Timing Reference Levels | 1.5V         |

| AC Test Load                   | See Figure 1 |

|                                | 5280 tbl 10  |

Figure 2. Lumped Capacitive Load, Typical Derating

### Synchronous Truth Table <sup>(1,3)</sup>

| Synchronous Trut Operation   | Address  | Ē | CS0 | <u>CS</u> 1 | ADSP | ADSC | ĀDV | GW | BWE | ₩x | OE <sup>(2)</sup> | CLK        | I/O  |

|------------------------------|----------|---|-----|-------------|------|------|-----|----|-----|----|-------------------|------------|------|

|                              | Used     |   |     |             |      |      |     |    |     |    |                   |            |      |

| Deselected Cycle, Power Down | None     | Н | Х   | Х           | Х    | L    | Х   | Х  | Х   | Х  | Х                 | ↑          | HI-Z |

| Deselected Cycle, Power Down | None     | L | Х   | Н           | L    | Х    | Х   | Х  | Х   | Х  | Х                 | 1          | HI-Z |

| Deselected Cycle, Power Down | None     | L | L   | Х           | L    | Х    | Х   | Х  | Х   | Х  | Х                 | Ŷ          | HI-Z |

| Deselected Cycle, Power Down | None     | L | Х   | Н           | Х    | L    | Х   | Х  | Х   | Х  | Х                 | Ŷ          | HI-Z |

| Deselected Cycle, Power Down | None     | L | L   | Х           | Х    | L    | Х   | Х  | Х   | Х  | Х                 | Ŷ          | HI-Z |

| Read Cycle, Begin Burst      | External | L | Н   | L           | L    | Х    | Х   | Х  | Х   | Х  | L                 | Ŷ          | Dout |

| Read Cycle, Begin Burst      | External | L | Н   | L           | L    | Х    | Х   | Х  | Х   | Х  | Н                 | Ŷ          | HI-Z |

| Read Cycle, Begin Burst      | External | L | Н   | L           | н    | L    | Х   | Н  | Н   | Х  | L                 | Ŷ          | Dout |

| Read Cycle, Begin Burst      | External | L | Н   | L           | Н    | L    | Х   | Н  | L   | Н  | L                 | $\uparrow$ | Dout |

| Read Cycle, Begin Burst      | External | L | Н   | L           | Н    | L    | Х   | Н  | L   | Н  | Н                 | Ŷ          | HI-Z |

| Write Cycle, Begin Burst     | External | L | Н   | L           | н    | L    | Х   | Н  | L   | L  | Х                 | Ŷ          | DiN  |

| Write Cycle, Begin Burst     | External | L | Н   | L           | н    | L    | Х   | L  | Х   | Х  | Х                 | Ŷ          | Din  |

| Read Cycle, Continue Burst   | Next     | Х | Х   | Х           | н    | н    | L   | Н  | н   | Х  | L                 | Ŷ          | Dout |

| Read Cycle, Continue Burst   | Next     | Х | Х   | х           | н    | н    | L   | Н  | Н   | Х  | Н                 | Ŷ          | HI-Z |

| Read Cycle, Continue Burst   | Next     | Х | Х   | х           | н    | Н    | L   | Н  | Х   | Н  | L                 | Ŷ          | Dout |

| Read Cycle, Continue Burst   | Next     | Х | Х   | Х           | Н    | Н    | L   | Н  | Х   | Н  | Н                 | Ŷ          | HI-Z |

| Read Cycle, Continue Burst   | Next     | Н | Х   | Х           | х    | Н    | L   | Н  | Н   | Х  | L                 | Ŷ          | Dout |

| Read Cycle, Continue Burst   | Next     | н | Х   | Х           | Х    | н    | L   | н  | Н   | Х  | Н                 | Ŷ          | HI-Z |

| Read Cycle, Continue Burst   | Next     | н | Х   | Х           | Х    | н    | L   | н  | Х   | Н  | L                 | Ŷ          | Dout |

| Read Cycle, Continue Burst   | Next     | н | Х   | Х           | х    | н    | L   | н  | Х   | Н  | Н                 | Ŷ          | HI-Z |

| Write Cycle, Continue Burst  | Next     | Х | Х   | Х           | н    | н    | L   | Н  | L   | L  | Х                 | $\uparrow$ | Din  |

| Write Cycle, Continue Burst  | Next     | Х | Х   | Х           | н    | Н    | L   | L  | Х   | Х  | Х                 | $\uparrow$ | Din  |

| Write Cycle, Continue Burst  | Next     | Н | Х   | Х           | Х    | н    | L   | Н  | L   | L  | Х                 | $\uparrow$ | DiN  |

| Write Cycle, Continue Burst  | Next     | Н | Х   | Х           | Х    | Н    | L   | L  | Х   | Х  | Х                 | Ŷ          | Din  |

| Read Cycle, Suspend Burst    | Current  | Х | Х   | Х           | н    | Н    | Н   | Н  | Н   | Х  | L                 | Ŷ          | Dout |

| Read Cycle, Suspend Burst    | Current  | Х | Х   | Х           | Н    | Н    | Н   | Н  | Н   | Х  | Н                 | Ŷ          | HI-Z |

| Read Cycle, Suspend Burst    | Current  | Х | Х   | Х           | Н    | Н    | Н   | Н  | Х   | Н  | L                 | Ŷ          | Dout |

| Read Cycle, Suspend Burst    | Current  | Х | Х   | Х           | Н    | Н    | Н   | Н  | Х   | Н  | Н                 | Ŷ          | HI-Z |

| Read Cycle, Suspend Burst    | Current  | Н | Х   | Х           | Х    | Н    | Н   | Н  | Н   | Х  | L                 | Ŷ          | Dout |

| Read Cycle, Suspend Burst    | Current  | Н | Х   | Х           | Х    | Н    | Н   | Н  | Н   | Х  | Н                 | Ŷ          | HI-Z |

| Read Cycle, Suspend Burst    | Current  | Н | Х   | Х           | Х    | Н    | Н   | Н  | Х   | Н  | L                 | Ŷ          | Dout |

| Read Cycle, Suspend Burst    | Current  | Н | Х   | Х           | Х    | Н    | Н   | Н  | х   | Н  | Н                 | Ŷ          | HI-Z |

| Write Cycle, Suspend Burst   | Current  | Х | Х   | х           | н    | Н    | Н   | н  | L   | L  | Х                 | Ŷ          | Din  |

| Write Cycle, Suspend Burst   | Current  | х | х   | х           | Н    | н    | Н   | L  | х   | х  | х                 | Ŷ          | Din  |

| Write Cycle, Suspend Burst   | Current  | Н | Х   | х           | Х    | Н    | Н   | Н  | L   | L  | Х                 | Ŷ          | Din  |

| Write Cycle, Suspend Burst   | Current  | н | х   | х           | х    | Н    | Н   | L  | х   | х  | х                 | Ŷ          | Din  |

### NOTES:

1.  $L = V_{IL}$ ,  $H = V_{IH}$ , X = Don't Care. 2.  $\overline{OE}$  is an asynchronous input.

3. ZZ - low for the table.

5280 tbl 12

5280 tbl 14

5280 tbl 15

### Synchronous Write Function Truth Table <sup>(1, 2)</sup>

| Operation                   | GW | BWE | BW1 | BW2 | <b>BW</b> 3 | BW4 |

|-----------------------------|----|-----|-----|-----|-------------|-----|

| Read                        | н  | Н   | Х   | Х   | Х           | Х   |

| Read                        | Н  | L   | н   | Н   | Н           | Н   |

| Write all Bytes             | L  | Х   | х   | х   | Х           | Х   |

| Write all Bytes             | н  | L   | L   | L   | L           | L   |

| Write Byte 1 <sup>(3)</sup> | Н  | L   | L   | Н   | Н           | Н   |

| Write Byte 2 <sup>(3)</sup> | Н  | L   | н   | L   | Н           | Н   |

| Write Byte 3 <sup>(3)</sup> | Н  | L   | н   | Н   | L           | Н   |

| Write Byte 4 <sup>(3)</sup> | н  | L   | н   | Н   | Н           | L   |

NOTES:

1. L = VIL, H = VIH, X = Don't Care.

2.  $\overline{BW}_3$  and  $\overline{BW}_4$  are not applicable for the AS8C401825.

3. Multiple bytes may be selected during the same cycle.

### Asynchronous Truth Table<sup>(1)</sup>

| Operation <sup>(2)</sup> | ŌĒ | Z | I/O Status       | Power    |

|--------------------------|----|---|------------------|----------|

| Read                     | L  | L | Data Out         | Active   |

| Read                     | н  | L | High-Z           | Active   |

| Write                    | Х  | L | High-Z – Data In | Active   |

| Deselected               | Х  | L | High-Z           | Standby  |

| Sleep Mode               | Х  | Н | High-Z           | Sleep    |

| 10750                    | •  | • | •                | 5280 tbl |

NOTES:

1. L = VIL, H = VIH, X = Don't Care.

2. Synchronous function pins must be biased appropriately to satisfy operation requirements.

### Interleaved Burst Sequence Table ( **LBO**=VDD)

|                               | Sequence 1 |    | Sequence 2 |    | Sequence 3 |    | Sequence 4 |    |

|-------------------------------|------------|----|------------|----|------------|----|------------|----|

|                               | A1         | A0 | A1         | A0 | A1         | A0 | A1         | A0 |

| First Address                 | 0          | 0  | 0          | 1  | 1          | 0  | 1          | 1  |

| Second Address                | 0          | 1  | 0          | 0  | 1          | 1  | 1          | 0  |

| Third Address                 | 1          | 0  | 1          | 1  | 0          | 0  | 0          | 1  |

| Fourth Address <sup>(1)</sup> | 1          | 1  | 1          | 0  | 0          | 1  | 0          | 0  |

NOTE:

1. Upon completion of the Burst sequence the counter wraps around to its initial state.

### Linear Burst Sequence Table ( **LBO**=Vss)

|                               | Sequence 1 |    | Sequence 2 |    | Sequence 3 |    | Sequence 4 |    |

|-------------------------------|------------|----|------------|----|------------|----|------------|----|

|                               | A1         | A0 | A1         | A0 | A1         | A0 | A1         | A0 |

| First Address                 | 0          | 0  | 0          | 1  | 1          | 0  | 1          | 1  |

| Second Address                | 0          | 1  | 1          | 0  | 1          | 1  | 0          | 0  |

| Third Address                 | 1          | 0  | 1          | 1  | 0          | 0  | 0          | 1  |

| Fourth Address <sup>(1)</sup> | 1          | 1  | 0          | 0  | 0          | 1  | 1          | 0  |

NOTE:

1. Upon completion of the Burst sequence the counter wraps around to its initial state.

5280 tbl 16

### **AC Electrical Characteristics**

### (VDD = 3.3V ±5%, Commercial and Industrial Temperature Ranges)

|                     |                                     |      | ns <sup>(5)</sup> | 8ns  |      | 8.5ns |      |      |

|---------------------|-------------------------------------|------|-------------------|------|------|-------|------|------|

| Symbol              | Parameter                           | Min. | Max.              | Min. | Max. | Min.  | Max. | Unit |

| Clock Pa            | rameter                             | -    | -                 | -    | -    |       |      | •    |

| tcyc                | Clock Cycle Time                    | 8.5  |                   | 10   |      | 11.5  |      | ns   |

| tCH <sup>(1)</sup>  | Clock High Pulse Width              | 3    |                   | 4    | _    | 4.5   |      | ns   |

| tCL <sup>(1)</sup>  | Clock Low Pulse Width               | 3    |                   | 4    |      | 4.5   |      | ns   |

| Output Pa           | arameters                           |      | •                 | 1    |      |       | •    |      |

| tCD                 | Clock High to Valid Data            |      | 7.5               |      | 8    |       | 8.5  | ns   |

| tCDC                | Clock High to Data Change           | 2    |                   | 2    |      | 2     |      | ns   |

| talz <sup>(2)</sup> | Clock High to Output Active         | 0    |                   | 0    |      | 0     |      | ns   |

| tCHZ <sup>(2)</sup> | Clock High to Data High-Z           | 2    | 3.5               | 2    | 3.5  | 2     | 3.5  | ns   |

| tOE                 | Output Enable Access Time           |      | 3.5               |      | 3.5  |       | 3.5  | ns   |

| toLz <sup>(2)</sup> | Output Enable Low to Output Active  | 0    |                   | 0    |      | 0     |      | ns   |

| tohz <sup>(2)</sup> | Output Enable High to Output High-Z |      | 3.5               |      | 3.5  |       | 3.5  | ns   |

| Set Up Ti           | mes                                 |      |                   |      |      |       |      |      |

| tsa                 | Address Setup Time                  | 1.5  |                   | 2    |      | 2     |      | ns   |

| tss                 | Address Status Setup Time           | 1.5  |                   | 2    |      | 2     |      | ns   |

| tsD                 | Data In Setup Time                  | 1.5  |                   | 2    |      | 2     |      | ns   |

| tsw                 | Write Setup Time                    | 1.5  |                   | 2    | —    | 2     |      | ns   |

| tsav                | Address Advance Setup Time          | 1.5  | —                 | 2    | —    | 2     |      | ns   |

| tsc                 | Chip Enable/Select Setup Time       | 1.5  |                   | 2    | —    | 2     |      | ns   |

| Hold Tim            | es                                  |      | -                 |      |      |       |      | -    |

| tha                 | Address Hold Time                   | 0.5  |                   | 0.5  |      | 0.5   |      | ns   |

| tHS                 | Address Status Hold Time            | 0.5  |                   | 0.5  | —    | 0.5   |      | ns   |

| thd                 | Data In Hold Time                   | 0.5  |                   | 0.5  | —    | 0.5   |      | ns   |

| tHW                 | Write Hold Time                     | 0.5  |                   | 0.5  | —    | 0.5   |      | ns   |

| thav                | Address Advance Hold Time           | 0.5  |                   | 0.5  | —    | 0.5   |      | ns   |

| tHC                 | Chip Enable/Select Hold Time        | 0.5  |                   | 0.5  | —    | 0.5   |      | ns   |

| Sleep Mo            | de and Configuration Parameters     |      |                   |      |      |       |      |      |

| tzzpw               | ZZ Pulse Width                      | 100  |                   | 100  | —    | 100   |      | ns   |

| tzzr(3)             | ZZ Recovery Time                    | 100  | —                 | 100  | —    | 100   |      | ns   |

| tOFG <sup>(4)</sup> | Configuration Set-up Time           | 34   |                   | 40   |      | 50    |      | ns   |

NOTES:

1. Measured as HIGH above VIH and LOW below VIL.

2. Transition is measured ±200mV from steady-state.

3. Device must be deselected when powered-up from sleep mode.

4. tors is the minimum time required to configure the device based on the LBO input. LBO is a static input and must not change during normal operation.

5. Commercial temperature range only.

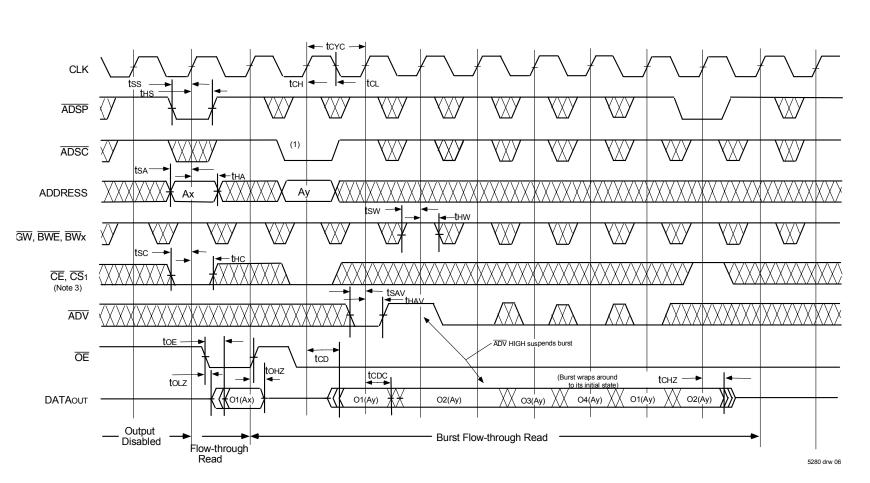

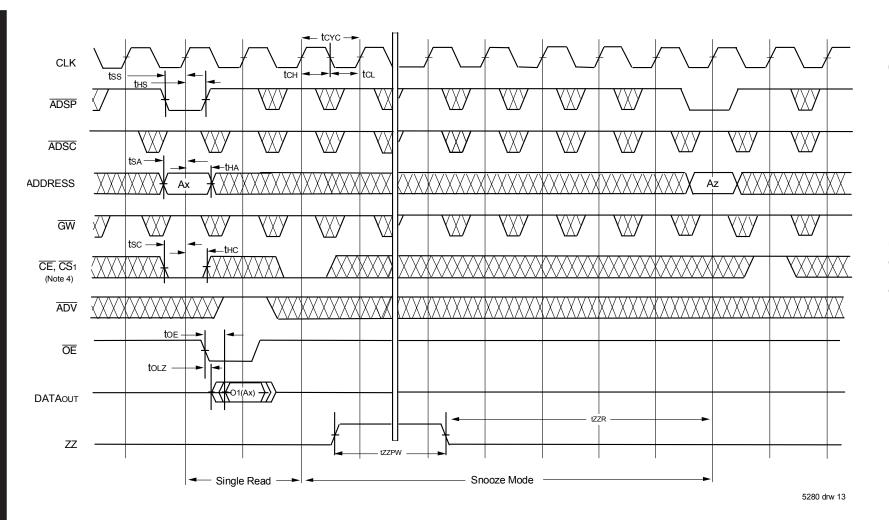

## Timing Waveform of Flow-Through Read Cycle <sup>(1,2)</sup>

### NOTES:

1. O1 (Ax) represents the first output from the external address Ax. O1 (Ay) represents the first output from the external address Ay; O2 (Ay) represents the next output data in the burst sequence of the base address Ay, etc. where A0 and A1 are advancing for the four word burst in the sequence defined by the state of the LBO input.

2. ZZ input is LOW and  $\overline{LBO}$  is Don't Care for this cycle.

3. CS0 timing transitions are identical but inverted to the CE and CS1 signals. For example, when CE and CS1 are LOW on this waveform, CS0 is HIGH.

6.42

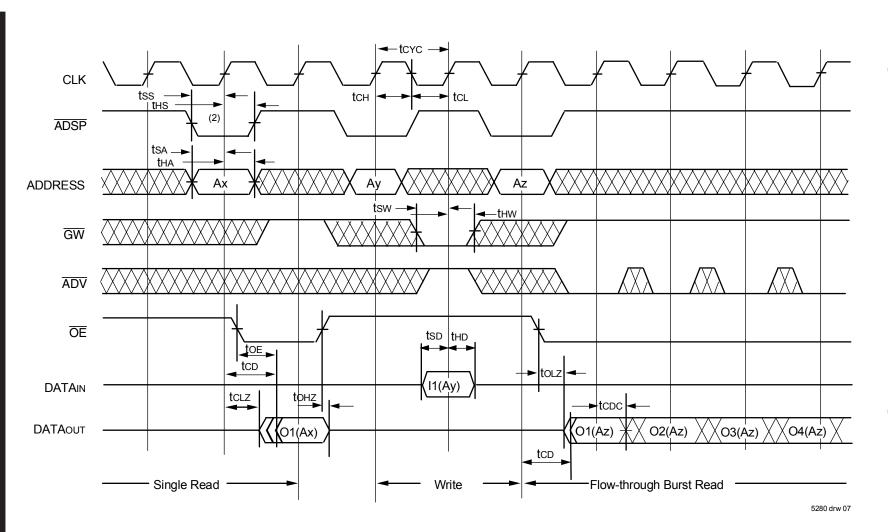

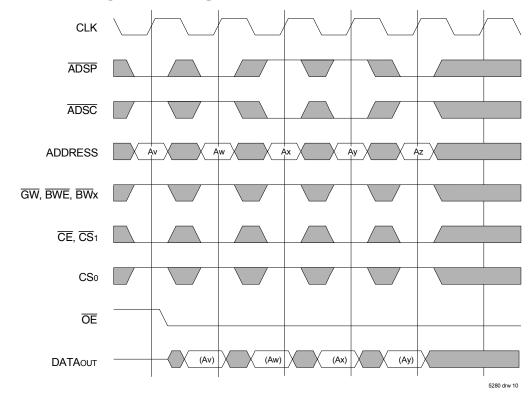

### NOTES:

6.42

- 1. Device is selected through entire cycle;  $\overline{CE}$  and  $\overline{CS}_1$  are LOW, CS0 is HIGH.

- 2. ZZ input is LOW and  $\overline{LBO}$  is Don't Care for this cycle.

3. O1 (Ax) represents the first output from the external address Ax. I1 (Ay) represents the first input from the external address Ay; O1 (Az) represents the first output from the external address Az; O2 (Az) represents the next output data in the burst sequence of the base address Az, etc. where A0 and A1 are advancing for the four word burst in the sequence defined by the state of the LBO input.

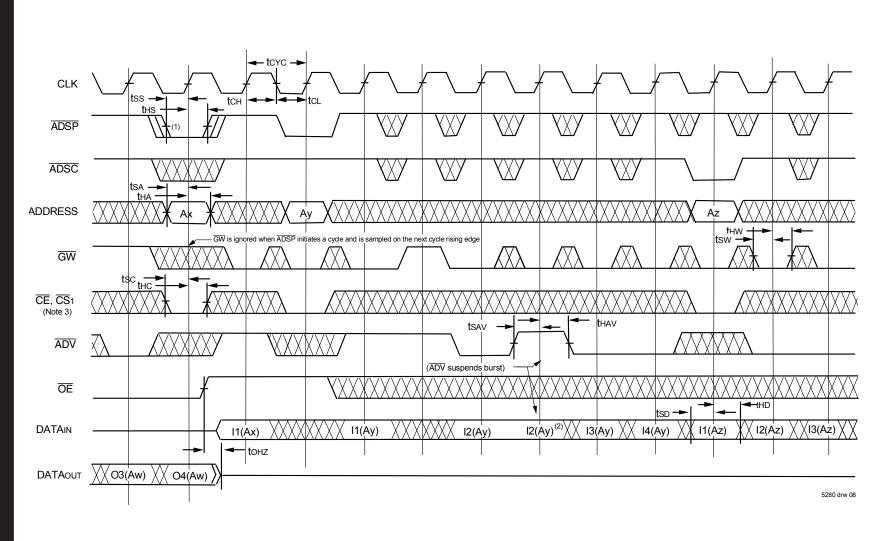

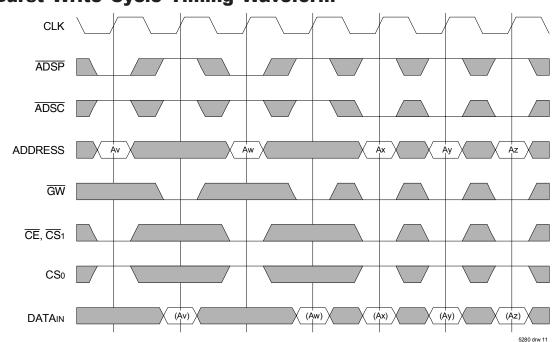

- 1. ZZ input is LOW, BWE is HIGH and LBO is Don't Care for this cycle.

- 2. O4 (Aw) represents the final output data in the burst sequence of the base address Aw. I1 (Ax) represents the first input from the external address Ay; I2 (Ay) represents the next input data in the burst sequence of the base address Ay, etc. where A0 and A1 are advancing for the four word burst in the sequence defined by the state of the LBO input. In the case of input I2 (Ay) this data is valid for two cycles because ADV is high and has suspended the burst.

- 3. CS0 timing transitions are identical but inverted to the CE and CS1 signals. For example, when CE and CS1 are LOW on this waveform, CS0 is HIGH.

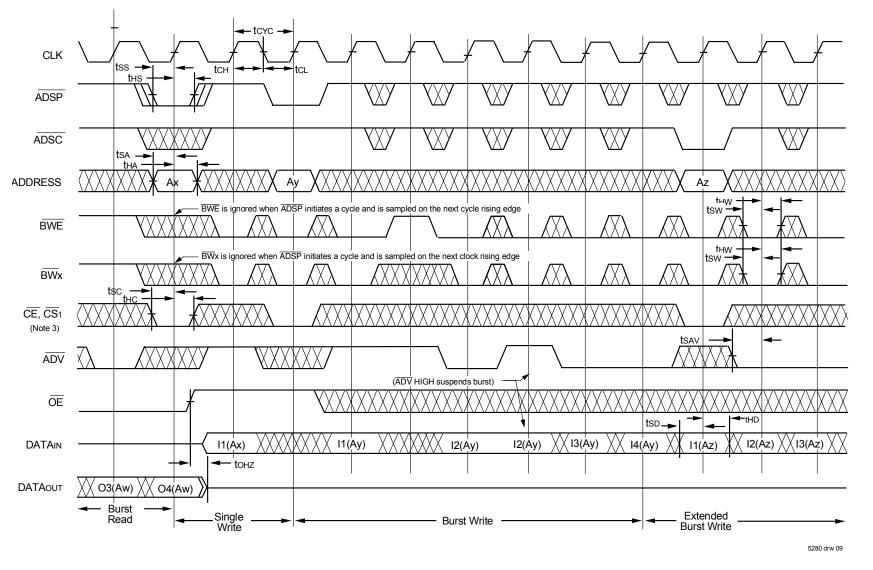

### Timing Waveform of Write Cycle No. N Byte Controlled (1,2,3)

### NOTES:

- 1. ZZ input is LOW,  $\overline{GW}$  is HIGH and  $\overline{LBO}$  is Don't Care for this cycle.

- 2. O4 (Aw) represents the final output data in the burst sequence of the base address Aw. 11 (Ax) represents the first input from the external address Ax. 11 (Ay) represents the first input from the external address Ay; I2 (Ay) represents the next input data in the burst sequence of the base address Ay, etc. where A0 and A1 are advancing for the four word burst in the sequence defined by the state of the LBO input. In the case of input I2 (Ay) this data is valid for two cycles because ADV is high and has suspended the burst.

- 3. CS0 timing transitions are identical but inverted to the CE and CS1 signals. For example, when CE and CS1 are LOW on this waveform, CS0 is HIGH.

6.42

# Timing Waveform of Sleep (ZZ) and Power-Down Modes <sup>(1,2,3)</sup>

NOTES:

6.4.2

1. Device must power up in deselected Mode.

2.  $\overline{\text{LBO}}$  is Don't Care for this cycle.

It is not necessary to retain the state of the input registers throughout the Power-down cycle.

CS0 timing transitions are identical but inverted to the CE and CS1 signaals. For example, when CE and CS1 are LOW on this waveform, CS0 is HIGH.

### Non-Burst Read Cycle Timing Waveform

### NOTES:

1. ZZ input is LOW, ADV is HIGH and LBO is Don't Care for this cycle.

2. (Ax) represents the data for address Ax, etc.

3. For read cycles, ADSP and ADSC function identically and are therefore interchangable.

### **Non-Burst Write Cycle Timing Waveform**

- 1. ZZ input is LOW,  $\overline{\text{ADV}}$  and  $\overline{\text{OE}}$  are HIGH, and  $\overline{\text{LBO}}$  is Don't Care for this cycle.

- 2. (Ax) represents the data for address Ax, etc.

- 3. Although only  $\overline{GW}$  writes are shown, the functionality of  $\overline{BWE}$  and  $\overline{BWx}$  together is the same as  $\overline{GW}$ .

- 4. For write cycles, ADSP and ADSC have different limitations.

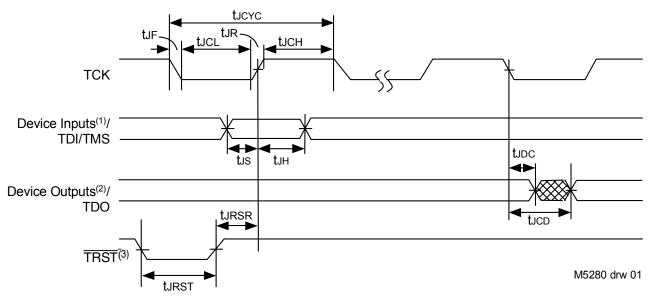

### JTAG Interface Specification (SA Version only)

### NOTES:

1. Device inputs = All device inputs except TDI, TMS and  $\overline{\text{TRST}}$ .

2. Device outputs = All device outputs except TDO.

3. During power up, TRST could be driven low or not be used since the JTAG circuit resets automatically. TRST is an optional JTAG reset.

### JTAG AC Electrical Characteristics<sup>(1,2,3,4)</sup>

| Symbol        | Parameter               | Min. | Max.             | Units        |

|---------------|-------------------------|------|------------------|--------------|

| tucyc         | JTAG Clock Input Period | 100  | I                | ns           |

| ţлсн          | JTAG Clock HIGH         | 40   | 1                | ns           |

| tJCL          | JTAG Clock Low          | 40   |                  | ns           |

| tιR           | JTAG Clock Rise Time    |      | 5 <sup>(1)</sup> | ns           |

| IJF           | JTAG Clock Fall Time    | _    | 5 <sup>(1)</sup> | ns           |

| <b>t</b> JRST | JTAG Reset              | 50   |                  | ns           |

| tu rsr        | JTAG Reset Recovery     | 50   |                  | ns           |

| tJCD          | JTAG Data Output        |      | 20               | ns           |

| tJDC          | JTAG Data Output Hold   | 0    |                  | ns           |

| tus           | JTAG Setup              | 25   |                  | ns           |

| ţлн           | JTAG Hold               | 25   |                  | ns           |

|               |                         |      |                  | 15280 tbl 01 |

### **Scan Register Sizes**

| Register Name              | Bit Size     |

|----------------------------|--------------|

| Instruction (IR)           | 4            |

| Bypass (BYR)               | 1            |

| JTAG Identification (JIDR) | 32           |

| Boundary Scan (BSR)        | Note (1)     |

|                            | I5280 tbl 03 |

NOTE:

1. The Boundary Scan Descriptive Language (BSDL) file for this device is available

### NOTES:

1. Guaranteed by design.

2. AC Test Load (Fig. 1) on external output signals.

3. Refer to AC Test Conditions stated earlier in this document.

4. JTAG operations occur at one speed (10MHz). The base device may run at any speed specified in this datasheet.

### JTAG Identification Register Definitions (SA Version only)

| Instruction Field                 | Value        | Description                                    |

|-----------------------------------|--------------|------------------------------------------------|

| Revision Number (31:28)           | 0x2          | Reserved for version number.                   |

| Device ID (27:12)                 | 0x22C, 0x22E | Defines AS8C403625/1825                        |

| JEDEC ID (11:1)                   | 0x33         | Allows unique identification of device vendor. |

| ID Register Indicator Bit (Bit 0) | 1            | Indicates the presence of an ID register.      |

15280 tbl 02

### **Available JTAG Instructions**

| Instruction    | Description                                                                                                                                                                                                                                                                                                          | OPCODE |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| EXTEST         | Forces contents of the boundary scan cells onto the device outputs <sup>(1)</sup> . Places the boundary scan register (BSR) between TDI and TDO.                                                                                                                                                                     | 0000   |

| SAMPLE/PRELOAD | Places the boundary scan register (BSR) between TDI and TDO.<br>SAMPLE allows data from device inputs <sup>(2)</sup> and outputs <sup>(1)</sup> to be captured<br>in the boundary scan cells and shifted serially through TDO. PRELOAD<br>allows data to be input serially into the boundary scan cells via the TDI. | 0001   |

| DEVICE_ID      | Loads the JTAG ID register (JIDR) with the vendor ID code and places the register between TDI and TDO.                                                                                                                                                                                                               | 0010   |

| HIGHZ          | Places the bypass register (BYR) between TDI and TDO. Forces all device output drivers to a High-Z state.                                                                                                                                                                                                            | 0011   |

| RESERVED       |                                                                                                                                                                                                                                                                                                                      | 0100   |

| RESERVED       | Several combinations are reserved. Do not use codes other than those                                                                                                                                                                                                                                                 | 0101   |

| RESERVED       | identified for EXTEST, SAMPLE/PRELOAD, DEVICE_ID, HIGHZ, CLAMP,<br>VALIDATE and BYPASS instructions.                                                                                                                                                                                                                 | 0110   |

| RESERVED       |                                                                                                                                                                                                                                                                                                                      | 0111   |

| CLAMP          | Uses BYR. Forces contents of the boundary scan cells onto the device outputs. Places the bypass register (BYR) between TDI and TDO.                                                                                                                                                                                  | 1000   |

| RESERVED       |                                                                                                                                                                                                                                                                                                                      | 1001   |

| RESERVED       | Same as above.                                                                                                                                                                                                                                                                                                       | 1010   |

| RESERVED       | Same as above.                                                                                                                                                                                                                                                                                                       | 1011   |

| RESERVED       |                                                                                                                                                                                                                                                                                                                      | 1100   |

| VALIDATE       | Automatically loaded into the instruction register whenever the TAP controller passes through the CAPTURE-IR state. The lower two bits '01' are mand ated by the IEEE std. 1149.1 specification.                                                                                                                     | 1101   |

| RESERVED       | Same as above.                                                                                                                                                                                                                                                                                                       | 1110   |

| BYPASS         | The BYPASS instruction is used to truncate the boundary scan register as a single bit in length.                                                                                                                                                                                                                     | 1111   |

15280 tbl 04

### NOTES:

1. Device outputs = All device outputs except TDO.

2. Device inputs = All device inputs except TDI, TMS, and  $\overline{\text{TRST}}$ .

### **ORDERING INFORMATION**

| Alliance         | Organization | VCC<br>Range | Package      | Operating Temp    | Speed<br>ns |

|------------------|--------------|--------------|--------------|-------------------|-------------|

| AS8C403625-QC75N | 128K x 36    | 3.1 - 3.4V   | 100 pin TQFP | Comercial 0 - 70C | 7.5         |

| AS8C401825-QC75N | 256K x 18    | 3.1 - 3.4V   | 100 pin TQFP | Comercial 0 - 70C | 7.5         |

### PART NUMBERING SYSTEM

| AS8C                 | Device  | Conf.               | Mode                                         | Package          | Operating Temp | Speed  | N           |

|----------------------|---------|---------------------|----------------------------------------------|------------------|----------------|--------|-------------|

| Sync.<br>SRAM prefix | 40 = 4M | 18= x18<br>36 = x36 | 01= ZBT<br>00 = Pipelined<br>25 = Flow- Thru | Q = 100 Pin TQFP | 0 ~ 70C        | 7.5 ns | N= Leadfree |

Alliance Memory, Inc. 551 Taylor way, suite#1, San Carlos, CA 94070 Tel: 650-610-6800 Fax: 650-620-9211

www.alliancememory.com

Copyright © Alliance Memory All Rights Reserved Part Number: AS8C403625/401825 Document Version: v. 1.0

© Copyright 2003 Alliance Memory, Inc. All rights reserved. Our three-point logo, our name and Intelliwatt are trademarks or registered trademarks of Alliance. All other brand and product names may be the trademarks of their respective companies. Alliance reserves the right to make changes to this document and its products at any time without notice. Alliance assumes no responsibility for any errors that may appear in this document. The data contained herein represents Alliance's best data and/or estimates at the time of issuance. Alliance reserves the right to change or correct this data at any time, without notice. If the product described herein is under development, significant changes to these specifications are possible. The information in this product data sheet is intended to be general descriptive information for potential customers and users, and is not intended to operate as, or provide, any guarantee or warrantee to any user or customer. Alliance does not assume any responsibility or liability arising out of the application or use of any product described herein, and disclaims any express or implied warranties related to the sale and/or use of Alliance products including liability or warranties related to fitness for a particular purpose, merchantability, or infringement of any intellectual property rights, except as express agreed to in Alliance's Terms and Conditions of Sale (which are available from Alliance does not convey a license under any patent rights, copyrights; mask works rights, trademarks, or any other intellectual property rights of Alliance or third parties. Alliance does not authorize its products for use as critical components in life-supporting systems where a malfunction or failure may reasonably be expected to result in significant injury to the user, and the inclusion of Alliance products in such life-supporting systems implies that the manufacturer assumes all risk of such use and agrees to indemnify Alliance against all claims arising from such use.