# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

Low-Noise, High-Precision, Programmable Linear Hall-Effect Sensor IC with High-Bandwidth (120 kHz) Analog Output and Integrated Fault Comparator with Self-Test Diagnostic Mode

#### FEATURES AND BENEFITS

- Proprietary segmented linear temperature compensation (TC) technology provides a typical accuracy of 1% over the full operating temperature range

- Self-Test diagnostic mode can be used to achieve a high level of functional safety within a system

- 120 kHz nominal bandwidth achieved via proprietary packaging and chopper stabilization techniques

- Over Field Fault signal with 6-bit programmable trigger levels, 2-bit programmable hysteresis, and latching or non-latching behavior

- Over Field Fault response time < 4.5 μs (typ)

- Extremely low noise and high resolution achieved via proprietary Hall element and low-noise amplifier circuits

- Customer-programmable, high-resolution offset and sensitivity trim

- Available in a 1-mm-thick SIP through-hole package

Continued on the next page ....

#### PACKAGE:

#### DESCRIPTION

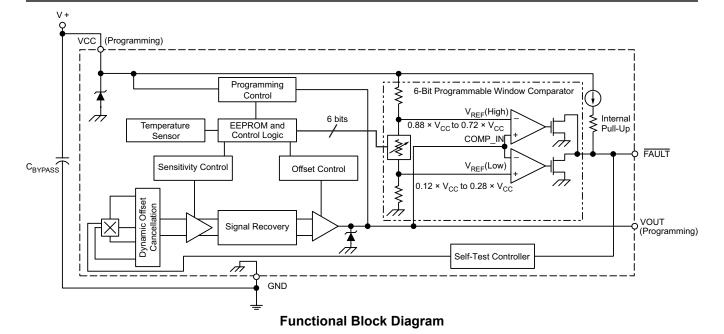

The A1365 linear output Hall-effect sensor IC is specifically designed to provide a highly accurate output with improved resolution at high bandwidth for use in current-sensing applications. This device employs a segmented, linearly interpolated temperature compensation technology, which provides greater accuracy in sensitivity and offset voltage trimming and hence virtually zero temperature drift. This improvement greatly reduces the total error of the device across the operating temperature range.

A user-activated Self-Test diagnostic mode verifies the A1365 Sensitivity and Over Field Fault functionality and can be used to achieve a high level of functional safety in application.

The highly programmable Over Field Fault signal (FAULT pin) can be used to detect a high magnetic field condition. Broken ground wire detection, undervoltage lockout for  $V_{CC}$  below specification, and user-selectable output voltage clamps are also included, which are important for high reliability in automotive applications. The sensor accuracy and diagnostic capability make it ideally suited for automotive sockets such as HEV inverter and DC-to-DC converter applications.

The A1365 Hall-effect sensor IC is extremely sensitive, fast, and temperature-stable. The accuracy and flexibility of this device is enhanced by user programmability, performed via the  $V_{CC}$  supply and the output pins, which allows the device to be optimized in the application.

Continued on the next page ....

Low-Noise, High-Precision, Programmable Linear Hall-Effect Sensor IC with High-Bandwidth (120 kHz) Analog Output and Integrated Fault Comparator with Self-Test Diagnostic Mode

#### FEATURES AND BENEFITS (CONTINUED)

- Factory-programmed sensitivity and quiescent output voltage TC with extremely stable temperature performance

- Selectable sensitivity range between 0.6 and 14 mV/G through use of coarse sensitivity program bits

- Ratiometric sensitivity, quiescent voltage output, and clamps enable simple interface with application A-to-D converter (ADC)

- Output voltage clamps provide short-circuit diagnostic capabilities

- Open-circuit detection on ground pin (broken wire)

- Undervoltage lockout for V<sub>CC</sub> below specification

- Wide ambient temperature range: -40°C to 150°C

#### **DESCRIPTION (CONTINUED)**

This ratiometric Hall-effect sensor IC provides a voltage output that is proportional to the applied magnetic field. The quiescent output voltage is user-adjustable around 50% (bidirectional) of the supply voltage,  $V_{CC}$ . The device sensitivity is adjustable within the range of 0.6 to 14 mV/G.

The A1365 incorporates a highly sensitive Hall element with a BiCMOS interface integrated circuit that employs temperaturecompensation circuitry to reduce the intrinsic sensitivity and offset drift of the Hall element. The IC also includes a small-signal high-gain amplifier, a clamped low-impedance output stage, and a proprietary high-bandwidth dynamic offset cancellation technique.

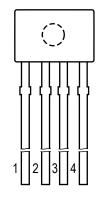

Device specifications apply across an extended ambient temperature range:  $-40^{\circ}$ C to  $150^{\circ}$ C. The A1365 sensor IC is provided in an extremely thin case (1 mm thick), 4-pin SIP (single inline package, suffix KT) that is lead (Pb) free, with 100% matte-tin leadframe plating. The thin package allows for better magnetic coupling because the smaller the air gap in the core is, the higher the coupling from current to magnetic field will be.

#### **Table of Contents**

| Features and Benefits                                  | 1    |

|--------------------------------------------------------|------|

| Description                                            | 1    |

| Package                                                | 1    |

| Functional Block Diagram                               |      |

| Selection Guide                                        | 2    |

| Absolute Maximum Ratings                               | 3    |

| Thermal Characteristics                                |      |

| Pinout Diagrams and Terminal List                      | 4    |

| Operating Characteristics                              | 5    |

| Characteristic Performance Data                        | 9    |

| Characteristic Definitions                             | . 13 |

| Functional Description                                 | . 19 |

| Programming Sensitivity and Quiescent Voltage Output   | . 19 |

| Coarse Sensitivity                                     | . 19 |

| Memory Locking Mechanisms                              | . 19 |

| Power-On Reset (POR) and Undervoltage Lockout (UVLO).  | . 20 |

| Detecting Broken Ground Wire                           | . 21 |

| Self-Test Diagnostic Operation after Power-Up          | . 22 |

| Self-Test Start Mode                                   | . 22 |

| Self-Test Sens Mode                                    | . 22 |

| Self-Test Fault Mode                                   | . 23 |

| Self-Test Operating Conditions                         | . 23 |

| Over Magnetic Field Fault                              | . 26 |

| Programming Serial Interface                           | . 28 |

| Transaction Types                                      | . 28 |

| Writing the Access Code                                | . 28 |

| Writing to Volatile Memory                             | . 28 |

| Writing to EEPROM                                      | . 29 |

| Reading from EEPROM or Volatile Memory                 | . 29 |

| Error Checking                                         | . 29 |

| Serial Interface Reference                             | . 30 |

| Serial Interface Message Structure                     | . 31 |

| V <sub>CC</sub> Levels During Manchester Communication | . 31 |

| Shadow Mode                                            | . 32 |

| EEPROM Margining                                       | . 33 |

| EEPROM Cell Organization                               |      |

| EEPROM Error Checking and Correction (ECC)             |      |

| Detecting ECC Error                                    | . 34 |

| Package Outline Drawing                                | . 35 |

|                                                        |      |

#### SELECTION GUIDE

| Part Number     | Package   | Packing <sup>[1]</sup>       | Sensitivity Range <sup>[2]</sup><br>(mV/G) |

|-----------------|-----------|------------------------------|--------------------------------------------|

| A1365LKTTN-1-T  | 4-pin SIP | 4000 pieces per 13-inch reel | 0.6 to 1.3                                 |

| A1365LKTTN-2-T  | 4-pin SIP | 4000 pieces per 13-inch reel | 1.3 to 2.9                                 |

| A1365LKTTN-5-T  | 4-pin SIP | 4000 pieces per 13-inch reel | 2.9 to 6.4                                 |

| A1365LKTTN-10-T | 4-pin SIP | 4000 pieces per 13-inch reel | 6.4 to 14                                  |

<sup>[1]</sup> Contact Allegro for additional packing options.

[2] Allegro recommends against changing Coarse Sensitivity settings when programming devices that will be used in production. Each A1365 has been factory temperature compensated at a specific sensitivity range, and changing the coarse bits setting could cause sensitivity drift through temperature range (ΔSens<sub>TC</sub>) to exceed specified limits.

#### **SPECIFICATIONS**

#### **ABSOLUTE MAXIMUM RATINGS**

| Characteristic                        | Symbol                   | Notes               | Rating     | Unit   |

|---------------------------------------|--------------------------|---------------------|------------|--------|

| Forward Supply Voltage                | V <sub>CC</sub>          |                     | 6          | V      |

| Reverse Supply Voltage                | V <sub>RCC</sub>         |                     | -0.1       | V      |

| Forward Output Voltage                | V <sub>OUT</sub>         |                     | 25         | V      |

| Reverse Output Voltage                | V <sub>ROUT</sub>        |                     | -0.1       | V      |

| Forward Fault Voltage                 | VFAULT                   |                     | 6          | V      |

| Reverse Fault Voltage                 | VRFAULT                  |                     | -0.1       | V      |

| Output Source Current                 | I <sub>OUT(source)</sub> | VOUT to GND         | 2.8        | mA     |

| Output Sink Current                   | I <sub>OUT(sink)</sub>   | VCC to VOUT         | 10         | mA     |

| Maximum Number of EEPROM Write Cycles | EEPROM <sub>w(max)</sub> |                     | 100        | cycles |

| Operating Ambient Temperature         | T <sub>A</sub>           | L temperature range | -40 to 150 | °C     |

| Storage Temperature                   | T <sub>stg</sub>         |                     | –65 to 165 | °C     |

| Maximum Junction Temperature          | T <sub>J</sub> (max)     |                     | 165        | °C     |

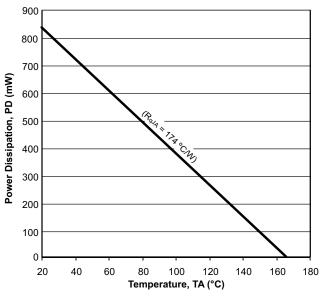

#### THERMAL CHARACTERISTICS: May require derating at maximum conditions; see application information

| Characteristic             | Symbol           | Test Conditions*                                          | Value | Unit |

|----------------------------|------------------|-----------------------------------------------------------|-------|------|

| Package Thermal Resistance | R <sub>θJA</sub> | On 1-layer PCB with exposed copper limited to solder pads | 174   | °C/W |

\*Additional thermal information available on the Allegro website

#### Power Dissipation versus Ambient Temperature

#### PINOUT DIAGRAM AND TERMINAL LIST TABLE

KT Package Pinout Diagram (Ejector pin mark on opposite side)

#### **Terminal List Table**

| Number | Name  | Function                                                                                 |

|--------|-------|------------------------------------------------------------------------------------------|

| 1      | VCC   | Input Power Supply, use bypass capacitor to connect to ground; also used for programming |

| 2      | VOUT  | Output Signal, also used for programming                                                 |

| 3      | FAULT | Over Field Fault Detection Flag                                                          |

| 4      | GND   | Ground                                                                                   |

4

## OPERATING CHARACTERISTICS: Valid through the full operating temperature range T<sub>A</sub>, C<sub>BYPASS</sub> = 0.1 μF, and V<sub>CC</sub> = 5 V, unless otherwise specified

| Characteristic                                           | Symbol                 | Test Conditions                                                                                                                           | Min. | Тур.            | Max. | Unit <sup>[1]</sup> |

|----------------------------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------|------|---------------------|

| ELECTRICAL CHARACTERISTICS                               |                        | ·                                                                                                                                         |      |                 |      |                     |

| Supply Voltage                                           | V <sub>CC</sub>        |                                                                                                                                           | 4.5  | 5               | 5.5  | V                   |

| Supply Current                                           | I <sub>cc</sub>        | No load on VOUT, $\ensuremath{\overline{FAULT}}$ pin in high-impedance state, connected through a 10 k $\Omega$ resistor to VCC           | -    | 10              | 15   | mA                  |

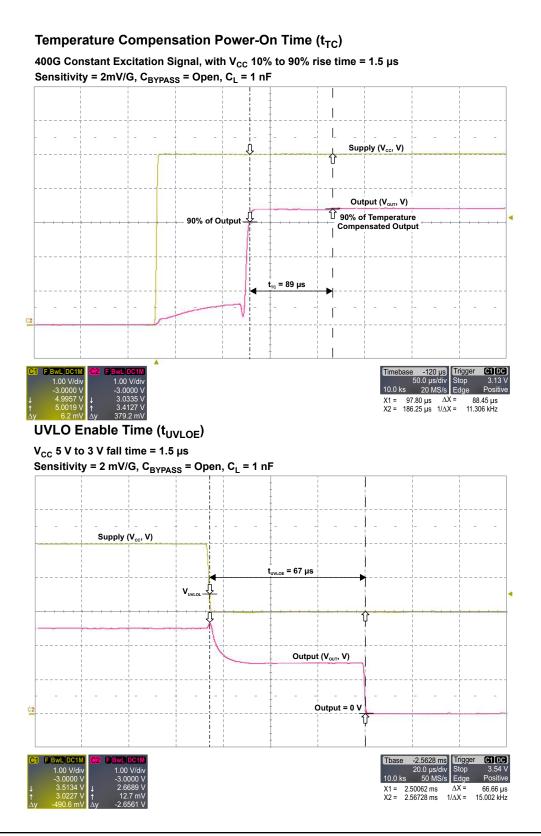

| Power-On Time <sup>[2]</sup>                             | t <sub>PO</sub>        | $T_A = 25^{\circ}C, C_{BYPASS} = open, C_L = 1 nF$                                                                                        | -    | 100             | -    | μs                  |

| Temperature Compensation<br>Power-On Time <sup>[2]</sup> | t <sub>TC</sub>        | $T_A = 25^{\circ}C, C_{BYPASS} = open, C_L = 1 nF$                                                                                        | -    | 90              | -    | μs                  |

| Undervoltage Lockout (UVLO)                              | V <sub>UVLOH</sub>     | $V_{CC}$ rising and device function enabled                                                                                               | _    | 4               | 4.3  | V                   |

| Threshold <sup>[2]</sup>                                 | V <sub>UVLOL</sub>     | $V_{CC}$ falling and device function disabled                                                                                             | 3.05 | 3.2             | -    | V                   |

| UVLO Enable/Disable Delay Time <sup>[2]</sup>            | t <sub>UVLOE</sub>     | $T_{A} = 25^{\circ}C, C_{BYPASS} = open, C_{L} = 1 \text{ nF}, V_{CC} \text{ fall time } (5 \text{ V to } 3 \text{ V}) = 1.5 \mu\text{s}$ | -    | 67              | _    | μs                  |

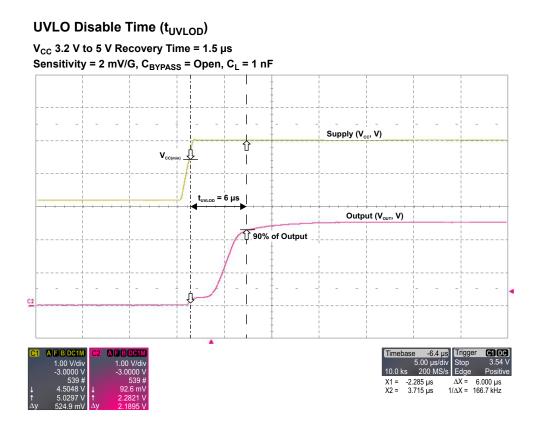

|                                                          | t <sub>UVLOD</sub>     | $T_A$ = 25°C, $C_{BYPASS}$ = open, $C_L$ = 1 nF, $V_{CC}$ recover time (3 V to 5 V) = 1.5 $\mu s$                                         | _    | 6               | _    | μs                  |

| Power-On Reset Voltage [2]                               | V <sub>PORH</sub>      | $T_A = 25^{\circ}C, V_{CC}$ rising                                                                                                        | _    | 2.9             |      | V                   |

| Tower-On Reset Voltage                                   | V <sub>PORL</sub>      | $T_A = 25^{\circ}C, V_{CC}$ falling                                                                                                       | _    | 2.5             | _    | V                   |

| Power-On Reset Release Time [2]                          | t <sub>PORR</sub>      | $T_A = 25^{\circ}C, V_{CC}$ rising                                                                                                        | _    | 85              | _    | μs                  |

| Supply Zener Clamp Voltage                               | Vz                     | T <sub>A</sub> = 25°C, I <sub>CC</sub> = 30 mA                                                                                            | 6.5  | 7.5             | _    | V                   |

| Internal Bandwidth                                       | BWi                    | Small signal –3 dB, $C_L$ = 1 nF, $T_A$ = 25°C                                                                                            | -    | 120             | -    | kHz                 |

| Chopping Frequency <sup>[3]</sup>                        | f <sub>C</sub>         | T <sub>A</sub> = 25°C                                                                                                                     | -    | 500             | -    | kHz                 |

| V <sub>OUT</sub> CHARACTERISTICS                         |                        |                                                                                                                                           |      |                 |      |                     |

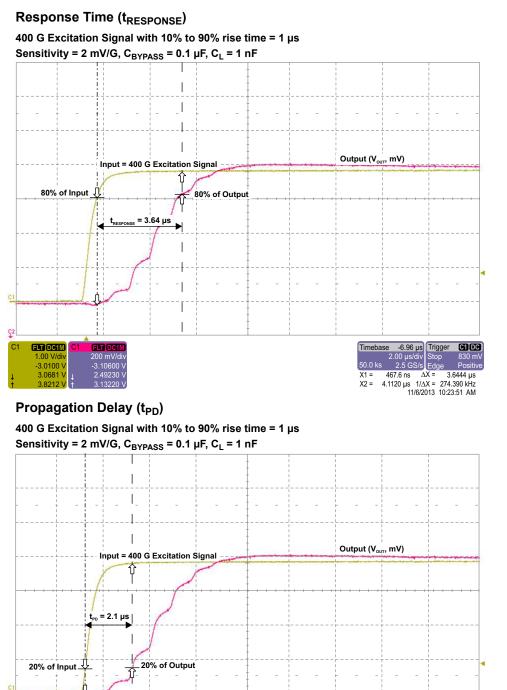

| Propagation Delay Time <sup>[2]</sup>                    | t <sub>pd</sub>        | $T_A = 25^{\circ}C$ , step magnetic field of 400 G,<br>$C_L = 1 \text{ nF}$ , Sens = 2 mV/G                                               | -    | 2.2             | _    | μs                  |

| Rise Time <sup>[2]</sup>                                 | t <sub>r</sub>         | $T_A = 25^{\circ}C$ , step magnetic field of 400 G,<br>$C_L = 1 \text{ nF}$ , Sens = 2 mV/G                                               | _    | 3.6             | _    | μs                  |

| Response Time <sup>[2]</sup>                             | t <sub>RESPONSE</sub>  | $T_A = 25^{\circ}C$ , step magnetic field of 400 G,<br>$C_L = 1 \text{ nF}$ , Sens = 2 mV/G                                               | -    | 3.7             | _    | μs                  |

| Delay to Clamp <sup>[2][4]</sup>                         | t <sub>CLP</sub>       | $T_A = 25^{\circ}C$ , step magnetic field from 160 to 240 G, $C_L = 1$ nF, Sens = 10 mV/G                                                 | -    | 10              | _    | μs                  |

|                                                          | V <sub>CLP(HIGH)</sub> | $T_A = 25^{\circ}C, R_{L(PULLDWN)} = 10 \text{ k}\Omega \text{ to GND}$                                                                   | 4.55 | -               | 4.85 | V                   |

| Output Voltage Clamp <sup>[5]</sup>                      | V <sub>CLP(LOW)</sub>  | $T_A = 25^{\circ}C, R_{L(PULLUP)} = 10 \text{ k}\Omega \text{ to VCC}$                                                                    | 0.15 | -               | 0.45 | V                   |

| Output Caturation Maltana [2]                            | V <sub>SAT(HIGH)</sub> | $T_A = 25^{\circ}C, R_{L(PULLDWN)} = 10 \text{ k}\Omega \text{ to GND}$                                                                   | 4.8  | -               | _    | V                   |

| Output Saturation Voltage [2]                            | V <sub>SAT(LOW)</sub>  | $T_A = 25^{\circ}C, R_{L(PULLDWN)} = 10 \text{ k}\Omega \text{ to VCC}$                                                                   | _    | -               | 300  | mV                  |

| Prokon Wire Voltage <sup>[2]</sup>                       | V <sub>BRK(HIGH)</sub> | $T_A = 25^{\circ}C, R_{L(PULLUP)} = 10 \text{ k}\Omega \text{ to VCC}$                                                                    | _    | V <sub>cc</sub> | _    | V                   |

| Broken Wire Voltage <sup>[2]</sup>                       | V <sub>BRK(LOW)</sub>  | $T_A = 25^{\circ}C, R_{L(PULLDWN)} = 10 \text{ k}\Omega \text{ to GND}$                                                                   | _    | 200             | _    | mV                  |

|                                                          |                        | $T_{A} = 25^{\circ}C, CL = 1 nF$                                                                                                          | _    | 1.1             | _    | mG/√(Hz)            |

| Noise <sup>[6]</sup>                                     | V <sub>N</sub>         | $T_A = 25^{\circ}C$ , CL = 1 nF, Sens = 2 mV/G,<br>bandwidth = BW <sub>i</sub>                                                            | -    | 6.3             | -    | mV <sub>p-p</sub>   |

|                                                          |                        | $T_A = 25^{\circ}C$ , CL = 1 nF, Sens = 2 mV/G,<br>bandwidth = BW <sub>i</sub>                                                            | -    | 1               | -    | mV <sub>RMS</sub>   |

Continued on the next page ...

## OPERATING CHARACTERISTICS (continued): Valid through the full operating temperature range T<sub>A</sub>, C<sub>BYPASS</sub> = 0.1 μF, and V<sub>CC</sub> = 5 V, unless otherwise specified

| Characteristic                                           | Symbol                  | Test Conditions                                                                                                                  | Min.                   | Тур. | Max.                   | Unit <sup>[1]</sup> |

|----------------------------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------|------|------------------------|---------------------|

| V <sub>OUT</sub> CHARACTERISTICS (continue               | ed)                     |                                                                                                                                  |                        |      |                        |                     |

| DC Output Resistance                                     | R <sub>OUT</sub>        | T <sub>A</sub> = 25°C                                                                                                            | _                      | < 10 | _                      | Ω                   |

|                                                          | R <sub>L(PULLUP)</sub>  | VOUT to VCC                                                                                                                      | 4.7                    | _    | _                      | kΩ                  |

| Output Load Resistance                                   | R <sub>L(PULLDWN)</sub> | VOUT to GND                                                                                                                      | 4.7                    | _    | _                      | kΩ                  |

| Output Load Capacitance [7]                              | CL                      | VOUT to GND                                                                                                                      | _                      | 1    | 10                     | nF                  |

| Output Slew Rate [8]                                     | SR                      | Sens = 2 mV/G, $C_L$ = 1 nF, $T_A$ = 25°C;<br>step magnetic field of 400 G                                                       | -                      | 230  | -                      | V/ms                |

| OVER FIELD FAULT CHARACTER                               | STICS                   |                                                                                                                                  |                        |      |                        |                     |

| Fault Switchpoint Programming Bits                       | FAULT_<br>THRESH        |                                                                                                                                  | -                      | 6    | -                      | bit                 |

| Positive Field Fault Switchpoint<br>Range <sup>[9]</sup> | V <sub>FPSP</sub>       | T <sub>A</sub> = 25°C, programmable using<br>FAULT_THRESH bits                                                                   | 0.72 × V <sub>CC</sub> | -    | 0.88 × V <sub>CC</sub> | V                   |

| Negative Field Fault Switchpoint<br>Range <sup>[9]</sup> | V <sub>FNSP</sub>       | T <sub>A</sub> = 25°C, programmable using<br>FAULT_THRESH bits                                                                   | 0.12 × V <sub>CC</sub> | -    | 0.28 × V <sub>CC</sub> | V                   |

| Fault Switchpoint Step Size                              | Step <sub>FAULT</sub>   | $T_A = 25^{\circ}C$ , Average Fault Switchpoint step<br>size, V <sub>CC</sub> = 5 V                                              | -                      | 16   | _                      | mV                  |

| Fault Hysteresis Programming Bits                        | FAULT_HYST              |                                                                                                                                  | -                      | 2    | -                      | bit                 |

|                                                          | V <sub>FHYST</sub>      | T <sub>A</sub> = 25°C, FAULT_HYST = 0 (decimal),<br>FAULT_THRESH = 0, no hysteresis                                              | -                      | 0    | -                      | mV                  |

|                                                          |                         | T <sub>A</sub> = 25°C, FAULT_HYST = 1 (decimal),<br>FAULT_THRESH = 0, V <sub>CC</sub> = 5 V                                      | -                      | 30   | -                      | mV                  |

| Fault Hysteresis Level Range <sup>[9]</sup>              |                         | T <sub>A</sub> = 25°C, FAULT_HYST = 2 (decimal),<br>FAULT_THRESH = 0, V <sub>CC</sub> = 5 V                                      | -                      | 60   | -                      | mV                  |

|                                                          |                         | $T_A = 25^{\circ}C$ , FAULT_HYST = 3 (decimal),<br>FAULT_THRESH = 0, maximum hysteresis<br>value, $V_{CC} = 5 V$                 | -                      | 120  | _                      | mV                  |

| Enable Latched Fault Bit                                 | FAULT_<br>LATCH         |                                                                                                                                  | -                      | 1    | _                      | bit                 |

| DC Fault Switchpoint Error                               | Err <sub>DFS</sub>      | FAULT_THRESH = 0 (decimal), $R_{F(PULLUP)}$ = 10 k $\Omega$ from FAULT to VCC; measured under DC conditions, $V_{FHYST}$ = 60 mV | -                      | ±40  | _                      | mV                  |

| DC Fault Switchpoint Symmetry Error                      | Err <sub>DFSS</sub>     | FAULT_THRESH = 0 (decimal), $R_{F(PULLUP)}$ = 10 k $\Omega$ from FAULT to VCC; measured under DC conditions, $V_{FHYST}$ = 60 mV | -                      | ±60  | _                      | mV                  |

| FAULT Pin Low Output Voltage                             | VFAULTL                 | $R_{F(PULLUP)} = 10 \text{ k}\Omega \text{ from } \overline{FAULT} \text{ to VCC}$                                               | -                      | _    | 0.3                    | V                   |

| Transient Fault Response Time [10]                       | t <sub>TFR</sub>        |                                                                                                                                  | -                      | 4.5  | -                      | μs                  |

| Transient Fault Release Time                             | t <sub>TFRL</sub>       |                                                                                                                                  | -                      | 2.5  | -                      | μs                  |

Continued on the next page ...

## OPERATING CHARACTERISTICS (continued): valid through the full operating temperature range, T<sub>A</sub>, C<sub>BYPASS</sub> = 0.1 μF, and V<sub>CC</sub> = 5 V, unless otherwise specified

| Characteristic                                                           | Symbol                   | Test Conditions                                                                    | Min. | Тур.                              | Max.            | Unit <sup>[1]</sup> |

|--------------------------------------------------------------------------|--------------------------|------------------------------------------------------------------------------------|------|-----------------------------------|-----------------|---------------------|

| FAULT CHARACTERISTICS (contin                                            | ued)                     |                                                                                    |      |                                   |                 | -                   |

| Fault Delay Due to Load Capacitance                                      | t <sub>FDC</sub>         | $R_{F(PULLUP)} = 10 \text{ k}\Omega \text{ from } \overline{FAULT} \text{ to VCC}$ | -    | 0.5                               | -               | µs/nF               |

| External Pull-Up Supply Voltage                                          | V <sub>F(PULLUP)</sub>   |                                                                                    | 1.65 | V <sub>CC</sub>                   | V <sub>CC</sub> | V                   |

| External FAULT Pull-Up Resistor                                          | R <sub>F(PULLUP)</sub>   |                                                                                    | 4.7  | -                                 | _               | kΩ                  |

| External FAULT Capacitance                                               | C <sub>F</sub>           |                                                                                    | _    | -                                 | 10              | nF                  |

| Internal FAULT Pull-Up Resistor                                          | R <sub>IF(PULLUP)</sub>  |                                                                                    | -    | 10                                | -               | kΩ                  |

| Internal FAULT Pull-Up Current                                           | I <sub>IF(PULLUP)</sub>  |                                                                                    | -    | 40                                | -               | μA                  |

| QUIESCENT VOLTAGE OUTPUT (V                                              | оит(q) <sup>) [2]</sup>  |                                                                                    |      |                                   |                 |                     |

| Initial Unprogrammed Quiescent<br>Voltage Output <sup>[2][11]</sup>      | V <sub>OUT(Q)init</sub>  | T <sub>A</sub> = 25°C                                                              | 2.4  | 2.5                               | 2.6             | V                   |

| Quiescent Voltage Output<br>Programming Range [2][5][12]                 | V <sub>OUT(Q)PR</sub>    | T <sub>A</sub> = 25°C                                                              | 2.3  | -                                 | 2.7             | V                   |

| Quiescent Voltage Output<br>Programming Bits [13]                        | QVO                      |                                                                                    | _    | 9                                 | _               | bit                 |

| Average Quiescent Voltage Output<br>Programming Step Size [2][14][15]    | Step <sub>VOUT(Q)</sub>  | T <sub>A</sub> = 25°C                                                              | 1.9  | 2.3                               | 2.8             | mV                  |

| Quiescent Voltage Output<br>Programming Resolution <sup>[2][16]</sup>    | Err <sub>PGVOUT(Q)</sub> | T <sub>A</sub> = 25°C                                                              | _    | ±0.5 ×<br>Step <sub>VOUT(Q)</sub> | _               | mV                  |

| SENSITIVITY (Sens) [2]                                                   | ·                        |                                                                                    |      |                                   |                 |                     |

|                                                                          | Sens <sub>init</sub>     | SENS_COARSE = 00, T <sub>A</sub> = 25°C                                            | _    | 1                                 | _               | mV/G                |

| Initial Upprogrammed Canaitivity [11]                                    |                          | SENS_COARSE = 01, T <sub>A</sub> = 25°C                                            | _    | 2.2                               | _               | mV/G                |

| Initial Unprogrammed Sensitivity [11]                                    |                          | SENS_COARSE = 10, T <sub>A</sub> = 25°C                                            | -    | 4.7                               | -               | mV/G                |

|                                                                          |                          | SENS_COARSE = 11, T <sub>A</sub> = 25°C                                            | -    | 9.6                               | -               | mV/G                |

|                                                                          |                          | SENS_COARSE = 00, T <sub>A</sub> = 25°C                                            | 0.6  | -                                 | 1.3             | mV/G                |

| Sensitivity Programming Dange [5][12]                                    | Cono                     | SENS_COARSE = 01, T <sub>A</sub> = 25°C                                            | 1.3  | -                                 | 2.9             | mV/G                |

| Sensitivity Programming Range <sup>[5][12]</sup>                         | Sens <sub>PR</sub>       | SENS_COARSE = 10, T <sub>A</sub> = 25°C                                            | 2.9  | -                                 | 6.4             | mV/G                |

|                                                                          |                          | SENS_COARSE = 11, T <sub>A</sub> = 25°C                                            | 6.4  | -                                 | 14              | mV/G                |

| Coarse Sensitivity Programming Bits [17]                                 | SENS_<br>COARSE          |                                                                                    | _    | 2                                 | _               | bit                 |

| Fine Sensitivity Programming Bits [13]                                   | SENS_FINE                |                                                                                    | _    | 9                                 | _               | bit                 |

|                                                                          |                          | SENS_COARSE = 00, T <sub>A</sub> = 25°C                                            | 2.4  | 3.2                               | 4.1             | μV/G                |

| Average Fine Sensitivity and                                             | 0.5                      | SENS_COARSE = 01, T <sub>A</sub> = 25°C                                            | 5    | 6.6                               | 8.5             | μV/G                |

| Temperature Compensation<br>Programming Step Size <sup>[2][14][15]</sup> | Step <sub>SENS</sub>     | SENS_COARSE = 10, T <sub>A</sub> = 25°C                                            | 11   | 14.2                              | 18              | μV/G                |

| 5 5 1                                                                    |                          | SENS_COARSE = 11, T <sub>A</sub> = 25°C                                            | 22   | 29                                | 38              | μV/G                |

| Sensitivity Programming<br>Resolution <sup>[2][16]</sup>                 | Err <sub>PGSENS</sub>    | T <sub>A</sub> = 25°C                                                              | _    | ±0.5 ×<br>Step <sub>SENS</sub>    | _               | μV/G                |

| FACTORY-PROGRAMMED SENSITI                                               |                          | RATURE COEFFICIENT                                                                 |      |                                   |                 |                     |

| Sensitivity Temperature Coefficient <sup>[2]</sup>                       | TC <sub>SENS</sub>       | $T_A$ =150°C, $T_A$ = -40°C, calculated relative to 25°C                           | _    | 0                                 | _               | %/°C                |

| Sensitivity Drift Through Temperature                                    | ASono                    | T <sub>A</sub> = 25°C to 150°C                                                     | -2.5 | -                                 | 2.5             | %                   |

| Range [2][12][18][23]                                                    | $\Delta Sens_{TC}$       | $T_A = -40^{\circ}C$ to 25°C                                                       | -3   | _                                 | 3               | %                   |

Continued on the next page ...

#### OPERATING CHARACTERISTICS (continued): valid through the full operating temperature range, T<sub>A</sub>, C<sub>BYPASS</sub> = 0.1 µF, and V<sub>CC</sub> = 5 V, unless otherwise specified

| Characteristic                                                            | Symbol                    | Test Conditions                                                                                   | Min. | Тур.           | Max. | Unit <sup>[1]</sup> |

|---------------------------------------------------------------------------|---------------------------|---------------------------------------------------------------------------------------------------|------|----------------|------|---------------------|

| FACTORY-PROGRAMMED QUIESC                                                 | ENT VOLTAG                | E OUTPUT TEMPERATURE COEFFICIENT                                                                  |      | · · · · ·      |      | · ·                 |

| Quiescent Voltage Output<br>Temperature Coefficient <sup>[2]</sup>        | TC <sub>QVO</sub>         | $T_A = 150^{\circ}C$ , $T_A = -40^{\circ}C$ , calculated relative to 25°C                         | _    | 0              | _    | mV/°C               |

| Quiescent Voltage Output Drift                                            |                           | SENS_COARSE = 00, SENS_COARSE = 01,<br>or SENS_COARSE = 10, $T_A = 25^{\circ}C$ to $150^{\circ}C$ | -10  | -              | 10   | mV                  |

| Through Temperature Range <sup>[2][12][18]</sup>                          | $\Delta V_{OUT(Q)TC}$     | SENS_COARSE = 11, T <sub>A</sub> = 25°C to 150°C                                                  | -15  | _              | 15   | mV                  |

|                                                                           |                           | $T_A = -40^{\circ}C$ to 25°C                                                                      | -30  | _              | 30   | mV                  |

| Average Quiescent Voltage<br>Output Temperature Compensation<br>Step Size | Step <sub>QVOTC</sub>     |                                                                                                   | _    | 2.3            | _    | mV                  |

| LOCK BIT PROGRAMMING                                                      |                           | · · · · ·                                                                                         |      |                |      |                     |

| EEPROM Lock Bit                                                           | EELOCK                    |                                                                                                   | _    | 1              | _    | bit                 |

| ERROR COMPONENTS                                                          |                           | · · · · ·                                                                                         |      |                |      |                     |

| Linearity Sensitivity Error [2][19]                                       | Lin <sub>ERR</sub>        |                                                                                                   | –1   | < ±0.25        | 1    | %                   |

| Symmetry Sensitivity Error [2]                                            | Sym <sub>ERR</sub>        |                                                                                                   | -0.5 | < ±0.25        | 0.5  | %                   |

| Ratiometry Quiescent Voltage Output<br>Error [2][20]                      | Rat <sub>ERRVOUT(Q)</sub> | Relative to $V_{CC} = 5 V \pm 5\%$                                                                | -0.3 | 0              | 0.3  | %                   |

| Ratiometry Sensitivity Error <sup>[2][20]</sup>                           | Rat <sub>ERRSens</sub>    | Relative to $V_{CC}$ = 5 V ±5%                                                                    | –1   | < ±0.5         | 1    | %                   |

| Ratiometry Clamp Error <sup>[2][21]</sup>                                 | Rat <sub>ERRCLP</sub>     | $T_A = 25^{\circ}C$ , Relative to $V_{CC} = 5 V \pm 5\%$                                          | _    | < ±1           | _    | %                   |

| Sensitivity Drift Due to Package<br>Hysteresis <sup>[2]</sup>             | ∆Sens <sub>PKG</sub>      | $T_A$ = 25°C, after temperature cycling, 25°C to 150°C and back to 25°C                           | _    | -1.25<br>±1.25 | _    | %                   |

| Sensitivity Drift Over Lifetime [22]                                      | ∆Sens <sub>LIFE</sub>     | $T_A = 25^{\circ}C$ , shift after AEC Q100 grade 0 qualification testing                          | _    | ±1%            | _    | %                   |

<sup>[1]</sup> 1 G (gauss) = 0.1 mT (millitesla).

<sup>[2]</sup> See Characteristic Definitions section.

$^{[3]}f_{C}$  varies up to approximately ±5% over the full operating ambient temperature range,  $T_{A}$ .  $^{[4]}$  If the programmed Fault Switchpoint exceeds the clamp voltage, Fault operation will have priority over clamp operation.

$^{[5]}$  Sens,  $V_{OUT(Q)}$ ,  $V_{CLP(LOW)}$ , and  $V_{CLP(HIGH)}$  scale with  $V_{CC}$  due to ratiometry.  $^{[6]}$  Noise, measured in mV\_{PP} and in mV\_{RMS}, is dependent on the sensitivity of the device.

<sup>[7]</sup> Output stability is maintained for capacitive loads as large as 10 nF

<sup>[8]</sup> High-to-low transition of output voltage is a function of external load components and device sensitivity.

<sup>[9]</sup> Fault Switchpoint and Fault Hysteresis are ratiometric.

<sup>[10]</sup> Refer to Fault Characteristics section for the impact of load circuit and different Fault switchpoint settings on Transient Fault

Response Time.

<sup>[11]</sup> Raw device characteristic values before any programming.

<sup>[12]</sup> Exceeding the specified ranges will cause sensitivity and Quiescent Voltage Output drift through the temperature range to deteriorate beyond the specified values. <sup>[13]</sup> Refer to Functional Description section.

<sup>[14]</sup> Step size is larger than required, in order to provide for manufacturing spread. See Characteristic Definitions section.

[15] Non-ideal behavior in the programming DAC can cause the step size at each significant bit rollover code to be greater than twice the maximum specified value of

Step<sub>VOUT(Q)</sub> or Step<sub>SENS</sub>.

<sup>[16]</sup> Overall programming value accuracy. See Characteristic Definitions section.

[17] Each A1365 part number is factory-programmed and temperature compensated at a different coarse sensitivity setting. Changing coarse bits setting could cause sensitivity drift through temperature range , $\Delta Sens_{TC}$ , to exceed specified limits.

[18] Allegro will be testing and temperature compensating each device at 150°C. Allegro will not be testing devices at -40°C. Temperature compensation codes will be applied based on characterization data.

<sup>[19]</sup> Linearity applies to output voltage ranges of ±2 V from the quiescent output for bidirectional devices.

<sup>[20]</sup> Percent change from actual value at  $V_{CC} = 5$  V, for a given temperature, through the supply voltage operating range. <sup>[21]</sup> Percent change from actual value at  $V_{CC} = 5$  V,  $T_A = 25^{\circ}$ C, through the supply voltage operating range. <sup>[22]</sup> Based on characterization data obtained during standardized stress test for Qualification of Integrated Circuits. Cannot be guaranteed. Drift is a function of customer application conditions. Contact Allegro MicroSystems for further information.

[23] Includes sensitivity drift due to package hysteresis after exposing the sensor to a temperature of 150°C for 60 seconds during test.

#### CHARACTERISTIC PERFORMANCE DATA

Timebase-6.96 µsTrigge2.00 µs/divStop50.0 ks2.5 GS/sEdge X1 = -33.2 ns ΔX = 2.0216 μs X2 = 1.9884 μs 1/ΔX = 494.66 kHz 11/6/2013 10:22:47 AM

9

Trigger

C1 DC

Positiv

FLT DC1M

-3.0100

## A1365

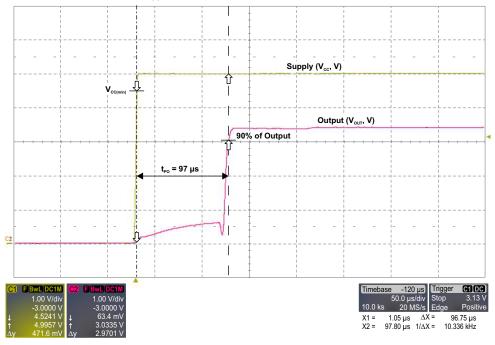

#### Power-On Time (t<sub>PO</sub>)

400 G Constant Excitation Signal with V<sub>CC</sub> 10% to 90% rise time = 1  $\mu s$  Sensitivity = 2 mV/G, C<sub>BYPASS</sub> = Open, C<sub>L</sub> = 1 nF

Allegro MicroSystems, LLC 115 Northeast Cutoff Worcester, Massachusetts 01615-0036 U.S.A. 1.508.853.5000; www.allegromicro.com

## A1365

#### CHARACTERISTIC DEFINITIONS

#### Power-On Time (t<sub>PO</sub>)

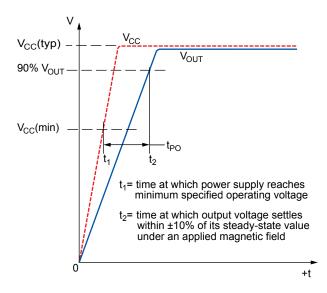

When the supply is ramped to its operating voltage, the device requires a finite time to power its internal components before responding to an input magnetic field.

Power-On Time (t<sub>PO</sub>) is defined as: the time it takes for the output voltage to settle within  $\pm 10\%$  of its steady-state value under an applied magnetic field, after the power supply has reached its minimum specified operating voltage (V<sub>CC(min)</sub>) as shown in Figure 1.

# Temperature Compensation Power-On Time $(t_{TC})$

After Power-On Time  $(t_{PO})$  elapses,  $t_{TC}$  is also required before a valid temperature compensated output.

#### Propagation Delay (t<sub>pd</sub>)

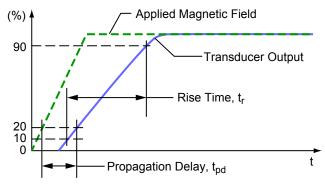

The time interval between a) when the applied magnetic field reaches 20% of its final value, and b) when the output reaches 20% of its final value (see Figure 2).

#### Rise Time (t<sub>r</sub>)

The time interval between a) when the sensor IC reaches 10% of its final value, and b) when it reaches 90% of its final value (see Figure 2). Both  $t_r$  and  $t_{RESPONSE}$  are detrimentally affected by eddy current losses observed in the conductive IC ground plane.

#### Response Time (t<sub>RESPONSE</sub>)

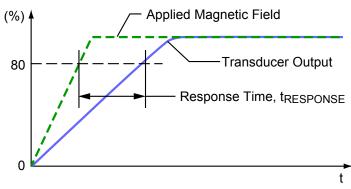

The time interval between a) when the applied magnetic field reaches 80% of its final value, and b) when the sensor reaches 80% of its output corresponding to the applied magnetic field (see Figure 3).

### Delay to Clamp $(t_{CLP})$

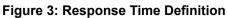

A large magnetic input step may cause the clamp to overshoot its steady-state value. The Delay to Clamp ( $t_{CLP}$ ) is defined as: the time it takes for the output voltage to settle within steady-state clamp voltage  $\pm 1\%$  of Clamp Voltage Dynamic Range, after initially passing through its steady-state voltage, as shown in Figure 4. Clamp Voltage Dynamic Range is defined as  $V_{CLP(HIGH)(min)} - V_{CLP(LOW)(max)}$ .

Figure 1: Power-On Time Definition

Figure 2: Propagation Delay and Rise Time Definitions

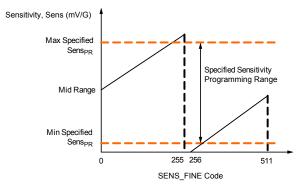

### Quiescent Voltage Output (V<sub>OUT(Q)</sub>)

In the quiescent state (no significant magnetic field: B = 0 G), the output (V<sub>OUT(Q)</sub>) has a constant ratio to the supply voltage (V<sub>CC</sub>) throughout the entire operating ranges of V<sub>CC</sub> and ambient temperature (T<sub>A</sub>).

#### Initial Unprogrammed Quiescent Voltage Output (V<sub>OUT(Q)init</sub>)

Before any programming, the Quiescent Voltage Output  $(V_{OUT(Q)})$  has a nominal value of  $V_{CC}$  /2, as shown in Figure 5.

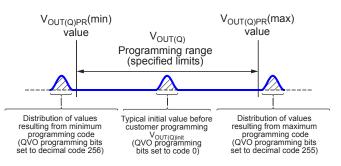

#### Quiescent Voltage Output Programming Range (V<sub>OUT(Q)PR</sub>)

The Quiescent Voltage Output (V<sub>OUT(Q)</sub>) can be programmed within the Quiescent Voltage Output Range limits: V<sub>OUT(Q)PR(min)</sub> and V<sub>OUT(Q)PR(max)</sub>. Exceeding the specified Quiescent Voltage Output Range will cause Quiescent Voltage Output Drift Through Temperature Range  $\Delta V_{OUT(Q)TC}$  to deteriorate beyond the specified values, as shown in Figure 5.

#### Average Quiescent Voltage Output Programming Step Size (Step<sub>VOUT(Q)</sub>)

The Average Quiescent Voltage Output Progamming Step Size (Step<sub>VOUT(Q)</sub>) is determined using the following calculation:

Figure 4: Delay to Clamp Definition

$$Step_{VOUT(Q)} = \frac{V_{OUT(Q)maxcode} - V_{OUT(Q)mincode}}{2^n - 1} , \qquad (1)$$

where n is the number of available programming bits in the trim range, 9 bits,  $V_{OUT(Q)maxcode}$  is at decimal code 255, and  $V_{OUT(Q)mincode}$  is at decimal code 256.

#### Quiescent Voltage Output Programming Resolution (Err<sub>PGVOUT(Q)</sub>)

The programming resolution for any device is half of its programming step size. Therefore, the typical programming resolution will be:

$$\operatorname{Err}_{\operatorname{PGVOUT}(Q)}(\operatorname{typ}) = 0.5 \times \operatorname{Step}_{\operatorname{VOUT}(Q)}(\operatorname{typ})$$

(2)

#### Quiescent Voltage Output Temperature Coefficient (TC<sub>QVO</sub>)

Device  $V_{OUT(Q)}$  changes as temperature changes, with respect to its programmed Quiescent Voltage Output Temperature Coefficient,  $TC_{QVO}$ .  $TC_{QVO}$  is programmed at 150°C and is calculated relative to the nominal  $V_{OUT(Q)}$  programming temperature of 25°C.  $TC_{OVO}$  (mV/°C) is defined as:

$$TC_{QVO} = [V_{OUT(Q)T2} - V_{OUT(Q)T1}][1/(T2 - T1)]$$

(3)

where T1 is the nominal  $V_{OUT(Q)}$  programming temperature of 25°C, and T2 is the TC<sub>QVO</sub> programming temperature of 150°C. The expected  $V_{OUT(Q)}$  through the full ambient temperature range ( $V_{OUT(Q)EXPECTED(TA)}$ ) is defined as:

$$V_{OUT(O)EXPECTED}(T_A) = V_{OUT(O)TI} + TC_{OVO}(T_A - TI)$$

(4)

Figure 5: Quiescent Voltage Output Range Definition

$V_{OUT(Q)EXPECTED(TA)}$  should be calculated using the actual measured values of  $V_{OUT(Q)T1}$  and  $TC_{QVO}$  rather than programming target values.

# Quiescent Voltage Output Drift Through Temperature Range ( $\Delta V_{OUT(Q)TC}$ )

Due to internal component tolerances and thermal considerations, the Quiescent Voltage Output  $(V_{OUT(Q)})$  may drift from its nominal value through the operating ambient temperature  $(T_A)$ . The Quiescent Voltage Output Drift Through Temperature Range  $(\Delta_{VOUT(Q)TC})$  is defined as:

$$D_{VOUT(Q)TC} = V_{OUT(Q)(TA)} - V_{OUT(Q)EXPECTED(TA)}$$

(5)

$\Delta V_{OUT(Q)TC}$  should be calculated using the actual measured values of  $\Delta V_{OUT(Q)(TA)}$  and  $\Delta V_{OUT(Q)EXPECTED(TA)}$  rather than programming target values.

#### Sensitivity (Sens)

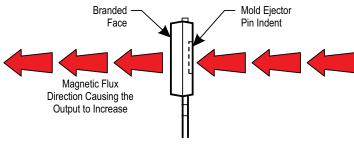

The presence of a south polarity magnetic field, perpendicular to the branded surface of the package face, increases the output voltage from its quiescent value toward the supply voltage rail. The amount of the output voltage increase is proportional to the magnitude of the magnetic field applied.

Conversely, the application of a north polarity field decreases the output voltage from its quiescent value. This proportionality is specified as the magnetic sensitivity, Sens (mv/G), of the device, and it is defined as:

$$Sens = \frac{V_{OUT(BPOS)} - V_{OUT(BNEG)}}{BPOS - BNEG} , \qquad (6)$$

where BPOS and BNEG are two magnetic fields with opposite polarities.

#### Initial Unprogrammed Sensitivity (Sensinit)

Before any programming, Sensitivity has a nominal value that depends on the SENS\_COARSE bits setting. Each A1365 variant has a different SENS\_COARSE setting.

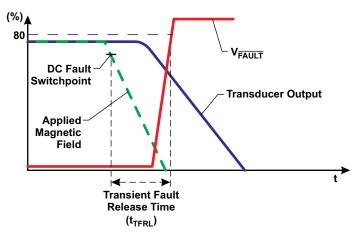

#### Sensitivity Programming Range (Sens<sub>PR</sub>)

The magnetic sensitivity (Sens) can be programmed around its initial value within the sensitivity range limits:  $Sens_{PR}(min)$  and  $Sens_{PR}(max)$ . Exceeding the specified Sensitivity Range will cause Sensitivity Drift Through Temperature Range  $\Delta Sens_{TC}$  to deteriorate beyond the specified values. Refer to the Quiescent Voltage Output Range section for a conceptual explanation of how value distributions and ranges are related.

# Average Fine Sensitivity Programming Step Size (Step<sub>SENS</sub>)

Refer to the Average Quiescent Voltage Output Programming Step Size section for a conceptual explanation.

#### Sensitivity Programming Resolution (Err<sub>PGSENS</sub>)

Refer to the Quiescent Voltage Output Programming Resolution section for a conceptual explanation.

#### Sensitivity Temperature Coefficient (TC<sub>SENS</sub>)

Device sensitivity changes as temperature changes, with respect to its programmed sensitivity temperature coefficient,  $TC_{SENS}$ .  $TC_{SENS}$  is programmed at 150°C, and calculated relative to the nominal sensitivity programming temperature of 25°C.  $TC_{SENS}$  (%/°C) is defined as:

$$TC_{SENS} = \left(\frac{Sens_{T2} - Sens_{T1}}{Sens_{T1}} \times 100\%\right) \left(\frac{1}{T2 - T1}\right), \quad (7)$$

where T1 is the nominal Sens programming temperature of 25°C, and T2 is the TC<sub>SENS</sub> programming temperature of 150°C. The expected value of Sens over the full ambient temperature range,  $Sens_{EXPECTED(TA)}$ , is defined as:

$$Sens_{EXPECTED(TA)} = Sens_{TI} \times \left[ 100\% + \frac{TC_{SENS} (T_{A} - TI)}{100} \right]$$

(8)

$Sens_{EXPECTED(TA)}$  should be calculated using the actual measured values of  $Sens_{T1}$  rather than programming target values.

# Sensitivity Drift Through Temperature Range (ΔSens<sub>TC</sub>)

Second-order-sensitivity temperature-coefficient effects cause the magnetic sensitivity, Sens, to drift from its expected value over the operating ambient temperature range ( $T_A$ ). The Sensitivity Drift Through Temperature Range ( $\Delta Sens_{TC}$ ) is defined as:

$$\Delta \text{Sens}_{\text{TC}} = \frac{\text{Sens}_{\text{TA}} - \text{Sens}_{\text{EXPECTED(TA)}}}{\text{Sens}_{\text{EXPECTED(TA)}}} \times 100\% \quad . \tag{9}$$

#### Sensitivity Drift Due to Package Hysteresis (ΔSens<sub>PKG</sub>)

Package stress and relaxation can cause the device sensitivity at  $T_A = 25^{\circ}C$  to change during and after temperature cycling. The sensitivity drift due to package hysteresis ( $\Delta Sens_{PKG}$ ) is defined as:

$$\Delta \text{Sens}_{\text{PKG}} = \frac{\text{Sens}_{(25^{\circ}\text{C})2} - \text{Sens}_{(25^{\circ}\text{C})1}}{\text{Sens}_{(25^{\circ}\text{C})1}} \times 100\% \quad , \qquad (10)$$

where  $\text{Sens}_{(25^{\circ}\text{C})1}$  is the programmed value of sensitivity at  $T_A = 25^{\circ}\text{C}$ , and  $\text{Sens}_{(25^{\circ}\text{C})2}$  is the value of sensitivity at  $T_A = 25^{\circ}\text{C}$ , after temperature cycling  $T_A$  up to 150°C and back to 25°C.

#### Linearity Sensitivity Error (Lin<sub>ERR</sub>)

The A1365 is designed to provide a linear output in response to a ramping applied magnetic field. Consider two magnetic fields, B1 and B2. Ideally, the sensitivity of a device is the same for both fields, for a given supply voltage and temperature. Linearity error is present when there is a difference between the sensitivities measured at B1 and B2.

#### **Linearity Error**

Linearity error is calculated separately for the positive  $(Lin_{ERRPOS})$  and negative  $(Lin_{ERRNEG})$  applied magnetic fields. Linearity Error (%) is measured and defined as:

$$\operatorname{Lin}_{\mathrm{ERRPOS}} = \left(1 - \frac{\operatorname{Sens}_{\mathrm{BPOS2}}}{\operatorname{Sens}_{\mathrm{BPOS1}}}\right) \times 100\% \quad ,$$

$$\operatorname{Lin}_{\mathrm{ERRNEG}} = \left(1 - \frac{\operatorname{Sens}_{\mathrm{BNEG2}}}{\operatorname{Sens}_{\mathrm{BNEG1}}}\right) \times 100\% \quad , \tag{11}$$

where:

$$\operatorname{Sens}_{Bx} = \frac{|V_{\text{OUT}(Bx)} - V_{\text{OUT}(Q)}|}{B_x} \quad , \tag{12}$$

and BPOSx and BNEGx are positive and negative magnetic fields, with respect to the quiescent voltage output such that  $|BPOS2| = 2 \times |BPOS1|$  and  $|BNEG2| = 2 \times |BNEG1|$ .

Then:

$$\operatorname{Lin}_{\operatorname{ERR}} = \max(\operatorname{Lin}_{\operatorname{ERRPOS}}, \operatorname{Lin}_{\operatorname{ERRNEG}})$$

. (13)

#### Symmetry Sensitivity Error (Sym<sub>ERR</sub>)

The magnetic sensitivity of an A1365 device is constant for any two applied magnetic fields of equal magnitude and opposite polarities. Symmetry Error,  $Sym_{ERR}$  (%), is measured and defined as:

$$Sym_{ERR} = \left(1 - \frac{Sens_{BPOS}}{Sens_{BNEG}}\right) \times 100\% , \qquad (14)$$

where  $\text{Sens}_{Bx}$  is as defined in equation 12, and BPOSx and BNEGx are positive and negative magnetic fields such that |BPOSx| = |BNEGx|.

#### Ratiometry Error (Rat<sub>ERR</sub>)

The A1365 device features ratiometric output. This means that the Quiescent Voltage Output ( $V_{OUT(Q)}$ ) magnetic sensitivity, Sens, and Output Voltage Clamp ( $V_{CLP(HIGH)}$  and  $V_{CLP(LOW)}$ ) are proportional to the Supply Voltage ( $V_{CC}$ ). In other words, when the supply voltage increases or decreases by a certain percentage, each characteristic also increases or decreases by the same percentage. Error is the difference between the measured change in the supply voltage relative to 5 V, and the measured change in each characteristic.

The ratiometric error in Quiescent Voltage Output, Rat<sub>ERRVOUT(Q)</sub> (%), for a given supply voltage ( $V_{CC}$ ) is defined as:

$$\operatorname{Rat}_{\operatorname{ERRVOUT}(Q)} = \left(1 - \frac{V_{\operatorname{OUT}(Q)(\operatorname{VCC})} / V_{\operatorname{OUT}(Q)(5\operatorname{V})}}{V_{\operatorname{CC}} / 5\operatorname{V}}\right) \times 100\% \quad (15)$$

The ratiometric error in magnetic sensitivity,  $Rat_{ERRSens}$  (%), for a given Supply Voltage  $(V_{CC})$  is defined as:

$$\operatorname{Rat}_{\operatorname{ERRSens}} = \left(1 - \frac{\operatorname{Sens}_{(\operatorname{VCC})} / \operatorname{Sens}_{(5\operatorname{V})}}{V_{\operatorname{CC}} / 5\operatorname{V}}\right) \times 100\% \quad . \tag{16}$$

The ratiometric error in the clamp voltages,  $Rat_{ERRCLP}$  (%), for a given supply voltage (V $_{CC}$ ) is defined as:

$$\operatorname{Rat}_{\operatorname{ERRCLP}} = \left(1 - \frac{V_{\operatorname{CLP}(\operatorname{VCC})} / V_{\operatorname{CLP}(5\operatorname{V})}}{V_{\operatorname{CC}} / 5\operatorname{V}}\right) \times 100\% , \qquad (17)$$

where  $V_{\mbox{CLP}}$  is either  $V_{\mbox{CLP(HIGH)}}$  or  $V_{\mbox{CLP(LOW)}}.$

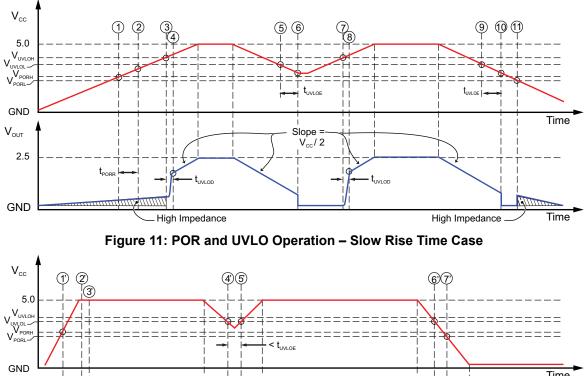

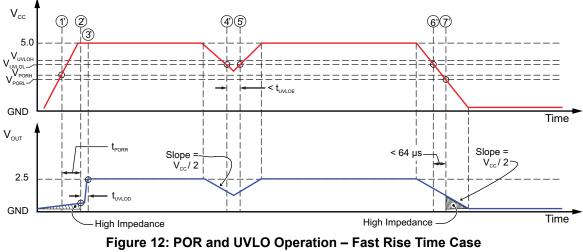

#### Power-On Reset Voltage (V<sub>POR</sub>)

On power-up, to initialize to a known state and avoid current spikes, the A1365 is held in Reset state. The Reset signal is disabled when  $V_{CC}$  reaches  $V_{UVLOH}$  and time  $t_{PORR}$  has elapsed, allowing the output voltage to go from a high-impedance state into normal operation. During power-down, the Reset signal is enabled when  $V_{CC}$  reaches  $V_{PORL}$ , causing the output voltage to go into a high-impedance state. (Note that a detailed description of POR and UVLO operation can be found in the Functional Description section).

### Power-On Reset Release Time (t<sub>PORR</sub>)

When  $V_{CC}$  rises to  $V_{PORH}$ , the Power-On Reset Counter starts. The A1365 output voltage will transition from a high-impedance state to normal operation only when the Power-On Reset Counter has reached  $t_{PORR}$  and  $V_{CC}$  has exceeded  $V_{UVLOH}$ .

### Undervoltage Lockout Threshold (V<sub>UVLO</sub>)

If  $V_{CC}$  drops below  $V_{UVLOL}$ , the output voltage will be pulled to GND. If  $V_{CC}$  starts rising, the A1365 will come out of this lock state when  $V_{CC}$  reaches  $V_{UVLOH}$ .

### UVLO Enable/Disable Delay Time (t<sub>UVLO</sub>)

When a falling  $V_{CC}$  reaches  $V_{UVLOL}$ , time  $t_{UVLOE}$  is required to engage the Undervoltage Lockout state. When  $V_{CC}$  rises above  $V_{UVLOH}$ , time  $t_{UVLOD}$  is required to disable UVLO and to have a valid output voltage.

### Output Saturation Voltage (V<sub>SAT</sub>)

When output voltage clamps are disabled, the output voltage can swing to a maximum of  $V_{SAT(HIGH)}$  and to a minimum of  $V_{SAT(LOW)}$ .

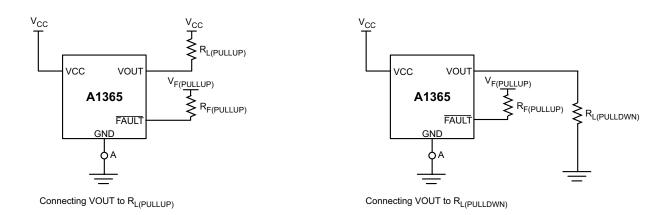

## Broken Wire Voltage (V<sub>BRK</sub>)

If the GND pin is disconnected (broken wire event), output voltage will go to  $\rm V_{BRK(HIGH)}$  if a load resistor is connected to VCC,

or to  $V_{BRK(LOW)}$  if a load resistor is connected to GND.

### DC Fault Switchpoint Error (Err<sub>DFS</sub>)

The Over Field Fault Switchpoint is user-programmable with a step size of  $\text{Step}_{FAULT}$ . DC Fault Switchpoint Error is a deviation from the user-programmed value that occurs over the operating temperature range.

# DC Fault Switchpoint Symmetry Error (Err<sub>DFSS</sub>)

Writing FLT\_THRESH bits sets the DC Fault Switchpoint for positive and negative magnetic fields as follows:

Positive Field Fault Switchpoint ( $V_{FPSP}$ ) = Xpos ×  $V_{CC}$  and Negative Field Fault Switchpoint ( $V_{FNSP}$ ) = Xneg ×  $V_{CC}$  where Xpos + Xneg = 1. For example, programming  $V_{FPSP}$  = 0.8 ×  $V_{CC}$ should automatically set  $V_{FNSP}$  = 0.2 ×  $V_{CC}$ . For a measured  $V_{FPSP}$ , the DC Fault Switchpoint Symmetry error is the delta between the expected  $V_{FNSP}$  and the measured one.

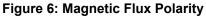

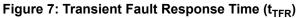

### Transient Fault Response Time (t<sub>TFR</sub>)

The time interval between a) when the input crosses the DC Fault Switchpoint and b) when the  $\overline{FAULT}$  pin reaches 20% of its final value.

Low-Noise, High-Precision, Programmable Linear Hall-Effect Sensor IC with High-Bandwidth (120 kHz) Analog Output and Integrated Fault Comparator with Self-Test Diagnostic Mode

#### Transient Fault Release Time (t<sub>TFRL</sub>)

As the Over Field Fault condition goes away,  $t_{TFRL}$  is the time interval between a) when the recovering input crosses the DC Fault Switchpoint and when the FAULT pin reaches 80% of its final value. Note that the DC Fault Switchpoint will be impacted by the programmed Fault Hysteresis Level (V<sub>FHSYT</sub>).

Figure 8: Transient Fault Release Time (t<sub>TFRL</sub>)

Low-Noise, High-Precision, Programmable Linear Hall-Effect Sensor IC with High-Bandwidth (120 kHz) Analog Output and Integrated Fault Comparator with Self-Test Diagnostic Mode

#### FUNCTIONAL DESCRIPTION

# Programming Sensitivity and Quiescent Voltage Output

Sensitivity and V<sub>OUT(Q)</sub> can be adjusted by programming SENS\_FINE and QVO bits, as illustrated in Figure 9 and Figure 10.

Users should not program sensitivity or  $V_{OUT(Q)}$  beyond the maximum or minimum programming ranges specified in the Operating Characteristics table. Exceeding the specified limits will cause the sensitivity and  $V_{OUT(Q)}$  drift over the temperature range ( $\Delta Sens_{TC}$  and  $\Delta V_{OUT(Q)TC}$ ) to deteriorate beyond the specified values.

Programming sensitivity might cause a small drift in  $V_{OUT(Q)}$ . As a result, Allegro recommends programming sensitivity first, then  $V_{OUT(Q)}$ .

#### **Coarse Sensitivity**

Each A1365 variant is programmed to a different coarse sensitivity setting. Devices are tested, and temperature compensation is factory-programmed under that specific coarse sensitivity setting. If the coarse sensitivity setting is changed, by programming SENS\_COARSE bits, Allegro cannot guarantee the specified sensitivity drift through temperature range limits ( $\Delta Sens_{TC}$ ).

#### **Memory-Locking Mechanisms**

The A1365 is equipped with two distinct memory-locking mechanisms:

- **Default Lock** At power-up, all registers of the A1365 are locked by default. EEPROM and volatile memory cannot be read or written. To disable Default Lock, a specific 30-bit customer access code has to be written to address 0x24 within Access Code Timeout ( $t_{ACC} = 8$  ms) from power-up. After doing so, registers can be accessed. If VCC is power-cycled, the Default Lock will automatically be re-enabled. This ensures that during normal operation, memory content will not be altered due to unwanted glitches on VCC or the output pin.

- Lock Bit After EEPROM has been programmed by the user, the EELOCK bit can be set high and VCC power-cycled to permanently disable the ability to read or write any register. This will prevent the ability to disable Default Lock using the method described above. Note that after the EELOCK bit is set high and the VCC pin is power-cycled, you will not have the ability to clear the EELOCK bit or read/write any register.

Figure 9: Device Sensitivity versus SENS\_FINE Programmed Value

Figure 10: Device V<sub>OUT(Q)</sub> versus QVO Programmed Value

# Power-On Reset (POR) and Undervoltage Lockout (UVLO) Operation

The descriptions in this section assume:  $T_A = 25^{\circ}C$ , no output load ( $R_L$ ,  $C_L$ ), and no significant magnetic field is present.

- *Power-Up* At power-up, as V<sub>CC</sub> ramps up, the output is in a high-impedance state. When V<sub>CC</sub> crosses V<sub>PORH</sub> (location [1] in Figure 11 and [1'] in Figure 12), the POR Release counter starts counting for t<sub>PORR</sub>. At this point, if V<sub>CC</sub> exceeds V<sub>UVLOH</sub> [2'], the output will go to V<sub>CC</sub> / 2 after t<sub>UVLOD</sub> [3']. If V<sub>CC</sub> does not exceed V<sub>UVLOH</sub> [2], the output will stay in the high-impedance state until V<sub>CC</sub> reaches V<sub>UVLOH</sub> [3] and then go to V<sub>CC</sub> / 2 after t<sub>UVLOD</sub> [4].

- V<sub>CC</sub> drops below V<sub>CC</sub>(min)= 4.5 V If V<sub>CC</sub> drops below

V<sub>UVLOL</sub> [4', 5], the UVLO Enable Counter starts counting. If

V<sub>CC</sub> is still below V<sub>UVLOL</sub> when the counter reaches t<sub>UVLOE</sub>,

the UVLO function will be enabled and the ouput will be pulled near GND [6]. If  $V_{CC}$  exceeds  $V_{UVLOL}$  before the UVLO Enable Counter reaches 64 µs [5'], the output will continue to be  $V_{CC}/2$ .

- Coming out of UVLO While UVLO is enabled [6], if V<sub>CC</sub> exceeds V<sub>UVLOH</sub> [7], UVLO will be disabled after t<sub>UVLOD</sub>, and the output will be V<sub>CC</sub> / 2 [8].

- **Power-Down** As  $V_{CC}$  ramps down below  $V_{UVLOL}$  [6', 9], the UVLO Enable Counter will start counting. If  $V_{CC}$  is higher than  $V_{PORL}$  when the counter reaches  $t_{UVLOE}$ , the UVLO function will be enabled and the ouput will be pulled near GND [10]. The output will enter a high-impedance state as  $V_{CC}$  goes below  $V_{PORL}$  [11]. If  $V_{CC}$  falls below  $V_{PORL}$  before the UVLO Enable Counter reaches  $t_{UVLOE}$ , the output will transition directly into a high-impedance state [7'].

A1365

Low-Noise, High-Precision, Programmable Linear Hall-Effect Sensor IC with High-Bandwidth (120 kHz) Analog Output and Integrated Fault Comparator with Self-Test Diagnostic Mode

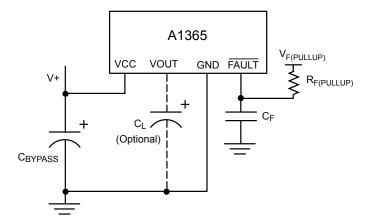

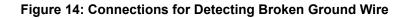

#### **Detecting Broken Ground Wire**

If the GND pin is disconnected, node A becoming open (see Figure 14), the VOUT pin will go to a high-impedance state. The output voltage will go to  $V_{BRK(HIGH)}$  if a load resistor  $R_{L(PULLUP)}$  is connected to  $V_{CC}$  or to  $V_{BRK(LOW)}$  if a load resistor  $R_{L(PULLDWN)}$  is connected to GND. The device will not respond to any applied magnetic field.

If the ground wire is reconnected, the A1365 will resume normal operation.

Figure 13: Typical Application Drawing

21

#### Self-Test Diagnostic Operation after Power-Up

The A1365 has a Self-Test Diagnostics operating mode, allowing the user to verify at any point: connectivity of the Analog Signal path, drifts in sensitivity and quiescent output voltage, and connectivity and functionality of the Over Field Fault Signal path. Timing of various parts of the self-test sequence are user programmable.

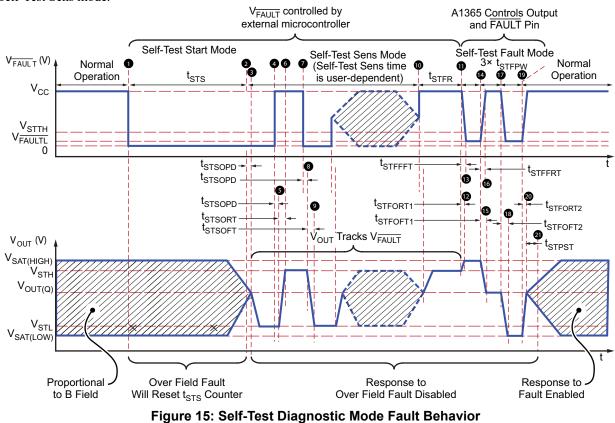

#### Self-Test Start Mode

After power-up is complete, the VOUT pin responds to the applied magnetic field, and the Over Field FAULT pin responds to a magnetic field exceeding the programmed fault threshold. Self-Test Diagnostic mode can be started at any point after power-up by pulling  $V_{FAULT}$  below  $V_{STTH}$  level (location [1] in Figure 15), causing the sensor IC to enter the Self-Test Start mode and the self-test counter to start. The VOUT pin will continue responding to the magnetic field during this mode, but if the sensor IC is exposed to a magnetic field exceeding the fault threshold, the self-test counter will be reset. After the counter reaches the programmed Self-Test Start Time (t<sub>STS</sub> [2]), the VOUT pin will go to  $V_{STL}$ , indicating that the sensor IC has entered Self-Test Sens mode.

#### Self-Test Sens Mode

Self-Test Sens mode allows the user to verify the sensitivity of the sensor IC. Setting  $V_{\overline{FAULT}} > V_{STTH}$  [4] causes VOUT to respond by going to  $V_{STH}$ , [6]. Setting  $V_{\overline{FAULT}} < V_{STTH}$  [7] causes VOUT to become equal to V<sub>STL</sub> [9]. By measuring VOUT and comparing it to the specified values, the user can detect failures in the Analog Signal path as well as drifts in sensitivity. Quiescent voltage can be measured during the Self-Test Start waiting period as long as no external magnetic fields are present. When the  $V_{\overline{FAULT}}$  value is changed in either direction [4, 7], Self-Test Sens Output Propagation Delay Time (t<sub>STSOPD</sub>) is required before a change is observed on VOUT [5, 8]. VOUT will settle to a stable value after Self-Test Sens Output Rise Time (t<sub>STSORT</sub> [6]) or Self-Test Sens Output Fall Time (t<sub>STSOFT</sub> [9]). The sensor IC can stay in Self-Test Sens mode as long as required by the user. To exit, the  $\overline{FAULT}$  pin should be released, causing  $V_{\overline{FAULT}}$  to exceed V<sub>STTH</sub> [10] and to be pulled near V<sub>CC</sub> by the pull-up resistor. When the programmed Self-Test Fault Request Time (t<sub>STFR</sub>) expires [11], the device will enter Self-Test Fault mode.

#### Self-Test Fault Mode

During Self-Test Fault mode, the FAULT pin should be released by the user. The A1365 will automatically apply an internal positive stimulus to the internal signal path, causing the output to reach  $V_{SAT(HIGH)}$  [12]. After  $V_{OUT}$  crosses the programmed fault threshold, the FAULT pin will be pulled to  $V_{FAULTL}$  [13]. After the programmed Self-Test Fault Pulse Width time ( $t_{STFPW}$ ) has expired [14], the positive internal stimulus will be removed, causing the output to settle at  $V_{OUT(Q)}$  [15], which in turn will cause the FAULT pin to be released and pulled to  $V_{CC}$  [16].

After the Self-Test Fault Pulse Width time ( $t_{STFPW}$ ) has expired [17], a negative internal stimulus will be applied to the signal path, causing the output to reach  $V_{SAT(LOW)}$  [18]. After  $V_{OUT}$  crosses the programmed fault threshold, the FAULT pin will be pulled to GND. After the Self-Test Fault Pulse Width time

$(t_{STFPW})$  has expired [19], the output will be released and should reach  $V_{OUT(Q)}$  in the absence of an external magnetic field [20]. The A1365 will then automatically exit Self-Test mode, release the FAULT pin, and resume normal operation after the Post Self-Test Settling Time ( $t_{STPST}$  [21]). The user can determine if the Over Fault Signal path is functional by ensuring the VOUT pin and the FAULT pin toggle as described in Figure 13 and reach the appropriate voltage levels.

#### Self-Test Operating Conditions

For proper functionality, no magnetic field should be present during any Self-Test mode. If a read/write transaction is received during any Self-Test mode, the sensor IC will exit Self-Test and service the transaction. A Self-Test Start request is ignored during a read/write transaction. If  $V_{\rm CC}$  drops below  $V_{\rm UVLOL}$ , the sensor IC will exit Self-Test mode.

## Table 1: Self-Test Operating Characteristics: Valid through the full operating temperature range T<sub>A</sub>, C<sub>BYPASS</sub> = 0.1 μF, V<sub>CC</sub> = 5 V, and no magnetic field is present, unless otherwise specified

| $V_{CC}$ = 5 V, and no magnetic field      | -                        | -                                                                       |                                |                           |                                |      |

|--------------------------------------------|--------------------------|-------------------------------------------------------------------------|--------------------------------|---------------------------|--------------------------------|------|

| Characteristic                             | Symbol                   | Test Conditions                                                         | Min.                           | Тур.                      | Max.                           | Unit |

| SELF-TEST START MODE                       |                          | · · · · · · · · · · · · · · · · · · ·                                   |                                | · · · · ·                 |                                |      |

| Self-Test Start Time [1]                   | t <sub>sts</sub>         | Programmable                                                            | 0.05                           | -                         | 200                            | ms   |

| Self-Test Threshold Voltage [2]            | V <sub>STTH</sub>        |                                                                         | 0.85                           | 1                         | 1.15                           | V    |

| Self-Test Comparator Hysteresis            | V <sub>STHYST</sub>      |                                                                         | -                              | 75                        | -                              | mV   |

| Self-Test Sens Mode                        |                          |                                                                         |                                |                           |                                |      |

| Self-Test Sens Output Propagation<br>Delay | t <sub>STSOPD</sub>      |                                                                         | -                              | 4                         | _                              | μs   |

| Self-Test Sens Output Rise Time            | t <sub>STSORT</sub>      |                                                                         | _                              | 8                         | _                              | μs   |

| Self-Test Sens Output Fall Time            | t <sub>STSOFT</sub>      |                                                                         | _                              | 8                         | _                              | μs   |

| Self-Test Fault Request Time [1]           | t <sub>STFR</sub>        | Programmable                                                            | 0.05                           | -                         | 10                             | ms   |

| Self-Test High Output Voltage [2]          | V <sub>STH</sub>         |                                                                         | V <sub>OUT(Q)</sub><br>+ 1.275 | V <sub>OUT(Q)</sub> + 1.5 | V <sub>OUT(Q)</sub><br>+ 1.725 | V    |

| Self-Test Low Output Voltage [2]           | V <sub>STL</sub>         |                                                                         | V <sub>OUT(Q)</sub><br>– 1.725 | V <sub>OUT(Q)</sub> – 1.5 | V <sub>OUT(Q)</sub><br>– 1.275 | V    |

| Ratiometry Self-Test Sensitivity           | Rat <sub>ERRSTSens</sub> | $T_A = 25^{\circ}C$ to 150°C relative to $V_{CC} = 5 \text{ V} \pm 5\%$ | -4                             | -                         | 4                              | %    |

| Error                                      |                          | $T_A = -40^{\circ}C$ to 25°C relative to $V_{CC} = 5 \text{ V} \pm 5\%$ | -5                             | -                         | 5                              | %    |