# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### **Brief Description**

The ASI4U is a next-generation CMOS integrated circuit for AS-i networks. This low-level field bus AS-i (Actuator Sensor Interface) was designed for easy, safe, and cost-effective interconnection of sensors, actuators, and switches. It transports both power and data over the same two-wire unshielded cable.

The ASI4U is used as part of a master or slave node and functions as an interface to the physical bus. It provides the power supply, physical data transfer, and communication protocol handling. The ASI4U is fully compliant with the *AS-Interface Complete Specification V3.0.* It is function and pin compatible with the A<sup>2</sup>SI IC.

All configuration data are stored in an internal EEPROM that can be easily programmed by a stationary or handheld programming device. The special AS-i safety option assures short response times for security-related events.

#### Features

- Compliant with AS-Interface Complete Specification V3.0

- Universal application: slaves, masters, repeaters, and bus-monitors

- Floating AS-i transmitter and receiver for highly symmetrical high-power applications

- On-chip electronic inductor with current drive capability of 55 mA

- Two configurable LED outputs to support all AS-Interface Complete Specification V3.0 status indication modes

- Several data pre-processing functions, including configurable data input filters and bit-selective data inverting

- Additional addressing channel for easy wireless

module setup

- Support of 8 and 16 MHz crystals by automatic frequency detection

- Special AS-i safety option

- Clock watchdog for high system security

#### **Related Products**

• SAP5 Universal AS-Interface IC

#### **Benefits**

- Flexible, separated I/O pins

- Flexible AS-i Bus adoption (isolated transceiver)

- Very small package SSOP28 (ASI4U and ASI4U-F)

- High ambient temperature applications (ASI4U-E)

#### **Physical Characteristics**

- ASI4U operational temperature: -25 to +85 °C

- ASI4U-F operational temperature: -40 to +85 °C

- ASI4U-E operational temperature: -25 to +105 °C

- RoHS-conformant package: SSOP28 (ASI4U and ASI4U-F) / SOP28 (ASI4U-E)

#### **Available Support**

- IDT AS-Interface Programmer Kit V2.0

- IDT ASI4U Evaluation Board V2.0

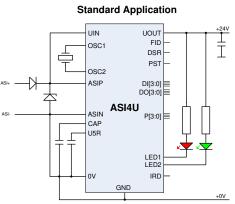

### **ASI4U Basic Application Circuits**

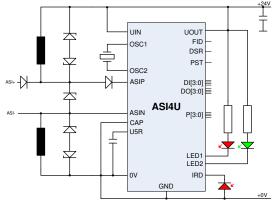

#### Extended Power Application with IR-Addressing Option

#### UIN UOUT U5R OSC1 OSC2 **ASI4U Block Diagram** ELECTRONIC INDUCTOR POWER SUPPLY OUTPUT STAGE OSCILLATOR CAP DO(3:0) DATA-OIL DOWN ASI4U/ASI4U-E/ASI4U-F OWER-15RD INPUT STAGE ž JOUT DI(3:0) ATA-IN P - PULSE RECEIVE I/O STAGE DSR N - PULSE RESE. ASIP DIGITAL REC- RESET LOGIC OUTPUT STAGE PST STR ASIN TRANSMIT SEND-SB INPUT STAGE THERMAL / OVERLOAD PROTECTION OVER PWR\_FAIL Q A C 퇴능 PARAM =AULT OVER-HEA **Typical Applications** P(3:0) CMOS AC INPUT CURREN STAGE INPUT DIG ANA OUTPUT STAGE OUTPUT STAGE INPUT STAGE AS-i Master Modules • AS-i Slave Modules • A<u>GN</u>D L<u>GN</u>D AS-i Safety Modules GND FID ov IRD LED1 LED2

#### **Ordering Information**

| Ordering Code  | Туре     | Package | <b>T</b> <sub>a</sub> [° <b>C</b> ] | RoHS<br>Conform | Packaging                       | Minimum<br>Order |

|----------------|----------|---------|-------------------------------------|-----------------|---------------------------------|------------------|

| ASI4UE-G1-ST   | Standard | SSOP28  | -25 to 85                           | Y               | Tube (47 parts/tube)            | 470              |

| ASI4UE-G1-SR   | Standard | SSOP28  | -25 to 85                           | Y               | Tape & Reel (1500 parts/reel)   | 1500             |

| ASI4UE-G1-SR-7 | Standard | SSOP28  | -25 to 85                           | Y               | Tape & Reel 7" (500 parts/reel) | 500              |

| ASI4UE-G1-MT   | Master   | SSOP28  | -25 to 85                           | Y               | Tube (47 parts/tube)            | 470              |

| ASI4UE-G1-MR   | Master   | SSOP28  | -25 to 85                           | Y               | Tape & Reel (1500 parts/reel)   | 1500             |

| ASI4UE-E-G1-ST | Standard | SOP28   | -25 to 105                          | Y               | Tube (27 parts/tube)            | 270              |

| ASI4UE-E-G1-SR | Standard | SOP28   | -25 to 105                          | Y               | Tape & Reel (1000 parts/reel)   | 1000             |

| ASI4UE-F-G1-ST | Standard | SSOP28  | -40 to 85                           | Y               | Tube (47 parts/tube)            | 470              |

| ASI4UE-F-G1-SR | Standard | SSOP28  | -40 to 85                           | Y               | Tape & Reel (1500 parts/reel)   | 1500             |

Corporate Headquarters 6024 Silver Creek Valley Road San Jose, CA 95138 www.IDT.com Sales 1-800-345-7015 or 408-284-8200 Fax: 408-284-2775

www.IDT.com/go/sales

#### **Tech Support**

www.IDT.com/go/support

DISCLAIMER Integrated Device Technology, Inc. (IDT) reserves the right to modify the products and/or specifications described herein at any time, without notice, at IDT's sole discretion. Performance specifications and operating parameters of the described products are determined in an independent state and are not guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied, including, but not limited to, the suitability of IDT's products for any particular purpose, an implied warranty of merchantability, or non-infringement of the intellectual property rights of others. This document is presented only as a guide and does not convey any license under intellectual property rights of IDT or any third parties.

IDT's products are not intended for use in applications involving extreme environmental conditions or in life support systems or similar devices where the failure or malfunction of an IDT product can be reasonably expected to significantly affect the health or safety of users. Anyone using an IDT product in such a manner does so at their own risk, absent an express, written agreement by IDT.

Integrated Device Technology, IDT and the IDT logo are trademarks or registered trademarks of IDT and its subsidiaries in the United States and other countries. Other trademarks used herein are the property of IDT or their respective third party owners. For datasheet type definitions and a glossary of common terms, visit <u>www.idt.com/go/glossary</u>. All contents of this document are copyright of Integrated Device Technology, Inc. All rights reserved.

### Contents

| 1 | Imp  | ortai  | nt Safety Advice                                         | . 7 |

|---|------|--------|----------------------------------------------------------|-----|

|   | 1.1. | AS-    | i-Safety Applications                                    | . 7 |

|   | 1.2. | Rep    | air of ASI-Safety Modules                                | . 7 |

| 2 | Ger  | neral  | Device Specifications                                    | . 8 |

|   | 2.1. | Abs    | olute Maximum Ratings (Non-Operating)                    | . 8 |

|   | 2.2. | Ope    | erating Conditions                                       | 10  |

|   | 2.3. | Qua    | ility Standards                                          | 10  |

| 3 | Bas  | sic Fu | Inctional Description 1                                  | 11  |

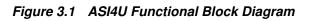

|   | 3.1. | Fun    | ctional Block Diagram                                    | 11  |

|   | 3.2. |        | neral Operational Modes                                  |     |

|   | 3.3. |        | /e Mode1                                                 |     |

|   | 3.3. | 1.     | AS-Interface Communication Channel                       | 14  |

|   | 3.3. |        | IRD Communication Channel                                |     |

|   | 3.3. |        | Parameter Port Pins                                      |     |

|   | 3.3. | 4.     | Data Port Pins                                           | 16  |

|   | 3.3. | 5.     | Data Input Inversion                                     | 16  |

|   | 3.3. |        | Data Input Filtering                                     |     |

|   | 3.3. |        | Fixed-Data Output Driving                                |     |

|   | 3.3. |        | Synchronous Data I/O Mode                                |     |

|   | 3.3. |        | 4 Input / 4 Output Processing in Extended Address Mode 1 |     |

|   |      |        | AS-i Safety Mode                                         |     |

|   |      |        | Enhanced LED Status Indication                           |     |

|   |      |        | Communication Monitor/Watchdog                           |     |

|   |      |        | Write Protection of ID_Code_Extension_1                  |     |

|   | 3.3. |        | Summary of Master Calls                                  |     |

|   | 3.4. |        | ster Mode                                                |     |

|   |      |        | 2 PROM                                                   |     |

| 4 |      |        | Functional Description2                                  |     |

|   |      |        | i Receiver                                               |     |

|   |      |        | i Transmitter                                            |     |

|   | 4.3. |        | ressing Channel Input IRD                                |     |

|   | 4.3. |        | General Slave Mode Functionality                         |     |

|   | 4.3. |        | AC Current Input Mode2                                   |     |

|   | 4.3. |        | CMOS Input Mode                                          |     |

|   | 4.3. |        | Master, Repeater, and Monitor Modes                      |     |

|   | 4.4. | •      | tal Inputs – DC Characteristics                          |     |

|   | 4.5. | Digi   | tal Outputs - DC Characteristics                         | 30  |

### () IDT.

| 4.6. Parameter Port and PST Pin                                              | 31 |

|------------------------------------------------------------------------------|----|

| 4.6.1. Slave Mode                                                            | -  |

| 4.6.2. Parameter Multiplex Mode                                              |    |

| 4.6.3. Special Function of P0, P1 and P2                                     |    |

| 4.6.4. Master, Repeater, and Monitor Modes                                   |    |

| 4.7. Data Port and DSR Pin                                                   |    |

| 4.7.1. Slave Mode                                                            |    |

| 4.7.2. Input Data Pre-processing                                             |    |

| 4.7.3. Fixed Output Data Driving                                             |    |

| 4.7.4. Synchronous Data I/O Mode                                             |    |

| 4.7.5. Support of 4I/4O Processing in Extended Address Mode, Profile 7.A.x.E |    |

| 4.7.6. Safety Mode Operation                                                 |    |

| 4.7.7. Master, Repeater, and Monitor Modes                                   |    |

| 4.7.8. Special Function of DSR                                               |    |

| 4.8. Fault Indication Input Pin FID                                          |    |

| 4.8.1. Slave Mode                                                            |    |

| 4.8.2. Master and Monitor Modes                                              |    |

| 4.9. LED Outputs                                                             |    |

| 4.9.1. Slave Mode                                                            |    |

| 4.9.2. Communication via Addressing Channel                                  |    |

| 4.9.3. Master, Repeater, and Monitor Modes                                   |    |

| 4.10. Oscillator Pins OSC1, OSC2                                             |    |

| 4.11. IC Reset                                                               |    |

| 4.11.1. Power-On Reset                                                       |    |

| 4.11.2. Logic Controlled Reset                                               | 51 |

| 4.11.3. External Reset                                                       | 51 |

| 4.12. UART                                                                   |    |

| 4.12.1. AS-i Input Channel                                                   |    |

| 4.12.2. Addressing Channel                                                   |    |

| 4.13. Main State Machine                                                     |    |

| 4.14. Status Registers                                                       |    |

| 4.15. Communication Monitor/Watchdog                                         |    |

| 4.16. Toggle Watchdog for 4I/4O Processing in Extended Address Mode          |    |

| 4.17. Write Protection of ID_Code_Extension_1                                |    |

| 4.18. Power Supply                                                           |    |

| 4.18.1. Voltage Output Pins UOUT and U5R                                     |    |

| 4.18.2. Input Impedance (AS-Interface Bus Load)                              |    |

| 4.19. Thermal and Overload Protection                                        |    |

|                                                                              |    |

### () IDT.

| Ар                                        | plication Circuits                                   | 60                                                                                                                                                                                                                                                                                                                                      |

|-------------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pa                                        | ckage Specifications                                 | . 64                                                                                                                                                                                                                                                                                                                                    |

| 5.1.                                      | Package Pin Assignment                               | 64                                                                                                                                                                                                                                                                                                                                      |

| 5.2.                                      | SOP28 Package Outline for ASI4U-E                    | 66                                                                                                                                                                                                                                                                                                                                      |

| 5.3.                                      | SSOP28 Package Outline for ASI4U and ASI4U-F         | . 67                                                                                                                                                                                                                                                                                                                                    |

| 5.4.                                      | Package Marking                                      | . 68                                                                                                                                                                                                                                                                                                                                    |

| Or                                        | dering Information                                   | . 69                                                                                                                                                                                                                                                                                                                                    |

| Re                                        | elated Documents                                     | 69                                                                                                                                                                                                                                                                                                                                      |

| Gl                                        | ossary                                               | 70                                                                                                                                                                                                                                                                                                                                      |

| <ul> <li>Package Specifications</li></ul> |                                                      |                                                                                                                                                                                                                                                                                                                                         |

|                                           | Pa<br>5.1.<br>5.2.<br>5.3.<br>6.4.<br>Or<br>Re<br>Gl | Application Circuits         Package Specifications         6.1. Package Pin Assignment         6.2. SOP28 Package Outline for ASI4U-E         6.3. SSOP28 Package Outline for ASI4U and ASI4U-F         6.4. Package Marking         Ordering Information         Related Documents         Glossary         Document Revision History |

### List of Figures

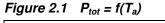

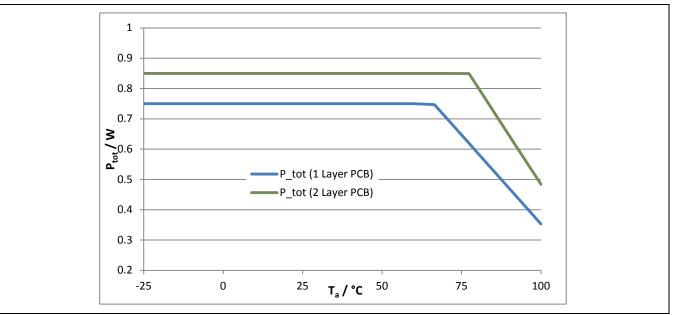

| Figure 2.1  | $P_{tot} = f(T_a)$                                                         | 9  |

|-------------|----------------------------------------------------------------------------|----|

| Figure 3.1  | ASI4U Functional Block Diagram                                             |    |

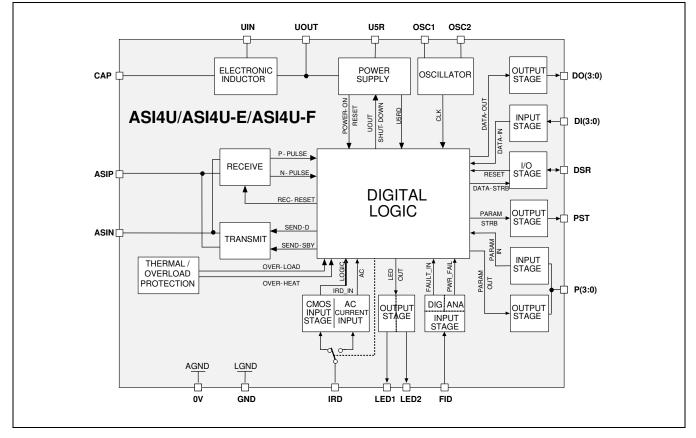

| Figure 3.2  | Conventional Application for AS-i IC with One External Coil                | 15 |

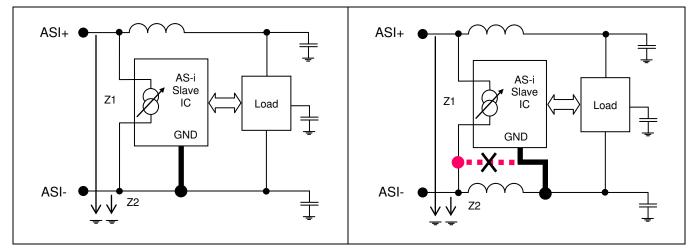

| Figure 3.3  | Application for AS-i IC with Two External Coils                            |    |

| Figure 3.4  | Data Path in the Master, Repeater, and Monitor Modes                       | 21 |

| Figure 4.1  | Simplified Receiver Comparator Threshold Setup                             | 25 |

| Figure 4.2  | Addressing Channel Input (IRD), Photo-Current Waveforms                    | 28 |

| Figure 4.3  | Timing Diagram Parameter Ports P[3:0] and PST                              | 32 |

| Figure 4.4  | Timing Diagram Data Ports DO[3:0], DI[3:0] and DSR                         | 35 |

| Figure 4.5  | Input Path at Data Port                                                    |    |

| Figure 4.6  | Principles of Input Filtering                                              | 36 |

| Figure 4.7  | Principle of AS-i Cycle Input Filtering (Example for Slave with Address 1) | 37 |

| Figure 4.8  | Flowchart – Input DI3, DI2, and DI1 in Safety Mode                         | 43 |

| Figure 4.9  | Flowchart – Input DI0 in Safety Mode                                       |    |

| Figure 4.10 | Flowchart – Data_Exchange_Disable                                          | 45 |

| Figure 4.11 | Power-On Behavior (All Modes)                                              | 50 |

| Figure 4.12 | Timing Diagram External Reset via DSR                                      | 51 |

| Figure 4.13 | Manchester-II-Coded Modulation Principle                                   | 54 |

| Figure 5.1  | Standard Application Circuit with Bi-directional Data I/O                  | 61 |

| Figure 5.2  | Extended Power Application Circuit with IR-Addressing Option               | 62 |

| Figure 5.3  | ASI4U Master/Repeater Mode Application                                     | 63 |

| Figure 6.1  | ASI4U Package Pin Assignment                                               | 65 |

| Figure 6.2  | SOP28 Package Outline Dimensions                                           | 66 |

| Figure 6.3  | SSOP28 Package Outline Dimensions                                          | 67 |

| Figure 6.4  | Package Marking                                                            | 68 |

### List of Tables

| Table 2.1  | Absolute Maximum Ratings                                              | 8  |

|------------|-----------------------------------------------------------------------|----|

| Table 2.2  | Operating Conditions                                                  | 10 |

| Table 2.3  | Crystal Frequency                                                     | 10 |

| Table 3.1  | Assignment of Operational Modes                                       | 14 |

| Table 3.2  | ASI4U Master Calls and Related Slave Responses                        | 19 |

| Table 3.3  | Signal Assignments for Data I/O and Parameter Port Pins               | 21 |

| Table 3.4  | EEPROM Contents                                                       | 22 |

| Table 4.1  | Receiver Parameters                                                   | 25 |

| Table 4.2  | Transmitter Current Amplitude                                         |    |

| Table 4.3  | IRD AC Current Input Parameters                                       |    |

| Table 4.4  | IRD Current/Voltage Mode Switching                                    | 29 |

| Table 4.5  | IRD CMOS Input Mode Levels                                            | 29 |

| Table 4.6  | Polarity of Manchester-II Signal at IRD in Master Mode                | 29 |

| Table 4.7  | DC Characteristics of Digital High Voltage Input Pins                 | 30 |

| Table 4.8  | DC Characteristics of Digital High Voltage Output Pins                |    |

| Table 4.9  | Timing Parameter Port                                                 |    |

| Table 4.10 | Parameter Port Output Signals in Master, Repeater, and Monitor Modes  |    |

| Table 4.11 | Timing Data Port Outputs                                              | 34 |

| Table 4.12 | Data Input Filter Time Constants                                      |    |

| Table 4.13 | Input Filter Activation by Parameter Port Pin P1                      | 37 |

| Table 4.14 | EEPROM Configuration for Different Input Modes                        |    |

| Table 4.15 | Activation States of Synchronous Data IO Mode                         |    |

| Table 4.16 | Meaning of Master Call Bits I0, I1, I2, and I3 in Ext_Addr_4I/4O_Mode | 41 |

| Table 4.17 | Control Signal Inputs in the Master, Repeater, and Monitor Modes      | 45 |

| Table 4.18 | Error Signal Outputs in Monitor Mode                                  | 45 |

| Table 4.19 | Power Failure Detection at FID (Master Mode and Monitor Mode)         |    |

| Table 4.20 | LED Status Indication                                                 |    |

| Table 4.21 | Polarity of Manchester-II Signal at LED1                              |    |

| Table 4.22 | Oscillator Pin Parameters                                             |    |

| Table 4.23 | IC Initialization Times                                               | 50 |

| Table 4.24 | Power-On Reset Threshold Voltages                                     | 50 |

| Table 4.25 | Timing of External Reset                                              | 51 |

| Table 4.26 | Status Register Content                                               |    |

| Table 4.27 | Properties of Voltage Output Pins UOUT and U5R                        | 59 |

| Table 4.28 | AS-Interface Bus Load Properties                                      | 59 |

| Table 4.29 | CAP Pin Parameters                                                    | 60 |

| Table 4.30 | Shutdown Temperature                                                  |    |

| Table 6.1  | ASI4U Package Pin List                                                | 64 |

| Table 6.2  | SOP28 Package Dimensions (mm)                                         | 66 |

| Table 6.3  | SSOP28 Package Dimensions (mm)                                        | 67 |

### 1 Important Safety Advice

**Important Safety Notice:** This IDT product is intended for use in commercial applications. Applications requiring extended temperature range, unusual environmental requirements, or high-reliability applications, such as military, medical life-support, or life-sustaining equipment, are specifically not recommended without additional mutually agreed upon processing by IDT for such applications.

#### 1.1. AS-i-Safety Applications

The ASI4U/ASI4U-E/ASI4U-F is designed to allow replacement of IDT's A<sup>2</sup>SI ICs in existing board layouts and applications (also see section 1.2 for important restrictions). However, since the ASI4U/ASI4U-E/ASI4U-F provides additional data preprocessing functions at the data input channel, the fault reaction time of an AS-i Safety module could increase by 40ms if some of the new features become activated by intention, by accident, or hardware fault.

IDT strongly recommends the use of the Safety Mode feature of the ASI4U/ASI4U-E/ASI4U-F if it is replacing the A<sup>2</sup>SI in existing ASI-Safety designs. The same fault reaction times as with the A<sup>2</sup>SI are guaranteed only in this Safety Mode. For compatibility with the modified data input routing in Safety Mode, the user must adapt the safety code table stored in the external microcontroller. Only safety code sequences that contain the value **1110** are permitted.

If the IC is operated in Safety Mode, the user must ensure that the Synchronous Data I/O Mode as well as the data input filters remain disabled by appropriate EEPROM configuration.

Application of the ASI4U/ASI4U-E/ASI4U-F in Standard Mode (no Safety Mode enabled) for AS-i Safety products is possible if an additional fault reaction time of 40ms is taken into account.

The user must also adhere to the additional security advice provided in *Production and Repair of AS-i Safety Slaves*, which is available on the IDT web page <u>www.IDT.com</u> (see section 8).

#### 1.2. Repair of ASI-Safety Modules

**Important:** If an A<sup>2</sup>SI-based ASI-Safety module must be repaired, replacing the A<sup>2</sup>SI IC with the newer ASI4U/ASI4U-E/ASI4U-F is **explicitly prohibited**. This is to prevent safety-relevant deviations of module properties that can result from the different data input paths and the possible increase in fault reaction time discussed in section 1.1.

The user must also adhere to the additional security advice provided in *Production and Repair of AS-i Safety Slaves*, which is available on the IDT web page www.IDT.com.

### 2 General Device Specifications

Important: Stresses beyond those listed under "Absolute Maximum Ratings" (section 2.1) may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" are not implied. Exposure to conditions rated as the absolute maximum for extended periods might affect device reliability.

#### 2.1. Absolute Maximum Ratings (Non-Operating)

| Parameter                                                                                                                 | Symbol                      | Conditions                                                                      | Min  | Мах                     | Unit |

|---------------------------------------------------------------------------------------------------------------------------|-----------------------------|---------------------------------------------------------------------------------|------|-------------------------|------|

| Voltage reference                                                                                                         | $V_{0V}, V_{GND}$           |                                                                                 | 0    | 0                       | V    |

| Voltage difference between ASIP and ASIN $(V_{ASIP} - V_{ASIN})^{1)}$                                                     | VASIP-ASIN                  |                                                                                 | -0.3 | 40                      | V    |

| Pulse voltage<br>between ASIP and ASIN<br>(V <sub>ASIP</sub> - V <sub>ASIN</sub> )                                        | Vasip-asin_p                | Pulse width $\le 50\mu s$<br>Repetition rate $\le 0.5Hz$                        | -0.3 | 50                      | V    |

| Pulse voltage between ASIP and 0V $\left(V_{\text{ASIP}} - V_{0V}\right)^{2)}$                                            | VASIP                       | Pulse width $\le 50\mu s$<br>Repetition rate $\le 0.5Hz$                        | -0.3 | 50                      | V    |

| Voltage between ASIN and 0V $\left(V_{ASIN}-V_{0V}\right)^{2)}$                                                           | VASIN                       |                                                                                 | -6.0 | 6.0                     | V    |

| Power supply input voltage                                                                                                | V <sub>UIN</sub>            |                                                                                 | -0.3 | 40                      | V    |

| Pulse voltage at power supply input                                                                                       | $V_{\text{UIN}_{\text{P}}}$ | Pulse width $\le$ 50 $\mu$ s<br>Repetition rate $\le$ 0.5Hz                     | -0.3 | 50                      | V    |

| Voltage at DI3, DI2, DI1, DI0,<br>DO3, DO2, DO1, DO0, P3, P2,<br>P1, P0, DSR, PST, LED1,<br>LED2, FID, IRD, and UOUT pins | Vinputs1                    |                                                                                 | -0.3 | V <sub>UOUT</sub> + 0.3 | V    |

| Voltage at OSC1, OSC2, CAP, and U5R pins                                                                                  | V <sub>inputs2</sub>        |                                                                                 | -0.3 | 7                       | V    |

| Input current into any pin except supply pins                                                                             | l <sub>in</sub>             | Latch-up resistance, reference to pin 0V                                        | -50  | 50                      | mA   |

| Humidity – non-condensing                                                                                                 | Н                           | Level 4 according to<br>JEDEC-020D standard                                     |      |                         |      |

| Electrostatic discharge –<br>Human Body Model (HBM1)                                                                      | V <sub>HBM1</sub>           | C = 100pF charged to V <sub>HBM1</sub> with resistor R = $1.5k\Omega$ in series | 3500 |                         | V    |

| Electrostatic discharge –<br>Human Body Model (HBM2)                                                                      | V <sub>HBM2</sub>           | $C$ = 100pF charged to $V_{HBM2}$ with resistor $R$ = 1.5k $\Omega$ in series   | 2000 |                         | V    |

#### Table 2.1Absolute Maximum Ratings

| Parameter                                                       | Symbol            | Conditions                                                                            | Min | Мах  | Unit |

|-----------------------------------------------------------------|-------------------|---------------------------------------------------------------------------------------|-----|------|------|

| Electrostatic discharge –<br>Equipment Discharge Model<br>(EDM) | V <sub>EDM</sub>  | C = 200pF charged to $V_{EDM}$ with no resistor in series                             | 400 |      | V    |

| Storage temperature                                             | T <sub>STG</sub>  |                                                                                       | -55 | 125  | °C   |

| Soldering temperature Sn/Pb                                     | T <sub>Lead</sub> | JEDEC-J-STD-020D                                                                      |     | 240  | °C   |

| Soldering temperature 100%Sn                                    | $T_{Lead}$        | JEDEC-J-STD-020D                                                                      |     | 260  | °C   |

| Total power dissipation <sup>6)</sup>                           | P <sub>tot</sub>  |                                                                                       |     | 0.85 | W    |

| Thermal resistance of SSOP 28<br>package<br>(ASI4U and ASI4U-F) | _                 | Single layer board<br>P <sub>tot</sub> = 0.5W<br>Air velocity = 0m/s at               | 40  | 80   | K/W  |

| Thermal resistance of SOP 28<br>package<br>(ASI4U-E)            | R <sub>thj</sub>  | Air velocity = 011/s at<br>maximum value<br>Air velocity = 2.5m/s at<br>minimum value | 60  | 80   | K/W  |

1) Reverse polarity protection must be performed externally.

2) VASIP-ASIN and VASIP-ASIN\_P must not be exceeded.

3) Valid for ASIP-ASIN only.

4) Valid for all pins except ASIP-ASIN.

5) Valid for ASIP-ASIN only.

At the maximum operating temperature, the maximum total power dissipation allowed depends on additional the thermal 6) resistance from the package to the ambient air and on the operational ambient temperature as shown in Figure 2.1

#### 2.2. Operating Conditions

#### Table 2.2Operating Conditions

| PARAMETER                                                       | SYMBOL            | CONDITIONS                                                                                                                              | MIN | MAX. | UNIT |

|-----------------------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|

| Positive supply voltage for IC operation <sup>1)</sup>          | V <sub>UIN</sub>  | DC parameter:<br>V <sub>UINmin</sub> = V <sub>UOUTmin</sub> + V <sub>DROPmax</sub>                                                      | 16  | 33.1 | V    |

|                                                                 |                   | $V_{UINmax} = V_{UOUTmax} + V_{DROPmin}$                                                                                                |     |      |      |

| Negative supply voltage                                         | $V_{0V},V_{GND}$  |                                                                                                                                         | 0   | 0    | V    |

| DC voltage at ASIP <sup>2)</sup>                                | VASIP             | Relative to $V_{0V}$                                                                                                                    | 16  | 33.1 | V    |

| DC voltage at ASIN <sup>2)</sup>                                | V <sub>ASIN</sub> | Relative to V <sub>0V</sub>                                                                                                             | -4  | 4    | V    |

| Operating current                                               | I <sub>UIN</sub>  | $V_{UIN} = 30V$<br>f <sub>c</sub> = 8.000 MHz; no load at any<br>pin; transmitter turned off; digital<br>State Machine is in idle state |     | 6    | mA   |

| Maximum output sink current at DO0, DO1, DO2, DO3, and DSR pins | I <sub>CL1</sub>  |                                                                                                                                         |     | 10   | mA   |

| Maximum output sink current at P0, P1, P2, P3, and PST pins     | I <sub>CL2</sub>  |                                                                                                                                         |     | 10   | mA   |

| Ambient temperature range, operating range                      | Ta                | ASI4U                                                                                                                                   | -25 | 85   | °C   |

|                                                                 |                   | ASI4U-E                                                                                                                                 | -25 | 105  | °C   |

|                                                                 |                   | ASI4U-F                                                                                                                                 | -40 | 85   | °C   |

2) Outside the maximum and minimum limits, the send current shape and send current amplitude cannot be guaranteed.

#### Table 2.3Crystal Frequency

| PARAMETER                                                                                                                                                                                                                                                                                               | SYMBOL                             | CONDITIONS                                                                | NOMINAL             | UNIT  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|---------------------------------------------------------------------------|---------------------|-------|

| Crystal frequency 1)                                                                                                                                                                                                                                                                                    | f <sub>c</sub>                     |                                                                           | 8.000/16.000        | MHz   |

| <ol> <li>The IC automatically detects whether the crystal freq<br/>accordingly. The frequency detection is locked as so<br/>It can be reset by a power-on reset only.</li> <li>Note: In Slave Mode, the locking occurs if a Master of<br/>Call or a Slave Response that has been received on</li> </ol> | on as one AS-i<br>Call has been re | telegram has been correctly receiv<br>eceived. In the Master, Repeater, o | ed at any input cha | nnel. |

The ASI4U/ASI4U-E/ASI4U-F supports an integrated clock watchdog. If no crystal or clock oscillation is recognized for 150µs, the IC generates a RESET event until clock oscillation is available. More detailed oscillator pin definitions can be found in section 4.10.

### 2.3. Quality Standards

The quality of the ASI4U/ASI4U-E/ASI4U-F is ensured according to the IDT quality standards. Functional device parameters are valid for device operating conditions specified in section 2.2. Unless otherwise stated, production device tests are performed at  $T_a = +25^{\circ}$ C within the recommended ranges of (V<sub>ASIP</sub> - V<sub>ASIN</sub>) and (V<sub>IN</sub> - V<sub>0V</sub>). Additional sample base testing is done at +85°C and -25°C (-40°C for the ASI4U-F).

### 3 Basic Functional Description

#### 3.1. Functional Block Diagram

Following device functions are associated with the different blocks of the IC:

**RECEIVE** The RECEIVE block converts the analog telegram waveform from the AS-i bus to a digital pulsecoded signal that can be processed further by a digital UART circuit.

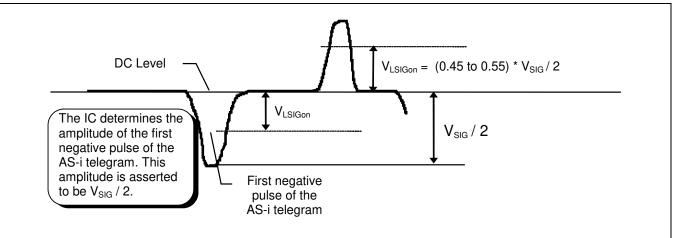

The RECEIVE block is directly connected to the ASIP and ASIN pins, which connect to the AS-i line. It converts the differential AS-i telegram to a single-ended signal and removes the DC offset by high-pass filtering. To adapt quickly to changing signal amplitudes in telegrams from different network users, the amplitude of the first telegram pulse is measured by a 3-bit flash ADC and the threshold of a positive and a negative comparator is set accordingly to about 50% of the measured level. The comparators generate the P-pulse and N-pulse signals.

- **TRANSMIT** The TRANSMIT block transforms a digital response signal to a correctly shaped send current signal that is applied to the AS-i bus. Due to the inductive network behavior of the network, the changing send current induces voltage pulses on the network line that overlay the DC operating voltage. The voltage pulses must have sin<sup>2</sup>-wave shapes; therefore the send current shape must follow the integral of the sin<sup>2</sup>-wave function.

- **DIGITAL LOGIC** The DIGITAL LOGIC block contains the UART, Main State Machine, EEPROM memory and other control logic. EEPROM write access and other I/O operations of the Main State Machine are supported in Slave Mode only (see description of general IC operational modes below). In Master Mode, the IC is basically equivalent to a physical layer transceiver.

If Slave Mode is activated, the UART demodulates the received telegrams, verifies telegram syntax and timing, and controls a register interface to the Main State Machine. After reception of a correct telegram, the UART generates appropriate Receive Strobe signals that tell the Main State Machine to start further processing. The Main State Machine decodes the telegram information and starts respective I/O processes or EEPROM access. A second register interface is used to send data back to the UART for construction of a telegram response. The UART modulates the response data into a Manchester-II-coded bit stream that is used to control the TRANSMIT unit.

**ELECTRONIC INDUCTOR** The ELECTRONIC INDUCTOR block is basically a gyrator circuit. It provides an inductive behavior between the IC's UIN and UOUT pins while the inductance is controlled by the capacitor on the CAP pin. The inductor decouples the power regulator of the IC as well as the external load circuit from the AS-i bus, and this prevents cross talk or switching noise from disturbing the telegram communication on the bus.

The AS-Interface Complete Specification V3.0 describes the input impedance behavior of a slave module by an equivalent circuit that consists of a resistance (R), an inductance (L), and a capacitance (C) in parallel. For example, a slave module in Extended Address Mode must have  $R > 13.5k\Omega$ , L > 13.5mH and C < 50pF. The electronic inductor of the ASI4U/ASI4U-E/ASI4U-F delivers values that are well within the required ranges for output currents up to 55mA. More detailed parameters can be found in section 4.18.2.

The electronic inductor requires an external capacitor of at least  $10\mu\text{F}$  at the UOUT pin for stability.

- **POWER SUPPLY** The POWER SUPPLY block consists of a bandgap-referenced 5V regulator and other reverence voltage and bias current generators for internal use. The 5V regulator requires an external capacitor at pin U5R of at least 1µF for stability. It can source up to 4mA for external use; however, the power dissipation and the resulting device heating become a major concern if too much current is drawn from the regulator.

- **OSCILLATOR** The OSCILLATOR block supports direct connection to 8.000 MHz or 16.000 MHz crystals with a dedicated load capacity of 12pF and parasitic pin capacities of up to 8pF. The IC automatically detects the oscillation frequency of the connected crystal and controls the internal clock generator circuit accordingly.

<sup>© 2016</sup> Integrated Device Technology, Inc.

After power-on reset, the IC is set to 16.000 MHz operation by default. After approximately  $200\mu s$ , it will either switch to 8.000 MHz operation or remain in the 16.000 MHz mode. The frequency detection is active until the first AS-i telegram has been successfully received in order to ensure that the IC has found the correct clock frequency setting. The detection result is locked thereafter to increase resistance against burst or other interferences.

The oscillator unit also contains a clock watchdog circuit that can generate an unconditional IC reset if there has been no clock oscillation for more than approximately  $20\mu s$ . This is to prevent the IC from unpredictable behavior if a clock signal is no longer available.

**THERMAL/OVERLOAD PROTECTION** The IC is self-protected against overheating and short-circuiting of the UOUT pin toward IC ground.

If the silicon die temperature rises above approximately 140°C for more than 2 seconds, the IC detects overheating, switches off the electronic inductor, performs an IC reset, and sets all analog blocks to power down mode. Although the 5V regulator is turned off in this state, there will still remain a voltage of approximately 3V to 3.5V available at U5R that is derived from the internal start circuitry. The overheating protection state can only be de-activated by power-cycling the AS-i voltage.

Short-circuiting the UOUT pin toward IC ground causes the same IC behavior as overheating.

- **IRD CMOS** / **AC CURRENT INPUT** The IRD pin is the input for the additional addressing channel in Slave Mode (see section 3.2 for a description of general IC operational modes) or the direct AS-i transmitter input in Master Mode. In Slave Mode, the IRD pin can be operated either in CMOS Mode or AC Current Input Mode. The latter is provided for direct connection of a photodiode. More detailed information can be found in section 4.3.

- **FID DIGITAL** / **ANALOG STAGE** The FID pin can be set to the Digital CMOS Mode or Analog Voltage Input Mode. In Slave Mode, it is set to CMOS operation; in Master Mode, it works in Analog Mode and functions as the input for the power fail comparator.

- **INPUT STAGE** All digital inputs, except the oscillator pins, have high voltage capabilities and partial Schmitt trigger and pull-up features. For more details, see section 4.4.

- **OUTPUT STAGE** All digital output stages, except for the oscillator pins, have high voltage capabilities and are implemented as NMOS open-drain buffers. Each pin can sink up to 10mA of current.

#### 3.2. General Operational Modes

The ASI4U/ ASI4U-E/ASI4U-F provides two main operational modes and two additional sub-operational modes. The two main operation modes are Slave Mode and Master Mode. Sub-operation modes are Repeater Mode and Monitor Mode. The latter were derived from Master Mode for providing different output signals at the Parameter Port.

The active operational mode is selected by programming the *Master\_Mode* and *Repeater\_Mode* flags in the "Firmware Area" block of the EEPROM (also see Table 3.4). The EEPROM is read at every initialization of the IC. Online mode switching is not provided. Table 3.1 gives the bit configurations for the operational modes.

<sup>© 2016</sup> Integrated Device Technology, Inc.

| SELECTED OPERATIONAL MODE | MASTER MODE FLAG | REPEATER MODE FLAG |

|---------------------------|------------------|--------------------|

| Slave Mode                | 0                | 0                  |

| Master Mode               | 1                | 0                  |

| Repeater Mode             | 1                | 1                  |

| Monitor Mode              | 0                | 1                  |

#### Table 3.1 Assignment of Operational Modes

In Slave Mode, the IC operates as a full-feature AS-i slave IC according to the AS-Interface Complete Specification V3.0.

In Master Mode, the IC translates a digital output signal from the master control logic (e.g., a programmable logic controller or microcontroller) to a correctly shaped, analog AS-i pulse sequence and vice versa. Every AS-i telegram received is checked for consistency with the AS-Interface communication protocol specifications, and if no errors were found, an appropriate Receive Strobe signal is generated.

Master Mode and Monitor Mode differ in the kind of telegrams signaled. In Master Mode, a single Receive Strobe signal is provided validating every correctly received Slave Response; in Monitor Mode, two different Receive Strobe signals are available indicating every correctly received Master and Slave telegram separately. The Monitor Mode is intended for use in intelligent slaves and bus monitors that provide their own telegram decoding mechanisms but do not check for correct telegram timing or syntax.

The Repeater Mode is specifically provided for AS-i bus repeater applications.

#### 3.3. Slave Mode

The Slave Mode is the most complex operational mode of the IC. The IC supports all mandatory AS-i Slave functions and also a variety of additional features that make AS-i slave module design very easy and flexible.

#### 3.3.1. AS-Interface Communication Channel

In Slave Mode, the ASI4U can work on two different communication channels: the AS-i channel and the IRD channel. The AS-i channel is directly connected to the AS-i bus via the ASIP and ASIN pins. A receiver and a transmitter unit are connected in parallel to the pins. This allows fully bi-directional communication through ASIP and ASIN.

The ASI4U/ASI4U-E/ASI4U-F is the first IC that supports floating operation of the AS-i receiver and transmitter (within specified limits) relative to IC ground. Previously, the ASIN pin always had to be on the same potential as the IC ground (see Figure 3.2 for an example), preventing full symmetrical input circuits with external coils. Figure 3.3 illustrates the new enhanced functionality. The relation Z1/Z2 is a measure of the symmetry of the AS-i module input relative to machine ground. The application in Figure 3.3 is more symmetrical since Z1 and Z2 are more equal than in the conventional solution. Note: This is not a complete application circuit.

Figure 3.2 Conventional Application for AS-i IC with One External Coil

Figure 3.3 Application for AS-i IC with Two External Coils

#### 3.3.2. IRD Communication Channel

In addition to the AS-Interface communication channel, the ASI4U can also operate on a second input channel: the IRD Input Channel or Addressing Channel. In this mode, the IRD pin is the input for an AS-i signal in Manchester-II-coded format. The signal can be either an AC-current signal generated by a photodiode or a 5V-CMOS signal. The IC automatically detects the type of the signal and switches the input path accordingly.

The output pin in IRD Communication Mode is LED1. It transmits the slave response as an inverted Manchester-II-coded AS-i signal. A red LED connected to LED1 can form the response transmitter in an optical communication system, or LED1 can be directly connected to external circuitry.

Activation of the IRD communication channel is achieved by a transmission referred to as a "Magic Sequence" that is sent in advance of the desired communication. The construction of a Magic Sequence is described in detail in section 4.3. The IRD communication mode is deactivated by an IC reset, except in a special case described in section 4.3.

#### 3.3.3. Parameter Port Pins

The ASI4U features a 4-bit-wide parameter port and a related parameter strobe signal on the PST pin. There is a defined phase relation between a parameter output event, the parameter input sampling, and the activation of the PST signal, so it can be used to trigger external logic or a microcontroller to process the received parameter data or to provide new input data for the AS-i slave response.

Version 3.0 of the *AS-Interface Complete Specification* defines a bidirectional mode for parameter data. The ASI4U/ASI4U-E/ASI4U-F supports this feature, which can be activated by special EEPROM setting.

See section 4.6 for further details.

#### 3.3.4. Data Port Pins

An important feature of the ASI4U/ASI4U-E/ASI4U-F is the 8-bit wide data port that consists of a 4-bit-wide input section and a 4-bit-wide output section. The input and output sections work independently from each other allowing a maximum of 8 devices (4 input and 4 output devices) to be connected to the ASI4U/ASI4U-E/ASI4U-F. For special applications (compatibility), the Multiplex Mode can be activated, which limits the output activation to a specific time frame. With this feature, a 4-bit wide bi-directional data I/O port can be achieved by external connection of the corresponding data input and output pins.

The data port is accompanied by the data strobe signal on the DSR pin. There is a defined phase relation between a data output event, the input data sampling, and the activation of the DSR signal, so it can be used to trigger external logic or a microcontroller to process the received data or to provide new input data for the AS-i slave response. See section 4.7 for further details.

#### 3.3.5. Data Input Inversion

By default, the logic signal (HIGH/LOW) that is present at the data input pins during the input sampling phase is transferred without modification to the send register, which is interfaced by the UART so that the signal directly becomes part of the slave response.

Some applications function with inverted logic levels. To avoid additional external inverters, the input signal can be inverted by the ASI4U/ASI4U-E/ASI4U-F before the signal is transferred to the send register. The inversion of the input signals can either be done bit-selectively or jointly for all data input pins. See section 4.7.2.

#### 3.3.6. Data Input Filtering

To prevent input signal bouncing being transferred to the AS-Interface Master, the data input signals can be digitally filtered. Filter times can be configured in seven steps from 128µs up to 8.192ms. When the AS-i Cycle Mode is activated, the filter time is determined by the actual AS-i cycle time. For more detailed information, refer to section 4.7.2.

The filter function can be enabled bit-selectively. Activation of the filters can be done jointly either by EEPROM configuration or by the logic state of the parameter port pin P2. See section 4.7.2.

#### 3.3.7. Fixed-Data Output Driving

The fixed-data output-driving feature is intended to facilitate board-level design for similar products that do not require the full data output port width. The user can select one or more bits from the data output port to be driven by a distinct logic level instead of by the data that was sent by the master. The distinct output data is stored in the EEPROM and can be set during final module configuration. With this feature, it is possible to signal the actual IC profile to external circuitry and to allow reuse of some types of board designs for different product applications.

See section 4.7.3.

#### 3.3.8. Synchronous Data I/O Mode

Version 3.0 of the *AS-Interface Complete Specification* defines a synchronous data I/O feature that allows a number of slaves in the network to switch their outputs at the same time and to have their inputs sampled jointly. This feature is especially useful if more than 4-bit wide data are to be provided synchronously to an application.

The synchronization point is defined as the data exchange event of the slave with the lowest address in the network. This definition relies on the cyclical slave polling with incrementing slave addresses each cycle, which is one of the basic communication principles of AS-i. The IC always monitors the data communication and detects the change from a higher to a lower slave address. If such a change has been recognized, the IC assumes that the slave with the lower address has the lowest address in the network.

There are some special procedures that become active during the start of synchronous I/O mode operation and if more than three consecutive telegrams have been sent to the same slave address. This is described in more detail in section 4.7.4.

#### 3.3.9. 4 Input / 4 Output Processing in Extended Address Mode

Version 3.0 of the *AS-Interface Complete Specification* also supports 4-bit wide output data in Extended Address Mode. Up to *AS-Interface Complete Specification V2.11*, it was only possible to send three data output bits from the master to the slave in Extended Address Mode because telegram bit I3 was used to select between the A and B slave types for extended slave addressing (up to 62 slaves per network). In Normal Address Mode, bit I3 carries output data for pin D3.

The version 3.0 definition introduces a multiplexed data transfer so that all 4-bits of the data output port can be used again. A first AS-i cycle transfers the data for a 2-bit output nibble only, while the second AS-i cycle transfers the data for the contrary 2-bit nibble. Nibble selection is done by the remaining third bit. To ensure continuous alternation of bit information I2 and thus continued data transfer to both nibbles, a special watchdog was implemented that observes the state of the I2 bit. The watchdog can be activated or deactivated by EERPOM setting. It provides a watchdog filter time of about 327ms.

The multiplexed transfer increases the refresh time per output by a factor of two; however, some applications can tolerate this increase for the benefit of less external circuitry and better slave address efficiency. The sampling cycle of the data inputs remains unchanged since the meaning of the I3 bit was not changed in the slave response with the definition of the Extended Address Mode.

For more detailed information, see section 4.7.5.

#### 3.3.10. AS-i Safety Mode

The enhanced data input features described in previous sections require additional registers in the data input path that store the input values for a specific time before they transfer them to the AS-i transmitter. This causes a time delay in the input path that could lead to a delayed "turn off" event if the registers are activated by intention or unintentionally in AS-i Safety applications.

To safely exclude an activation of the enhanced data I/O features in AS-i Safety applications, the IC provides a special Safety Mode that is strongly recommended for AS-i Safety communication purposes. See section 4.7.6 for further details.

#### 3.3.11. Enhanced LED Status Indication

ASI4U now supports enhanced status indication by two LED outputs. A special mode for direct application of dual LEDs and the respective different signaling modes are also implemented. Compared to the A<sup>2</sup>SI, the former U5RD pin was reassigned as LED2 pin. Thus, compatibility to existing A<sup>2</sup>SI board layouts is still guaranteed. However, it will require keeping the LED2 pin disabled (default state at delivery) in order to avoid short-circuiting U5R to ground. More detailed information on the different signaling schemes and their activation can be found in section 4.9.

#### 3.3.12. Communication Monitor/Watchdog

Data and parameter communication are continuously observed by a communication monitor. If neither *Data\_Exchange* nor *Write\_Parameter* calls were addressed to and received by the IC within a time frame of approximately 41ms, a *No Data/Parameter Exchange* status is detected and signaled at LED1.

If the respective flags are set in the EEPROM, the communication monitor can also act as communication watchdog that initiates a complete IC reset after expiration of the watchdog timer. The watchdog mode can also be activated and deactivated by a signal at parameter port pin P0. See section 4.15 for more detailed information.

#### 3.3.13. Write Protection of *ID\_Code\_Extension\_1*

As defined in the *AS-Interface Complete Specification V3.0*, the ASI4U/ASI4U-E/ASI4U-F also supports write protection for *ID\_Code\_Extension\_1*. This feature allows the activation of new manufacturer-protected slave profiles and is enabled by an EEPROM setting. For more details, see section 4.17.

#### 3.3.14. Summary of Master Calls

Table 3.2 and the diagram on the following page show the complete set of Master calls that are decoded by the ASI4U/ASI4U-E/ASI4U-F in Slave Mode. The "Enter Program Mode" call is intended for programming of the IC by the slave manufacturer only. It becomes deactivated as soon as the *Program\_Mode\_Disable* flag is set in the "Firmware Area" block of the EEPROM.

Important note regarding full compliance with the AS-Interface Complete Specification: In order to achieve full compliance to the AS-Interface Complete Specification, the Program\_Mode\_Disable flag must be set by the manufacturer of AS-i slave modules during the final manufacturing and configuration process and before an AS-i slave device is delivered to field application users.

|                             |      |    | Master Request |            |    |    |    |    |    |            |     |     |     |    |    | Slave             | Resp     | onse     |          |          |    |    |

|-----------------------------|------|----|----------------|------------|----|----|----|----|----|------------|-----|-----|-----|----|----|-------------------|----------|----------|----------|----------|----|----|

| Instruction                 | MNE  | ST | СВ             | <b>A</b> 4 | A3 | A2 | A1 | A0 | 14 | 13         | 12  | 1   | 10  | PB | EB | SB                | 13       | 12       | 1        | 10       | PB | EB |

| Data Exchange               | DEXG | 0  | 0              | A4         | A3 | A2 | A1 | A0 | 0  | D3<br>~Sel | D2  | D1  | D0  | ΡВ | 1  | 0                 | D3<br>E3 | D2<br>E2 | D1<br>E1 | D0<br>E0 | PB | 1  |

| Write Parameter             | WPAR | 0  | 0              | A4         | A3 | A2 | A1 | A0 | 1  | P3<br>~Sel | P2  | P1  | P0  | PB | 1  | 0                 | P3<br> 3 | P2<br>12 | P1<br>11 | P0<br>10 | PB | 1  |

| Address Assignment          | ADRA | 0  | 0              | 0          | 0  | 0  | 0  | 0  | A4 | A3         | A2  | A1  | A0  | ΡВ | 1  | 0                 | 0        | 1        | 1        | 0        | 0  | 1  |

| Write Extented ID<br>Code_1 | WID1 | 0  | 1              | 0          | 0  | 0  | 0  | 0  | 0  | ID3        | ID2 | ID1 | ID0 | РВ | 1  | 0                 | 0        | 0        | 0        | 0        | 0  | 1  |

| Delete Address              | DELA | 0  | 1              | A4         | A3 | A2 | A1 | A0 | 0  | 0<br>Sel   | 0   | 0   | 0   | РВ | 1  | 0                 | 0        | 0        | 0        | 0        | 0  | 1  |

| Reset Slave                 | RES  | 0  | 1              | A4         | A3 | A2 | A1 | A0 | 1  | 1<br>~Sel  | 1   | 0   | 0   | PB | 1  | 0                 | 0        | 1        | 1        | 0        | 0  | 1  |

| Read IO Configuration       | RDIO | 0  | 1              | A4         | A3 | A2 | A1 | A0 | 1  | 0<br>Sel   | 0   | 0   | 0   | PB | 1  | 0                 | IO3      | IO2      | IO1      | IO0      | PB | 1  |

| Read ID Code                | RDID | 0  | 1              | A4         | A3 | A2 | A1 | A0 | 1  | 0<br>Sel   | 0   | 0   | 1   | PB | 1  | 0                 | ID3      | ID2      | ID1      | ID0      | PB | 1  |

| Read ID Code_1              | RID1 | 0  | 1              | A4         | A3 | A2 | A1 | A0 | 1  | 0<br>Sel   | 0   | 1   | 0   | PB | 1  | 0                 | ID3      | ID2      | ID1      | ID0      | PB | 1  |

| Read ID Code_2              | RID2 | 0  | 1              | A4         | A3 | A2 | A1 | A0 | 1  | 0<br>Sel   | 0   | 1   | 1   | PB | 1  | 0                 | ID3      | ID2      | ID1      | ID0      | PB | 1  |

| Read Status                 | RDST | 0  | 1              | A4         | A3 | A2 | A1 | A0 | 1  | 1<br>~Sel  | 1   | 1   | 0   | PB | 1  | 0                 | S3       | S2       | S1       | S0       | PB | 1  |

| Broadcast (Reset)           | BR01 | 0  | 1              | 1          | 1  | 1  | 1  | 1  | 1  | 0          | 1   | 0   | 1   | 1  | 1  | no slave response |          |          |          |          |    |    |

| Enter Program Mode          | PRGM | 0  | 1              | 0          | 0  | 0  | 0  | 0  | 1  | 1          | 1   | 0   | 1   | 1  | 1  | no slave response |          |          |          |          |    |    |

#### Table 3.2 ASI4U Master Calls and Related Slave Responses

**Note:** In Extended Address Mode, the "Select Bit" defines whether the A-Slave or B-Slave is being addressed. Depending on the type of master call, bit I3 carries the select bit information (Sel = A-Slave) or the inverted select bit information (~Sel = B-Slave).

|                                 | 1        | B-Slave with<br>Profile 0.A<br>(green shaded) |                                    | ASI Master<br>Request<br>(black/green) | ASI Slave<br>Response<br>(blue)   |                  |            |                           | No Slave<br>Response<br>(blue shaded) |

|---------------------------------|----------|-----------------------------------------------|------------------------------------|----------------------------------------|-----------------------------------|------------------|------------|---------------------------|---------------------------------------|

|                                 |          | (green shaded)                                |                                    | (black/green)                          | (blue)                            |                  |            |                           | (blue shaded)                         |

| ADR ! <u>= 0</u>                | 12 I1 I0 | 000                                           | 001                                | 010                                    | 011                               | 100              | 101        | 110                       | / 111                                 |

| CB 14 13                        | l3=Sel   |                                               | (Slave Address                     | != 0) AND (Prog                        | am Mode not ac                    | tivated)         |            |                           |                                       |

| 000                             | Sel=0    | Data_                                         | Exchange /Sel D2                   | D1 D0                                  |                                   |                  |            |                           | /                                     |

| 001                             | Sel=1    | Data                                          | _Exchange D3 D2 [                  | D1 D0                                  | D3 D2 D1 D0                       |                  |            |                           |                                       |

| 010                             | Sel=0    | Write_                                        | Parameter /Sel P2                  | P1 P0                                  |                                   |                  |            |                           |                                       |

| 011                             | Sel=1    |                                               | Parameter P3 P2                    | P1 P0                                  | P3 P2 P1 P0                       |                  |            |                           |                                       |

| 100                             | Sel=0    | Delete_Addr x0                                |                                    |                                        |                                   |                  |            | ///                       |                                       |

| 101                             | Sel=1    | Delete_Addr x0                                |                                    |                                        |                                   |                  |            |                           |                                       |

| 110                             | Sel=0    | Rd_IO_Cfg <13:10>                             | Read_ID < <mark> 3: 0</mark> >     | Read_ID_1 <i3:i0></i3:i0>              | Read_ID_2 <13:10>                 | Reset_Slave 0x6  | Broadcast  | Rd_Status s3:s0>          |                                       |

| 111                             | Sel=1    | Rd_IO_Cfg <13:10>                             | Read_ID < <mark> 3: 0</mark> >     | Read_ID_1<13:10>                       | Read_ID_2 <13:10>                 | Reset_Slave 0x6  |            | Ro_Status <s3:s0></s3:s0> |                                       |

|                                 |          |                                               |                                    |                                        |                                   | _                |            |                           |                                       |

| ADR == 0                        | 12 I1 I0 | 000                                           | 001                                | 010                                    | 011                               | 100              | 101        | 1/10                      | 111                                   |

| CB 14 13                        |          |                                               | (Slave Address                     | == 0) AND (Pro                         | gam Mode not a                    | ctivated)        | /          |                           |                                       |

| 000                             |          |                                               |                                    |                                        |                                   |                  | /          | /                         |                                       |

| 001                             |          |                                               |                                    | Address_Assignm                        | nent A4 A3 A2 A1 A                | 0                | /          |                           |                                       |

| 010                             |          |                                               |                                    |                                        | 0x6                               |                  | /          |                           |                                       |

| 011                             |          | <u> </u>                                      |                                    |                                        |                                   |                  |            | /                         |                                       |

| 100                             |          |                                               |                                    | Write_Var_Ext_Co                       | de1 ID3 ID2 ID1 ID0               |                  |            | /                         |                                       |

| 101                             |          |                                               |                                    |                                        | 0x0                               |                  | Distant    |                           |                                       |

| 110                             |          | Rd_IO_Cfg <13:10>                             | Read_ID <13:10>                    | Read_ID_1 <i3:i0></i3:i0>              | Read_ID_2 <13:10>                 | Deast Olaura Out | Broadcast  | Dil Otatus avai           |                                       |

| 111                             | 1        | <u> </u>                                      |                                    |                                        |                                   | Reset_Slave 0x6  | EnterPmode | Rd_Status <s3:s0></s3:s0> |                                       |

|                                 | 12 11 10 | 000                                           | 001                                | 010                                    | 011                               | 100              | 101        | 110                       | 111                                   |

|                                 | 12 11 10 | 000                                           | Progam Mode a                      |                                        | UTI                               | 100              |            | 110                       | 111                                   |

| СВИР                            |          |                                               | i logani wode a                    | activated                              |                                   |                  |            | ,                         |                                       |

| CB 14 13                        |          |                                               |                                    |                                        |                                   |                  |            |                           |                                       |

| 000                             |          |                                               | ata Exchange                       |                                        | 13 12 11 10                       |                  |            |                           |                                       |

| 000<br>001                      |          | C                                             | ata_Exchange                       | -                                      | 13 12 11 10                       | (EEPROM READ AC  | CESS)      |                           |                                       |

| 000<br>001<br>010               |          |                                               |                                    |                                        |                                   | <u> </u>         |            |                           |                                       |

| 000<br>001<br>010<br>011        |          |                                               | ata_Exchange<br>te_Parameter 13 12 | 1 10                                   | 13 12 11 10                       | (EEPROM READ AC  |            |                           |                                       |

| 000<br>001<br>010<br>011<br>100 |          |                                               |                                    |                                        | 13 12 11 10<br>1e 1D3 1D2 1D1 1D0 | <u> </u>         |            |                           |                                       |

| 000<br>001<br>010<br>011        |          |                                               |                                    | 1 10                                   | 13 12 11 10                       | <u> </u>         |            | Rd Status <53:50>         | reserved                              |

#### 3.4. Master Mode

Master Mode and the related Repeater and Monitor Modes differ completely in their functional properties from the Slave Mode. While the IC can autonomously perform different tasks in Slave Mode, it will only act as a physical layer transceiver in the Master, Repeater, and Monitor Modes.

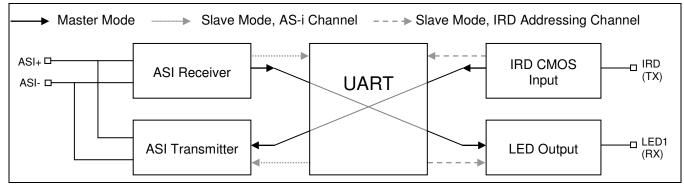

The basic property of these modes is a modulation/demodulation of AS-i signals to Manchester-II code and vice versa. The following figure shows the different data path configurations.

Figure 3.4 Data Path in the Master, Repeater, and Monitor Modes