Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **ASL2416SHN**

# **Enhanced two channel LED buck driver**

Rev. 5.1 — 26 October 2017

**Product data sheet**

## 1. Introduction

The ASL2416SHN is a two channel buck mode LED driver IC delivering constant average DC current to LEDs independent of the input voltage. The ASL2416SHN supports up to two output channels. It means that with one driver IC, 1 or 2 LED strings can be driven independently of each other. It provides a cost effective design solution, specifically targeting automotive exterior and interior lighting applications.

## 2. General description

The ASL2416SHN has a hysteretic buck DC-to-DC topology. With input voltages from 10 V to 80 V, it allows maximum flexibility on output voltages for each channel, enabling applications with up to 20 LEDs. It also provides an output current of up to and above 1.5 A per channel. Furthermore, two output channels can be connected together to provide an even higher current. It drives an external high-side N channel MOSFET from an internally regulated adjustable supply. The ASL2416SHN buck driver gives a flexible system design which can be used to drive two LED strings with the same architecture.

The ASL2416SHN provides an SPI interface for extensive control and diagnostic communication with an external microcontroller.

The ASL2416SHN offers an adjustable hysteresis for optimizing external components as well as minimizing LED current ripple.

In addition, the ASL2416SHN provides an output voltage of up to 70 V. It has a measurement capability that can be used to identify LED open or short circuit conditions. The microcontroller can read this voltage and use it to detect open or short circuit conditions. There are also additional diagnostic features such as current reached status.

Additional features include input under-voltage lockout and thermal shutdown when the junction temperature of the ASL2416SHN exceeds  $+175\,^{\circ}$ C.

It is housed in a very small HVQFN32 pin package with an exposed thermal pad and is designed to meet the stringent requirements of automotive applications. It is fully AEC Q100 grade 1 qualified. It operates over the ambient automotive temperature range of  $-40~^{\circ}\text{C}$  to  $+125~^{\circ}\text{C}$ .

The ASL2416 provides an accurate current over a 1:12.5 range. This range can be scaled up or down using external

components. Depending on the operating conditions and component choices, output currents of min 30 mA and more than 3 A can

be achieved.

## 3. Features and benefits

- The ASL2416SHN is an automotive grade product that is AEC-Q100 grade 1 qualified.

- Operating ambient temperature range of -40 °C to +125 °C

- Wide operating input voltage range from +10 V to +80 V

- Able to drive up to 20 LEDs, wide operating LED voltage range regulated from 2.5 V to 70 V

- Output current of up to and above 1.5 A with high LED current accuracy of  $\pm 5$  % over the complete operating temperature range

- Output current programmable via SPI interface

- Read back programmed current via SPI

- Two output current ranges, programmable via SPI interface with 5 % accuracy

- Hysteretic converter

- Fast gate drive for high efficiency

- Programmable internal gate driver voltage regulator

- Support logic level and standard level FETs

- Integrated bootstrap diode

- PWM inputs for individual dimming of each channel

- Low Electro Magnetic Emission (EME) and high Electro Magnetic Immunity (EMI)

- Input voltage monitoring and input under voltage protection

- Output voltage monitoring

- Control signal to enable the device

- Junction temperature monitoring via SPI

- Small package outline HVQFN32

- Low quiescent current <5 μA at 25 °C when EN = 0</p>

- Short-circuit and open-circuit output protection

# 4. Applications

- Automotive LED lighting Daytime running lights

- Position or park light

- Low beam

- High beam

- Turn indicator

- Fog light

- Cornering light

- Advanced front lighting

## 5. Ordering information

Table 1. Ordering information

| Type number | Package |                                                                                                                   |           |  |  |  |  |

|-------------|---------|-------------------------------------------------------------------------------------------------------------------|-----------|--|--|--|--|

|             | Name    | Description                                                                                                       | Version   |  |  |  |  |

| ASL2416SHN  | HVQFN32 | plastic thermal enhanced very thin quad flat package; no leads; 32 terminals; body $5\times5\times0.85~\text{mm}$ | SOT617-12 |  |  |  |  |

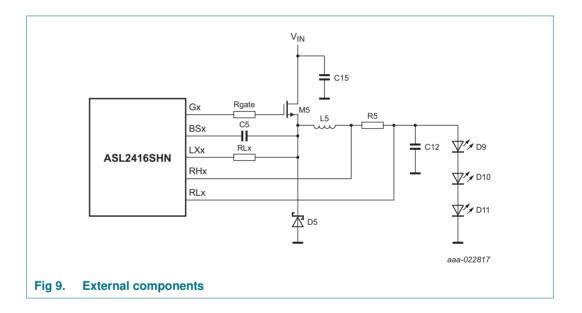

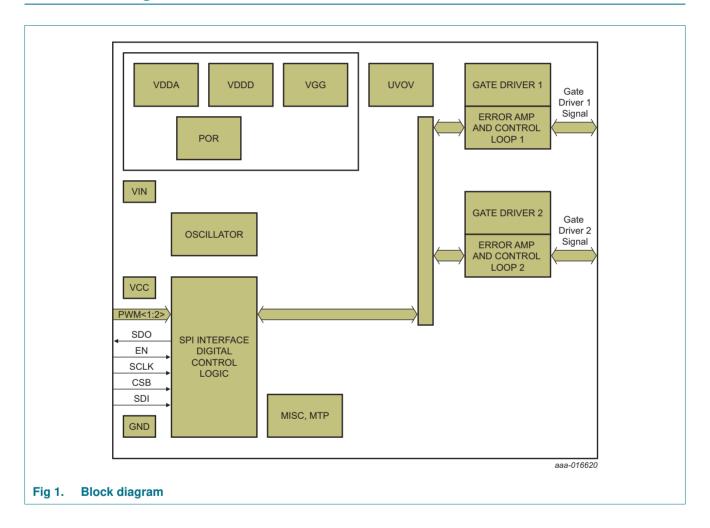

# 6. Block diagram

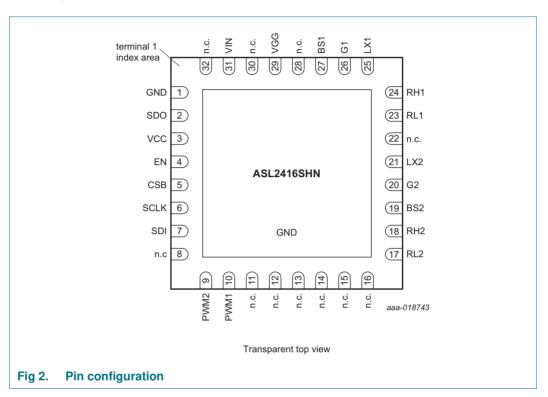

# 7. Pinning information

## 7.1 Pinning

# 7.2 Pin description

## Table 2. Pin description[1]

|        | •   |                               |  |  |

|--------|-----|-------------------------------|--|--|

| Symbol | Pin | Description                   |  |  |

| GND    | 1   | chip ground                   |  |  |

| SDO    | 2   | SPI data out                  |  |  |

| VCC    | 3   | external 5 V supply           |  |  |

| EN     | 4   | enable signal                 |  |  |

| CSB    | 5   | SPI chip select               |  |  |

| SCLK   | 6   | SPI Clock                     |  |  |

| SDI    | 7   | SPI data input                |  |  |

| n.c.   | 8   | not connected                 |  |  |

| PWM2   | 9   | external PWM signal channel 2 |  |  |

| PWM1   | 10  | external PWM signal channel 1 |  |  |

| n.c.   | 11  | not connected                 |  |  |

| n.c.   | 12  | not connected                 |  |  |

| n.c.   | 13  | not connected                 |  |  |

| n.c.   | 14  | not connected                 |  |  |

| n.c.   | 15  | not connected                 |  |  |

| n.c.   | 16  | not connected                 |  |  |

Table 2. Pin description[1] ...continued

| Symbol | Pin | Description                                    |  |

|--------|-----|------------------------------------------------|--|

| RL2    | 17  | sense resistor low side channel 2              |  |

| RH2    | 18  | sense resistor high side channel 2             |  |

| BS2    | 19  | boot supply channel 2                          |  |

| G2     | 20  | channel 2 gate driver                          |  |

| LX2    | 21  | inductor connection to switching FET channel 2 |  |

| n.c.   | 22  | not connected                                  |  |

| RL1    | 23  | sense resistor low side channel 1              |  |

| RH1    | 24  | sense resistor high side channel 1             |  |

| LX1    | 25  | inductor connection to switching FET channel 1 |  |

| G1     | 26  | channel 1 gate driver                          |  |

| BS1    | 27  | boot supply channel 1                          |  |

| n.c.   | 28  | not connected                                  |  |

| VGG    | 29  | gate driver supply                             |  |

| n.c.   | 30  | not connected                                  |  |

| VIN    | 31  | input voltage                                  |  |

| n.c.   | 32  | not connected                                  |  |

<sup>[1]</sup> Not connected (n.c.) pins are internally not connected and must be left floating to maintain high-voltage separation.

For enhanced thermal and electrical performance, the exposed center pad of the package should be soldered to board ground (and not to any other voltage level).

# 8. Functional description

## 8.1 Operating modes

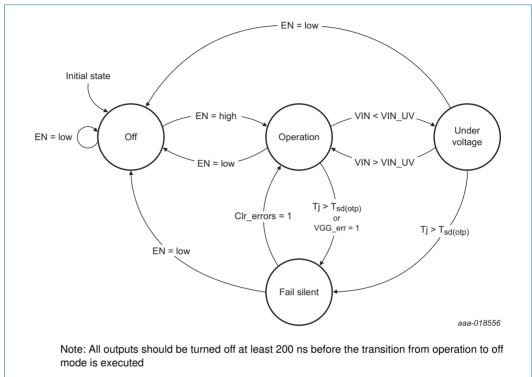

## Fig 3. State diagram

#### 8.1.1 Off mode

If the input voltage drops below the power-off detection threshold ( $V_{th(det)poff}$ ) or the EN pin is low, the ASL2416SHN switches to off mode.

In Off mode, the SPI interface and all outputs are turned off. Before Off mode is entered, all channels should be turned off.

## 8.1.2 Operation mode

The ASL2416SHN switches from Off mode to Operation mode when the input voltage is above the power-on detection threshold ( $V_{th(det)pon}$ ) and the EN pin is high. In Operation mode, all outputs are available as configured via the SPI interface.

## 8.1.3 Under voltage mode

The ASL2416SHN switches from Operation mode to Under voltage mode as soon as the input voltage drops below the programmed voltage. In Under voltage mode, all outputs, including the gate voltage supply are off.

## 8.1.4 Fail silent mode

The ASL2416SHN switches from Operation mode to Fail silent mode, when the junction temperature exceeds the over temperature shutdown threshold or a gate driver error is detected.

In Fail silent mode, all outputs are turned off and only the SPI interface remains operational.

## 8.2 Buck converter

The ASL2416SHN is a buck converter IC delivering constant current to the LEDs. It is a hysteretic controller that regulates the inductor current. It switches off the external FET when the inductor current rises above the upper threshold current. It switches on when the current falls below the lower threshold. The width of the hysteresis window can be programmed via SPI to keep the switching frequency between bounds. The anode of the LED string is connected to the driver, while the cathode of the LED string is connected to ground. This arrangement helps to reduce the total number of connections to the LEDs.

## 8.3 Input voltage measurement

The ASL2416SHN measures the supply voltage of the device and makes this measurement available via the SPI interface.

Table 3. VIN voltage measurement register, address 0x38h[1]

| Bit | Symbol     | Description | Value | Function                                   |

|-----|------------|-------------|-------|--------------------------------------------|

| 7:0 | V_VIN[7:0] | VIN voltage | 0x00h | voltage measurement not available          |

|     |            | measurement |       | VIN voltage = 0.3548 × V_VIN[7:0] – 0.56 V |

[1] A write to the VIN voltage measurement register does not set the SPI error bit high.

## 8.4 Input under voltage detection

The ASL2416SHN offers a variable undervoltage detection threshold.

When the supply voltage is above the under voltage detection threshold, the bit VIN\_stat is high, when the supply voltage is below, the bit is low.

For effects of this bit on the functionality of the device, see <u>Section 8.12.1.1</u>.

Table 4. Undervoltage threshold register, address 0x0Fh

| I | Bit | Symbol        | Description  | Value | Function                                                           |

|---|-----|---------------|--------------|-------|--------------------------------------------------------------------|

| 7 | 7:0 | V_VIN_UV[7:0] | undervoltage | 0x00h | undervoltage detection threshold = 0 V                             |

|   |     |               | threshold    |       | undervoltage detection threshold = 0.3548 × V_VIN_UV[7:0] - 0.56 V |

## 8.5 Output current programmability

The ASL2416SHN provides the possibility to program the LED current and LED current hysteresis via the SPI interface.

#### 8.5.1 Output target current programming

The target output current of the ASL2416SHN can be programmed via the LED current range registers and the LED current registers of channel 1 and channel 2. The sense voltage that is set via SPI, and the value of the external sense resistor, determine the actual level.

$$I_{LED} = \frac{V_{LED current}}{R_{sense}} \tag{1}$$

ASL2416SHN

| Table 5. LED current range register, address | apie 5. | LED current rand | ie reaister. | . address | uxusn |

|----------------------------------------------|---------|------------------|--------------|-----------|-------|

|----------------------------------------------|---------|------------------|--------------|-----------|-------|

| Bit | Symbol | Description           | Value  | Function                                      |

|-----|--------|-----------------------|--------|-----------------------------------------------|

| 7:2 |        | reserved              | 000000 | reserved; keep clear for future use           |

| 1   | I_CH2  |                       | 0      | maximum sense voltage is approximately 300 mV |

|     |        | channel 2             | 1      | maximum sense voltage is approximately 120 mV |

| 0   | I_CH1  | LED current range bit | 0      | maximum sense voltage is approximately 300 mV |

|     |        | channel 1             | 1      | maximum sense voltage is approximately 120 mV |

## Table 6. LED current channel 1 register, address 0x02h

| Bit | Symbol         | Description           | Value                | Function                                         |

|-----|----------------|-----------------------|----------------------|--------------------------------------------------|

| 7:0 | I_LED_CH1[7:0] | LED current channel 1 | 0x00h;<br>0xF6h0xFFh | not recommended                                  |

|     |                |                       |                      | When I_CH1 is 0: 1.179 mV × I_LED_CH1 + 0.74 mV  |

|     |                |                       |                      | When I_CH1 is 1: 0.47882 mV × I_LED_CH1 - 0.6 mV |

#### Table 7. LED current channel 2 register, address 0x03h

| Bit | Symbol         | Description | Value                | Function                                         |

|-----|----------------|-------------|----------------------|--------------------------------------------------|

| 7:0 | I_LED_CH2[7:0] |             | 0x00h;<br>0xF6h0xFFh | not recommended                                  |

|     |                |             |                      | When I_CH2 is 0: 1.179 mV × I_LED_CH2 + 0.74 mV  |

|     |                |             |                      | When I_CH2 is 1: 0.47882 mV × I_LED_CH2 – 0.6 mV |

The LED current is the result of the voltage drop across the R<sub>sense</sub> resistor in mV.

## Example:

To achieve an output current of e.g. 300 mA with 200 m $\Omega$  R<sub>sense</sub> resistor on Channel 1, two settings are possible:

- 1. set bit I CH1 to 1 and the LED current channel 1 register to 0x80h

- 2. set bit I\_CH1 to 0 and the LED current channel 1 register to 0x33h

For higher granularity and higher accuracy, use setting 1. When the LED current is dynamically adjusted to higher levels than offered when bit  $I\_CHx = 1$ , deviations are possible.

## 8.5.2 Hysteresis programming via SPI

ASL2416SHN provides an option to program the level of hysteresis via the SPI interface. The hysteresis setting is independent of the I\_CH1 and I\_CH2 bits in LED current range registers.

The hysteresis voltage that is set via SPI, and the value of the external sense resistor, determine the actual level.

$$I_{Hyst} = \frac{V_{Hyst}}{R_{sense}} \tag{2}$$

The switching frequency varies depending on the hysteresis level, the values of the external components, and the input and the output voltages.

The ASL2416SHN is specified for switching frequencies from 100 kHz to 2 MHz.

Note: For all hysteresis settings, the hysteresis, specified in mV, corresponds with the lowest average LED current in the static characteristics section.

Table 8. Hysteresis channel 1 register, address 0x0Bh

| Bit | Symbol    | Description          | Value  | Function                            |

|-----|-----------|----------------------|--------|-------------------------------------|

| 7:2 |           | reserved             | 000000 | reserved; keep clear for future use |

| 1:0 | HCH1[1:0] | hysteresis channel 1 | 00     | setting 0                           |

|     |           |                      | 01     | setting 1                           |

|     |           |                      | 10     | setting 2                           |

|     |           |                      | 11     | setting 3                           |

Table 9. Hysteresis channel 2 register, address 0x0Ch

| Bit | Symbol    | Description          | Value  | Function                            |

|-----|-----------|----------------------|--------|-------------------------------------|

| 7:2 |           | reserved             | 000000 | reserved; keep clear for future use |

| 1:0 | HCH2[1:0] | hysteresis channel 2 | 00     | setting 0                           |

|     |           |                      | 01     | setting 1                           |

|     |           |                      | 10     | setting 2                           |

|     |           |                      | 11     | setting 3                           |

By increasing the hysteresis level, the switching frequency is reduced, leading to less switching events and consequently lower overall switching losses. However, the ripple of the LED current increases.

#### Calculation example:

A system has 40 V input voltage, an LED voltage of 15 V, a 200 m $\Omega$  R<sub>sense</sub>, and an inductor of 220  $\mu$ H. It operates with a hysteresis of 20 mV at:

$$f = \frac{1}{T} = \frac{1}{T_{on} + T_{off}} = \frac{1}{I_{Hyst} \cdot \frac{L}{V_{IN} - V_{LED}} + I_{Hyst} \cdot \frac{L}{V_{LED}}} = \frac{V_{IN} \cdot V_{LED} - V_{LED}^2}{I_{Hyst} \cdot L \cdot V_{IN}} \approx 426 \text{ kHz}$$

(3)

#### Remarks:

The calculation above does not account for delays in the switching. Due to these delays, the measured switching frequency is lower than calculated here.

To avoid that the device is operating with undesired settings, pull the PWM pin high only when a channel is completely configured.

In case the PWM functionality is not needed, it is possible to connect the PWM pin directly to pin VCC. In this case, the PWM pin control bits can be used to enable or disable the channel. To avoid operation at an undesired frequency, the hysteresis for the channel should be set before the LED current register is set.

The hysteresis and LED current level can be adapted during operation of the device to enable smooth fade-in/fade-out scenarios down to very low output currents. It does it in combination with the PWM inputs.

## 8.5.3 Overcurrent protection

The ASL3416SHN offers an overcurrent protection feature in addition to the set trip points to protect the system. If the output voltage suddenly changes very fast, the upper and lower hysteretic thresholds may deviate from actual target values. In case the deviation is too large the built-in overcurrent protection feature prevents the system from excessive current build-up.

In case such an event is detected, the gate driver will immediately be turned off for approximately 16 ms after which the system is restarted.

## 8.5.4 Output diagnostics

The diagnostic options for the outputs are:

- measurement of the output voltages during the LED on and off state details can be found in Section 8.6

- indication that the target LED current is reached details can be found in Section 8.11

- indication that a channel is operating with low voltage headroom details can be found in <u>Section 8.12.3.1</u>

## 8.6 Output voltage measurement

The ASL2416SHN measures the output voltage of all channels every  $t_{meas}$ . On a transition from the PWM pin of a channel, the measurement results are stored in the corresponding registers. The registers V\_LEDx\_on, contain the voltage information when the PWM input of the channel is high. The registers V\_LEDx\_off, contain the voltage information when the PWM input is low. It ensures that the registers contain the latest measured value of the individual channels with respect to the status of the PWM pin. If the PWM input of one channel stays constant for  $t_{meas(LED)}$ , the V\_LEDx\_on voltage register and the V\_LEDx\_off voltage register of this channel are updated.

Table 10. LED on voltage channel 1 register, address 0x20h

| Bi  | it | Symbol         | Description              | Value | Function                                          |

|-----|----|----------------|--------------------------|-------|---------------------------------------------------|

| 7:0 | 0  | V_LED1_on[7:0] | LED on voltage channel 1 | 0x00h | LED on voltage = 0 V                              |

|     |    |                |                          |       | LED on voltage = 0.3548 × V_LED1_on[7:0] - 0.56 V |

Table 11. LED off voltage channel 1 register, address 0x21h

| Bit | Symbol          | Description               | Value | Function                                            |

|-----|-----------------|---------------------------|-------|-----------------------------------------------------|

| 7:0 | V_LED1_off[7:0] | LED off voltage channel 1 | 0x00h | LED off voltage = 0 V                               |

|     |                 |                           |       | LED off voltage = 0.3548 × V_LED1_off[7:0] - 0.56 V |

#### Table 12. LED on voltage channel 2 register, address 0x22h

| В | Bit | Symbol         | Description              | Value | Function                                          |

|---|-----|----------------|--------------------------|-------|---------------------------------------------------|

| 7 | :0  | V_LED2_on[7:0] | LED on voltage channel 2 | 0x00h | LED on voltage = 0 V                              |

|   |     |                |                          |       | LED on voltage = 0.3548 × V_LED2_on[7:0] - 0.56 V |

Table 13. LED off voltage channel 2 register, address 0x23h

| Bit | Symbol          | Description               | Value | Function                                           |

|-----|-----------------|---------------------------|-------|----------------------------------------------------|

| 7:0 | V_LED2_off[7:0] | LED off voltage channel 2 | 0x00h | LED off voltage = 0 V                              |

|     |                 |                           |       | LED on voltage = 0.3548 × V_LED2_off[7:0] - 0.56 V |

## 8.7 External PWM input

The ASL2416SHN provides a dedicated PWM input for each of the two channels. It allows full control over the PWM frequency and duty cycle and allows phase shifting of the PWM cycles to balance the input current variations.

Pin PWM1 controls channel 1, and PWM2 controls channel 2. A high level at the pins represents that the corresponding channel is turned on and the configured current is delivered to the output.

As soon as the pin is pulled high, pin Gx of the corresponding channel starts toggling. It switches the MOSFET attached to the pin on and off and the system starts to deliver the configured output current.

As soon as the pin is pulled low, pin Gx of the corresponding channel is no longer turned on. The MOSFET stays off and no current is delivered to the output of the corresponding channel.

## 8.7.1 Control for PWM pins

The ASL2416SHN provides the option to disable the PWM input for each of the two channels individually. In case the PWM input of one channel is disabled, this channel stays off, independent of any other conditions.

The bits to disable the PWM inputs are located in the function control register (refer to Section 8.8 for details of the function control register).

## 8.7.2 Diagnostics for PWM functionality

The diagnostic options for the PWM functionality comprise the toggle information for the individual PWM pins. Details of the functionality can be found in <u>Section 8.8</u>.

## 8.8 Function control register

To monitor the status of the SPI interface, use the function control register. It allows a reset of the fail silent mode and offers the control of the PWM inputs.

After enabling the device, the SPI\_status bit should be set. When a query returns that the bit is set, the SPI interface is operational and the device can be configured. Configuration of the device is not permitted before this bit is set.

When the device enters fail silent mode due to an error condition, bit Clr\_error can be set to bring the device back into operation mode. Once the error bits are cleared, the device clears the Clr\_error bit automatically. If the Clr\_error bit is set, when no error is present, the Clr\_error bit remains set, until an error occurs. This error is cleared automatically.

The functionality of bits PWMctrl1 and PWMctrl2 is described in <u>Section 8.7.1</u>.

| Table 14. | Function | control | register  | addrage | Ovooh  |

|-----------|----------|---------|-----------|---------|--------|

| Table 14. | runction | COILLIO | register, | auuress | UXUUII |

| Bit | Symbol     | Description         | Value | Function                                                                |

|-----|------------|---------------------|-------|-------------------------------------------------------------------------|

| 7   | SPI_status | SPI status bit      | 0     | SPI is not available                                                    |

|     |            |                     | 1     | SPI is operating                                                        |

| 6   | Clr_error  | clear error bits    | 0     | no pending clear request                                                |

|     |            |                     | 1     | request to clear error bits and reset fail silent mode pending          |

| 5:3 |            | reserved            | 0     | reserved; keep clear for future use                                     |

| 2   | PWMctrl2   | PWM control for pin | 0     | PWM2 is disabled, channel stays off                                     |

|     |            | PWM2                | 1     | PWM2 is enabled, LED current depends on PWM state and Register settings |

| 1   | PWMctrl1   | PWM control for pin | 0     | PWM1 is disabled, channel stays off                                     |

|     |            | PWM1                | 1     | PWM1 is enabled, LED current depends on PWM state and Register settings |

| 0   |            | reserved            | 0     | reserved; keep clear for future use                                     |

## 8.9 Gate voltage supply

The ASL2416SHN has an integrated linear regulator to generate the supply voltage of the gate drivers. The voltage generated by the linear regulator can be set via the VGG control register.

Table 15. VGG control register, address 0x01h

| Bit | Symbol   | Description | Value | Function                         |

|-----|----------|-------------|-------|----------------------------------|

| 7:0 | VGG[7:0] | VGG control | 0x00h | not allowed                      |

|     |          |             |       | not allowed                      |

|     |          |             | 0x5Dh | maximum output voltage = 10.04 V |

|     |          |             |       | (255-VGG[7:0]) * 62 mV           |

|     |          |             | 0xA6h | minimum output voltage = 5.52 V  |

|     |          |             |       | not allowed                      |

|     |          |             | 0xFFh | not allowed                      |

The actual value of VGG can deviate from the target setting due to the tolerances of the VGG regulation loop (see  $V_{o(reg)acc}$  in <u>Table 32</u>).

When a setting between 0x00h and 0x5Dh is used, the resulting gate driver target voltage exceeds the limiting values of the IC. The limiting values of the VGG pin can also be violated with target settings of 0xA6h to 0x5Dh due to these tolerances. A violation of the limiting values with the actual VGG voltage must be avoided. To ensure that only allowed settings are used for the gate driver target voltage, an immediate read back of the programmed value is required after setting the registers.

If a setting between 0xFFh and 0xA6h is used, the device may shut down.

## 8.9.1 Gate voltage supply diagnostics

The diagnostic options for the gate voltage supply are:

- VGG available. Details can be found in Section 8.12

- VGG overload protection active. Details can be found in Section 8.12

## 8.10 Junction temperature information

The ASL2416SHN provides a measurement of the IC junction temperature. The measurement information is available in the junction temperature register.

Table 16. Junction temperature register, address 0x26h

| Bit | Symbol          | Description          | Value | Function                                                |

|-----|-----------------|----------------------|-------|---------------------------------------------------------|

| 7:0 | T_junction[7:0] | junction temperature | 0xD8h | device junction temperature = −40 °C                    |

|     |                 |                      |       | device junction temperature = (256 - T_juction[7:0]) °C |

|     |                 |                      | 0xFFh | device junction temperature = −1 °C                     |

|     |                 |                      | 0x00h | device junction temperature = 0 °C                      |

|     |                 |                      | 0x01h | device junction temperature = 1 °C                      |

|     |                 |                      |       | device junction temperature = T_juction[7:0]* °C        |

|     |                 |                      | 0xAFh | device junction temperature = 175 °C                    |

The reading of the junction temperature register should be in the range as given in <u>Table 16</u>. If not, the Tj\_err bit (Bit 5 in diagnostic register 1, address 0x37h) can be used to indicate whether the temperature is below  $175 \,^{\circ}$ C (Tj\_err = Low) or above  $175 \,^{\circ}$ C (Tj\_err = High).

## 8.11 Bootstrap recharge mechanism

The gate drivers and current delivered to the gate pins of the ASL2416SHN is supplied by the bootstrap capacitors. These capacitors are attached between the LXx and the BSx pins of the device. To allow a proper drive of the external FET, the voltage across this capacitor must remain near the target level of the gate drive voltage.

During device operation, if the external FET switches periodically at quite high frequency, the bootstrap capacitor is charged when the Lx node is low. It is the case when the external FET is off and the converter coil is delivering current to the output.

When the external FET is not switching periodically, the bootstrap capacitor is recharged regularly every to when:

- the PWM pin is low for more than T<sub>meas(LED)</sub>

- . the PWM is high and the CR0 bit is low

## 8.11.1 Bootstrap charge maintaining

To avoid a discharge of the bootstrap capacitors when the system is operated with long PWM off times and short PWM on times, an additional mechanism maintains the bootstrap charge.

The ASL2416SHN compensates for the current consumption of the IC on the BS pins. As a result, the BS cap no longer discharges, but slowly settles around VBS-LX.

The compensating mechanism is enabled when the gate driver is enabled, the PWM is low, and no Bootstrap undervoltage or low voltage headroom condition is detected.

## 8.12 Diagnostic information

Diagnostic registers contain useful information for diagnostic purposes. Details of each bit can be found in the following subchapters.

## 8.12.1 Diagnostic Register 1

The diagnostic register 1 contains information about the operational status of the ASL2416SHN.

Table 17. Diagnostic register 1, address 0x37h

| Bit | Symbol   | Description                         | Value | Function                                                     |

|-----|----------|-------------------------------------|-------|--------------------------------------------------------------|

| 7   | VIN_stat | VIN status                          | 0     | VIN below under voltage detection threshold                  |

|     |          |                                     | 1     | VIN above under voltage detection threshold                  |

| 6   | SPI_err  | SPI error                           | 0     | last SPI command was executed correctly                      |

|     |          |                                     | 1     | last SPI command was erroneous and has been discarded        |

| 5   | Tj_err   | device temperature is too           | 0     | device temperature below 175 °C                              |

|     |          | high                                | 1     | device temperature above 175 °C                              |

| 4   | VGG_err  | VGG error                           | 0     | VGG overload protection not active                           |

|     |          |                                     | 1     | VGG overload protection has turned on and VGG is deactivated |

| 3   | VGG_ok   | VGG regulation ok                   | 0     | VGG is not available                                         |

|     |          |                                     | 1     | VGG is available                                             |

| 2   |          | reserved                            | 0     | reserved; keep clear for future use                          |

| 1   | I-CH2    | target current reached on           | 0     | target current was not reached during last PWM cycle         |

|     |          | channel 2                           | 1     | target current was reached during last PWM cycle             |

| 0   | I-CH1    | target current reached on channel 1 | 0     | target current was not reached during last PWM cycle         |

|     |          |                                     | 1     | target current was reached during last PWM cycle             |

#### 8.12.1.1 Bit VIN stat

The bit VIN\_stat indicates the VIN voltage status of the device. This bit is set once the VIN voltage is higher than programmed under voltage threshold value. When VIN is less than the programmed under voltage threshold value, the bit is cleared. (see <a href="Section 8.4">Section 8.4</a> for details about the input under voltage detection functionality)

When the bit is high, the gate pins start switching. The device starts to deliver the output current as requested via the PWM inputs of the corresponding channels. The bits VGG\_ok and VGG\_err indicate the functional status of VGG.

When the bit is low, the VGG regulator and gate drivers are turned off. The gate pins stop switching, resulting in a turn-off of the output currents. The bit VGG\_ok is reset, the bit VGG\_err is not changed and the VLED measurement registers are no longer updated.

Table 18. Effect of VIN\_stat on device functionality

| Status of VIN                           | VIN_stat | VGG_ok       | VGG_err       | Output current | VLED measurement         |

|-----------------------------------------|----------|--------------|---------------|----------------|--------------------------|

| below under voltage detection threshold | 0        | reset        | cannot be set | disabled       | no update                |

| above under voltage detection threshold | 1        | no influence | no influence  | enabled        | updated when VGG_ok is 1 |

#### 8.12.1.2 Bit SPI err

The bit SPI\_err indicates if some error has occurred during the last SPI transfer. When this bit is set after a write access to the device, the device discards the command. When the bit is set after a read command, the microcontroller should discard the information delivered by the device. The SPI err bit is set in the following cases:

- SPI write is attempted to a read-only location or reserved location

- · SPI read is attempted from a reserved location

- SPI command does not consist of a multiple of 16 clock counts

The SPI\_err bit is cleared on a write to the diagnostic register 1.

In case a SPI\_error has been detected, the device will return the diagnostic register 1 (default read) and diagnostic register 2 for the next SPI access.

## 8.12.1.3 Bit Tj err

When the junction temperature rises above the maximum allowable temperature ( $T_{sd(otp)}$ ), bit Tj\_err is set high. It turns off the gate driver and the gate driver voltage regulator, and clears bit VGG\_ok. If VGG\_ok was already set high, bit VGG\_err is set. The output current is no longer delivered. Only the SPI remains operational.

Bit Tj\_err must only be cleared with the Clr\_errors command when the junction temperature is below the maximum allowable temperature threshold again. Bit VGG\_err, that is set together with bit Tj\_err, is cleared together with bit Tj\_err.

#### 8.12.1.4 Bit VGG err

The bit VGG\_err is set when VGG cannot be regulated to its target value. During start-up, the device waits for  $t_{err(startup)}$  until the bit is set, during normal operation the device waits only  $t_{err(oper)}$ . Once the bit is set, it turns off the gate driver and the gate driver voltage regulator, and clears bit VGG\_ok. Consequently, output current can no longer be delivered. Only the SPI remains operational.

In case the VGG\_err bit is set, the LED voltage measurement is no longer updated.

To reset the bit, the bit Clr\_errors in the function control register can be set. Alternatively, the device must be set to off mode, e.g. by EN going low, or a power-on reset.

## 8.12.1.5 Bit VGG\_ok

The bit VGG\_ok is set, as soon as the VGG output is regulated to the target value. The bit is cleared on an under voltage condition at VIN, or an error on VGG.

#### 8.12.1.6 Bit I-Ch1 and I-CH2

The bits I-CH1 and I-CH2 indicate, whether the targeted output current was reached or not in the last PWM cycle. Reasons for not reaching the target current can be e.g. an open LED string or a too low input voltage.

The bits are updated for a:

- falling edge of the PWM

- · write of the CR copy pulse bit

The bits are cleared for a:

- VIN under voltage event

- low voltage headroom event on the representative channel

## 8.12.1.7 CR copy pulse

The bits CCH1 and CCH2 can be used to force an update of the LED current reached information. Setting a bit high, initiates an update of the I-CHx bit in the diagnostic register 1 and clears the CR0\_CHx bit. The device automatically clears the bit that was set high after the update.

Table 19. CR copy pulse register, address 0x06h

| Bit | Symbol                            | Description                     | Value  | Function                            |

|-----|-----------------------------------|---------------------------------|--------|-------------------------------------|

| 7:2 |                                   | reserved                        | 000000 | reserved; keep clear for future use |

| 1   | CCH2                              | update request for bit<br>I-CH2 | 0      | no pending update request           |

|     |                                   |                                 | 1      | update request for bit I-CH2        |

| 0   | CCH1 update request for bit I-CH1 |                                 | 0      | no pending update request           |

|     |                                   | I-CH1                           | 1      | update request for bit I-CH1        |

## 8.12.2 Diagnostic register 2

The diagnostic register 2 contains the PWM toggle information of the ASL2416SHN.

Table 20. Diagnostic register 2, address 0x36h

| Bit | Symbol | Description                     | Value | Function                                                   |

|-----|--------|---------------------------------|-------|------------------------------------------------------------|

| 7   |        | reserved                        | 0     | reserved; keep clear for future use                        |

| 6   |        | reserved                        | 1     | reserved; keep clear for future use                        |

| 5:2 |        | reserved                        | 000   | reserved; keep clear for future use                        |

| 1   | PWM2   | toggle information for pin PWM2 | 0     | PWM2 has not toggled since last time the register was read |

|     |        |                                 | 1     | PWM2 has toggled since last time the register was read     |

| 0   | PWM1   | toggle information for pin PWM1 | 0     | PWM1 has not toggled since last time the register was read |

|     |        |                                 | 1     | PWM1 has toggled since last time the register was read     |

#### 8.12.2.1 PWM toggle information (bits PWM1 and PWM2)

To allow the detection of errors in the control of the PWM pins, the ASL2416SHN allows some diagnostics of the PWM inputs via diagnostic register 2. This register contains the toggle information of the PWM inputs.

The bits are set when a change in the level of the pin is detected. The bits are reset on a write to diagnostic register 2.

## 8.12.3 Diagnostic register 3

Diagnostic register 3 contains the low voltage headroom warning information and the output current state bits.

## 8.12.3.1 Low voltage headroom warning

When the ASL2416SHN operates with low voltage headroom, it could lead to very high duty cycles. Subsequent long on-times for the external FET, could result in low switching frequencies. To avoid long on-times of the external FET, the supply voltage and output voltages are continuously monitored while the channel is on and VIN\_stat is high. Once the output voltage is measured to be above VIN minus the low voltage headroom, the gate

pin is pulled low. It results in the FET being turned off. At the same moment in time, the low voltage headroom bit (LV\_CHx in diagnostic register 3) for the corresponding channel is set.

If the voltage difference is again above the low voltage headroom, the device starts to operate again.

Bits LV\_CH1 and LV\_CH2 remain set until a write to the diagnostic register 3 is performed. If the bits are cleared while the channels are turned off or VIN\_stat is low, the bits might be set again if the last sampled voltage indicates a low voltage headroom condition.

## 8.12.3.2 Output current state

Diagnostic register 3 also contains bits CR0\_CH1 and CR0\_CH2. The bits indicate the target current reached information of the individual channels for the current PWM cycle.

The bits are set as soon as the target current of the channel is reached.

The bits are cleared under the following conditions:

- · a falling edge on the PWM pin

- · a VIN under voltage event

- a CR0 copy pulse request via SPI

- the gate is driven high for more than 1 ms while PWM is high

#### 8.12.3.3 Register content

Table 21. Diagnostic register 3, address 0x35h

| Bit | Symbol  | Description                 | Value | Function                                 |

|-----|---------|-----------------------------|-------|------------------------------------------|

| 7:5 |         | reserved                    | 00    | reserved; keep clear for future use      |

| 4   | CR0_CH2 | current reached CH2         | 0     | output current is not reached            |

|     |         |                             | 1     | output current is reached                |

| 3   | CR0_CH1 | current reached CH1         | 0     | output current is not reached            |

|     |         |                             | 1     | output current is reached                |

| 2   |         | reserved                    | 00    | reserved; keep clear for future use      |

| 1   | LV_CH2  | low voltage headroom in CH2 | 0     | no low headroom event occurred           |

|     |         |                             | 1     | at least one low headroom event occurred |

| 0   | LV_CH1  | low voltage headroom in CH1 | 0     | no low headroom event occurred           |

|     |         |                             | 1     | at least one low headroom event occurred |

## 8.12.4 Diagnostic register 4

Diagnostic register 4 contains the BS undervoltage detection bits.

## 8.12.4.1 Bootstrap undervoltage detection

The integrated bootstrap undervoltage detection monitors the voltage between the BS and the LX pins during the off time of the LX pin. If the voltage drops below VBS\_UV, the ASL2416SHN prevents the gate from being turned-on and prevent the MOSFET being driven at a low voltage.

When this condition is detected on a channel, the channel is turned off and the appropriate error bit is set. A write command to the device clears the error bit and any bits to be cleared are set high. Once the error is cleared, the channel is enabled again.

Table 22. BS UV register - read access, address 0x34h

| Bit | Symbol | Description        | Value | Function                            |

|-----|--------|--------------------|-------|-------------------------------------|

| 7:2 |        | reserved           | 00000 | reserved; keep clear for future use |

| 1   | BS_UV2 | low BS warning CH2 | 0     | no low BS event occurred            |

|     |        |                    | 1     | at least one low BS event occurred  |

| 0   | BS_UV1 | low BS warning CH1 | 0     | no low BS event occurred            |

|     |        |                    | 1     | at least one low BS event occurred  |

Table 23. BS\_UV register - write access, address 0x34h

| Bit | Symbol | Description        | Value | Function                            |

|-----|--------|--------------------|-------|-------------------------------------|

| 7:2 |        | reserved           | 00000 | reserved; keep clear for future use |

| 1   | BS_UV2 | low BS warning CH2 | 0     | no action                           |

|     |        |                    | 1     | clear low BS warning for channel 2  |

| 0   | BS_UV1 | low BS warning CH1 | 0     | no action                           |

|     |        |                    | 1     | clear low BS warning for channel 1  |

## 8.13 SPI

The ASL2416SHN uses an SPI interface to communicate with an external microcontroller. The SPI interface can be used for setting the LEDs current, reading and writing the control register.

## 8.13.1 Introduction

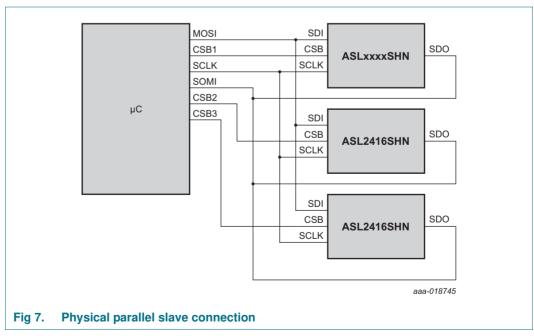

The Serial Peripheral Interface (SPI) provides the communication link with the microcontroller, supporting multi-slave operations. The SPI is configured for full duplex data transfer, so status information is returned when new control data is shifted in. The interface also offers a read-only access option, allowing the application to read back the registers without changing the register content.

The SPI uses four interface signals for synchronization and data transfer:

- · CSB SPI chip select; active LOW

- SCLK SPI clock default level is LOW due to low-power concept

- SDI SPI data input

- SDO SPI data output floating when pin CSB is HIGH

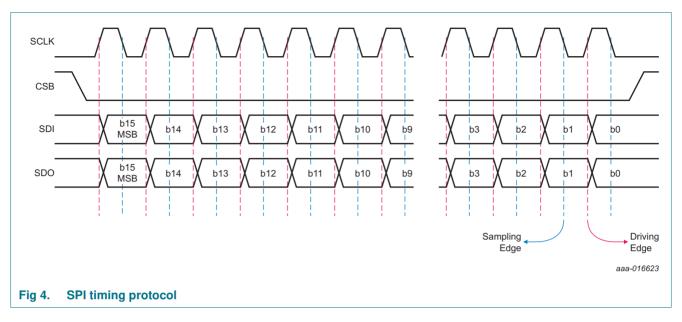

Bit sampling is performed on the falling clock edge and data is shifted on the rising clock edge as illustrated in <u>Figure 4</u>.

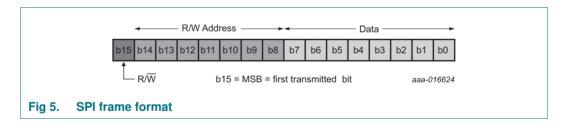

The data bits of the ASL2416SHN are arranged in registers of 1 byte length. Each register is assigned to a 7-bit address. For writing into a register, 2 bytes must be sent to the LED driver. The first byte is an identifier byte that consists of the 7-bit address and one read-only bit. For writing, the read-only bit must be set to "0". The second byte is the data that Is written into the register. So an SPI access consists of at least 16 bits.

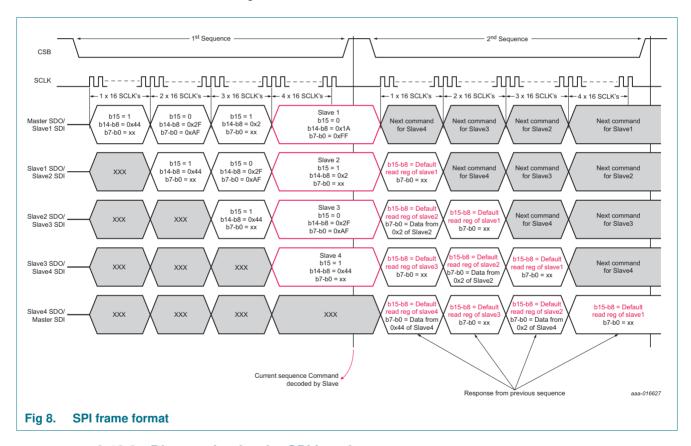

Figure 5 together with Table 24 and Table 25 demonstrate the SPI frame format.

Table 24. SPI frame format for a transition to the device

| Bit  | Symbol | Description  | Value | Function         |

|------|--------|--------------|-------|------------------|

| 15   | b15    | R/W bits     | 0     | write access     |

|      |        |              | 1     | read access      |

| 14:8 | b14:8  | address bits |       | selected address |

| 7:0  | b7:0   | data bits    |       | transmitted data |

Table 25. SPI frame format for a transition from the device

| Bit  | Symbol | Description           | Value | Function                                                                                                     |

|------|--------|-----------------------|-------|--------------------------------------------------------------------------------------------------------------|

| 15:8 | b15:8  | diagnostic register 1 |       | content of diagnostic register 1                                                                             |

| 7:0  | b7:0   | data bits             |       | when previous command was a valid read command, content of the register that is supposed to be read          |

|      |        |                       |       | When previous command was a valid write command, new content of the register that was supposed to be written |

Note: The first SPI command after a leaving of off mode returns 0x00h.

The Master initiates the command sequence. The sequence begins with CSB pin pulled low and lasts until it is asserted high.

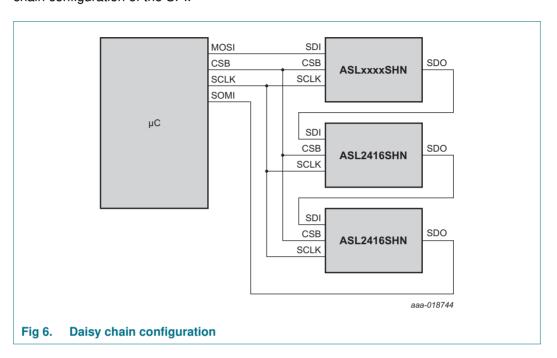

The ASL2416SHN also tolerates SPI accesses with a multiple of 16 bits. It allows a daisy chain configuration of the SPI.

During the SPI data transfer, the identifier byte and the actual content of the addressed registers is returned via the SDO pin. The same happens for pure read accesses. Here the read-only bit must be set to 1. The content of the data bytes that are transmitted to the ASL2416SHN is ignored.

The ASL2416SHN monitors the number of data bits that are transmitted. If the number is not 16, or a multiple of 16, then a write access is ignored and the SPI error indication bit is set.

## 8.13.2 Typical use case illustration (write/read)

Consider a daisy chain scheme with one master connected to 4 slaves in Daisy chain fashion. The following commands are performed during one sequence (first sequence).

- write data 0xFF to register 0x1A slave 1

- read from register 0x02 of slave 2

- write data 0xAF to register 0x2F of slave 3

- · read from register 0x44 of slave 4

## 8.13.3 Diagnostics for the SPI interface

The diagnostic options for the SPI interface are Error during last SPI transfer. For details, refer to Section 8.11.

## 8.13.4 Register map

The addressable register space amounts to 128 registers from 0x00 to 0x7F. They are separated in two groups as shown in <u>Table 26</u>. The register mapping is shown in <u>Table 27</u> and <u>Table 28</u>. The functional description of each bit can be found in the dedicated chapter.

Table 26. Grouping of the register space

| Address range | Description          | Content                              |

|---------------|----------------------|--------------------------------------|

| 0x00 0x1F     | control registers    | thresholds, LED currents             |

| 0x20 0x7F     | diagnostic registers | LED voltages, PWM toggle information |

## 8.13.4.1 Control registers

Table 27 provides an overview of the control registers and their reset state.

Table 27. Control register group overview

| Address | Name                      | Reset value | 7          | 6              | 5 | 4   | 3          | 2        | 1        | 0     |

|---------|---------------------------|-------------|------------|----------------|---|-----|------------|----------|----------|-------|

| 0x00h   | function control          | 0x0Eh       | SPI_status | Clr_errors     | - | -   | -          | PWMctrl2 | PWMctrl1 | -     |

| 0x01h   | VGG control               | 0xFFh       |            |                |   |     | VGG[7:0]   |          |          |       |

| 0x02h   | LED current channel 1     | 0x00h       |            |                |   | I_L | .ED_CH1[7: | :0]      |          |       |

| 0x03h   | LED current channel 2     | 0x00h       |            | I_LED_CH2[7:0] |   |     |            |          |          |       |

| 0x05h   | LED current range         | 0x07h       | -          | -              | - | -   | -          | -        | I_CH2    | I_CH1 |

| 0x06h   | CR copy pulse             | 0x00h       | -          | -              | - | -   | -          | -        | CCH2     | CCH1  |

| 0x0Bh   | hysteresis channel 1      | 0x03h       | -          | -              | - | -   | -          | -        | HCH1[    | 1:0]  |

| 0x0Ch   | hysteresis channel 2      | 0x03h       | HCH2[1:0]  |                |   |     |            | 1:0]     |          |       |

| 0x0Fh   | undervoltage<br>threshold | 0x00h       |            |                |   | V_  | VIN_UV[7:  | 0]       |          |       |

## 8.13.4.2 Diagnostic registers

<u>Table 28</u> provides an overview of the diagnostic registers. As the device continuously updates these registers, they do not have a default value.

Table 28. Diagnostic register group overview

| Address | Name                                          | 7        | 6               | 5     | 4       | 3        | 2 | 1      | 0      |

|---------|-----------------------------------------------|----------|-----------------|-------|---------|----------|---|--------|--------|

| 0x20h   | LED on voltage channel 1                      |          |                 |       | V_LED1_ | on[7:0]  |   |        |        |

| 0x21h   | LED off voltage channel 1                     |          |                 |       | V_LED1_ | off[7:0] |   |        |        |

| 0x22h   | LED on voltage channel 2                      |          |                 |       | V_LED2_ | on[7:0]  |   |        |        |

| 0x23h   | LED off voltage channel 2                     |          |                 |       | V_LED2_ | off[7:0] |   |        |        |

| 0x26h   | junction temperature                          |          | T_junction[7:0] |       |         |          |   |        |        |

| 0x34h   | diagnostic register 4                         | -        | -               | -     | -       | -        | - | BS_UV2 | BS_UV1 |

| 0x35h   | diagnostic register 3                         | -        | -               | -     | CR0_CH2 | CR0_CH1  | - | LV_CH2 | LV_CH1 |

| 0x36h   | diagnostic register 2                         | -        | 1               | -     | -       | -        | - | PWM2   | PWM1   |

| 0x37h   | diagnostic register 1 (default read register) | VIN_Stat | SPI_er          | Tj_er | VGG_er  | VGG_ok   | - | I-CH2  | I-CH1  |

| 0x38h   | VIN voltage<br>measurement <sup>[1]</sup>     |          |                 |       | V_VIN   | 7:0]     |   |        |        |

<sup>[1]</sup> A write to the VIN voltage measurement register does not set the SPI error bit high.

## 8.13.4.3 Internal registers

The ASL2416SHN uses the SPI registers to control some internal functions. In order to avoid any unintended behavior of the device, do not modify these registers but leave them all at their default value.

Table 29. Internal register overview

|         | 3          |               |   |   |   |   |   |   |   |   |

|---------|------------|---------------|---|---|---|---|---|---|---|---|

| Address | Name       | Default value | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 0x04h   | Internal 1 | 0x16h         | - | - | - | - | - | - | - | - |

| 0x0Dh   | Internal 2 | 0x03h         | - | - | - | - | - | - | - | - |

| 0x24h   | Internal 3 | 0x00h         | - | - | - | - | - | - | - | - |

| 0x25h   | Internal 4 | 0x00h         | - | - | - | - | - | - | - | - |

# 9. Limiting values

#### Table 30. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol                  | Parameter                                   | Conditions                                             | Min  | Max    | Unit |

|-------------------------|---------------------------------------------|--------------------------------------------------------|------|--------|------|

| V <sub>IN</sub>         | voltage on pin VIN                          | EN = low                                               | -0.3 | +80    | ٧    |

|                         |                                             | EN = high                                              | 10   | 80     | ٧    |

| V <sub>VCC</sub>        | voltage on pin VCC                          |                                                        | -0.3 | +5.5   | ٧    |

| $V_{I(dig)}$            | digital input voltage                       | voltage on pins SDO, SDI, CSB, SCLK, EN, PWM1 and PWM2 | -0.3 | +5.5   | V    |

| V <sub>VGG</sub>        | voltage on pin VGG                          |                                                        | -0.3 | +10    | V    |

| $V_{LX}$                | voltage on pin LX                           | LX1 and LX2                                            | -1.0 | +80    | V    |

| SR <sub>f(max)</sub>    | maximum falling edge slew rate              | on pins LX1, LX2 and LX3; at maximum input voltage     | -    | 5.0[1] | V/ns |

| V <sub>sense</sub>      | sense voltage                               | voltage on sense pins RH1, RL1, RH2, RL2, RH3 and RL3  | -1.0 | +70[2] | V    |

| $\Delta V_{RH-RL(max)}$ | maximum voltage drop between pins RH and RL | maximum drop between the RH and RL pins of one channel | -0.3 | +0.8   | V    |

| V <sub>BSx</sub>        | voltage on bootstrap pins                   | BS1 and BS2                                            | -0.3 | +90    | V    |

| $V_{Gx}$                | voltage on gate pins                        | G1 and G2                                              | -1.0 | +90    | ٧    |

| $\Delta V_{max}$        | maximum voltage difference                  | between pins G and LX of one channel                   | -    | 12     | ٧    |

|                         |                                             | between pins BS and LX of one channel                  | -    | 12     | ٧    |

| T <sub>j</sub>          | junction temperature                        |                                                        | -40  | +175   | °C   |

| T <sub>stg</sub>        | storage temperature                         |                                                        | -55  | +175   | °C   |

| V <sub>ESD</sub>        | electrostatic discharge voltage             | HBM <sup>[3]</sup>                                     | ,    | "      | '    |

|                         |                                             | at any pin                                             | -2   | +2     | kV   |

|                         |                                             | at pins RLx with respect to GND and 100 nF at pin      | -6   | +6     | kV   |

|                         |                                             | CDM[4]                                                 | II.  | 1      | 1    |

|                         |                                             | at any pin                                             | -500 | +500   | ٧    |

<sup>[1]</sup> The limitation of the slew rate is an IC constraint. When the IC is operating in an application circuit, the external circuitry influences the slew rate capability. An example guideline for some specific MOSFET parameters to be considered when selecting the appropriate resistor values, can be found in the table below. Nonetheless, each application should be validated to determine the final solution when considering EMC performance and correct gate driver operation.

<sup>[2] 76</sup> V for  $t \le 10$  seconds guaranteed by design.

<sup>[3]</sup> Human Body Model (HBM): according to AEC-Q100-002 (100 pF, 1.5 k $\Omega$ ).

<sup>[4]</sup> Charged Device Model (CDM): according to AEC-Q100-011 (field Induced charge; 4 pF).

## 9.1 External circuitry

Table 31. Guideline for external circuitry

| Symbol            | Component                       | •         |           | nfiguration typical values |    |  |  |

|-------------------|---------------------------------|-----------|-----------|----------------------------|----|--|--|

|                   |                                 | Config. 1 | Config. 2 | Config. 3                  |    |  |  |

| $R_G$             | [1]                             | 1.0       | 4.7       | 1.7                        | Ω  |  |  |

| $Q_{GS}$          | [1]                             | 0.6       | 1.2       | 0.8                        | nC |  |  |

| $Q_{GD}$          | [1]                             | 0.9       | 1.8       | 1.2                        | nC |  |  |

| R <sub>DSon</sub> | [1]                             | 175       | 80        | 72                         | mΩ |  |  |

| R <sub>gate</sub> | gate resistor                   | 33        | 15        | 33                         | Ω  |  |  |

| RLx               | sense resistor low side channel | 10        | 10        | 10                         | Ω  |  |  |

| C5                |                                 | 1         | 1         | 1                          | μF |  |  |

## [1] MOSFET M5