Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **ASL2500SHN**

# Two phase boost converter

Rev. 3 — 26 October 2017

Product data sheet

# 1. Introduction

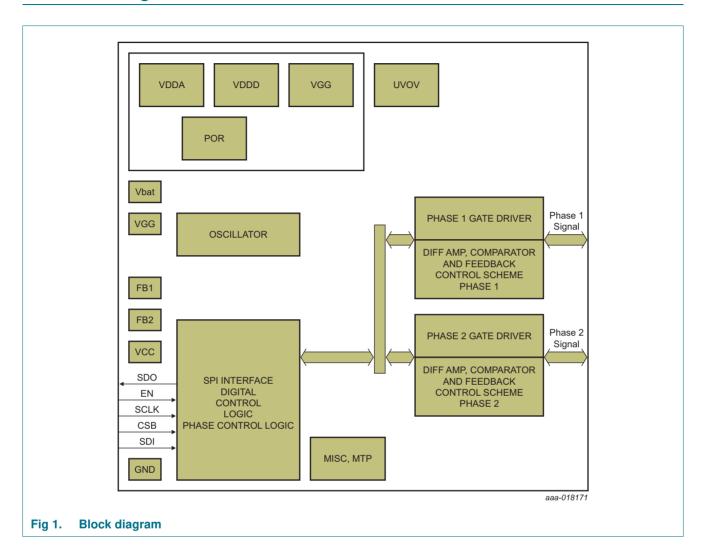

The ASL2500SHN is a highly integrated and flexible two-phase DC-to-DC boost converter IC. It has an SPI interface allowing control and diagnostic communication with an external microcontroller.

It is designed primarily for use in automotive LED lighting applications and provides an optimized supply voltage for ASLx415SHN Multi-channel LED Buck Driver.

# 2. General description

The ASL2500SHN has a fixed frequency peak current mode control with parabolic/non-linear slope compensation. It can operate with input voltages from 5.5 V to 40 V. It can be configured via SPI for output voltages of up to 80 V, to power the LED buck driver IC.

The ASL2500SHN is a two-phase converter which can have two independent outputs. The flexible driver can be configured, via the SPI interface, as a single output converter, or with multiple combinations of number of outputs and phases.

The ASL2500SHN boost converter can drive up to two external low-side N channel MOSFETs from an internally regulated adjustable supply. It can drive either logic or standard level MOSFETs.

The integrated SPI interface also allows for programming the supply under/over voltage range, output voltage range and DC-to-DC switching frequency. It enables the optimization of external components and flexibility for EMC design. This interface can also be used to provide diagnostic information such as the driver temperature.

Additional features include input under-voltage lockout and thermal shutdown when the junction temperature of the ASL2500SHN exceeds  $+175\,^{\circ}$ C.

The device is housed in a very small HVQFN32 pin package with an exposed thermal pad. It is designed to meet the stringent requirements of automotive applications. It is fully AEC Q100 grade 1 qualified. It operates over the  $-40~^{\circ}$ C to  $+125~^{\circ}$ C ambient automotive temperature range.

# 3. Features and benefits

- The ASL2500SHN is an automotive grade product that is AEC-Q100 grade 1 qualified.

- Operating ambient temperature range of –40 °C to +125 °C

- Wide operating input voltage range from +5.5 V to +40 V

- Output voltage programmable via SPI interface

- Multi-phase operation for higher power

- Up to two phases per output

- Up to two flexible output voltages with 3 % accuracy programmable via SPI

- Both output voltages can be controlled independently

- Fixed Frequency Operation via built-in oscillator

- Slope compensation to track the frequency and output voltage

- Programmable control loop compensation

- Fast high efficiency FET switching

- Programmable internal gate driver voltage regulator

- Gate switching is halted when overvoltage on output is detected

- Support both Logic Level and Standard Level FETs

- Low Electro Magnetic Emission (EME) and high Electro Magnetic Immunity (EMI)

- Output voltage monitoring

- Supply voltage measurement

- Control signal to enable the device

- Read-back programmed voltage and frequency range via SPI

- Junction temperature monitoring via SPI

- Small package outline HVQFN32

- Low quiescent current <5 μA at 25 °C when EN = 0</p>

# 4. Applications

- Automotive LED lighting

- Daytime running lights

- Position or park light

- Low beam

- High beam

- Turn indicator

- Fog light

- Cornering light

# 5. Ordering information

Table 1. Ordering information

| Type number | Package |                                                                                                                   |           |  |  |

|-------------|---------|-------------------------------------------------------------------------------------------------------------------|-----------|--|--|

|             | Name    | Description                                                                                                       | Version   |  |  |

| ASL2500SHN  | HVQFN32 | plastic thermal enhanced very thin quad flat package; no leads; 32 terminals; body $5\times5\times0.85~\text{mm}$ | SOT617-12 |  |  |

ASL2500SHN

# 6. Block diagram

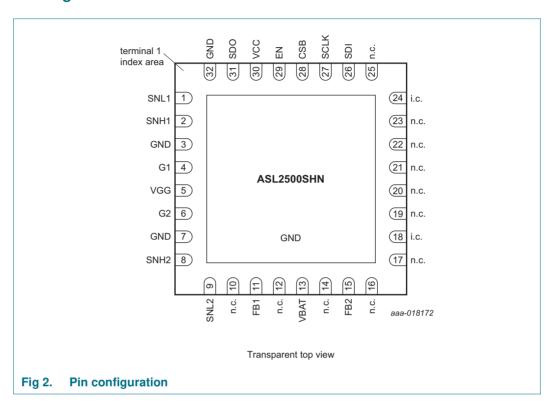

# 7. Pinning information

# 7.1 Pinning

# 7.2 Pin description

Table 2. Pin description[1]

| 0                | D' . | B                   |  |  |

|------------------|------|---------------------|--|--|

| Symbol           | Pin  | Description         |  |  |

| SNL1             | 1    | phase 1 sense low   |  |  |

| SNH1             | 2    | phase 1 sense high  |  |  |

| GND              | 3    | ground              |  |  |

| G1               | 4    | phase 1 gate driver |  |  |

| VGG              | 5    | gate driver supply  |  |  |

| G2               | 6    | not connected       |  |  |

| GND              | 7    | ground              |  |  |

| SNH2             | 8    | phase 2 sense high  |  |  |

| SNL2             | 9    | phase 2 sense low   |  |  |

| n.c.             | 10   | not connected       |  |  |

| FB1 <sup>2</sup> | 11   | feedback, output 1  |  |  |

| n.c.             | 12   | not connected       |  |  |

| VBAT             | 13   | battery supply      |  |  |

| n.c.             | 14   | not connected       |  |  |

| FB2[2]           | 15   | feedback, output 2  |  |  |

Table 2. Pin description[1] ...continued

| Symbol  | Pin | Description          |  |  |

|---------|-----|----------------------|--|--|

| n.c.    | 16  | not connected        |  |  |

| n.c.    | 17  | not connected        |  |  |

| i.c.[3] | 18  | internally connected |  |  |

| n.c.    | 19  | not connected        |  |  |

| n.c.    | 20  | not connected        |  |  |

| n.c.    | 21  | not connected        |  |  |

| n.c.    | 22  | not connected        |  |  |

| n.c.    | 23  | not connected        |  |  |

| i.c.[3] | 24  | internally connected |  |  |

| n.c.    | 25  | not connected        |  |  |

| SDI     | 26  | SPI Data Input       |  |  |

| SCLK    | 27  | SPI Clock            |  |  |

| CSB     | 28  | SPI chip select      |  |  |

| EN      | 29  | enable signal        |  |  |

| VCC     | 30  | external 5 V supply  |  |  |

| SDO     | 31  | SPI Data Out         |  |  |

| GND     | 32  | chip ground          |  |  |

<sup>[1]</sup> n.c. pins are internally not connected and can be left floating or can be connected to any voltage level.

For enhanced thermal and electrical performance, the exposed center pad of the package should be soldered to board ground (and not to any other voltage level).

<sup>[2]</sup> See Figure 4 and Figure 14 for recommend connections for pin FB1 and pin FB2.

<sup>[3]</sup> Internally connected pins should be connected to GND.

# 8. Functional description

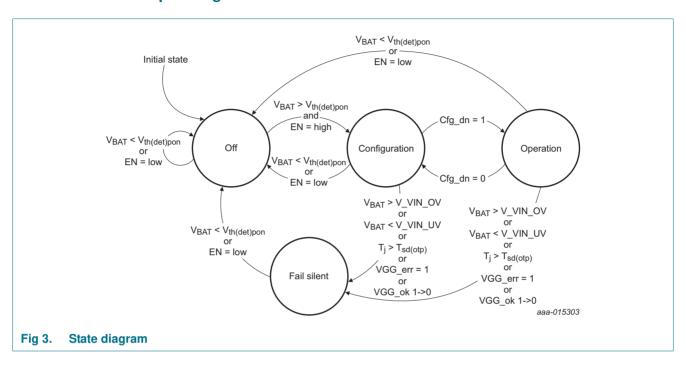

# 8.1 Operating modes

Table 3. Operating modes

| Mode          | Control registers | Configuration registers | Diagnostic IC registers | VGG                   | Vout1                 | Remark                                                                  |

|---------------|-------------------|-------------------------|-------------------------|-----------------------|-----------------------|-------------------------------------------------------------------------|

| Off           | n.a.              | n.a.                    | n.a.                    | Off                   | Off                   | device is off, no communication possible                                |

| Configuration | Read/write        | Read/write              | Read                    | Off                   | Off                   | VGG is off if the output was not previously enabled                     |

|               |                   |                         |                         | According to register | Off                   | VGG stays on as soon as the output has been enabled                     |

| Operation     | Read/write        | Read                    | Read                    | Locked                | According to register | configuration register is locked                                        |

| Fail silent   | Read/write        | Read <sup>[1]</sup>     | Read                    | Off                   | Off                   | communication possible, but the output is off; restart via EN possible. |

<sup>[1]</sup> Setting the bit cfg\_dn to 0 also grants write access to the configuration registers.

#### 8.1.1 Off mode

The ASL2500SHN switches to off mode, if the input voltage drops below the power-on detection threshold ( $V_{th(det)pon}$ ) or the EN pin is low.

The SPI interface and output are turned off when the ASL2500SHN is in the Off mode.

## 8.1.2 Configuration mode

The ASL2500SHN switches from off mode to configuration mode, as soon the input voltage is above the power-on detection threshold ( $V_{th(det)pon}$ ) and pin EN is high.

The configuration registers can be set when the ASL2500SHN is in the Configuration mode.

#### 8.1.3 Operation mode

The ASL2500SHN switches from configuration mode to operation mode, as soon as the configuration done bit is set. Once the bit is set, the configuration registers are locked and cannot be changed.

In operation mode, the output is available as configured via the SPI interface. Setting the bits Vout1en or Vout2en, starts up VGG. Once VGG is in regulation (signaled by bit VGG\_ok), the output voltages Vout1 and Vout2 are turned on accordingly. When the converters are on, the battery monitoring functionality is available.

#### 8.1.4 Fail silent mode

The ASL2500SHN switches from Operation mode to Fail silent mode, when the junction temperature exceeds the over temperature shutdown threshold or a VGG error is detected. It will also switch modes when the input voltage is below the under voltage detection threshold or above the over voltage detection threshold.

In Fail silent mode, all outputs are turned off and only the SPI interface remains operational.

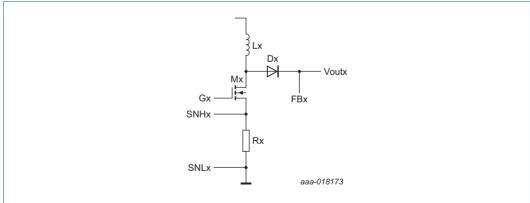

## 8.2 Boost converter configuration

The ASL2500SHN is an automatic boost converter IC delivering constant DC-to-DC voltage to a load. It has a fixed frequency current-mode control for an enhanced stable operation.

The ASL2500SHN offers two phases. Each phase consists of a coil, a resistor, a MOSFET and a diode as shown in Figure 4.

Fig 4. Phase of the boost converter with IC and application connections

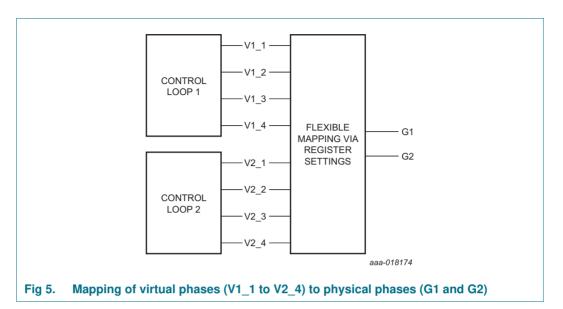

To allow a flexible use of the ASL2500SHN, the configuration is based on virtual phases. These phases are then mapped to a real, physical phase according to the physical connections and conditions of the circuitry around the ASL2500SHN as shown in Figure 5.

# 8.2.1 Configuration of the virtual phases

The ASL2500SHN can generate up to four internal phases for up to two virtual outputs. With the internal phase control enable registers, it can be selected, how many virtual phases are generated for the individual virtual outputs.

Table 4. Internal phase control enable for output 1, address 0x0Bh

| Bit | Symbol  | Description     | Value | Function                                       |

|-----|---------|-----------------|-------|------------------------------------------------|

| 7:4 |         | reserved        | 0000  | reserved; should remain cleared for future use |

| 3   | EN_P4_1 | phase 4 enabled | 0     | phase 4 is off                                 |

|     |         |                 | 1     | phase 4 is enabled                             |

| 2   | EN_P3_1 | phase 3 enabled | 0     | phase 3 is off                                 |

|     |         |                 | 1     | phase 3 is enabled                             |

| 1   | EN_P2_1 | phase 2 enabled | 0     | phase 2 is off                                 |

|     |         |                 | 1     | phase 2 is enabled                             |

| 0   | EN_P1_1 | phase 1 enabled | 0     | phase 1 is off                                 |

|     |         |                 | 1     | phase 1 is enabled                             |

Table 5. Internal phase control enable for output 2, address 0x0Ch

| Bit | Symbol        | Description     | Value | Function                                       |

|-----|---------------|-----------------|-------|------------------------------------------------|

| 7:4 |               | reserved        | 0000  | reserved; should remain cleared for future use |

| 3   | EN_P4_2       | phase 4 enabled | 0     | phase 4 is off                                 |

|     |               |                 | 1     | phase 4 is enabled                             |

| 2   | EN_P3_2 phase | phase 3 enabled | 0     | phase 3 is off                                 |

|     |               |                 | 1     | phase 3 is enabled                             |

| 1   | EN_P2_2       | phase 2 enabled | 0     | phase 2 is off                                 |

|     |               |                 | 1     | phase 2 is enabled                             |

| 0   | EN_P1_2       | phase 1 enabled | 0     | phase 1 is off                                 |

|     |               |                 | 1     | phase 1 is enabled                             |

## 8.2.2 Association of physical phases to the output voltages

Each phase that the ASL2500SHN offers, must be associated to one of the outputs. Multiple combinations are possible here, e.g. all phases to one of the outputs, or 1 phase to one output and 1 phase to another one.

Table 6. Gate driver output, address 0x02h

| Bit | Symbol | Description         | Value   | Function                                     |

|-----|--------|---------------------|---------|----------------------------------------------|

| 7:2 |        | reserved            | 0000000 | reserved; should remain clear for future use |

| 1   | O_G2   | association phase 2 | 0       | phase 2 is connected to Vout1                |

|     |        |                     | 1       | phase 2 is connected to Vout2                |

| 0   | O_G1   | association phase 1 | 0       | phase 1 is connected to Vout1                |

|     |        |                     | 1       | phase 1 is connected to Vout2                |

#### 8.2.3 Association of connected phases to the internal phase generation

The physical phase that the ASL2500SHN offers, must be associated to one of the virtual phases of one of the outputs. It is established with the gate driver phase and phase select configuration registers.

Table 7. Gate driver phase, address 0x0Fh

| Bit | Symbol | Description         | Value  | Function                                     |

|-----|--------|---------------------|--------|----------------------------------------------|

| 7:2 |        | reserved            | 000000 | reserved; should remain clear for future use |

| 1   | O_GP2  | association phase 2 | 0      | phase 2 is connected to Vout1                |

|     |        |                     | 1      | phase 2 is connected to Vout2                |

| 0   | O_GP1  | association phase 1 | 0      | phase 1 is connected to Vout1                |

|     |        |                     | 1      | phase 1 is connected to Vout2                |

Table 8. Phase select configuration, address 0x10h

| Bit | Symbol      | Description       | Value | Function                                     |

|-----|-------------|-------------------|-------|----------------------------------------------|

| 7:4 |             | reserved          | 0000  | reserved; should remain clear for future use |

| 3:2 | Phsel2[1:0] | phase select gate | 0x0h  | routing from phase 1                         |

|     |             | driver 2          | 0x1h  | routing from phase 2                         |

|     |             |                   | 0x2h  | routing from phase 3                         |

|     |             |                   | 0x3h  | routing from phase 4                         |

| 1:0 | Phsel1[1:0] | phase select gate | 0x0h  | routing from phase 1                         |

|     |             | driver 1          | 0x1h  | routing from phase 2                         |

|     |             |                   |       | routing from phase 3                         |

|     |             |                   | 0x3h  | routing from phase 4                         |

## 8.2.4 Enabling of connected phases

The gate driver enable register is used to configure which of the phases is active.

Table 9. Gate driver enable, address 0x01h

| Bit | Symbol | Description     | Value   | Function                                     |

|-----|--------|-----------------|---------|----------------------------------------------|

| 7:2 |        | reserved        | 0000000 | reserved; should remain clear for future use |

| 1   | EN_G2  | phase 2 enabled | 0       | phase 2 is off                               |

|     |        |                 | 1       | phase 2 is enabled                           |

| 0   | EN_G1  | phase 1 enabled | 0       | phase 1 is off                               |

|     |        |                 | 1       | phase 1 is enabled                           |

#### 8.2.5 Configuration of the boost converter frequencies

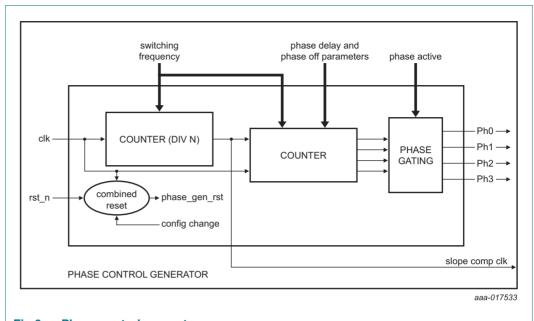

The operation frequency of the boost converters can be set with via several SPI registers. To ensure a stable phase delay between the different phases, all timings are derived from the same oscillator. An integer number downscales the internal oscillator frequency for each regulation loop. The slower clock controls the off-time of a phase and the delay from one phase of the regulation loop to the next internal phase. The number of phases determinates finally when the phase is turned on again and so defines the operation frequency of the boost converter.

Fig 6. Phase control generator

Table 10. Clock divider for Vout1, address 0x09h

| Bit | Symbol | Description                        | Value | Function                           |

|-----|--------|------------------------------------|-------|------------------------------------|

| 7:0 |        | clock divider for output voltage 1 | 0x00h | clock is not divided               |

|     | [7:0]  |                                    |       | clock is divided by clkdiv1[7:0]+1 |

|     |        |                                    | 0xFFh | clock is divided by 256            |

Table 11. Clock divider for Vout2, address 0x0Ah

| Bit | Symbol  | Description                        | Value | Function                           |

|-----|---------|------------------------------------|-------|------------------------------------|

| 7:0 | Clkdiv1 | clock divider for output voltage 2 | 0x00h | clock is not divided               |

|     | [7:0]   |                                    |       | clock is divided by clkdiv2[7:0]+1 |

|     |         |                                    | 0xFFh | clock is divided by 256            |

Table 12. Phase-off time and phase delay of output 1, address 0x0Dh

| Bit | Symbol | Description                       | Value | Function                                                           |

|-----|--------|-----------------------------------|-------|--------------------------------------------------------------------|

| 7:3 |        | delay to next<br>phase of output1 | 0x0h  | phase delay is 1 clock period of the divided clock                 |

|     |        |                                   |       | phase delay is<br>Phdel1[4:0]+1 clock period of the divided clock  |

|     |        |                                   | 0x1Fh | phase delay is 32 clock periods of the divided clock               |

| 2:0 | Phoff1 | phase-off time of                 | 0x0h  | phase-off time is 1 clock period of the divided clock              |

|     | [2:0]  | output1                           |       | phase-off time is<br>Phoff1[2:0] clock period of the divided clock |

|     |        |                                   | 0x7h  | phase-off time is 7 clock periods of the divided clock             |

Table 13. Phase-off time and phase delay of output 2, address 0x0Eh

| Bit | Symbol                 | Description       | Value                                                             | Function                                                           |

|-----|------------------------|-------------------|-------------------------------------------------------------------|--------------------------------------------------------------------|

| 7:3 |                        |                   | 0x0h                                                              | phase delay is 1 clock period of the divided clock                 |

|     | [4:0] phase of output2 |                   | phase delay is<br>Phdel2[4:0]+1 clock period of the divided clock |                                                                    |

|     |                        |                   | 0x1Fh                                                             | phase delay is 32 clock periods of the divided clock               |

| 2:0 | Phoff2                 | phase-off time of | 0x0h                                                              | phase-off time is 1 clock period of the divided clock              |

|     | [2:0]                  | output2           |                                                                   | phase-off time is<br>Phoff2[2:0] clock period of the divided clock |

|     |                        |                   | 0x7h                                                              | phase-off time is 7 clock periods of the divided clock             |

**Note:** To obtain the best performance of the internal slope compensation, keep the settings of the delay between the phases as close to 32 as possible.

#### 8.2.6 Control loop parameter setting

The ASL2500SHN is able to operate with a wide range of external components and offers wide range of operating frequencies. To achieve the maximum performance for each set of operation conditions, set the control loop parameters according to the external components and the operating frequency.

Table 14. Loop filter proportional configuration, address 0x11h

| Bit | Symbol                                  | Description  | Value                                                | Function                             |

|-----|-----------------------------------------|--------------|------------------------------------------------------|--------------------------------------|

| 7:4 | Prop2[3:0]                              | proportional | 0x0h                                                 | proportional factor output 2 is 0.05 |

|     | factor output 2                         |              | proportional factor output 2 is Prop2[3:0]*0.05+0.05 |                                      |

|     |                                         | 0xFh         | proportional factor output 2 is 0.8                  |                                      |

| 3:0 | Prop1[3:0] proportional factor output 1 | 0x0h         | proportional factor output 1 is 0.05                 |                                      |

|     |                                         |              | proportional factor output 1 is Prop1[3:0]*0.05+0.05 |                                      |

|     |                                         |              | 0xFh                                                 | proportional factor output 1 is 0.8  |

Table 15. Loop filter integral configuration, address 0x12h

| Symbol                                   | Description | Value                                                             | Function                                            |

|------------------------------------------|-------------|-------------------------------------------------------------------|-----------------------------------------------------|

| output 2                                 | 0x0h        | integral factor output 2 is 0.005                                 |                                                     |

|                                          |             | integral factor output 2 is Integ2[3:0]*0.005+0.005               |                                                     |

|                                          |             | 0xFh                                                              | integral factor output 2 is 0.08                    |

| 3:0 Integ1[3:0] integral factor output 1 | 0x0h        | integral factor output 1 is 0.005                                 |                                                     |

|                                          |             |                                                                   | integral factor output 1 is Integ1[3:0]*0.005+0.005 |

|                                          |             | 0xFh                                                              | integral factor output 1 is 0.08                    |

|                                          | Integ2[3:0] | Integ2[3:0] integral factor output 2  Integ1[3:0] integral factor | Integ2[3:0] integral factor output 2                |

Table 16. Slope compensation configuration, address 0x13h

| Bit | Symbol       | Description                              | Value | Function                                            |

|-----|--------------|------------------------------------------|-------|-----------------------------------------------------|

| 7:4 | Slpcmp2[3:0] | slope                                    | 0x0h  | slope compensation factor output 2 = 112 k $\Omega$ |

|     |              | compensation factor output 2             | 0x1h  | slope compensation factor output 2 = 84 k $\Omega$  |

|     |              | lactor output 2                          | 0x2h  | slope compensation factor output 2 = 70 k $\Omega$  |

|     |              |                                          | 0x4h  | slope compensation factor output 2 = 56 k $\Omega$  |

|     |              |                                          | 0x8h  | slope compensation factor output 2 = 28 k $\Omega$  |

| 3:0 | Slpcmp1[3:0] | slope<br>compensation<br>factor output 1 | 0x0h  | slope compensation factor output 1 = 112 k $\Omega$ |

|     |              |                                          | 0x1h  | slope compensation factor output 1 = 84 k $\Omega$  |

|     |              |                                          | 0x2h  | slope compensation factor output 1 = 70 k $\Omega$  |

|     |              |                                          | 0x4h  | slope compensation factor output 1 = 56 k $\Omega$  |

|     |              |                                          | 0x8h  | slope compensation factor output 1 = 28 k $\Omega$  |

Table 17. Current sense slope resistor configuration, address 0x14h

| Bit | Symbol                                  | Description                     | Value         | Function       |

|-----|-----------------------------------------|---------------------------------|---------------|----------------|

| 7:4 |                                         |                                 |               |                |

| 3:2 | Slpr2[1:0] slope resistor               | 0x0h                            | 2'b00 - 250 Ω |                |

|     |                                         | configuration for gate driver 2 | 0x1h          | 2'b01 - 500 Ω  |

|     |                                         | ioi gate diivei 2               | 0x2h          | 2'b10 - 1000 Ω |

|     |                                         |                                 | 0x3h          | 2'b11 - 1500 Ω |

| 1:0 | Slpr1[1:0] slope resistor configuration | 0x0h                            | 2'b00 - 250 Ω |                |

|     |                                         | configuration for gate driver 1 | 0x1h          | 2'b01 - 500 Ω  |

|     |                                         |                                 | 0x2h          | 2'b10 - 1000 Ω |

|     |                                         |                                 | 0x3h          | 2'b11 - 1500 Ω |

# 8.3 Output voltage programmability

The ASL2500SHN provides the possibility to program the output voltage and output overvoltage protection of the output via the SPI interface.

#### 8.3.1 Output voltage target programming

The target output voltage can be programmed via the Output voltage registers. As the ASL2500SHN is a boost converter, the output voltage cannot be lower than the supply voltage minus the drop of the converter diode (Dx in Figure 4).

Table 18. Output voltage 1 register, address 0x03h

| Bit | Symbol        | Description    | Value | Function                                            |

|-----|---------------|----------------|-------|-----------------------------------------------------|

| 7:0 | V_Vout_1[7:0] | target voltage | 0x00h | output 1 is turned off                              |

|     | out           | output 1       |       | target voltage output 1<br>= 0.3606 * V_Vout_1[7:0] |

|     |               |                | 0xFFh | maximum target output voltage = 90 V                |

Table 19. Output voltage 2 register, address 0x04h

| Bit | Symbol        | Description                | Value | Function                                            |

|-----|---------------|----------------------------|-------|-----------------------------------------------------|

| 7:0 | V_Vout_2[7:0] | target voltage<br>output 2 | 0x00h | output 2 is turned off                              |

|     |               |                            |       | target voltage output 2<br>= 0.3606 * V_Vout_2[7:0] |

|     |               |                            | 0xFFh | maximum target output voltage = 90 V                |

#### 8.3.2 Output overvoltage protection programming

Due to fast changes in the supply or the output, it is possible that the output voltage is disturbed. To avoid high voltages that may result into damage of attached components, the ASL2500SHN offers a programmable overvoltage protection threshold. Once the output voltage is above this threshold, the gate pin of the output stops toggling. It results in a halt of the energy delivery to the output.

Once the output voltage recovers and is below the threshold again, the gate pin starts toggling again. The regulation loop regulates the output back to the target value.

For stable operation of the device, the limit voltage output register should be programmed around 5 V higher than the output voltage registers.

Table 20. Limit voltage output 1 register, address 0x05h

| Bit | Symbol         | Description   | Value | Function                                               |

|-----|----------------|---------------|-------|--------------------------------------------------------|

| 7:0 | Vmax_Vout_1    | limit voltage | 0x00h | output 1 is turned off                                 |

|     | [7:0] output 1 | output 1      |       | target voltage output 1<br>= 0.3606 * Vmax_Vout_1[7:0] |

|     |                |               | 0xFFh | maximum output over voltage protection output 1 = 90 V |

Table 21. Limit voltage output 2 register, address 0x06h

| Bit | Symbol      | Description   | Value | Function                                               |

|-----|-------------|---------------|-------|--------------------------------------------------------|

| 7:0 | Vmax_Vout_2 | limit voltage | 0x00h | output 2 is turned off                                 |

|     | [7:0]       | output 2      |       | target voltage output 2<br>= 0.3606 * Vmax_Vout_2[7:0] |

|     |             |               | 0xFFh | maximum output over voltage protection output 2 = 90 V |

#### 8.4 Coil peak current limitation

The ASL2500SHN offers a function to limit peak current inside the coil and therefore to limit the input current for the system. Furthermore this functionality can be used to avoid magnetic saturation of the coils. It also allows some soft start feature to be realized with this function.

With the Max phase current Vout1 register, the maximum peak current for the phase can be configured. Once the voltage between pins SNSLx and SNSHx reaches this level, the gate will be turned off until the next switching cycle. To avoid sub harmonic oscillations when the coil peak current limitation is becoming active, the slope compensation remains active. It reduces the coil peak current towards the end of the switching cycle to ensure stable operation of the system.

In order to avoid that this function interferes with the normal regulation, the limit should be placed well above the maximum expected current.

Table 22. Maximum phase current Vout1 register, address 0x07h

| Bit | Symbol                | Description | Value              | Function                                                                                         |

|-----|-----------------------|-------------|--------------------|--------------------------------------------------------------------------------------------------|

| 7:0 | limitation for phases | 0x00h       | no current allowed |                                                                                                  |

|     |                       |             |                    | maximum peak current = (I_max_per_phase_Vout1 [7:0] * 1.8 V / 256 - 0.24 V) / R <sub>sense</sub> |

|     |                       | Vout1       | 0x80               | max allowed setting = $(128/255*1.8V-0.24) V / R_{sense}$                                        |

|     |                       |             | not allowed        |                                                                                                  |

|     |                       |             | 0xFFh              | not allowed                                                                                      |

Table 23. Maximum phase current Vout2 register, address 0x08h

| Bit | Symbol | Description                       | Value              | Function                                                                                         |

|-----|--------|-----------------------------------|--------------------|--------------------------------------------------------------------------------------------------|

| 7:0 |        | 0x00h                             | no current allowed |                                                                                                  |

|     |        | limitation for phases assigned to |                    | maximum peak current = (I_max_per_phase_Vout2 [7:0] * 1.8 V / 256 - 0.24 V) / R <sub>sense</sub> |

|     |        | Vout2                             | 0x80               | max allowed setting = $(128/255*1.8V-0.24) V / R_{sense}$                                        |

|     |        |                                   | not allowed        |                                                                                                  |

|     |        |                                   | 0xFFh              | not allowed                                                                                      |

# 8.5 Enabling the output voltage

The ASL2500SHN provides two independent output voltages. In operation mode, the output voltages are turned on with the bit Vout1en and Vout2en.

As soon as one of the outputs is turned on, the VGG voltage regulator is turned on. After  $t_{VGG\ startup}$  the gate drivers start switching, provided the bit VGG\_ok is set.

Table 24. Function control register, address 0x00h

| Bit | Symbol                    | Description            | Value                                    | Function                                                   |

|-----|---------------------------|------------------------|------------------------------------------|------------------------------------------------------------|

| 7:4 |                           | reserved               | 0000                                     | reserved; should remain cleared for future use             |

| 3   | Cnt_CSB count chip        |                        | 0                                        | chip select low count feature is disabled                  |

|     | select time               | 1                      | chip select low count feature is enabled |                                                            |

| 2   | 2 Vout2en enable output 2 | 0                      | output 2 is turned off                   |                                                            |

|     |                           | output 2               | 1                                        | output 2 is turned on when the device is in operation mode |

| 1   | Vout1en                   | enable                 | 0                                        | output 1 is turned off                                     |

|     |                           | output 1               | 1                                        | output 1 is turned on when the device is in operation mode |

| 0   | Cfg_dn                    | configuration done bit | 0                                        | device is in configuration mode - no configuration lock    |

|     |                           |                        | 1                                        | device is in operation mode - configuration lock is active |

## 8.6 Frequency trimming

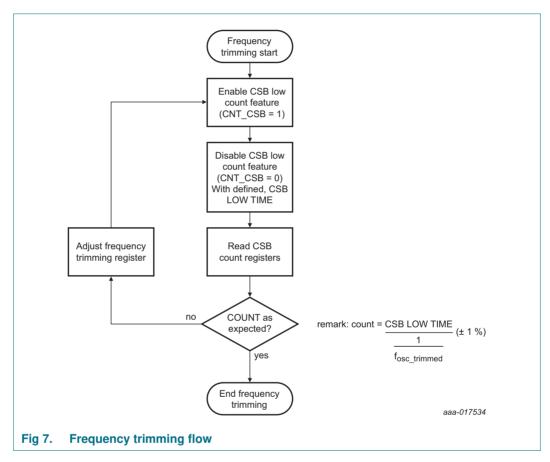

To ensure the ASL2500SHN operates inside the specified oscillator frequency range, it is mandatory to adjust the internal oscillator frequency of the device.

To measure the actual internal frequency, the device is measuring the time that the CSB pin is low during an SPI transfer. This time information can be used to adjust the oscillator frequency of the device. The recommended procedure for the time adjustment is shown in Figure 7.

At the start of the sequence, the CSB low count feature is activated. It is done by setting the Cnt\_CSB Bit high in the Frequency trimming control register (Bit 3; register 0x00h). The device now measures the time with its internal time domain each time the CSB pin is low. It makes this information available in the CSB count registers. To allow an exact stable reading, set the Cnt\_CSB Bit low again with an accurately known CSB low time. Setting the bit low freezes the count registers. They store the last value, which in this case is the command that set the Cnt\_CSB bit low.

The CSB count registers contain the count of the CSB low time of the last SPI command the CSB low count feature was enabled. CSB count register 1 contains the bits 7 to 0 of the counter, while the CSB count register 2 contains the bits 15:8.

Table 25. CSB count register 1, address 0x41h

| Bit | Symbol       | Description   | Value | Function               |

|-----|--------------|---------------|-------|------------------------|

| 7:0 | CSB_cnt[7:0] | CSB count low |       | count value (bits 7:0) |

Table 26. CSB count register 2, address 0x42h

| Bit | Symbol        | Description    | Value | Function                |

|-----|---------------|----------------|-------|-------------------------|

| 7:0 | CSB_cnt[15:8] | CSB count high |       | count value (bits 15:8) |

The count, the CSB count register returns, should correspond to the real time of the CSB low time. 1 count should correspond with  $1/f_{osc\ trimmed}$  (see <u>Table 44</u>).

When the count that the CSB count registers return, deviates from the applied CSB low time, the device internal timing must be adjusted by modifying the frequency trimming register.

Table 27. Frequency trimming register, address 0x1Ch

| Bit | Symbol         | Description         | Value  | Function                    |

|-----|----------------|---------------------|--------|-----------------------------|

| 7:6 |                | reserved            |        | not allowed                 |

| 5:0 | Freq_trim[5:0] | frequency trim bits | 010001 | default frequency -33.33 %  |

|     |                |                     | 010011 | default frequency -30.56 %  |

|     |                |                     | 010101 | default frequency –27.78 %  |

|     |                |                     | 010111 | default frequency -25.00 %  |

|     |                |                     | 011001 | default frequency -22.22 %  |

|     |                |                     | 011011 | default frequency -19.44 %  |

|     |                |                     | 011101 | default frequency -16.67 %  |

|     |                |                     | 011111 | default frequency -13.89 %  |

|     |                |                     | 000001 | default frequency -11.11 %  |

|     |                |                     | 000011 | default frequency -8.33 %   |

|     |                |                     | 000101 | default frequency -5.56 %   |

|     |                |                     | 000111 | default frequency -2.78 %   |

|     |                |                     | 001001 | default frequency           |

|     |                |                     | 001011 | default frequency + 2.78 %  |

|     |                |                     | 001101 | default frequency + 5.56 %  |

|     |                |                     | 001111 | default frequency + 8.33 %  |

|     |                |                     | 110001 | default frequency + 11.11 % |

|     |                |                     | 110011 | default frequency + 13.89 % |

|     |                |                     | 110101 | default frequency + 16.67 % |

|     |                |                     | 110111 | default frequency + 19.44 % |

|     |                |                     | 111001 | default frequency + 22.22 % |

|     |                |                     | 111011 | default frequency + 25.00 % |

|     |                |                     | 111101 | default frequency + 27.78 % |

|     |                |                     | 111111 | default frequency + 30.56 % |

|     |                |                     | 100001 | default frequency + 33.33 % |

|     |                |                     | 100011 | default frequency + 36.11 % |

|     |                |                     | others | not allowed                 |

To ensure that the adjustment had the desired effect, restart the procedure and check the count with the new settings in the frequency trimming register.

When the device internal time matches the applied CSB low time, no further adjustment is needed and the trimming procedure is finished.

## 8.7 Gate voltage supply

The ASL2500SHN has an integrated linear regulator to generate the supply voltage of the gate drivers, which is internally connected to the pin VGG. The voltage generated by the linear regulator can be set via the VGG control register.

Table 28. VGG control register, address 0x15h

| Bit | Symbol   | Description     | Value | Function                         |

|-----|----------|-----------------|-------|----------------------------------|

| 7:0 | VGG[7:0] | supply voltage  | 0x00h | not allowed                      |

|     |          | for gate driver |       | not allowed                      |

|     |          |                 | 0x5Dh | maximum output voltage = 10.04 V |

|     |          |                 |       | (255- VGG[7:0]) * 62 mV          |

|     |          |                 | 0xB7h | minimum output voltage = 4.46 V  |

|     |          |                 |       | not allowed                      |

|     |          |                 | 0xFFh | not allowed                      |

The actual value of VGG can deviate from the target setting due to the tolerances of the VGG regulation loop (see  $V_{o(reg)acc}$  in Table 43).

When a setting between 0x00h and 0x5Dh is used, the resulting gate driver target voltage exceeds the limiting values of the IC. The limiting values of the VGG pin can also be violated with target settings of 0xA6h to 0x5Dh due to these tolerances. A violation of the limiting values with the actual VGG voltage must be avoided. To ensure that only allowed settings are used for the gate driver target voltage, an immediate read back of the programmed value is required after setting the registers.

If a setting between 0xFFh and 0xB7h is used, the device may not start up VGG. If the device operates, parameters of VGG are not guaranteed.

## 8.7.1 Gate voltage supply diagnostics

The diagnostic options for the gate voltage supply are:

- VGG available. Details can be found in Section 8.10

- VGG protection active. Details can be found in Section 8.10

#### 8.8 Supply voltage monitoring

The ASL2500SHN is continuously measuring the voltage at pin Vbat, when at least one of the outputs is enabled and bit VGG\_ok is set. It allows the system to monitor the supply voltage without additional external components. It also offers the option to put an automatic under- and/or overvoltage protection in place.

**Note:** The VIN\_UV and VIN\_OV bits in the status register use the battery voltage measurement. Consequently the VIN\_UV and VIN\_OV bits are only reliable when at least one output is enabled.

#### 8.8.1 Battery voltage measurement

The ASL2500SHN continuously measures the voltage at pin Vbat. The measurement result is available in the battery voltage register when the output is enabled.

Table 29. Battery voltage register, address 0x45h

| Bit | Symbol      | Description     | Value | Function                                  |

|-----|-------------|-----------------|-------|-------------------------------------------|

| 7:0 | V_VBAT[7:0] | Battery voltage | 0x00h | battery voltage = 0 V                     |

|     |             |                 |       | battery voltage = 0.3606 * V_VBAT[7:0]    |

|     |             |                 | 0xFFh | maximum measurable battery voltage = 90 V |

### 8.8.2 Undervoltage detection

The ASL2500SHN offers a variable undervoltage detection threshold. When the supply voltage drops below this threshold, the undervoltage detect bit is set, and fail silent mode is entered. The gate pin stops toggling and no more power is delivered to the output.

Table 30. Undervoltage threshold register, address 0x1Bh

| Bit | Symbol        | Description            | Value | Function                                                     |

|-----|---------------|------------------------|-------|--------------------------------------------------------------|

| 7:0 | V_VIN_UV[7:0] |                        | 0x00h | undervoltage detection threshold = 0 V                       |

|     |               | detection<br>threshold |       | under voltage detection threshold<br>= 0.3606 * V_VIN_UV[7:0 |

|     |               |                        | 0xFFh | maximum undervoltage detection threshold = 90 V              |

# 8.8.3 Overvoltage detection

The ASL2500SHN offers a variable overvoltage detection threshold. When the supply voltage rises above this threshold, the overvoltage detect bit is set, and fail silent mode is entered. The gate pin stops toggling and no more power is delivered to the output.

Table 31. Overvoltage threshold register, address 0x1Ah

| Bit | Symbol        | Description                                   | Value | Function                                                   |

|-----|---------------|-----------------------------------------------|-------|------------------------------------------------------------|

| 7:0 | V_VIN_OV[7:0] | /_VIN_OV[7:0] overvoltage detection threshold | 0x00h | overvoltage detection threshold = 0 V                      |

|     |               |                                               |       | overvoltage detection threshold<br>= 0.3606 * V_VIN_OV[7:0 |

|     |               |                                               | 0xFFh | maximum overvoltage detection threshold = 90 V             |

# 8.9 Junction temperature information

The ASL2500SHN provides a measurement of the IC junction temperature. The measurement information is available in the junction temperature register.

Table 32. Junction temperature register, address 0x46h

| Bit | Symbol          | Description | Value                                | Function                                                                |

|-----|-----------------|-------------|--------------------------------------|-------------------------------------------------------------------------|

| 7:0 | T_junction[7:0] | junction    |                                      | device junction temperature below -40 °C                                |

|     |                 | temperature | 0x18h                                | device junction temperature = -40 °C                                    |

|     |                 |             |                                      | device junction temperature<br>= T_junction[7:0] * (215/106) °C - 88 °C |

|     |                 | 0x82h       | device junction temperature ≥ 175 °C |                                                                         |

## 8.10 Diagnostic information

The diagnostic register contains useful information for diagnostic purposes. Details for each bit can be found in the following subchapters.

Table 33. Diagnostic register, address 0x5Fh

| Bit | Symbol   | Description                    | Value | Function                                                     |

|-----|----------|--------------------------------|-------|--------------------------------------------------------------|

| 7   | Vout1_ok | Vout1 regulated                | 0     | Vout1 is deviating from the target value                     |

|     |          |                                | 1     | Vout1 is regulated to the target value                       |

| 6   | Vout2_ok | Vout2 regulated                | 0     | Vout2 is deviating from the target value                     |

|     |          |                                | 1     | Vout2 is regulated to the target value                       |

| 5   | VGG_ok   | VGG regulation OK              | 0     | VGG is not available                                         |

|     |          |                                | 1     | VGG is available                                             |

| 4   | Tj_err   | device temperature is too high | 0     | device temperature below T <sub>sd(otp)</sub>                |

|     |          |                                | 1     | device temperature above T <sub>sd(otp)</sub>                |

| 3   | VIN_UV   | VIN under voltage              | 0     | no under voltage at VIN detected                             |

|     |          |                                | 1     | under voltage at VIN detected                                |

| 2   | VIN_OV   | VIN over voltage               | 0     | no over voltage at VIN detected                              |

|     |          |                                | 1     | over voltage at VIN detected                                 |

| 1   | SPI_err  | SPI error                      | 0     | last SPI command was executed correctly                      |

|     |          |                                | 1     | last SPI command was erroneous and has been discarded        |

| 0   | VGG_err  | VGG error                      | 0     | VGG overload protection not active                           |

|     |          |                                | 1     | VGG overload protection has turned on and VGG is deactivated |

#### 8.10.1 Bit VIN OV

The bit VIN OV depends on the battery monitoring functionality as described in Section 8.8. It indicates that the device has detected an overvoltage condition and entered fail silent mode. A write access to the diagnostic register or when the Off mode has been entered, clears the bit. Independent of the clearing of the bit, the device stays in fail silent mode.

#### 8.10.2 Bit VIN UV

The bit VIN UV depends on the battery monitoring functionality as described in Section 8.8. It indicates that the device has detected an undervoltage condition and entered fail silent mode. A write access to the diagnostic register or when the Off mode has been entered, clears the bit. Independent of the clearing of the bit, the device stays in fail silent mode.

# 8.10.3 Bit SPI err

The device is evaluating all SPI accesses to the device for the correctness of the commands. When the command is not allowed, the SPI err bit is set.

A write access to the diagnostic register or when the Off mode is entered, clears the bit.

#### 8.10.4 Bit Tj err

The bit Tj\_err indicates that the junction temperature has exceeded the maximum allowable temperature, and the device has entered Fail silent mode. A write access to the diagnostic register, or once Off mode has been entered, clears the bit. The device stays in Fail silent mode irrespective of the clearing of the bit. After leaving the OFF mode (at IC start-up), it is possible that bit Tj\_err is set. To avoid wrong diagnostics, clear the diagnostic register before it is evaluated.

#### 8.10.5 Bit VGG err

Bit VGG\_err is set when the gate driver does not reach the VGG\_ok window (when  $V_{VGG}$  is within range) within the regulator voltage start-up error time. Once bit VGG\_err is set, it indicates that an error on the gate driver has been detected and the device has entered Fail silent mode. A write access to the diagnostic register, or once Off mode has been entered, clears the bit. The device stays in Fail silent mode irrespective of the clearing of the bit.

#### 8.10.6 Bit VGG ok

The bit VGG\_ok indicates that the gate driver is regulated to the target voltage and allows the gate drivers to drive the gate driver pins. If the gate driver is outside the VGG\_ok window after t<sub>startup</sub>, and V<sub>VGG</sub> is within range, the device clears VGG\_ok bit and enters Fail silent mode.

#### 8.10.7 Bit Vout1 ok and Vout2 ok

The bits Vout1\_ok and Vout2\_ok indicate whether the output voltage is regulated to the target value or deviating from the target value. The bits are set as soon as the corresponding output is within the Vout\_ok window (when  $V_O$  is within the range) for more than  $t_{fltr(ov)}$ . The bits are cleared when the corresponding output is outside the Vout\_ok window for more than  $t_{fltr(ov)}$ .

#### 8.11 SPI

The ASL2500SHN uses an SPI interface to communicate with an external microcontroller. The SPI interface can be used for setting the LEDs current, reading and writing the control register.

#### 8.11.1 Introduction

The Serial Peripheral Interface (SPI) provides the communication link with the microcontroller, supporting multi-slave operations. The SPI is configured for full duplex data transfer, so status information is returned when new control data is shifted in. The interface also offers a read-only access option, allowing the application to read back the registers without changing the register content.

The SPI uses four interface signals for synchronization and data transfer:

- CSB SPI chip select; active LOW

- SCLK SPI clock default level is LOW due to low-power concept

- SDI SPI data input

- SDO SPI data output floating when pin CSB is HIGH

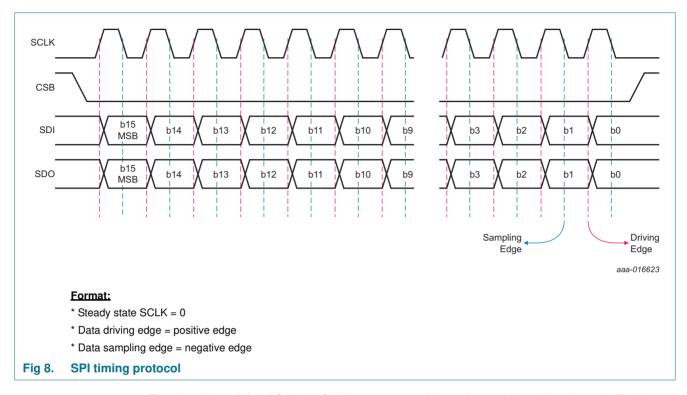

Bit sampling is performed on the falling clock edge and data is shifted on the rising clock edge as illustrated in Figure 8.

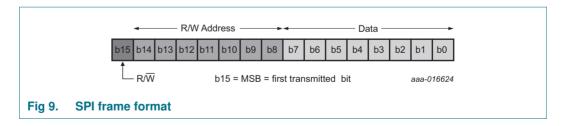

The data bits of the ASL2500SHN are arranged in registers of one-byte length. Each register is assigned to a 7-bit address. For writing into a register, 2 bytes must be sent to the LED driver. The first byte is an identifier byte that consists of the 7-bit address and one read-only bit. For writing, the read-only bit must be set to 0. The second byte is the data that is written into the register. So an SPI access consists of at least 16 bit.

Figure 9 together with Table 34 and Table 35 demonstrate the SPI frame format.

Table 34. SPI frame format for a transition to the device

| Bit  | Symbol | Description  | Value | Function         |

|------|--------|--------------|-------|------------------|

| 15   | b15    | R/W bits     | 0     | write access     |

|      |        |              | 1     | read access      |

| 14:8 | b14:8  | address bits |       | selected address |

| 7:0  | b7:0   | data bits    |       | transmitted data |

Table 35. SPI frame format for a transition from the device

| Bit  | Symbol | Description         | Value | Function <sup>[1]</sup>                                                                                      |

|------|--------|---------------------|-------|--------------------------------------------------------------------------------------------------------------|

| 8:15 | b8:15  | diagnostic register |       | content of diagnostic register                                                                               |

| 7:0  | b7:0   | data bits           |       | when previous command was a valid read command, content of the register that is supposed to be read          |

|      |        |                     |       | when previous command was a valid write command, new content of the register that was supposed to be written |

<sup>[1]</sup> The first SPI command after leaving the Off mode, will return 0x00h.

The master initiates the command sequence. The sequence begins with CSB pin pulled low and lasts until it is asserted high.

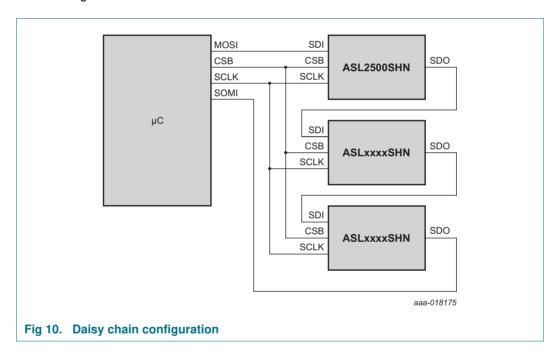

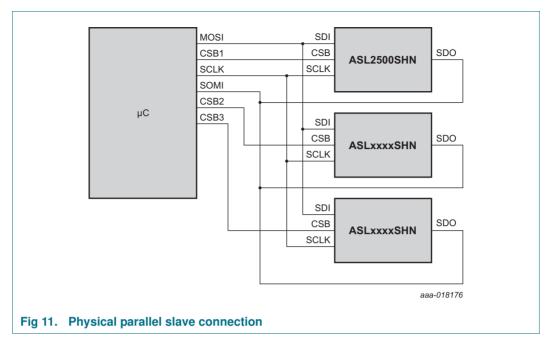

The ASL2500SHN also tolerates SPI accesses with a multiple of 16 bits. It allows a daisy chain configuration of the SPI.

During the SPI data transfer, the identifier byte and the actual content of the addressed registers is returned via the SDO pin. The same happens for pure read accesses. Here the read-only bit must be set to 1. The content of the data bytes that are transmitted to the ASL2500SHN is ignored.

The ASL2500SHN monitors the number of data bits that are transmitted. If the number is not 16, or a multiple of 16, then a write access is ignored and the SPI error indication bit is set.

#### 8.11.2 Typical use case illustration (Write/Read)

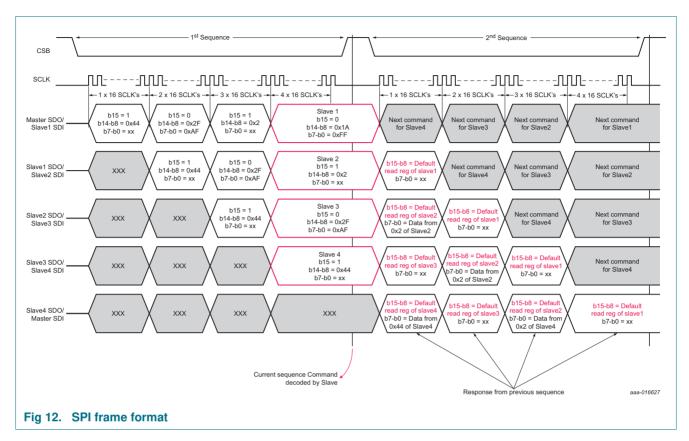

Consider a daisy chain scheme with one master connected to 4 slaves in Daisy chain fashion. The following commands are performed during one sequence (first sequence).

- Write data 0xFF to register 0x1A Slave 1

- Read from register 0x02 of Slave 2

- Write data 0xAF to register 0x2F of Slave 3

- · Read from register 0x44 of Slave 4

**Product data sheet**

## 8.11.3 Diagnostics for the SPI interface

The device is evaluating all SPI access to the device for the correctness of the commands. When the command is not allowed, the SPI\_err bit is set. The conditions that are considered as erratic accesses are:

- · SPI write is attempted to a read-only location or reserved location

- · SPI write is attempted during operation to a configuration register

- · SPI read is attempted from a reserved location

- SPI command does not consist of a multiple of 16 clock counts

If an SPI access is considered to be erratic, no modifications to a SPI register are made. The access after the erratic SPI command returns the diagnostic register and zero in the data field.

For details about the SPI err bit, see Section 8.10.3.

#### 8.11.4 Register map

The addressable register space amounts to 128 registers from 0x00 to 0x7F. They are separated in two groups as shown in <u>Table 36</u>. The register mapping is shown in <u>Table 37</u>, <u>Table 38</u>, <u>Table 39</u> and <u>Table 40</u>. The functional description of each bit can be found in the dedicated chapter.