Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### **Features**

- Core

- ARM® Cortex®-M3 revision 2.0 running at up to 64 MHz

- Memory Protection Unit (MPU)

- Thumb<sup>®</sup>-2 instruction set

- Pin-to-pin compatible with AT91SAM7S legacy products (48- and 64-pin versions)

- Memories

- From 64 to 256 Kbytes embedded Flash, 128-bit wide access, memory accelerator, single plane

- From 16 to 48 Kbytes embedded SRAM

- 16 Kbytes ROM with embedded bootloader routines (UART, USB) and IAP routines

- 8-bit Static Memory Controller (SMC): SRAM, PSRAM, NOR and NAND Flash support

- Memory Protection Unit (MPU)

- System

- Embedded voltage regulator for single supply operation

- Power-on-Reset (POR), Brown-out Detector (BOD) and Watchdog for safe operation

- Quartz or ceramic resonator oscillators: 3 to 20 MHz main power with Failure

Detection and optional low power 32.768 kHz for RTC or device clock

- High precision 8/12 MHz factory trimmed internal RC oscillator with 4 MHz default frequency for device startup. In-application trimming access for frequency adjustment

- Slow Clock Internal RC oscillator as permanent low-power mode device clock

- Two PLLs up to 130 MHz for device clock and for USB

- Temperature Sensor

- Up to 22 peripheral DMA (PDC) channels

- Low Power Modes

- Sleep and Backup modes, down to 3 µA in Backup mode

- Ultra low power RTC

- Peripherals

- USB 2.0 Device: 12 Mbps, 2668 byte FIFO, up to 8 bidirectional Endpoints. On-Chip Transceiver

- Up to 2 USARTs with ISO7816, IrDA®, RS-485, SPI, Manchester and Modem Mode

- Two 2-wire UARTs

- Up to 2 Two Wire Interface (I2C compatible), 1 SPI, 1 Serial Synchronous Controller (I2S), 1 High Speed Multimedia Card Interface (SDIO/SD Card/MMC)

- Up to 6 Three-Channel 16-bit Timer/Counter with capture, waveform, compare and PWM mode. Quadrature Decoder Logic and 2-bit Gray Up/Down Counter for Stepper Motor

- 4-channel 16-bit PWM with Complementary Output, Fault Input, 12-bit Dead Time Generator Counter for Motor Control

- 32-bit Real-time Timer and RTC with calendar and alarm features

- Up to 15-channel, 1Msps ADC with differential input mode and programmable gain stage

- One 2-channel 12-bit 1Msps DAC

- One Analog Comparator with flexible input selection, Selectable input hysteresis

- 32-bit Cyclic Redundancy Check Calculation Unit (CRCCU)

- I/O

- Up to 79 I/O lines with external interrupt capability (edge or level sensitivity), debouncing, glitch filtering and on-die Series Resistor Termination

- Three 32-bit Parallel Input/Output Controllers, Peripheral DMA assisted Parallel Capture Mode

- Packages

- 100-lead LQFP, 14 x 14 mm, pitch 0.5 mm/100-ball LFBGA, 9 x 9 mm, pitch 0.8 mm

- 64-lead LQFP, 10 x 10 mm, pitch 0.5 mm/64-pad QFN 9x9 mm, pitch 0.5 mm

- 48-lead LQFP, 7 x 7 mm, pitch 0.5 mm/48-pad QFN 7x7 mm, pitch 0.5 mm

# AT91SAM ARM-based Flash MCU

# **SAM3S Series**

# Summary

**NOTE:** This is a summary document. The complete document is available on the Atmel website at www.atmel.com.

# 1. SAM3S Description

Atmel's SAM3S series is a member of a family of Flash microcontrollers based on the high performance 32-bit ARM Cortex-M3 RISC processor. It operates at a maximum speed of 64 MHz and features up to 256 Kbytes of Flash and up to 48 Kbytes of SRAM. The peripheral set includes a Full Speed USB Device port with embedded transceiver, a High Speed MCI for SDIO/SD/MMC, an External Bus Interface featuring a Static Memory Controller providing connection to SRAM, PSRAM, NOR Flash, LCD Module and NAND Flash, 2x USARTs, 2x UARTs, 2x TWIs, 3x SPI, an I2S, as well as 1 PWM timer, 6x general-purpose 16-bit timers, an RTC, an ADC, a 12-bit DAC and an analog comparator.

The SAM3S series is ready for capacitive touch thanks to the QTouch library, offering an easy way to implement buttons, wheels and sliders

The SAM3S device is a medium range general purpose microcontroller with the best ratio in terms of reduced power consumption, processing power and peripheral set. This enables the SAM3S to sustain a wide range of applications including consumer, industrial control, and PC peripherals.

It operates from 1.62V to 3.6V and is available in 48-, 64- and 100-pin QFP, 48- and 64-pin QFN, and 100-pin BGA packages.

The SAM3S series is the ideal migration path from the SAM7S series for applications that require more performance. The SAM3S series is pin-to-pin compatible with the SAM7Sseries.

#### 1.1 Configuration Summary

The SAM3S series devices differ in memory size, package and features list. Table 1-1 below summarizes the configurations of the device family

**Table 1-1.** Configuration Summary

| Device  | Flash                      | SRAM      | Timer<br>Counter<br>Channels | GPIOs | UART/<br>USARTs    | ADC    | 12-bit<br>DAC<br>Output | External Bus<br>Interface                        | HSMCI            | Package           |

|---------|----------------------------|-----------|------------------------------|-------|--------------------|--------|-------------------------|--------------------------------------------------|------------------|-------------------|

| SAM3S4C | 256 Kbytes<br>single plane | 48 Kbytes | 6                            | 79    | 2/2 <sup>(1)</sup> | 16 ch. | 2                       | 8-bit data,<br>4 chip selects,<br>24-bit address | 1 port<br>4 bits | LQFP100<br>BGA100 |

| SAM3S4B | 256 Kbytes<br>single plane | 48 Kbytes | 3                            | 47    | 2/2                | 10 ch. | 2                       | -                                                | 1 port<br>4 bits | LQFP64<br>QFN 64  |

| SAM3S4A | 256 Kbytes<br>single plane | 48 Kbytes | 3                            | 34    | 2/1                | 8 ch.  | -                       | -                                                | -                | LQFP48<br>QFN 48  |

| SAM3S2C | 128 Kbytes<br>single plane | 32 Kbytes | 6                            | 79    | 2/2 <sup>(1)</sup> | 16 ch. | 2                       | 8-bit data,<br>4 chip selects,<br>24-bit address | 1 port<br>4 bits | LQFP100<br>BGA100 |

| SAM3S2B | 128 Kbytes single plane    | 32 Kbytes | 3                            | 47    | 2/2                | 10 ch. | 2                       | -                                                | 1 port<br>4 bits | LQFP64<br>QFN 64  |

| SAM3S2A | 128 Kbytes<br>single plane | 32 Kbytes | 3                            | 34    | 2/1                | 8 ch.  | -                       | -                                                | -                | LQFP48<br>QFN 48  |

| SAM3S1C | 64 Kbytes<br>single plane  | 16 Kbytes | 6                            | 79    | 2/2 <sup>(1)</sup> | 16 ch. | 2                       | 8-bit data,<br>4 chip selects,<br>24-bit address | 1 port<br>4 bits | LQFP100<br>BGA100 |

| SAM3S1B | 64 Kbytes<br>single plane  | 16 Kbytes | 3                            | 47    | 2/2                | 10 ch. | 2                       | -                                                | 1 port<br>4 bits | LQFP64<br>QFN 64  |

| SAM3S1A | 64 Kbytes<br>single plane  | 16 Kbytes | 3                            | 34    | 2/1                | 8 ch.  | -                       | -                                                | -                | LQFP48<br>QFN 48  |

Note: 1. Full Modem support on USART1.

# 2. SAM3S Block Diagram

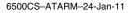

Figure 2-1. SAM3S 100-pin Version Block Diagram

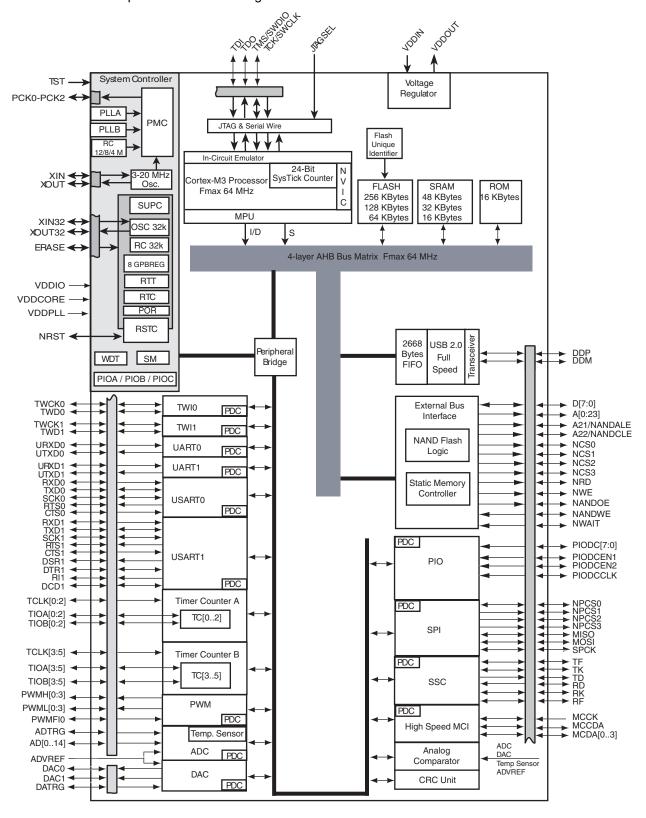

Figure 2-2. SAM3S 64-pin Version Block Diagram

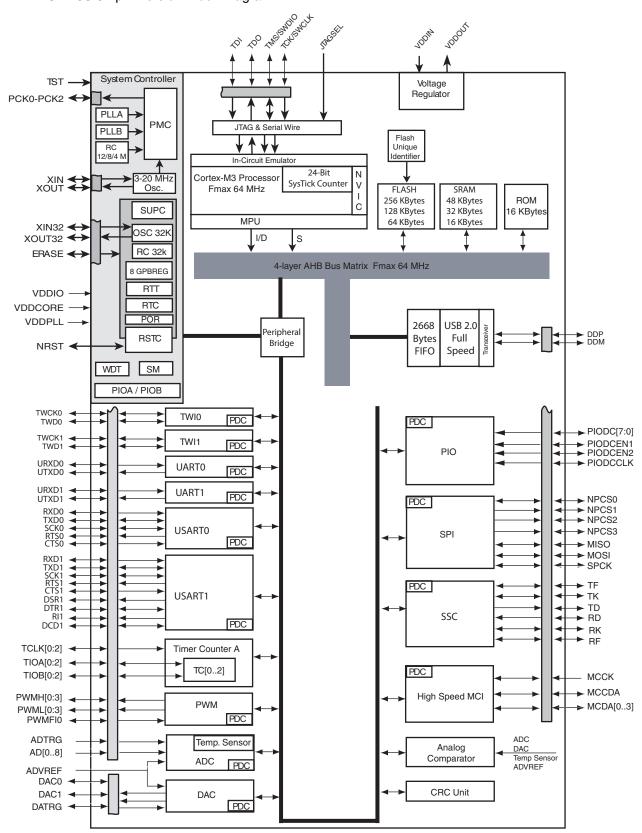

Figure 2-3. SAM3S 48-pin Version Block Diagram

# 3. Signal Description

Table 3-1 gives details on the signal names classified by peripheral.

Table 3-1.

Signal Description List

| Signal Name  | Function                                                             | Туре          | Active<br>Level | Voltage reference | Comments                                                                                         |

|--------------|----------------------------------------------------------------------|---------------|-----------------|-------------------|--------------------------------------------------------------------------------------------------|

| <del>-</del> | Power S                                                              | Supplies      |                 | 1                 |                                                                                                  |

| VDDIO        | Peripherals I/O Lines and USB transceiver Power Supply               | Power         |                 |                   | 1.62V to 3.6V                                                                                    |

| VDDIN        | Voltage Regulator Input, ADC, DAC and Analog Comparator Power Supply | Power         |                 |                   | 1.8V to 3.6V <sup>(4)</sup>                                                                      |

| VDDOUT       | Voltage Regulator Output                                             | Power         |                 |                   | 1.8V Output                                                                                      |

| VDDPLL       | Oscillator and PLL Power Supply                                      | Power         |                 |                   | 1.62 V to 1.95V                                                                                  |

| VDDCORE      | Power the core, the embedded memories and the peripherals            | Power         |                 |                   | 1.62V to 1.95V                                                                                   |

| GND          | Ground                                                               | Ground        |                 |                   |                                                                                                  |

|              | Clocks, Oscilla                                                      | ators and PLI | _S              |                   |                                                                                                  |

| XIN          | Main Oscillator Input                                                | Input         |                 |                   | Reset State:                                                                                     |

| XOUT         | Main Oscillator Output                                               | Output        |                 |                   | - PIO Input                                                                                      |

| XIN32        | Slow Clock Oscillator Input                                          | Input         |                 |                   | - Internal Pull-up disabled                                                                      |

| XOUT32       | Slow Clock Oscillator Output                                         | Output        |                 | VDDIO             | - Schmitt Trigger enabled <sup>(1)</sup>                                                         |

| PCK0 - PCK2  | Programmable Clock Output                                            | Output        |                 |                   | Reset State: - PIO Input - Internal Pull-up enabled - Schmitt Trigger enabled <sup>(1)</sup>     |

|              | Serial Wire/JTAG De                                                  | ebug Port - S | WJ-DP           |                   |                                                                                                  |

| TCK/SWCLK    | Test Clock/Serial Wire Clock                                         | Input         |                 |                   |                                                                                                  |

| TDI          | Test Data In                                                         | Input         |                 |                   | Reset State: - SWJ-DP Mode                                                                       |

| TDO/TRACESWO | Test Data Out / Trace Asynchronous Data<br>Out                       | Output        |                 | VDDIO             | - Internal pull-up disabled - Schmitt Trigger enabled <sup>(1)</sup>                             |

| TMS/SWDIO    | Test Mode Select /Serial Wire Input/Output                           | Input / I/O   |                 |                   | Committe magger emabled                                                                          |

| JTAGSEL      | JTAG Selection                                                       | Input         | High            |                   | Permanent Internal pull-down                                                                     |

|              | Flash M                                                              | lemory        |                 |                   |                                                                                                  |

| ERASE        | Flash and NVM Configuration Bits Erase<br>Command                    | Input         | High            | VDDIO             | Reset State: - Erase Input - Internal pull-down enabled - Schmitt Trigger enabled <sup>(1)</sup> |

|              | Rese                                                                 | t/Test        |                 |                   |                                                                                                  |

| NRST         | Synchronous Microcontroller Reset                                    |               | Low             | VDDIO             | Permanent Internal pull-up                                                                       |

| TST          | Test Select                                                          | Input         |                 |                   | Permanent Internal pull-down                                                                     |

Table 3-1.

Signal Description List (Continued)

| Signal Name   | Function                       | Туре               | Active<br>Level | Voltage reference                                 | Comments                           |

|---------------|--------------------------------|--------------------|-----------------|---------------------------------------------------|------------------------------------|

|               | Universal Asynchronou          | s Receiver Trans   | smitter - U     | ARTx                                              |                                    |

| URXDx         | UART Receive Data              | Input              |                 |                                                   |                                    |

| UTXDx         | UART Transmit Data             | Output             |                 |                                                   |                                    |

|               | PIO Controlle                  | r - PIOA - PIOB -  | PIOC            |                                                   |                                    |

| PA0 - PA31    | Parallel IO Controller A       | I/O                |                 |                                                   | Reset State:                       |

| PB0 - PB14    | Parallel IO Controller B       | I/O                |                 | VDDIO                                             | - PIO or System IOs <sup>(2)</sup> |

| PC0 - PC31    | Parallel IO Controller C       | I/O                |                 | - Internal pull-up enal<br>- Schmitt Trigger enal |                                    |

|               | PIO Controller - Paral         | lel Capture Mod    | e (PIOA Or      | nly)                                              |                                    |

| PIODC0-PIODC7 | Parallel Capture Mode Data     | Input              |                 |                                                   |                                    |

| PIODCCLK      | Parallel Capture Mode Clock    | Input              |                 | VDDIO                                             |                                    |

| PIODCEN1-2    | Parallel Capture Mode Enable   | Input              |                 | -                                                 |                                    |

|               | Externa                        | I Bus Interface    | 1               | 1                                                 |                                    |

| D0 - D7       | Data Bus                       | I/O                |                 |                                                   |                                    |

| A0 - A23      | Address Bus                    | Output             |                 |                                                   |                                    |

| NWAIT         | External Wait Signal           | Input              | Low             |                                                   |                                    |

|               | Static Memo                    | ory Controller - S | SMC             | 1                                                 |                                    |

| NCS0 - NCS3   | Chip Select Lines              | Output             | Low             |                                                   |                                    |

| NRD           | Read Signal                    | Output             | Low             |                                                   |                                    |

| NWE           | Write Enable                   | Output             | Low             |                                                   |                                    |

|               | NANI                           | ) Flash Logic      |                 | 1                                                 |                                    |

| NANDOE        | NAND Flash Output Enable       | Output             | Low             |                                                   |                                    |

| NANDWE        | NAND Flash Write Enable        | Output             | Low             |                                                   |                                    |

|               | High Speed Multime             | edia Card Interfa  | ice - HSMC      |                                                   |                                    |

| MCCK          | Multimedia Card Clock          | I/O                |                 |                                                   |                                    |

| MCCDA         | Multimedia Card Slot A Command | I/O                |                 |                                                   |                                    |

| MCDA0 - MCDA3 | Multimedia Card Slot A Data    | I/O                |                 |                                                   |                                    |

|               | Universal Synchronous Async    | hronous Receive    | er Transmi      | tter USARTx                                       | [                                  |

| SCKx          | USARTx Serial Clock            | I/O                |                 |                                                   |                                    |

| TXDx          | USARTx Transmit Data           | I/O                |                 |                                                   |                                    |

| RXDx          | USARTx Receive Data            | Input              |                 |                                                   |                                    |

| RTSx          | USARTx Request To Send         | Output             |                 |                                                   |                                    |

| CTSx          | USARTx Clear To Send           | Input              |                 |                                                   |                                    |

| DTR1          | USART1 Data Terminal Ready     | I/O                |                 |                                                   |                                    |

| DSR1          | USART1 Data Set Ready          | Input              |                 |                                                   |                                    |

| DCD1          | USART1 Data Carrier Detect     | Input              |                 |                                                   |                                    |

| RI1           | USART1 Ring Indicator          | Input              |                 |                                                   |                                    |

Table 3-1.

Signal Description List (Continued)

| Signal Name              | Function                                    | Туре               | Active<br>Level | Voltage reference | Comments                                                                       |

|--------------------------|---------------------------------------------|--------------------|-----------------|-------------------|--------------------------------------------------------------------------------|

|                          | Synchronous Seri                            | al Controller      | - SSC           |                   |                                                                                |

| TD                       | SSC Transmit Data                           | Output             |                 |                   |                                                                                |

| RD                       | SSC Receive Data                            | Input              |                 |                   |                                                                                |

| TK                       | SSC Transmit Clock                          | I/O                |                 |                   |                                                                                |

| RK                       | SSC Receive Clock                           | I/O                |                 |                   |                                                                                |

| TF                       | SSC Transmit Frame Sync                     | I/O                |                 |                   |                                                                                |

| RF                       | SSC Receive Frame Sync                      | I/O                |                 |                   |                                                                                |

|                          | Timer/Co                                    | unter - TC         |                 |                   |                                                                                |

| TCLKx                    | TC Channel x External Clock Input           | Input              |                 |                   |                                                                                |

| TIOAx                    | TC Channel x I/O Line A                     | I/O                |                 |                   |                                                                                |

| TIOBx                    | TC Channel x I/O Line B                     | I/O                |                 |                   |                                                                                |

|                          | Pulse Width Modulat                         | on Controlle       | r- PWMC         | 1                 |                                                                                |

| PWMHx                    | PWM Waveform Output High for channel x      | Output             |                 |                   |                                                                                |

| PWMLx                    | PWM Waveform Output Low for channel x       | Output             |                 |                   | only output in<br>complementary mode when<br>dead time insertion is<br>enabled |

| PWMFI0                   | PWM Fault Input                             | Input              |                 |                   |                                                                                |

|                          | Serial Periphera                            | al Interface -     | SPI             |                   |                                                                                |

| MISO                     | Master In Slave Out                         | I/O                |                 |                   |                                                                                |

| MOSI                     | Master Out Slave In                         | I/O                |                 |                   |                                                                                |

| SPCK                     | SPI Serial Clock                            | I/O                |                 |                   |                                                                                |

| SPI_NPCS0                | SPI Peripheral Chip Select 0                | I/O                | Low             |                   |                                                                                |

| SPI_NPCS1 -<br>SPI_NPCS3 | SPI Peripheral Chip Select                  | Output             | Low             |                   |                                                                                |

|                          | Two-Wire In                                 | terface- TWI       |                 |                   |                                                                                |

| TWDx                     | TWIx Two-wire Serial Data                   | I/O                |                 |                   |                                                                                |

| TWCKx                    | TWIx Two-wire Serial Clock                  | I/O                |                 |                   |                                                                                |

|                          | Ana                                         | alog               |                 |                   |                                                                                |

| ADVREF                   | ADC, DAC and Analog Comparator<br>Reference | Analog             |                 |                   |                                                                                |

|                          | Analog-to-Digital                           | Converter -        | ADC             |                   |                                                                                |

| AD0 - AD14               | Analog Inputs                               | Analog,<br>Digital |                 |                   |                                                                                |

| ADTRG                    | ADC Trigger                                 | Input              |                 | VDDIO             |                                                                                |

|                          | 12-bit Digital-to-Ana                       | log Converte       | er - DAC        |                   |                                                                                |

| DAC0 - DAC1              | Analog output                               | Analog,<br>Digital |                 |                   |                                                                                |

| DACTRG                   | DAC Trigger                                 | Input              |                 | VDDIO             |                                                                                |

|                          | •                                           |                    |                 |                   | t .                                                                            |

**Table 3-1.** Signal Description List (Continued)

| Signal Name   | Function                          | Туре               | Active<br>Level | Voltage reference | Comments                                          |  |

|---------------|-----------------------------------|--------------------|-----------------|-------------------|---------------------------------------------------|--|

|               | Fast Flash Programm               | ning Interfac      | e - FFPI        |                   |                                                   |  |

| PGMEN0-PGMEN2 | Programming Enabling              | Input              |                 | VDDIO             |                                                   |  |

| PGMM0-PGMM3   | Programming Mode                  | Input              |                 |                   |                                                   |  |

| PGMD0-PGMD15  | PGMD0-PGMD15 Programming Data I/O |                    |                 |                   |                                                   |  |

| PGMRDY        | Programming Ready                 | Output             | High            |                   |                                                   |  |

| PGMNVALID     | Data Direction                    | Output             | Low             | VDDIO             |                                                   |  |

| PGMNOE        | Programming Read                  | Input              | Low             |                   |                                                   |  |

| PGMCK         | Programming Clock                 | Input              |                 |                   |                                                   |  |

| PGMNCMD       | Programming Command               | Input              | Low             |                   |                                                   |  |

|               | USB Full Speed Device             |                    |                 |                   |                                                   |  |

| DDM           | USB Full Speed Data -             | Analog             |                 |                   | Reset State:                                      |  |

| DDP           | USB Full Speed Data +             | Analog,<br>Digital |                 | VDDIO             | - USB Mode<br>- Internal Pull-down <sup>(3)</sup> |  |

- Notes: 1. Schmitt Triggers can be disabled through PIO registers.

- 2. Some PIO lines are shared with System IOs.

- 3. Refer to the USB sub section in the product Electrical Characteristics Section for Pull-down value in USB Mode.

- 4. See Section 5.3 "Typical Powering Schematics" for restriction on voltage range of Analog Cells.

# 4. Package and Pinout

### 4.1 SAM3S4/2/1C Package and Pinout

Figure 4-2 shows the orientation of the 100-ball LFBGA Package

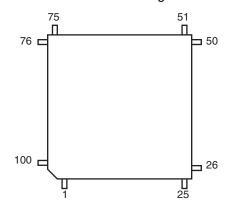

#### 4.1.1 100-lead LQFP Package Outline

Figure 4-1. Orientation of the 100-lead LQFP Package

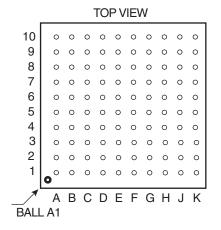

#### 4.1.2 100-ball LFBGA Package Outline

The 100-Ball LFBGA package has a 0.8 mm ball pitch and respects Green Standards. Its dimensions are 9 x 9 x 1.1 mm.

Figure 4-2. Orientation of the 100-BALL LFBGA Package

#### 4.1.3 100-Lead LQFP Pinout

Table 4-1. 100-lead LQFP SAM3S4/2/1C Pinout

| 1  | ADVREF          |

|----|-----------------|

| 2  | GND             |

| 3  | PB0/AD4         |

| 4  | PC29/AD13       |

| 5  | PB1/AD5         |

| 6  | PC30/AD14       |

| 7  | PB2/AD6         |

| 8  | PC31            |

| 9  | PB3/AD7         |

| 10 | VDDIN           |

| 11 | VDDOUT          |

| 12 | PA17/PGMD5/AD0  |

| 13 | PC26            |

| 14 | PA18/PGMD6/AD1  |

| 15 | PA21/PGMD9/AD8  |

| 16 | VDDCORE         |

| 17 | PC27            |

| 18 | PA19/PGMD7/AD2  |

| 19 | PC15/AD11       |

| 20 | PA22/PGMD10/AD9 |

| 21 | PC13/AD10       |

| 22 | PA23/PGMD1      |

| 23 | PC12/AD12       |

| 24 | PA20/PGMD8/AD3  |

| 25 | PC0             |

|    |                 |

| 77 (17100 -172) 1 0 1 1110 dt |                         |  |  |  |

|-------------------------------|-------------------------|--|--|--|

| 26                            | GND                     |  |  |  |

| 27                            | VDDIO                   |  |  |  |

| 28                            | PA16/PGMD4              |  |  |  |

| 29                            | PC7                     |  |  |  |

| 30                            | PA15/PGMD3              |  |  |  |

| 31                            | PA14/PGMD2              |  |  |  |

| 32                            | PC6                     |  |  |  |

| 33                            | PA13/PGMD1              |  |  |  |

| 34                            | PA24/PGMD12             |  |  |  |

| 35                            | PC5                     |  |  |  |

| 36                            | VDDCORE                 |  |  |  |

| 37                            | PC4                     |  |  |  |

| 38                            | PA25/PGMD13             |  |  |  |

| 39                            | PA26/PGMD14             |  |  |  |

| 40                            | PC3                     |  |  |  |

| 41                            | PA12/PGMD0              |  |  |  |

| 42                            | PA11/PGMM3              |  |  |  |

| 43                            | PC2                     |  |  |  |

| 44                            | PA10/PGMM2              |  |  |  |

| 45                            | GND                     |  |  |  |

| 46                            | PA9/PGMM1               |  |  |  |

| 47                            | PC1                     |  |  |  |

| 48                            | PA8/XOUT32/<br>PGMM0    |  |  |  |

| 49                            | PA7/XIN32/<br>PGMNVALID |  |  |  |

| 50                            | VDDIO                   |  |  |  |

|                               |                         |  |  |  |

| 51 | TDI/PB4     |

|----|-------------|

| 52 | PA6/PGMNOE  |

| 53 | PA5/PGMRDY  |

| 54 | PC28        |

| 55 | PA4/PGMNCMD |

| 56 | VDDCORE     |

| 57 | PA27/PGMD15 |

| 58 | PC8         |

| 59 | PA28        |

| 60 | NRST        |

| 61 | TST         |

| 62 | PC9         |

| 63 | PA29        |

| 64 | PA30        |

| 65 | PC10        |

| 66 | PA3         |

| 67 | PA2/PGMEN2  |

| 68 | PC11        |

| 69 | VDDIO       |

| 70 | GND         |

| 71 | PC14        |

| 72 | PA1/PGMEN1  |

| 73 | PC16        |

| 74 | PA0/PGMEN0  |

| 75 | PC17        |

| 76  | TDO/TRACESWO/PB<br>5 |

|-----|----------------------|

| 77  | JTAGSEL              |

| 78  | PC18                 |

| 79  | TMS/SWDIO/PB6        |

| 80  | PC19                 |

| 81  | PA31                 |

| 82  | PC20                 |

| 83  | TCK/SWCLK/PB7        |

| 84  | PC21                 |

| 85  | VDDCORE              |

| 86  | PC22                 |

| 87  | ERASE/PB12           |

| 88  | DDM/PB10             |

| 89  | DDP/PB11             |

| 90  | PC23                 |

| 91  | VDDIO                |

| 92  | PC24                 |

| 93  | PB13/DAC0            |

| 94  | PC25                 |

| 95  | GND                  |

| 96  | PB8/XOUT             |

| 97  | PB9/PGMCK/XIN        |

| 98  | VDDIO                |

| 99  | PB14/DAC1            |

| 100 | VDDPLL               |

#### 4.1.4 100-ball LFBGA Pinout

Table 4-2.100-ball LFBGA SAM3S4/2/1C Pinout

| A1         | PB1/AD5              |

|------------|----------------------|

| A2         | PC29                 |

| А3         | VDDIO                |

| A4         | PB9/PGMCK/XIN        |

| <b>A</b> 5 | PB8/XOUT             |

| A6         | PB13/DAC0            |

| A7         | DDP/PB11             |

| A8         | DDM/PB10             |

| A9         | TMS/SWDIO/PB6        |

| A10        | JTAGSEL              |

| B1         | PC30                 |

| B2         | ADVREF               |

| В3         | GNDANA               |

| B4         | PB14/DAC1            |

| B5         | PC21                 |

| B6         | PC20                 |

| B7         | PA31                 |

| B8         | PC19                 |

| B9         | PC18                 |

| B10        | TDO/TRACESWO/<br>PB5 |

| C1         | PB2/AD6              |

| C2         | VDDPLL               |

| СЗ         | PC25                 |

| C4         | PC23                 |

| C5         | ERASE/PB12           |

| C6  | TCK/SWCLK/PB7  |

|-----|----------------|

| C7  | PC16           |

| C8  | PA1/PGMEN1     |

| C9  | PC17           |

| C10 | PA0/PGMEN0     |

| D1  | PB3/AD7        |

| D2  | PB0/AD4        |

| D3  | PC24           |

| D4  | PC22           |

| D5  | GND            |

| D6  | GND            |

| D7  | VDDCORE        |

| D8  | PA2/PGMEN2     |

| D9  | PC11           |

| D10 | PC14           |

| E1  | PA17/PGMD5/AD0 |

| E2  | PC31           |

| E3  | VDDIN          |

| E4  | GND            |

| E5  | GND            |

| E6  | NRST           |

| E7  | PA29/AD13      |

| E8  | PA30/AD14      |

| E9  | PC10           |

| E10 | PA3            |

| F1  | PA18/PGMD6/AD1 |

|-----|----------------|

| F2  | PC26           |

| F3  | VDDOUT         |

| F4  | GND            |

| F5  | VDDIO          |

| F6  | PA27/PGMD15    |

| F7  | PC8            |

| F8  | PA28           |

| F9  | TST            |

| F10 | PC9            |

| G1  | PA21/PGMD9/AD8 |

| G2  | PC27           |

| G3  | PA15/PGMD3     |

| G4  | VDDCORE        |

| G5  | VDDCORE        |

| G6  | PA26/PGMD14    |

| G7  | PA12/PGMD0     |

| G8  | PC28           |

| G9  | PA4/PGMNCMD    |

| G10 | PA5/PGMRDY     |

| H1  | PA19/PGMD7/AD2 |

| H2  | PA23/PGMD11    |

| НЗ  | PC7            |

| H4  | PA14/PGMD2     |

| H5  | PA13/PGMD1     |

| H6         | PC4                     |  |

|------------|-------------------------|--|

| H7         | PA11/PGMM3              |  |

| Н8         | PC1                     |  |

| H9         | PA6/PGMNOE              |  |

| H10        | TDI/PB4                 |  |

| J1         | PC15/AD11               |  |

| J2         | PC0                     |  |

| J3         | PA16/PGMD4              |  |

| J4         | PC6                     |  |

| J5         | PA24/PGMD12             |  |

| J6         | PA25/PGMD13             |  |

| J7         | PA10/PGMM2              |  |

| J8         | GND                     |  |

| J9         | VDDCORE                 |  |

| J10        | VDDIO                   |  |

| K1         | PA22/PGMD10/AD9         |  |

| K2         | PC13/AD10               |  |

| K3         | PC12/AD12               |  |

| K4         | PA20/PGMD8/AD3          |  |

| <b>K</b> 5 | PC5                     |  |

| K6         | PC3                     |  |

| K7         | PC2                     |  |

| K8         | PA9/PGMM1               |  |

| K9         | PA8/XOUT32/PGMM0        |  |

| K10        | PA7/XIN32/<br>PGMNVALID |  |

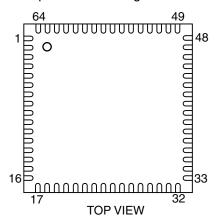

# 4.2 SAM3S4/2/1B Package and Pinout

Figure 4-3. Orientation of the 64-pad QFN Package

Figure 4-4. Orientation of the 64-lead LQFP Package

#### 4.2.1 64-Lead LQFP and QFN Pinout

64-pin version SAM3S devices are pin-to-pin compatible with AT91SAM7S legacy products. Furthermore, SAM3S products have new functionalities shown in italic in Table 4-3.

**Table 4-3.** 64-pin SAM3S4/2/1B Pinout

| 1     | ADVREF                     | 17 | GND                             | 33 | TDI/PB4                               | 49 | TDO/TRACESWO/PB5 |  |

|-------|----------------------------|----|---------------------------------|----|---------------------------------------|----|------------------|--|

| 2     | GND                        | 18 | VDDIO                           | 34 | PA6/PGMNOE                            | 50 | JTAGSEL          |  |

| 3     | PB0/AD4                    | 19 | PA16/PGMD4                      | 35 | PA5/PGMRDY                            | 51 | TMS/SWDIO/PB6    |  |

| 4     | PB1/AD5                    | 20 | PA15/PGMD3                      | 36 | PA4/PGMNCMD                           | 52 | PA31             |  |

| 5     | PB2/AD6                    | 21 | PA14/PGMD2                      | 37 | PA27/PGMD15                           | 53 | TCK/SWCLK/PB7    |  |

| 6     | PB3/AD7                    | 22 | PA13/PGMD1                      | 38 | PA28                                  | 54 | VDDCORE          |  |

| 7     | VDDIN                      | 23 | PA24/PGMD12                     | 39 | NRST                                  | 55 | ERASE/PB12       |  |

| 8     | VDDOUT                     | 24 | VDDCORE                         | 40 | TST                                   | 56 | DDM/PB10         |  |

| 9     | PA17/PGMD5/<br>AD <i>0</i> | 25 | PA25/PGMD13                     | 41 | PA29                                  | 57 | DDP/PB11         |  |

| 10    | PA18/PGMD6/<br>AD1         | 26 | PA26/PGMD14                     | 42 | PA30                                  | 58 | VDDIO            |  |

| 11    | PA21/PGMD9/<br>AD8         | 27 | PA12/PGMD0                      | 43 | PA3                                   | 59 | PB13/DAC0        |  |

| 12    | VDDCORE                    | 28 | PA11/PGMM3                      | 44 | PA2/PGMEN2                            | 60 | GND              |  |

| 13    | PA19/PGMD7/<br>AD2         | 29 | PA10/PGMM2                      | 45 | VDDIO                                 | 61 | XOUT/PB8         |  |

| 14    | PA22/PGMD10/<br>AD9        | 30 | PA9/PGMM1                       | 46 | GND                                   | 62 | XIN/PGMCK/PB9    |  |

| 15    | PA23/PGMD11                | 31 | PA8/ <i>XOUT32/</i><br>PGMM0    | 47 | PA1/PGMEN1                            | 63 | PB14/DAC1        |  |

| 16    | PA20/PGMD8/<br>AD3         | 32 | PA7/ <i>XIN32/</i><br>PGMNVALID | 48 | PA0/PGMEN0                            | 64 | VDDPLL           |  |

| Notor | T                          |    | and must be sennested to        |    | · · · · · · · · · · · · · · · · · · · |    |                  |  |

Note: The bottom pad of the QFN package must be connected to ground.

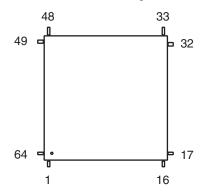

# 4.3 SAM3S4/2/1A Package and Pinout

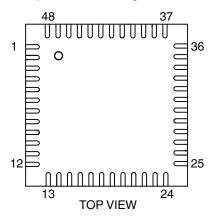

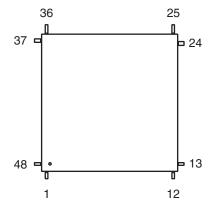

Figure 4-5. Orientation of the 48-pad QFN Package

Figure 4-6. Orientation of the 48-lead LQFP Package

#### 4.3.1 48-Lead LQFP and QFN Pinout

Table 4-4. 48-pin SAM3S4/2/1A Pinout

| Iable | 4-4. 40-pin SAM    | 1334 | _ |

|-------|--------------------|------|---|

| 1     | ADVREF             |      | 1 |

| 2     | GND                |      | 1 |

| 3     | PB0/AD4            |      | 1 |

| 4     | PB1/AD5            |      | 1 |

| 5     | PB2/AD6            |      | 1 |

| 6     | PB3/AD7            |      | 1 |

| 7     | VDDIN              |      | 1 |

| 8     | VDDOUT             |      | 2 |

| 9     | PA17/PGMD5/<br>AD0 |      | 2 |

| 10    | PA18/PGMD6/<br>AD1 |      | 2 |

| 11    | PA19/PGMD7/<br>AD2 |      | 2 |

| 12    | PA20/AD3           |      | 2 |

| 13 VDDIO  14 PA16/PGMD4  15 PA15/PGMD3  16 PA14/PGMD2  17 PA13/PGMD1  18 VDDCORE  19 PA12/PGMD0  20 PA11/PGMM3  21 PA10/PGMM2  22 PA9/PGMM1  23 PA8/XOUT32/PGMM0 |            |                     |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------|--|--|--|

| 15 PA15/PGMD3 16 PA14/PGMD2 17 PA13/PGMD1 18 VDDCORE 19 PA12/PGMD0 20 PA11/PGMM3 21 PA10/PGMM2 22 PA9/PGMM1 23 PA8/XOUT32/                                       | 13         | VDDIO               |  |  |  |

| 16 PA14/PGMD2 17 PA13/PGMD1 18 VDDCORE 19 PA12/PGMD0 20 PA11/PGMM3 21 PA10/PGMM2 22 PA9/PGMM1 23 PA8/XOUT32/                                                     | 14         | PA16/PGMD4          |  |  |  |

| 17 PA13/PGMD1 18 VDDCORE 19 PA12/PGMD0 20 PA11/PGMM3 21 PA10/PGMM2 22 PA9/PGMM1 23 PA8/XOUT32/                                                                   | 15         | PA15/PGMD3          |  |  |  |

| 18 VDDCORE  19 PA12/PGMD0  20 PA11/PGMM3  21 PA10/PGMM2  22 PA9/PGMM1  PA8/XOUT32/                                                                               | 16         | PA14/PGMD2          |  |  |  |

| 19 PA12/PGMD0 20 PA11/PGMM3 21 PA10/PGMM2 22 PA9/PGMM1 23 PA8/XOUT32/                                                                                            | 17         | PA13/PGMD1          |  |  |  |

| 20 PA11/PGMM3 21 PA10/PGMM2 22 PA9/PGMM1 23 PA8/XOUT32/                                                                                                          | 18         | VDDCORE             |  |  |  |

| 21 PA10/PGMM2  22 PA9/PGMM1  PA8/XOUT32/                                                                                                                         | 19         | PA12/PGMD0          |  |  |  |

| 22 PA9/PGMM1 PA8/XOUT32/                                                                                                                                         | 20         | PA11/PGMM3          |  |  |  |

| PA8/XOUT32/                                                                                                                                                      | 21         | PA10/PGMM2          |  |  |  |

| 23                                                                                                                                                               | 22         | PA9/PGMM1           |  |  |  |

|                                                                                                                                                                  | 23         | PA8/XOUT32/         |  |  |  |

|                                                                                                                                                                  | 23         | PGMM0               |  |  |  |

| PA7/XIN32/                                                                                                                                                       | 24         | PA7/ <i>XIN32</i> / |  |  |  |

| PGMNVALID                                                                                                                                                        | <b>4</b> 7 | PGMNVALID           |  |  |  |

| 25 | TDI/PB4     |  |  |  |

|----|-------------|--|--|--|

| 26 | PA6/PGMNOE  |  |  |  |

| 27 | PA5/PGMRDY  |  |  |  |

| 28 | PA4/PGMNCMD |  |  |  |

| 29 | NRST        |  |  |  |

| 30 | TST         |  |  |  |

| 31 | PA3         |  |  |  |

| 32 | PA2/PGMEN2  |  |  |  |

| 33 | VDDIO       |  |  |  |

| 34 | GND         |  |  |  |

| 35 | PA1/PGMEN1  |  |  |  |

| 36 | PA0/PGMEN0  |  |  |  |

| 37 | TDO/TRACESWO/<br>PB5 |  |  |  |

|----|----------------------|--|--|--|

| 38 | JTAGSEL              |  |  |  |

| 39 | TMS/SWDIO/PB6        |  |  |  |

| 40 | TCK/SWCLK/PB7        |  |  |  |

| 41 | VDDCORE              |  |  |  |

| 42 | ERASE/PB12           |  |  |  |

| 43 | DDM/PB10             |  |  |  |

| 44 | DDP/PB11             |  |  |  |

| 45 | XOUT/PB8             |  |  |  |

| 46 | XIN/PB9/PGMCK        |  |  |  |

| 47 | VDDIO                |  |  |  |

| 48 | VDDPLL               |  |  |  |

Note: The bottom pad of the QFN package must be connected to ground.

#### 5. Power Considerations

#### 5.1 Power Supplies

The SAM3S product has several types of power supply pins:

- VDDCORE pins: Power the core, the embedded memories and the peripherals; voltage ranges from 1.62V and 1.95V.

- VDDIO pins: Power the Peripherals I/O lines (Input/Output Buffers); USB transceiver; Backup part, 32kHz crystal oscillator and oscillator pads; ranges from 1.62V and 3.6V

- VDDIN pin: Voltage Regulator Input, ADC, DAC and Analog Comparator Power Supply;

Voltage ranges from 1.8V to 3.6V

- VDDPLL pin: Powers the PLLA, PLLB, the Fast RC and the 3 to 20 MHz oscillator; voltage ranges from 1.62V and 1.95V.

#### 5.2 Voltage Regulator

The SAM3S embeds a voltage regulator that is managed by the Supply Controller.

This internal regulator is intended to supply the internal core of SAM3S. It features two different operating modes:

- In Normal mode, the voltage regulator consumes less than 700 μA static current and draws 80 mA of output current. Internal adaptive biasing adjusts the regulator quiescent current depending on the required load current. In Wait Mode quiescent current is only 7 μA.

- In Backup mode, the voltage regulator consumes less than 1  $\mu$ A while its output (VDDOUT) is driven internally to GND. The default output voltage is 1.80V and the start-up time to reach Normal mode is inferior to 100  $\mu$ s.

For adequate input and output power supply decoupling/bypassing, refer to the Voltage Regulator section in the Electrical Characteristics section of the datasheet.

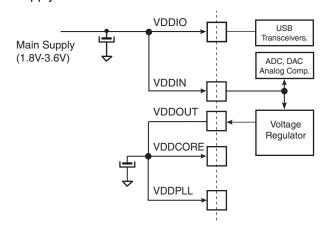

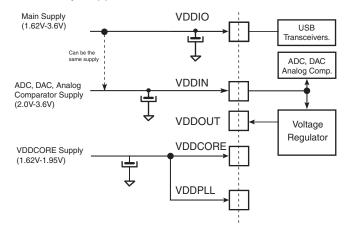

### 5.3 Typical Powering Schematics

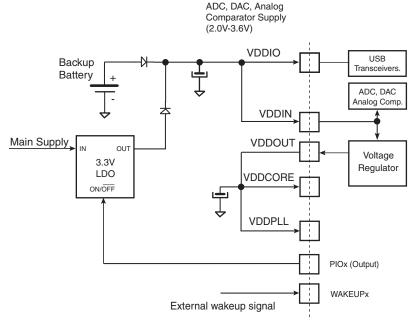

The SAM3S supports a 1.62V-3.6V single supply mode. The internal regulator input connected to the source and its output feeds VDDCORE. Figure 5-1 shows the power schematics.

As VDDIN powers the voltage regulator, the ADC/DAC and the analog comparator, when the user does not want to use the embedded voltage regulator, it can be disabled by software via the SUPC (note that it is different from Backup mode).

Figure 5-1. Single Supply

Note: Restrictions

With Main Supply < 2.0 V, USB and ADC/DAC and Analog comparator are not usable.

With Main Supply  $\geq$  2.0V and < 3V, USB is not usable. With Main Supply  $\geq$  3V, all peripherals are usable.

Figure 5-2. Core Externally Supplied

Note: Restrictions

With Main Supply < 2.0V, USB is not usable.

With VDDIN < 2.0V, ADC/DAC and Analog comparator are not usable.

With Main Supply  $\geq$  2.0V and < 3V, USB is not usable.

With Main Supply and VDDIN ≥ 3V, all peripherals are usable.

Figure 5-3 below provides an example of the powering scheme when using a backup battery. Since the PIO state is preserved when in backup mode, any free PIO line can be used to switch off the external regulator by driving the PIO line at low level (PIO is input, pull-up enabled after backup reset). External wake-up of the system can be from a push button or any signal. See Section 5.6 "Wake-up Sources" for further details.

Figure 5-3. Backup Battery

Note: The two diodes provide a "switchover circuit" (for illustration purpose; between the backup battery and the main supply when the system is put in backup mode.

#### 5.4 Active Mode

Active mode is the normal running mode with the core clock running from the fast RC oscillator, the main crystal oscillator or the PLLA. The power management controller can be used to adapt the frequency and to disable the peripheral clocks.

#### 5.5 Low Power Modes

The various low power modes of the SAM3S are described below:

#### 5.5.1 Backup Mode

The purpose of backup mode is to achieve the lowest power consumption possible in a system which is performing periodic wake-ups to perform tasks but not requiring fast startup time (<0.1ms). Total current consumption is 3 µA typical.

The Supply Controller, zero-power power-on reset, RTT, RTC, Backup registers and 32 kHz oscillator (RC or crystal oscillator selected by software in the Supply Controller) are running. The regulator and the core supply are off.

Backup mode is based on the Cortex-M3 deepsleep mode with the voltage regulator disabled.

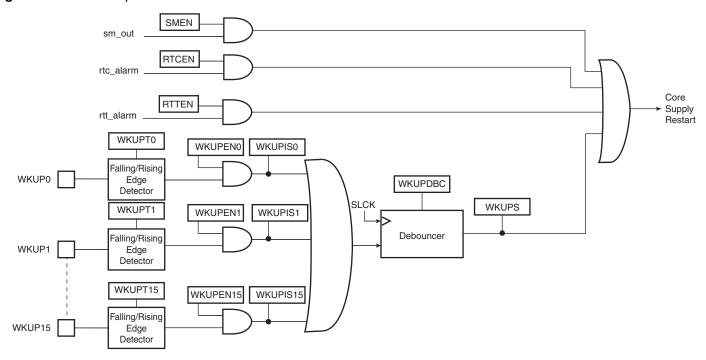

The SAM3S can be awakened from this mode through WUP0-15 pins, the supply monitor (SM), the RTT or RTC wake-up event.

Backup mode is entered by using WFE instructions with the SLEEPDEEP bit in the System Control Register of the Cortex-M3 set to 1. (See the Power management description in The ARM Cortex M3 Processor section of the product datasheet).

Exit from Backup mode happens if one of the following enable wake up events occurs:

- WKUPEN0-15 pins (level transition, configurable debouncing)

- Supply Monitor alarm

- RTC alarm

- RTT alarm

#### 5.5.2 Wait Mode

The purpose of the wait mode is to achieve very low power consumption while maintaining the whole device in a powered state for a startup time of less than 10  $\mu$ s. Current Consumption in Wait mode is typically 15  $\mu$ A (total current consumption) if the internal voltage regulator is used or 8  $\mu$ A if an external regulator is used.

In this mode, the clocks of the core, peripherals and memories are stopped. However, the core, peripherals and memories power supplies are still powered. From this mode, a fast start up is available.

This mode is entered via Wait for Event (WFE) instructions with LPM = 1 (Low Power Mode bit in PMC\_FSMR). The Cortex-M3 is able to handle external events or internal events in order to wake-up the core (WFE). This is done by configuring the external lines WUP0-15 as fast startup wake-up pins (refer to Section 5.7 "Fast Startup"). RTC or RTT Alarm and USB wake-up events can be used to wake up the CPU (exit from WFE).

#### Entering Wait Mode:

- Select the 4/8/12 MHz fast RC oscillator as Main Clock

- Set the LPM bit in the PMC Fast Startup Mode Register (PMC\_FSMR)

- Execute the Wait-For-Event (WFE) instruction of the processor

Note: Internal Main clock resynchronization cycles are necessary between the writing of MOSCRCEN bit and the effective entry in Wait mode. Depending on the user application, Waiting for MOSCRCEN bit to be cleared is recommended to ensure that the core will not execute undesired instructions.

#### 5.5.3 Sleep Mode

The purpose of sleep mode is to optimize power consumption of the device versus response time. In this mode, only the core clock is stopped. The peripheral clocks can be enabled. The current consumption in this mode is application dependent.

This mode is entered via Wait for Interrupt (WFI) or Wait for Event (WFE) instructions with LPM = 0 in PMC FSMR.

The processor can be woke up from an interrupt if WFI instruction of the Cortex M3 is used, or from an event if the WFE instruction is used to enter this mode.

#### 5.5.4 **Low Power Mode Summary Table**

The modes detailed above are the main low power modes. Each part can be set to on or off separately and wake up sources can be individually configured. Table 5-1 below shows a summary of the configurations of the low power modes.

**Table 5-1.** Low Power Mode Configuration Summary

| Mode           | SUPC,<br>32 kHz<br>Oscillator<br>RTC RTT<br>Backup<br>Registers,<br>POR<br>(Backup<br>Region) | Regulator | Core<br>Memory<br>Peripherals           | Mode Entry                                          | Potential Wake Up<br>Sources                       | Core at<br>Wake Up | PIO State<br>while in Low<br>Power Mode | PIO State<br>at Wake Up                             | Consumption (2) (3)       | Wake-up<br>Time <sup>(1)</sup> |

|----------------|-----------------------------------------------------------------------------------------------|-----------|-----------------------------------------|-----------------------------------------------------|----------------------------------------------------|--------------------|-----------------------------------------|-----------------------------------------------------|---------------------------|--------------------------------|

| Backup<br>Mode | ON                                                                                            | OFF       | OFF<br>(Not powered)                    | WFE<br>+SLEEPDEEP<br>bit = 1                        | WUP0-15 pins<br>SM alarm<br>RTC alarm<br>RTT alarm | Reset              | Previous<br>state saved                 | PIOA &<br>PIOB &<br>PIOC<br>Inputs with<br>pull ups | 3 μA typ <sup>(4)</sup>   | < 0.1 ms                       |

| Wait<br>Mode   | ON                                                                                            | ON        | Powered<br>(Not clocked)                | WFE<br>+SLEEPDEEP<br>bit = 0<br>+LPM bit = 1        | I                                                  | Clocked<br>back    | Previous<br>state saved                 | Unchanged                                           | 5 μΑ/15 μΑ <sup>(5)</sup> | < 10 μs                        |

| Sleep<br>Mode  | ON                                                                                            | ON        | Powered <sup>(7)</sup><br>(Not clocked) | WFE or WFI<br>+SLEEPDEEP<br>bit = 0<br>+LPM bit = 0 | trom: Fact ctart-lin                               | Clocked<br>back    | Previous<br>state saved                 | Unchanged                                           | (6)                       | (6)                            |

- Notes: 1. When considering wake-up time, the time required to start the PLL is not taken into account. Once started, the device works with the 4/8/12 MHz fast RC oscillator. The user has to add the PLL start-up time if it is needed in the system. The wake-up time is defined as the time taken for wake up until the first instruction is fetched.

- 2. The external loads on PIOs are not taken into account in the calculation.

- 3. Supply Monitor current consumption is not included.

- 4. Total Current consumption.

- 5. 5 μA on VDDCORE, 15 μA for total current consumption (using internal voltage regulator), 8 μA for total current consumption (without using internal voltage regulator).

- 6. Depends on MCK frequency.

- 7. In this mode the core is supplied and not clocked but some peripherals can be clocked.

### 5.6 Wake-up Sources

The wake-up events allow the device to exit the backup mode. When a wake-up event is detected, the Supply Controller performs a sequence which automatically reenables the core power supply and the SRAM power supply, if they are not already enabled.

Figure 5-4. Wake-up Source

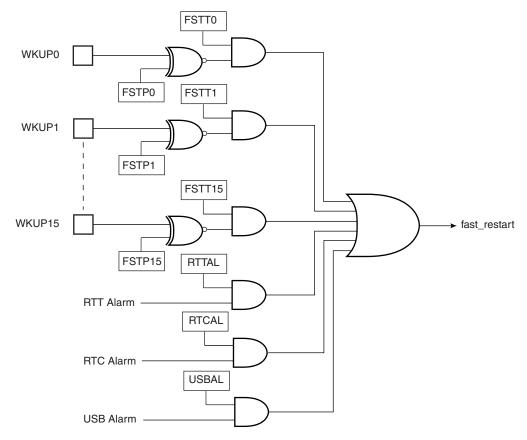

### 5.7 Fast Startup

The device allows the processor to restart in a few microseconds while the processor is in wait mode. A fast start up can occur upon detection of a low level on one of the 19 wake-up inputs (WKUP0 to 15 + SM + RTC + RTT).

The fast restart circuitry, as shown in Figure 5-5, is fully asynchronous and provides a fast start-up signal to the Power Management Controller. As soon as the fast start-up signal is asserted, the PMC automatically restarts the embedded 4/8/12 MHz fast RC oscillator, switches the master clock on this 4MHz clock and reenables the processor clock.

Figure 5-5. Fast Start-Up Circuitry

# 6. Input/Output Lines

The SAM3S has several kinds of input/output (I/O) lines such as general purpose I/Os (GPIO) and system I/Os. GPIOs can have alternate functionality due to multiplexing capabilities of the PIO controllers. The same PIO line can be used whether in IO mode or by the multiplexed peripheral. System I/Os include pins such as test pins, oscillators, erase or analog inputs.

#### 6.1 General Purpose I/O Lines

GPIO Lines are managed by PIO Controllers. All I/Os have several input or output modes such as pull-up or pull-down, input Schmitt triggers, multi-drive (open-drain), glitch filters, debouncing or input change interrupt. Programming of these modes is performed independently for each I/O line through the PIO controller user interface. For more details, refer to the product PIO controller section.

The input output buffers of the PIO lines are supplied through VDDIO power supply rail.

The SAM3S embeds high speed pads able to handle up to 32 MHz for HSMCI (MCK/2), 45 MHz for SPI clock lines and 35 MHz on other lines. See AC Characteristics Section in the Electrical Characteristics Section of the datasheet for more details. Typical pull-up and pull-down value is 100 k $\Omega$  for all I/Os.

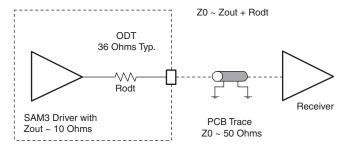

Each I/O line also embeds an ODT (On-Die Termination), see Figure 6-1. It consists of an internal series resistor termination scheme for impedance matching between the driver output (SAM3S) and the PCB trace impedance preventing signal reflection. The series resistor helps to reduce IOs switching current (di/dt) thereby reducing in turn, EMI. It also decreases overshoot and undershoot (ringing) due to inductance of interconnect between devices or between boards. In conclusion ODT helps diminish signal integrity issues.

**Figure 6-1.** On-Die Termination

#### 6.2 System I/O Lines

System I/O lines are pins used by oscillators, test mode, reset and JTAG to name but a few. Described below are the SAM3S system I/O lines shared with PIO lines:

These pins are software configurable as general purpose I/O or system pins. At startup the default function of these pins is always used.

Table 6-1. System I/O Configuration Pin List.

| SYSTEM_IO<br>bit number | Default function after reset | Other function | Constraints for normal start        | Configuration                                                              |

|-------------------------|------------------------------|----------------|-------------------------------------|----------------------------------------------------------------------------|

| 12                      | ERASE                        | PB12           | Low Level at startup <sup>(1)</sup> |                                                                            |

| 10                      | DDM                          | PB10           | -                                   |                                                                            |

| 11                      | DDP                          | PB11           | -                                   | In Matrix User Interface Registers                                         |

| 7                       | TCK/SWCLK                    | PB7            | -                                   | (Refer to the SystemIO Configuration Register in the Bus Matrix section of |

| 6                       | TMS/SWDIO                    | PB6            | -                                   | the product datasheet.)                                                    |

| 5                       | TDO/TRACESWO                 | PB5            | -                                   |                                                                            |

| 4                       | TDI                          | PB4            | -                                   |                                                                            |

| -                       | PA7                          | XIN32          | -                                   | See footnote (2) below                                                     |

| -                       | PA8                          | XOUT32         | -                                   | See footnote (=/ pelow                                                     |

| -                       | PB9                          | XIN            | -                                   | See footnote (3) below                                                     |

| -                       | PB8                          | XOUT           | -                                   | See loothote of below                                                      |

- Notes: 1. If PB12 is used as PIO input in user applications, a low level must be ensured at startup to prevent Flash erase before the user application sets PB12 into PIO mode,

- 2. In the product Datasheet Refer to: Slow Clock Generator of the Supply Controller section.

- 3. In the product Datasheet Refer to: 3 to 20 MHZ Crystal Oscillator information in PMC section.

#### 6.2.1 Serial Wire JTAG Debug Port (SWJ-DP) Pins

The SWJ-DP pins are TCK/SWCLK, TMS/SWDIO, TDO/SWO, TDI and commonly provided on a standard 20-pin JTAG connector defined by ARM. For more details about voltage reference and reset state, refer to Table 3-1 on page 6.

At startup, SWJ-DP pins are configured in SWJ-DP mode to allow connection with debugging probe. Please refer to the Debug and Test Section of the product datasheet.

SWJ-DP pins can be used as standard I/Os to provide users more general input/output pins when the debug port is not needed in the end application. Mode selection between SWJ-DP mode (System IO mode) and general IO mode is performed through the AHB Matrix Special Function Registers (MATRIX SFR). Configuration of the pad for pull-up, triggers, debouncing and glitch filters is possible regardless of the mode.

The JTAGSEL pin is used to select the JTAG boundary scan when asserted at a high level. It integrates a permanent pull-down resistor of about 15 k $\Omega$  to GND, so that it can be left unconnected for normal operations.

By default, the JTAG Debug Port is active. If the debugger host wants to switch to the Serial Wire Debug Port, it must provide a dedicated JTAG sequence on TMS/SWDIO and TCK/SWCLK which disables the JTAG-DP and enables the SW-DP. When the Serial Wire Debug Port is active, TDO/TRACESWO can be used for trace.

The asynchronous TRACE output (TRACESWO) is multiplexed with TDO. So the asynchronous trace can only be used with SW-DP, not JTAG-DP. For more information about SW-DP and JTAG-DP switching, please refer to the Debug and Test Section.