# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Features

- 80C52 Compatible

- 8051 Instruction Compatible

- Six 8-bit I/O Ports (64 Pins or 68 Pins Versions)

- Four 8-bit I/O Ports (44 Pins Version)

- Three 16-bit Timer/Counters

- 256 Bytes Scratch Pad RAM

- 9 Interrupt Sources with 4 Priority Levels

- Integrated Power Monitor (POR/PFD) to Supervise Internal Power Supply

- ISP (In-System Programming) Using Standard V<sub>CC</sub> Power Supply

- 2048 Bytes Boot ROM Contains Low Level Flash Programming Routines and a Default Serial Loader

- High-speed Architecture

- In Standard Mode:

- 40 MHz (Vcc 2.7V to 5.5V, both Internal and external code execution)

- 60 MHz (Vcc 4.5V to 5.5V and Internal Code execution only)

- In X2 mode (6 Clocks/machine cycle)

- 20 MHz (Vcc 2.7V to 5.5V, both Internal and external code execution)

- 30 MHz (Vcc 4.5V to 5.5V and Internal Code execution only)

- 64K Bytes On-chip Flash Program/Data Memory

- Byte and Page (128 Bytes) Erase and Write

- 100k Write Cycles

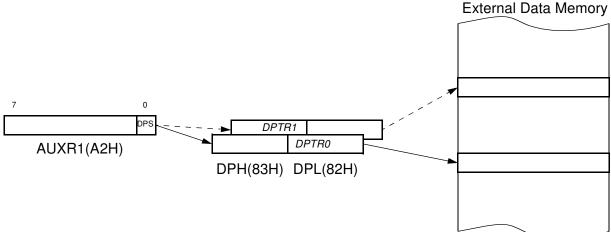

- On-chip 1792 bytes Expanded RAM (XRAM)

- Software Selectable Size (0, 256, 512, 768, 1024, 1792 Bytes)

- 768 Bytes Selected at Reset for T89C51RD2 Compatibility

- On-chip 2048 Bytes EEPROM Block for Data Storage (AT89C51ED2 Only)

- 100K Write Cycles

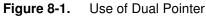

- Dual Data Pointer

- Variable Length MOVX for Slow RAM/Peripherals

- Improved X2 Mode with Independent Selection for CPU and Each Peripheral

- Keyboard Interrupt Interface on Port 1

- SPI Interface (Master/Slave Mode)

- 8-bit Clock Prescaler

- 16-bit Programmable Counter Array

- High Speed Output

- Compare/Capture

- Pulse Width Modulator

- Watchdog Timer Capabilities

- Asynchronous Port Reset

- Full-duplex Enhanced UART with Dedicated Internal Baud Rate Generator

- Low EMI (Inhibit ALE)

- · Hardware Watchdog Timer (One-time Enabled with Reset-Out), Power-off Flag

- Power Control Modes: Idle Mode, Power-down Mode

- Single Range Power Supply: 2.7V to 5.5V

- Industrial Temperature Range (-40 to +85°C)

- Packages: PLCC44, VQFP44, PLCC68, VQFP64

8-bit Flash Microcontroller

# AT89C51RD2 AT89C51ED2

### 1. Description

AT89C51RD2/ED2 is high performance CMOS Flash version of the 80C51 CMOS single chip 8bit microcontroller. It contains a 64-Kbyte Flash memory block for code and for data.

The 64-Kbytes Flash memory can be programmed either in parallel mode or in serial mode with the ISP capability or with software. The programming voltage is internally generated from the standard  $V_{CC}$  pin.

The AT89C51RD2/ED2 retains all of the features of the Atmel 80C52 with 256 bytes of internal RAM, a 9-source 4-level interrupt controller and three timer/counters. The AT89C51ED2 provides 2048 bytes of EEPROM for nonvolatile data storage.

In addition, the AT89C51RD2/ED2 has a Programmable Counter Array, an XRAM of 1792 bytes, a Hardware Watchdog Timer, SPI interface, Keyboard, a more versatile serial channel that facilitates multiprocessor communication (EUART) and a speed improvement mechanism (X2 Mode).

The fully static design of the AT89C51RD2/ED2 allows to reduce system power consumption by bringing the clock frequency down to any value, including DC, without loss of data.

The AT89C51RD2/ED2 has 2 software-selectable modes of reduced activity and an 8-bit clock prescaler for further reduction in power consumption. In the Idle mode the CPU is frozen while the peripherals and the interrupt system are still operating. In the Power-down mode the RAM is saved and all other functions are inoperative.

The added features of the AT89C51RD2/ED2 make it more powerful for applications that need pulse width modulation, high speed I/O and counting capabilities such as alarms, motor control, corded phones, and smart card readers.

| Package       | Flash (Bytes) | XRAM (Bytes) | Total RAM (Bytes) | I/O |

|---------------|---------------|--------------|-------------------|-----|

| PLCC44/VQFP44 | 64K           | 1792         | 2048              | 34  |

| PLCC68/VQFP64 | 64K           | 1792         | 2048              | 50  |

Table 1-1. Memory Size and I/O Pins

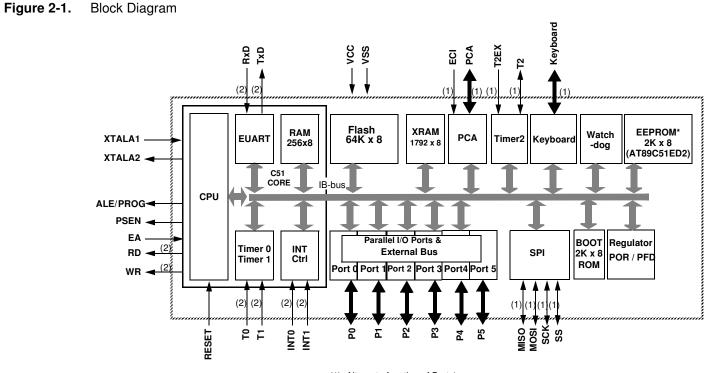

# 2. Block Diagram

<sup>(1):</sup> Alternate function of Port 1(2): Alternate function of Port 3

# 3. SFR Mapping

The Special Function Registers (SFRs) of the AT89C51RD2/ED2 fall into the following categories:

- C51 core registers: ACC, B, DPH, DPL, PSW, SP

- I/O port registers: P0, P1, P2, P3, PI2

- Timer registers: T2CON, T2MOD, TCON, TH0, TH1, TH2, TMOD, TL0, TL1, TL2, RCAP2L, RCAP2H

- Serial I/O port registers: SADDR, SADEN, SBUF, SCON

- PCA (Programmable Counter Array) registers: CCON, CCAPMx, CL, CH, CCAPxH, CCAPxL (x: 0 to 4)

- Power and clock control registers: PCON

- Hardware Watchdog Timer registers: WDTRST, WDTPRG

- Interrupt system registers: IE0, IPL0, IPH0, IE1, IPL1, IPH1

- Keyboard Interface registers: KBE, KBF, KBLS

- SPI registers: SPCON, SPSTR, SPDAT

- BRG (Baud Rate Generator) registers: BRL, BDRCON

- Clock Prescaler register: CKRL

- Others: AUXR, AUXR1, CKCON0, CKCON1

| Table 3-1.C51 Core SFRs |

|-------------------------|

|-------------------------|

| Mnemonic | Add | Name                   | 7  | 6  | 5  | 4   | 3   | 2  | 1  | 0 |

|----------|-----|------------------------|----|----|----|-----|-----|----|----|---|

| ACC      | E0h | Accumulator            |    |    |    |     |     |    |    |   |

| В        | F0h | B Register             |    |    |    |     |     |    |    |   |

| PSW      | D0h | Program Status Word    | CY | AC | F0 | RS1 | RS0 | OV | F1 | Р |

| SP       | 81h | Stack Pointer          |    |    |    |     |     |    |    |   |

| DPL      | 82h | Data Pointer Low Byte  |    |    |    |     |     |    |    |   |

| DPH      | 83h | Data Pointer High Byte |    |    |    |     |     |    |    |   |

#### Table 3-2.System Management SFRs

| Mnemonic | Add | Name                     | 7     | 6     | 5      | 4    | 3    | 2    | 1      | 0     |

|----------|-----|--------------------------|-------|-------|--------|------|------|------|--------|-------|

| PCON     | 87h | Power Control            | SMOD1 | SMOD0 | -      | POF  | GF1  | GF0  | PD     | IDL   |

| AUXR     | 8Eh | Auxiliary Register 0     | DPU   | -     | M0     | XRS2 | XRS1 | XRS0 | EXTRAM | AO    |

| AUXR1    | A2h | Auxiliary Register 1     | -     | -     | ENBOOT | -    | GF3  | 0    | -      | DPS   |

| CKRL     | 97h | Clock Reload Register    | -     | -     | -      | -    | -    | -    | -      | -     |

| CKCKON0  | 8Fh | Clock Control Register 0 | -     | WDTX2 | PCAX2  | SIX2 | T2X2 | T1X2 | T0X2   | X2    |

| CKCKON1  | AFh | Clock Control Register 1 | -     | -     | -      | -    | -    | -    | -      | SPIX2 |

#### Table 3-3.Interrupt SFRs

| Mnemonic | Add | Name                              | 7  | 6    | 5    | 4   | 3    | 2    | 1    | 0    |

|----------|-----|-----------------------------------|----|------|------|-----|------|------|------|------|

| IEN0     | A8h | Interrupt Enable Control 0        | EA | EC   | ET2  | ES  | ET1  | EX1  | ET0  | EX0  |

| IEN1     | B1h | Interrupt Enable Control 1        | -  | -    | -    | -   | -    | ESPI |      | KBD  |

| IPH0     | B7h | Interrupt Priority Control High 0 | -  | PPCH | PT2H | PHS | PT1H | PX1H | PT0H | PX0H |

| IPL0     | B8h | Interrupt Priority Control Low 0  | -  | PPCL | PT2L | PLS | PT1L | PX1L | PT0L | PX0L |

| IPH1     | B3h | Interrupt Priority Control High 1 | -  | -    | -    | -   | -    | SPIH |      | KBDH |

| IPL1     | B2h | Interrupt Priority Control Low 1  | -  | -    | -    | -   | -    | SPIL |      | KBDL |

#### Table 3-4.Port SFRs

| Mnemonic | Add | Name                            | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------|-----|---------------------------------|---|---|---|---|---|---|---|---|

| P0       | 80h | 8-bit Port 0                    |   |   |   |   |   |   |   |   |

| P1       | 90h | 8-bit Port 1                    |   |   |   |   |   |   |   |   |

| P2       | A0h | 8-bit Port 2                    |   |   |   |   |   |   |   |   |

| P3       | B0h | 8-bit Port 3                    |   |   |   |   |   |   |   |   |

| P4       | C0h | 8-bit Port 4                    |   |   |   |   |   |   |   |   |

| P5       | E8h | 8-bit Port 5                    |   |   |   |   |   |   |   |   |

| P5       | C7h | 8-bit Port 5 (byte addressable) |   |   |   |   |   |   |   |   |

### Table 3-5.Timer SFRs

| Mnemonic | Add | Name                                        | 7     | 6     | 5    | 4    | 3     | 2     | 1     | 0       |

|----------|-----|---------------------------------------------|-------|-------|------|------|-------|-------|-------|---------|

| TCON     | 88h | Timer/Counter 0 and 1 Control               | TF1   | TR1   | TF0  | TR0  | IE1   | IT1   | IE0   | IT0     |

| TMOD     | 89h | Timer/Counter 0 and 1 Modes                 | GATE1 | C/T1# | M11  | M01  | GATE0 | C/T0# | M10   | M00     |

| TL0      | 8Ah | Timer/Counter 0 Low Byte                    |       |       |      |      |       |       |       |         |

| TH0      | 8Ch | Timer/Counter 0 High Byte                   |       |       |      |      |       |       |       |         |

| TL1      | 8Bh | Timer/Counter 1 Low Byte                    |       |       |      |      |       |       |       |         |

| TH1      | 8Dh | Timer/Counter 1 High Byte                   |       |       |      |      |       |       |       |         |

| WDTRST   | A6h | WatchDog Timer Reset                        |       |       |      |      |       |       |       |         |

| WDTPRG   | A7h | WatchDog Timer Program                      | -     | -     | -    | -    | -     | WTO2  | WTO1  | WTO0    |

| T2CON    | C8h | Timer/Counter 2 control                     | TF2   | EXF2  | RCLK | TCLK | EXEN2 | TR2   | C/T2# | CP/RL2# |

| T2MOD    | C9h | Timer/Counter 2 Mode                        | -     | -     | -    | -    | -     | -     | T2OE  | DCEN    |

| RCAP2H   | CBh | Timer/Counter 2 Reload/Capture<br>High Byte |       |       |      |      |       |       |       |         |

| RCAP2L   | CAh | Timer/Counter 2 Reload/Capture<br>Low Byte  |       |       |      |      |       |       |       |         |

| TH2      | CDh | Timer/Counter 2 High Byte                   |       |       |      |      |       |       |       |         |

Table 3-5.Timer SFRs

| Mnemonic | Add | Name                     | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------|-----|--------------------------|---|---|---|---|---|---|---|---|

| TL2      | CCh | Timer/Counter 2 Low Byte |   |   |   |   |   |   |   |   |

#### Table 3-6. PCA SFRs

| Table 5-0     |     | 10/1  |                            |         |    |       |         |         |         |         |         |         |

|---------------|-----|-------|----------------------------|---------|----|-------|---------|---------|---------|---------|---------|---------|

| Mnemo<br>-nic | Add | Name  | 9                          | 7       |    | 6     | 5       | 4       | 3       | 2       | 1       | 0       |

| CCON          | D8h | PCA   | Timer/Counter Control      | CF      |    | CR    |         | CCF4    | CCF3    | CCF2    | CCF1    | CCF0    |

| CMOD          | D9h | PCA   | Timer/Counter Mode         | CIDL    | V  | VDTE  |         |         |         | CPS1    | CPS0    | ECF     |

| CL            | E9h | PCA   | Timer/Counter Low Byte     |         |    |       |         |         |         |         |         |         |

| СН            | F9h | PCA   | Timer/Counter High Byte    |         |    |       |         |         |         |         |         |         |

| CCAPM0        | DAh | PCA   | Timer/Counter Mode 0       |         | E  | COM0  | CAPP0   | CAPN0   | MAT0    | TOG0    | PWM0    | ECCF0   |

| CCAPM1        | DBh | PCA   | Timer/Counter Mode 1       |         | E  | COM1  | CAPP1   | CAPN1   | MAT1    | TOG1    | PWM1    | ECCF1   |

| CCAPM2        | DCh | PCA   | Timer/Counter Mode 2       |         | E  | COM2  | CAPP2   | CAPN2   | MAT2    | TOG2    | PWM2    | ECCF2   |

| ССАРМЗ        | DDh | PCA   | Timer/Counter Mode 3       |         | E  | СОМЗ  | CAPP3   | CAPN3   | MAT3    | TOG3    | PWM3    | ECCF3   |

| CCAPM4        | DEh | PCA   | Timer/Counter Mode 4       |         |    | COM4  | CAPP4   | CAPN4   | MAT4    | TOG4    | PWM4    | ECCF4   |

| CCAP0H        | FAh | PCA   | Compare Capture Module 0 H | CCAP0H7 | СС | AP0H6 | CCAP0H5 | CCAP0H4 | CCAP0H3 | CCAP0H2 | CCAP0H1 | CCAP0H0 |

| CCAP1H        | FBh | PCA   | Compare Capture Module 1 H | CCAP1H7 | CC | AP1H6 | CCAP1H5 | CCAP1H4 | CCAP1H3 | CCAP1H2 | CCAP1H1 | CCAP1H0 |

| CCAP2H        | FCh | PCA   | Compare Capture Module 2 H | CCAP2H7 | CC | AP2H6 | CCAP2H5 | CCAP2H4 | CCAP2H3 | CCAP2H2 | CCAP2H1 | CCAP2H0 |

| CCAP3H        | FDh | PCA   | Compare Capture Module 3 H | CCAP3H7 | CC | AP3H6 | CCAP3H5 | CCAP3H4 | CCAP3H3 | CCAP3H2 | CCAP3H1 | CCAP3H0 |

| CCAP4H        | FEh | PCA   | Compare Capture Module 4 H | CCAP4H7 | CC | AP4H6 | CCAP4H5 | CCAP4H4 | CCAP4H3 | CCAP4H2 | CCAP4H1 | CCAP4H0 |

| CCAP0L        | EAh | PCA   | Compare Capture Module 0 L | CCAP0L7 | СС | AP0L6 | CCAP0L5 | CCAP0L4 | CCAP0L3 | CCAP0L2 | CCAP0L1 | CCAP0L0 |

| CCAP1L        | EBh | PCA   | Compare Capture Module 1 L | CCAP1L7 | CC | AP1L6 | CCAP1L5 | CCAP1L4 | CCAP1L3 | CCAP1L2 | CCAP1L1 | CCAP1L0 |

| CCAP2L        | ECh | PCA   | Compare Capture Module 2 L | CCAP2L7 | CC | AP2L6 | CCAP2L5 | CCAP2L4 | CCAP2L3 | CCAP2L2 | CCAP2L1 | CCAP2L0 |

| CCAP3L        | EDh | PCA   | Compare Capture Module 3 L | CCAP3L7 | CC | AP3L6 | CCAP3L5 | CCAP3L4 | CCAP3L3 | CCAP3L2 | CCAP3L1 | CCAP3L0 |

| CCAP4L        | EEh | PCA   | Compare Capture Module 4 L | CCAP4L7 | CC | AP4L6 | CCAP4L5 | CCAP4L4 | CCAP4L3 | CCAP4L2 | CCAP4L1 | CCAP4L0 |

| Table 3-7     | 7.  | Seria | al I/O Port SFRs           |         |    |       |         |         |         |         |         |         |

| Mnemoni       | с   | Add   | Name                       | 7       |    | 6     | 5       | 4       | 3       | 2       | 1       | 0       |

| SCON          |     | 98h   | Serial Control             | FE/S    | M0 | SM1   | SM2     | REN     | TB8     | RB8     | ті      | RI      |

| SBUF          |     | 99h   | Serial Data Buffer         |         |    |       |         |         |         |         |         | 1       |

| SADEN         |     | B9h   | Slave Address Mask         |         |    |       |         |         |         |         |         |         |

| SADDR         |     | A9h   | Slave Address              |         |    |       |         |         |         |         |         |         |

#### Table 3-8.SPI Controller SFRs

9Bh

9Ah

**Baud Rate Control**

Baud Rate Reload

BDRCON

BRL

| Mnemonic | Add | Name        | 7    | 6    | 5     | 4    | 3    | 2    | 1    | 0    |

|----------|-----|-------------|------|------|-------|------|------|------|------|------|

| SPCON    | C3h | SPI Control | SPR2 | SPEN | SSDIS | MSTR | CPOL | CPHA | SPR1 | SPR0 |

| SPSTA    | C4h | SPI Status  | SPIF | WCOL | SSERR | MODF |      |      |      |      |

| SPDAT    | C5h | SPI Data    | SPD7 | SPD6 | SPD5  | SPD4 | SPD3 | SPD2 | SPD1 | SPD0 |

BRR

TBCK

RBCK

SPD

SRC

#### Table 3-9. Keyboard Interface SFRs

| Mnemonic | Add | Name                    | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|----------|-----|-------------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| KBLS     | 9Ch | Keyboard Level Selector | KBLS7 | KBLS6 | KBLS5 | KBLS4 | KBLS3 | KBLS2 | KBLS1 | KBLS0 |

| KBE      | 9Dh | Keyboard Input Enable   | KBE7  | KBE6  | KBE5  | KBE4  | KBE3  | KBE2  | KBE1  | KBE0  |

| KBF      | 9Eh | Keyboard Flag Register  | KBF7  | KBF6  | KBF5  | KBF4  | KBF3  | KBF2  | KBF1  | KBF0  |

### Table 3-10. EEPROM data Memory SFR (AT89C51ED2 only)

| Mnemonic | Add | Name                | 7 | 6 | 5 | 4 | 3 | 2 | 1   | 0      |

|----------|-----|---------------------|---|---|---|---|---|---|-----|--------|

| EECON    | D2h | EEPROM Data Control |   |   |   |   |   |   | EEE | EEBUSY |

### shows all SFRs with their address and their reset value.

#### Table 3-11.SFR Mapping

|     | Bit<br>Addressable                 |                    |                     | No                  | on Bit Addressal    | ble                 |                     |                                     |     |

|-----|------------------------------------|--------------------|---------------------|---------------------|---------------------|---------------------|---------------------|-------------------------------------|-----|

|     | 0/8                                | 1/9                | 2/A                 | 3/B                 | 4/C                 | 5/D                 | 6/E                 | 7/F                                 |     |

| F8h |                                    | CH<br>0000 0000    | CCAP0H<br>XXXX XXXX | CCAP1H<br>XXXX XXXX | CCAP2H<br>XXXX XXXX | CCAP3H<br>XXXX XXXX | CCAP4H<br>XXXX XXXX |                                     | FFh |

| F0h | B<br>0000 0000                     |                    |                     |                     |                     |                     |                     |                                     | F7h |

| E8h | P5 bit<br>addressable<br>1111 1111 | CL<br>0000 0000    | CCAP0L<br>XXXX XXXX | CCAP1L<br>XXXX XXXX | CCAP2L<br>XXXX XXXX | CCAP3L<br>XXXX XXXX | CCAP4L<br>XXXX XXXX |                                     | EFh |

| E0h | ACC<br>0000 0000                   |                    |                     |                     |                     |                     |                     |                                     | E7h |

| D8h | CCON<br>00X0 0000                  | CMOD<br>00XX X000  | CCAPM0<br>X000 0000 | CCAPM1<br>X000 0000 | CCAPM2<br>X000 0000 | CCAPM3<br>X000 0000 | CCAPM4<br>X000 0000 |                                     | DFh |

| D0h | PSW<br>0000 0000                   | FCON<br>XXXX 0000  | EECON<br>xxxx xx00  |                     |                     |                     |                     |                                     | D7h |

| C8h | T2CON<br>0000 0000                 | T2MOD<br>XXXX XX00 | RCAP2L<br>0000 0000 | RCAP2H<br>0000 0000 | TL2<br>0000 0000    | TH2<br>0000 0000    |                     |                                     | CFh |

| C0h | P4<br>1111 1111                    |                    |                     | SPCON<br>0001 0100  | SPSTA<br>0000 0000  | SPDAT<br>XXXX XXXX  |                     | P5 byte<br>Addressable<br>1111 1111 | C7h |

| B8h | IPL0<br>X000 000                   | SADEN<br>0000 0000 |                     |                     |                     |                     |                     |                                     | BFh |

| B0h | P3<br>1111 1111                    | IEN1<br>XXXX X000  | IPL1<br>XXXX X000   | IPH1<br>XXXX X000   |                     |                     |                     | IPH0<br>X000 0000                   | B7h |

| A8h | IEN0<br>0000 0000                  | SADDR<br>0000 0000 |                     |                     |                     |                     |                     | CKCON1<br>XXXX XXX0                 | AFh |

### Table 3-11. SFR Mapping

| A0h | P2<br>1111 1111   |                   | AUXR1<br>0XXX X0X0 |                     |                   |                  | WDTRST<br>XXXX XXXX | WDTPRG<br>XXXX X000 | A7h |

|-----|-------------------|-------------------|--------------------|---------------------|-------------------|------------------|---------------------|---------------------|-----|

| 98h | SCON<br>0000 0000 | SBUF<br>XXXX XXXX | BRL<br>0000 0000   | BDRCON<br>XXX0 0000 | KBLS<br>0000 0000 | KBE<br>0000 0000 | KBF<br>0000 0000    |                     | 9Fh |

| 90h | P1<br>1111 1111   |                   |                    |                     |                   |                  |                     | CKRL<br>1111 1111   | 97h |

| 88h | TCON<br>0000 0000 | TMOD<br>0000 0000 | TL0<br>0000 0000   | TL1<br>0000 0000    | TH0<br>0000 0000  | TH1<br>0000 0000 | AUXR<br>0X00 1000   | CKCON0<br>0000 0000 | 8Fh |

| 80h | P0<br>1111 1111   | SP<br>0000 0111   | DPL<br>0000 0000   | DPH<br>0000 0000    |                   |                  |                     | PCON<br>00X1 0000   | 87h |

|     | 0/8               | 1/9               | 2/A                | 3/B                 | 4/C               | 5/D              | 6/E                 | 7/F                 |     |

reserved

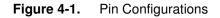

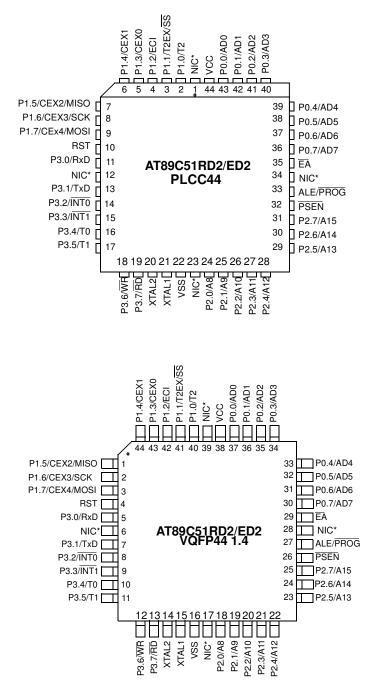

# 4. Pin Configurations

NIC: Not Internaly Connected

### Table 4-1.Pin Description

|                 |         | Pin N            | lumber                                  |                                         | -    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|-----------------|---------|------------------|-----------------------------------------|-----------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Mnemonic        | PLCC44  | VQFP44           | PLCC68                                  | VQFP64                                  | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| V <sub>SS</sub> | 22      | 16               | 51                                      | 40                                      | I    | Ground: 0V reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| V <sub>cc</sub> | 44      | 38               | 17                                      | 8                                       | I    | <b>Power Supply:</b> This is the power supply voltage for normal, idle and power-down operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| P0.0 - P0.7     | 43 - 36 | 37 - 30          | 15, 14,<br>12, 11,<br>9,6, 5, 3         | 6, 5, 3, 2,<br>64,<br>61,60,59          | I/O  | <b>Port 0</b> : Port 0 is an open-drain, bidirectional I/O port. Port 0 pins that have 1s written to them float and can be used as high impedance inputs Port 0 must be polarized to $V_{CC}$ or $V_{SS}$ in order to prevent any parasitic current consumption. Port 0 is also the multiplexed low-order address and data bus during access to external program and data memory. In this application, it uses strong internal pull-up when emitting 1s. Port 0 also inputs the code bytes during EPROM programming. External pull-ups are required during program verification during which P0 outputs the code bytes. |  |  |  |

| P1.0 - P1.7     | 2 - 9   | 40 - 44<br>1 - 3 | 19, 21,<br>22, 23,<br>25, 27,<br>28, 29 | 10, 12,<br>13, 14,<br>16, 18,<br>19, 20 | I/O  | <b>Port 1:</b> Port 1 is an 8-bit bidirectional I/O port with internal pull-ups. Port 1 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 1 pins that are externally pulled low will source current because of the internal pull-ups. Port 1 also receives the low-order address byte during memory programming and verification.<br>Alternate functions for AT89C51RD2/ED2 Port 1 include:                                                                                                                                                         |  |  |  |

|                 | 2       | 40               | 19                                      | 10                                      | I/O  | P1.0: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|                 |         |                  |                                         |                                         | I/O  | T2 (P1.0): Timer/Counter 2 external count input/Clockout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                 | 3       | 41               | 21                                      | 12                                      | I/O  | P1.1: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|                 |         |                  |                                         |                                         | I    | T2EX: Timer/Counter 2 Reload/Capture/Direction Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|                 |         |                  |                                         |                                         | I    | SS: SPI Slave Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                 | 4       | 42               | 22                                      | 13                                      | I/O  | P1.2: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|                 |         |                  |                                         |                                         | I    | ECI: External Clock for the PCA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|                 | 5       | 43               | 23                                      | 14                                      | I/O  | P1.3: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|                 |         |                  |                                         |                                         | I/O  | CEX0: Capture/Compare External I/O for PCA module 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|                 | 6       | 44               | 25                                      | 16                                      | I/O  | P1.4: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|                 |         |                  |                                         |                                         | I/O  | CEX1: Capture/Compare External I/O for PCA module 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|                 | 7       | 1                | 27                                      | 18                                      | I/O  | P1.5: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|                 |         |                  |                                         |                                         | I/O  | CEX2: Capture/Compare External I/O for PCA module 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|                 |         |                  |                                         |                                         | I/O  | MISO: SPI Master Input Slave Output line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                 |         |                  |                                         |                                         |      | When SPI is in master mode, MISO receives data from the slave peripheral. When SPI is in slave mode, MISO outputs data to the maste controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|                 | 8       | 2                | 28                                      | 19                                      | I/O  | P1.6: Input/Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|                 |         |                  |                                         |                                         | I/O  | CEX3: Capture/Compare External I/O for PCA module 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|                 |         |                  |                                         |                                         | I/O  | SCK: SPI Serial Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

### Table 4-1. Pin Description (Continued)

|             |                | Pin N        | lumber                                  |                                         | -    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|----------------|--------------|-----------------------------------------|-----------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mnemonic    | PLCC44         | VQFP44       | PLCC68                                  | VQFP64                                  | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|             | 9              | 3            | 29                                      | 20                                      | I/O  | P1.7: Input/Output:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|             |                |              |                                         |                                         | I/O  | CEX4: Capture/Compare External I/O for PCA module 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|             |                |              |                                         |                                         | I/O  | MOSI: SPI Master Output Slave Input line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|             |                |              |                                         |                                         |      | When SPI is in master mode, MOSI outputs data to the slave peripheral.<br>When SPI is in slave mode, MOSI receives data from the master<br>controller.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| XTALA1      | 21             | 15           | 49                                      | 38                                      | Ι    | <b>XTALA 1:</b> Input to the inverting oscillator amplifier and input to the internal clock generator circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| XTALA2      | 20             | 14           | 48                                      | 37                                      | 0    | XTALA 2: Output from the inverting oscillator amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| P2.0 - P2.7 | 24 - 31        | 18 - 25      | 54, 55,<br>56, 58,<br>59, 61,<br>64, 65 | 43, 44,<br>45, 47,<br>48, 50,<br>53, 54 | I/O  | <b>Port 2</b> : Port 2 is an 8-bit bidirectional I/O port with internal pull-ups. Port 2 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 2 pins that are externally pulled low will source current because of the internal pull-ups. Port 2 emits the high-order address byte during fetches from external program memory and during accesses to external data memory that use 16-bit addresses (MOVX @DPTR).In this application, it uses strong internal pull-ups emitting 1s. During accesses to external data memory that use 8-bit addresses (MOVX @Ri), port 2 emits the contents of the P2 SFR. |

| P3.0 - P3.7 | 11,<br>13 - 19 | 5,<br>7 - 13 | 34, 39,<br>40, 41,<br>42, 43,<br>45, 47 | 25, 28,<br>29, 30,<br>31, 32,<br>34, 36 | I/O  | <b>Port 3:</b> Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 3 pins that are externally pulled low will source current because of the internal pull-ups. Port 3 also serves the special features of the 80C51 family, as listed below.                                                                                                                                                                                                                                                                                     |

|             | 11             | 5            | 34                                      | 25                                      | Ι    | RXD (P3.0): Serial input port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|             | 13             | 7            | 39                                      | 28                                      | 0    | TXD (P3.1): Serial output port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             | 14             | 8            | 40                                      | 29                                      | I    | INT0 (P3.2): External interrupt 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|             | 15             | 9            | 41                                      | 30                                      | I    | INT1 (P3.3): External interrupt 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|             | 16             | 10           | 42                                      | 31                                      | I    | T0 (P3.4): Timer 0 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|             | 17             | 11           | 43                                      | 32                                      | I    | T1 (P3.5): Timer 1 external input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|             | 18             | 12           | 45                                      | 34                                      | 0    | WR (P3.6): External data memory write strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|             | 19             | 13           | 47                                      | 36                                      | 0    | RD (P3.7): External data memory read strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| P4.0 - P4.7 | -              | -            | 20, 24,<br>26, 44,<br>46, 50,<br>53, 57 | 11, 15,<br>17,33,<br>35,39,<br>42, 46   | I/O  | <b>Port 4:</b> Port 4 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 3 pins that are externally pulled low will source current because of the internal pull-ups.                                                                                                                                                                                                                                                                                                                                                                   |

| P5.0 - P5.7 | -              | -            | 60, 62,<br>63, 7, 8,<br>10, 13, 16      | 49, 51,<br>52, 62,<br>63, 1, 4, 7       | I/O  | <b>Port 5:</b> Port 5 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 3 pins that are externally pulled low will source current because of the internal pull-ups.                                                                                                                                                                                                                                                                                                                                                                   |

| RST         | 10             | 4            | 30                                      | 21                                      | I    | <b>Reset:</b> A high on this pin for two machine cycles while the oscillator is running, resets the device. An internal diffused resistor to $V_{SS}$ permits a power-on reset using only an external capacitor to $V_{CC}$ . This pin is an output when the hardware watchdog forces a system reset.                                                                                                                                                                                                                                                                                                                                                                       |

Table 4-1.

Pin Description (Continued)

|              |        | Pin N  | lumber |        | Turne |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------|--------|--------|--------|--------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mnemonic     | PLCC44 | VQFP44 | PLCC68 | VQFP64 | Туре  | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ALE/PRO<br>G | 33     | 27     | 68     | 56     | O (I) | Address Latch Enable/Program Pulse: Output pulse for latching the<br>low byte of the address during an access to external memory. In normal<br>operation, ALE is emitted at a constant rate of 1/6 (1/3 in X2 mode) the<br>oscillator frequency, and can be used for external timing or clocking. Note<br>that one ALE pulse is skipped during each access to external data<br>memory. This pin is also the program pulse input (PROG) during Flash<br>programming. ALE can be disabled by setting SFR's AUXR.0 bit. With<br>this bit set, ALE will be inactive during internal fetches. |

| PSEN         | 32     | 26     | 67     | 55     | 0     | <b>Program Strobe ENable:</b> The read strobe to external program memory.<br>When executing code from the external program memory, <u>PSEN</u> is<br>activated twice each machine cycle, except that two <u>PSEN</u> activations<br>are skipped during each access to external data memory. <u>PSEN</u> is not<br>activated during fetches from internal program memory.                                                                                                                                                                                                                 |

| EA           | 35     | 29     | 2      | 58     | I     | <b>External Access Enable:</b> EA must be externally held low to enable the device to fetch code from external program memory locations 0000H to FFFFH. If security level 1 is programmed, EA will be internally latched on Reset.                                                                                                                                                                                                                                                                                                                                                       |

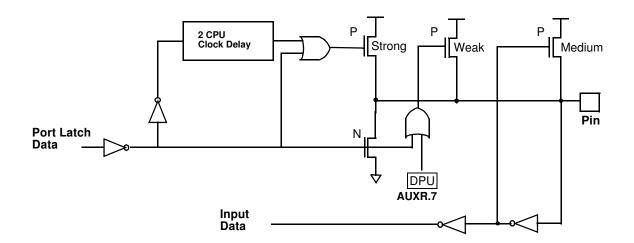

# 5. Port Types

AT89C51RD2/ED2 I/O ports (P1, P2, P3, P4, P5) implement the quasi-bidirectional output that is common on the 80C51 and most of its derivatives. This output type can be used as both an input and output without the need to reconfigure the port. This is possible because when the port outputs a logic high, it is weakly driven, allowing an external device to pull the pin low. When the pin is pulled low, it is driven strongly and able to sink a fairly large current. These features are somewhat similar to an open drain output except that there are three pull-up transistors in the quasi-bidirectional output that serve different purposes. One of these pull-ups, called the "weak" pull-up, is turned on whenever the port latch for the pin contains a logic 1. The weak pull-up sources a very small current that will pull the pin high if it is left floating. A second pull-up, called the "medium" pull-up, is turned on when the port latch for the pin contains a logic 1 and the pin itself is also at a logic 1 level. This pull-up provides the primary source current for a quasi-bidirectional pin that is outputting a 1. If a pin that has a logic 1 on it is pulled low by an external device, the medium pull-up turns off, and only the weak pull-up remains on. In order to pull the pin low under these conditions, the external device has to sink enough current to overpower the medium pull-up and take the voltage on the port pin below its input threshold.

The third pull-up is referred to as the "strong" pull-up. This pull-up is used to speed up low-tohigh transitions on a quasi-bidirectional port pin when the port latch changes from a logic 0 to a logic 1. When this occurs, the strong pull-up turns on for a brief time, two CPU clocks, in order to pull the port pin high quickly. Then it turns off again.

The DPU bit (bit 7 in AUXR register) allows to disable the permanent weak pull up of all ports when latch data is logical 0.

The quasi-bidirectional port configuration is shown in Figure 5-1.

Figure 5-1. Quasi-Bidirectional Output

# 6. Oscillator

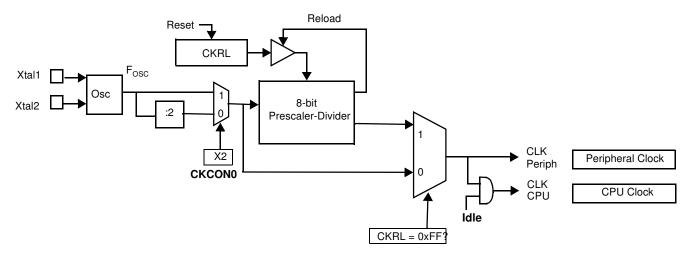

To optimize the power consumption and execution time needed for a specific task, an internal prescaler feature has been implemented between the oscillator and the CPU and peripherals.

### 6.1 Registers

Table 6-1.

CKRL Register

OKRL

Okada Dataset

CKRL - Clock Reload Register (97h)

| 7         |             | 6   | 5      | 4                                 | 3     | 2     | 1     | 0     |  |  |

|-----------|-------------|-----|--------|-----------------------------------|-------|-------|-------|-------|--|--|

| CKRL7     | CKRL7 CKRL6 |     | CKRL5  | CKRL4                             | CKRL3 | CKRL2 | CKRL1 | CKRL0 |  |  |

| Bit Numbe | ər          | Mne | emonic | Description                       |       |       |       |       |  |  |

| 7:0       | 7:0         |     | KRL    | Clock Reload R<br>Prescaler value | -     |       |       |       |  |  |

Reset Value = 1111 1111b Not bit addressable

### Table 6-2.PCON Register

PCON - Power Control Register (87h)

| 7                                                                                                      | 6                                   | 5    | 4                                                                                                                                                                                               | 3                | 2               | 1  | 0   |  |

|--------------------------------------------------------------------------------------------------------|-------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------|----|-----|--|

| SMOD1                                                                                                  | SMOD0                               | -    | POF                                                                                                                                                                                             | GF1              | GF0             | PD | IDL |  |

| Bit Numb                                                                                               | Bit Number Bit Mnemonic Description |      |                                                                                                                                                                                                 |                  |                 |    |     |  |

| 7                                                                                                      | S                                   | MOD1 | Serial Port Mod<br>Set to select do                                                                                                                                                             |                  | in mode 1, 2 or | 3. |     |  |

| 6                                                                                                      | S                                   | MOD0 | Serial Port Mode bit 0<br>Cleared to select SM0 bit in SCON register.<br>Set to select FE bit in SCON register.                                                                                 |                  |                 |    |     |  |

| 5                                                                                                      |                                     | -    | <b>Reserved</b><br>The value read from this bit is indeterminate. Do not set this bit.                                                                                                          |                  |                 |    |     |  |

| 4                                                                                                      |                                     | POF  | Power-off Flag           Cleared by software to recognize the next reset type.           Set by hardware when V <sub>CC</sub> rises from 0 to its nominal voltage. Can also be set by software. |                  |                 |    |     |  |

| 3                                                                                                      |                                     | GF1  | General-purpo<br>Cleared by softw<br>Set by software                                                                                                                                            | vare for general |                 | е. |     |  |

| 2                                                                                                      |                                     | GF0  | <b>General-purpose Flag</b><br>Cleared by software for general-purpose usage.<br>Set by software for general-purpose usage.                                                                     |                  |                 |    |     |  |

| 1                                                                                                      |                                     | PD   | Power-down Mode bit<br>Cleared by hardware when reset occurs.<br>Set to enter power-down mode.                                                                                                  |                  |                 |    |     |  |

| 0 IDL IDL Idle Mode bit<br>Cleared by hardware when interrupt or reset occu<br>Set to enter idle mode. |                                     |      |                                                                                                                                                                                                 |                  | ccurs.          |    |     |  |

Reset Value = 00X1 0000b Not bit addressable

### 6.2 Functional Block Diagram

Figure 6-1. Functional Oscillator Block Diagram

#### 6.2.1 Prescaler Divider

- A hardware RESET puts the prescaler divider in the following state:

- CKRL = FFh:  $F_{CLK CPU} = F_{CLK PERIPH} = F_{OSC}/2$  (Standard C51 feature)

- Any value between FFh down to 00h can be written by software into CKRL register in order to divide frequency of the selected oscillator:

- CKRL = 00h: minimum frequency  $F_{CLK CPU} = F_{CLK PERIPH} = F_{OSC}/1020$  (Standard Mode)  $F_{CLK CPU} = F_{CLK PERIPH} = F_{OSC}/510$  (X2 Mode)

- CKRL = FFh: maximum frequency  $F_{CLK CPU} = F_{CLK PERIPH} = F_{OSC}/2$  (Standard Mode)  $F_{CLK CPU} = F_{CLK PERIPH} = F_{OSC}$  (X2 Mode)

$F_{CLK CPU}$  and  $F_{CLK PERIPH}$

In X2 Mode, for CKRL<>0xFF:  $F_{CPU} = F_{CLKPERIPH} = \frac{F_{OSC}}{2 \times (255 - CKRL)}$

In X1 Mode, for CKRL<>0xFF then:

$F_{CPU} = F_{CLKPERIPH} = \frac{F_{OSC}}{4 \times (255 - CKRL)}$

# 7. Enhanced Features

In comparison to the original 80C52, the AT89C51RD2/ED2 implements some new features, which are:

- X2 option

- Dual Data Pointer

- Extended RAM

- Programmable Counter Array (PCA)

- Hardware Watchdog

- SPI interface

- 4-level interrupt priority system

- · Power-off flag

- ONCE mode

- ALE disabling

- Some enhanced features are also located in the UART and the Timer 2

### 7.1 X2 Feature

The AT89C51RD2/ED2 core needs only 6 clock periods per machine cycle. This feature called 'X2' provides the following advantages:

- Divide frequency crystals by 2 (cheaper crystals) while keeping same CPU power.

- Save power consumption while keeping same CPU power (oscillator power saving).

- Save power consumption by dividing dynamically the operating frequency by 2 in operating and idle modes.

- Increase CPU power by 2 while keeping same crystal frequency.

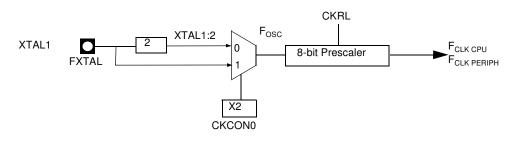

In order to keep the original C51 compatibility, a divider by 2 is inserted between the XTAL1 signal and the main clock input of the core (phase generator). This divider may be disabled by software.

### 7.1.1 Description

The clock for the whole circuit and peripherals is first divided by two before being used by the CPU core and the peripherals.

This allows any cyclic ratio to be accepted on XTAL1 input. In X2 mode, as this divider is bypassed, the signals on XTAL1 must have a cyclic ratio between 40 to 60%.

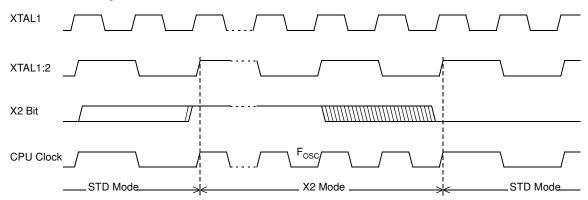

Figure 7-1 shows the clock generation block diagram. X2 bit is validated on the rising edge of the XTAL1  $\div$  2 to avoid glitches when switching from X2 to STD mode. Figure 7-2 shows the switching mode waveforms.

Figure 7-1. Clock Generation Diagram

Figure 7-2. Mode Switching Waveforms

The X2 bit in the CKCON0 register (see Table 7-1) allows a switch from 12 clock periods per instruction to 6 clock periods and vice versa. At reset, the speed is set according to X2 bit of Hardware Security Byte (HSB). By default, Standard mode is active. Setting the X2 bit activates the X2 feature (X2 mode).

The T0X2, T1X2, T2X2, UartX2, PcaX2, and WdX2 bits in the CKCON0 register (Table 7-1) and SPIX2 bit in the CKCON1 register (see Table 7-2) allows a switch from standard peripheral speed (12 clock periods per peripheral clock cycle) to fast peripheral speed (6 clock periods per peripheral clock cycle). These bits are active only in X2 mode.

Table 7-1.CKCON0 RegisterCKCON0 - Clock Control Register (8Fh)

| 7             | 6               | 5                                             | 4                                                                                                                                                                                                                                                         | 3    | 2    | 1    | 0  |  |  |  |

|---------------|-----------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|----|--|--|--|

| -             | WDX2            | PCAX2                                         | SIX2                                                                                                                                                                                                                                                      | T2X2 | T1X2 | T0X2 | X2 |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                   | Description                                                                                                                                                                                                                                               |      |      |      |    |  |  |  |

| 7             | Reserved        | The values for                                | The values for this bit are indeterminite. Do not set this bit.                                                                                                                                                                                           |      |      |      |    |  |  |  |

| 6             | WDX2            | (This control b<br>effect).<br>Cleared to sel | Watchdog Clock<br>(This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no<br>effect).<br>Cleared to select 6 clock periods per peripheral clock cycle.<br>Set to select 12 clock periods per peripheral clock cycle. |      |      |      |    |  |  |  |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                                                                                                                                                              |

|---------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5             | PCAX2           | Programmable Counter Array Clock<br>(This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no<br>effect).<br>Cleared to select 6 clock periods per peripheral clock cycle. Set to select 12 clock<br>periods per peripheral clock cycle.                                                                              |

| 4             | SIX2            | Enhanced UART Clock (Mode 0 and 2)<br>(This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no<br>effect).<br>Cleared to select 6 clock periods per peripheral clock cycle. Set to select 12 clock<br>periods per peripheral clock cycle.                                                                            |

| 3             | T2X2            | <b>Timer2 Clock</b><br>(This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no effect).<br>Cleared to select 6 clock periods per peripheral clock cycle.<br>Set to select 12 clock periods per peripheral clock cycle.                                                                                              |

| 2             | T1X2            | <b>Timer1 Clock</b><br>(This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no effect).<br>Cleared to select 6 clock periods per peripheral clock cycle. Set to select 12 clock periods per peripheral clock cycle.                                                                                                 |

| 1             | T0X2            | Timer0 Clock<br>(This control bit is validated when the CPU clock X2 is set; when X2 is low, this bit has no<br>effect).<br>Cleared to select 6 clock periods per peripheral clock cycle. Set to select 12 clock<br>periods per peripheral clock cycle.                                                                                                  |