Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## **INTEGRATED CIRCUITS**

# DATA SHEET

# **AU5780A**SAE/J1850/VPW transceiver

Product data Supersedes data of 1999 Jan 28

## SAE/J1850/VPW transceiver

**AU5780A**

#### **FEATURES**

- Supports SAE/J1850 VPW standard for in-vehicle class B multiplexing

- Bus speed 10.4 kbps nominal

- Drive capability 32 bus nodes

- Low RFI due to output waveshaping with adjustable slew rate

- Direct battery operation with protection against +50V load dump, jump start and reverse battery

- Bus terminals proof against automotive transients up to -200V/+200V

- Thermal overload protection

- Very low bus idle power consumption

- Diagnostic loop-back mode

- 4X mode (41.6 kbps) reception capability

- ESD protected to 9 KV on bus and battery pins

- 8-pin SOIC

#### **DESCRIPTION**

The AU5780A is a line transceiver being primarily intended for in-vehicle multiplex applications. It provides interfacing between a link controller and the physical bus wire. The device supports the SAE/J1850 VPWM standard with a nominal bus speed of 10.4 kbps.

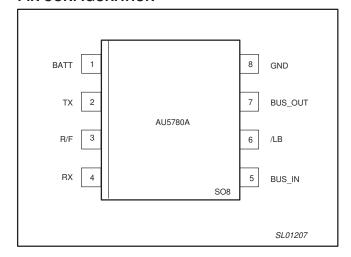

#### PIN CONFIGURATION

#### **QUICK REFERENCE DATA**

| SYMBOL                          | PARAMETER                                               | CONDITIONS                                                                                                                                                       | MIN. | TYP. | MAX. | UNIT |

|---------------------------------|---------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>BATT.op</sub>            | Operating supply voltage                                |                                                                                                                                                                  | 6    | 12   | 24   | V    |

| T <sub>A</sub>                  | Operating ambient temperature                           |                                                                                                                                                                  | -40  |      | +125 | °C   |

| V <sub>BATT.ld</sub>            | Battery voltage                                         | load dump; 1s                                                                                                                                                    |      |      | +50  | V    |

| I <sub>BATT.lp</sub>            | Bus idle supply current                                 | V <sub>BATT</sub> =12V                                                                                                                                           |      |      | 220  | μА   |

| V <sub>B</sub>                  | Bus voltage                                             | 0 < V <sub>BATT</sub> < 24V                                                                                                                                      | -20  |      | +20  | V    |

| V <sub>BOH</sub>                | Bus output voltage                                      | $300\Omega < R_L < 1.6k\Omega$                                                                                                                                   | 7.3  |      | 8.0  | V    |

| -I <sub>BO.LIM</sub>            | Bus output source current                               | 0V < V <sub>BO</sub> < +6.0V                                                                                                                                     | 27   |      | 50   | mA   |

| V <sub>BI</sub>                 | Bus input threshold                                     |                                                                                                                                                                  | 3.65 |      | 4.1  | V    |

| t <sub>bo</sub>                 | Delay TX to BUS_OUT, normal battery                     | Measured at 3.875V                                                                                                                                               | 13   |      | 21   | μs   |

| t <sub>r</sub> , t <sub>f</sub> | BUS_OUT transition times, rise and fall, normal battery | Measured between 1.5 V and ( $V_{BATT} - 2.75$ V), 9 < $V_{BATT}$ < 16 V, $t_r$ tested at an additional bus load of $R_{LOAD} = 400$ Ω and $C_{LOAD} = 22000$ pF | 11   |      | 18   | μs   |

## **ORDERING INFORMATION**

| DESCRIPTION                              | TEMPERATURE RANGE | ORDER CODE | DWG#    |

|------------------------------------------|-------------------|------------|---------|

| SO8: 8-pin plastic small outline package | -40 to +125°C     | AU5780AD   | SOT96-1 |

## SAE/J1850/VPW transceiver

AU5780A

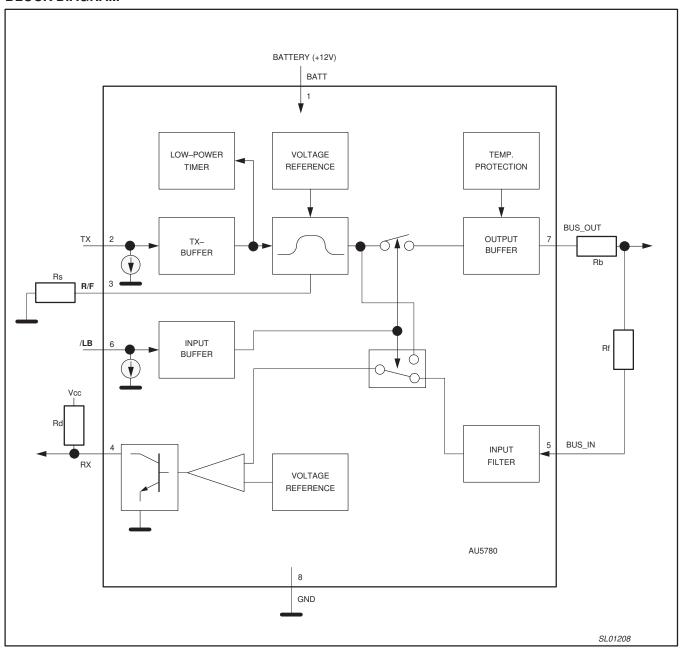

## **BLOCK DIAGRAM**

## SAE/J1850/VPW transceiver

AU5780A

#### PIN DESCRIPTION

| SYMBOL  | PIN | DESCRIPTION                                                                                         |

|---------|-----|-----------------------------------------------------------------------------------------------------|

| BATT    | 1   | Battery supply input (12V nom.)                                                                     |

| TX      | 2   | Transmit data input; low: transmitter passive; high: transmitter active                             |

| R/F     | 3   | Rise/fall slew rate set input                                                                       |

| RX      | 4   | Receive data output; low: active bus condition detected; float/high: passive bus condition detected |

| BUS_IN  | 5   | Bus line receive input                                                                              |

| /LB     | 6   | Loop-back test mode control input; low: loop-back mode; high: normal communication mode             |

| BUS_OUT | 7   | Bus line transmit output                                                                            |

| GND     | 8   | Ground                                                                                              |

#### **FUNCTIONAL DESCRIPTION**

The AU5780A is an integrated line transceiver IC that interfaces an SAE/J1850 protocol controller IC to the vehicle's multiplexed bus line. It is primarily intended for automotive "Class B" multiplexing applications in passenger cars using VPW (Variable Pulse Width) modulated signals with a nominal bit rate of 10.4 kbps. The AU5780A also receives messages in the so-called 4X mode where data is transmitted with a typical bit rate of 41.6 kbps. The device provides transmit and receive capability as well as protection to a J1850 electronic module.

A J1850 link controller feeds the transmit data stream to the transceiver's TX input. The AU5780A transceiver waveshapes the TX data input signal with controlled rise & fall slew rates and rounded shape. The bus output signal is transmitted with both voltage and current control. The BUS\_IN input is connected to the physical bus line via an external resistor. The external resistor and an internal capacitance provides filtering against RF bus noise. The incoming signal is output at the RX pin being connected to the J1850 link controller.

If the TX input is idle for a certain time, then the AU5780A enters a low-power mode. This mode is dedicated to help meet ignition-off current draw requirements. The BUS\_IN input comparator is kept alive in the low-power mode. Normal power mode will be entered again upon detection of activity, i.e., rising edge at the TX input. The device is able to receive and transmit a valid J1850 message when initially in low-power mode.

The AU5780A features special robustness at its BATT and BUS\_OUT pins hence the device is well suited for applications in

the automotive environment. Specifically, the BATT input is protected against 50V load dump, jump start and reverse battery condition. The BUS\_OUT output is protected against wiring fault conditions, e.g., short circuit to battery voltage as well as typical automotive transients (i.e., -200V/+200V). In addition, an overtemperature shutdown function with hysteresis is incorporated which protects the device under system fault conditions. The chip temperature is sensed at the bus drive transistor in the output buffer. In case of the chip temperature reaching the trip point, the AU5780A will latch-off the transceiver function. The device is reset on the first rising edge on the TX input after a small decrease of the chip temperature.

The AU5780A also provides a loop-back mode for diagnostic purpose. If the /LB pin is open circuit or pulled low, then TX signal is internally looped back to the RX output independent of the signals on the bus. In this mode the electronic module is disconnected from the bus, i.e., the TX signal is not output to the physical bus line. In this mode, it can be used, e.g., for self-test purpose.

The AU5780A is an enhanced successor of the AU5780. The AU5780A provides improved wave shaping when exiting the low power standby mode for reduced EMI. Several parameters that were formerly only characterized to the maximum normal operating supply of 16 volts, have now been characterized to 24 volt supplies. These parameters which are tested and guaranteed to 24 volts are identified with appropriate test conditions in the "conditions" columns of the Characteristics tables, otherwise the conditions at the top of the characteristic table applies to all parameters.

## SAE/J1850/VPW transceiver

AU5780A

## **CONTROL INPUT SUMMARY**

| тх | /LB | MODE          | BIT VALUE                  | BUS_OUT | RX<br>(out)            |

|----|-----|---------------|----------------------------|---------|------------------------|

| 0  | 0   | Loop-back     | TX passive (default state) | float   | float (high)           |

| 1  | 0   | Loop-back     | TX active                  | float   | low                    |

| 0  | 1   | Communication | Transmitter passive        | float   | bus state <sup>1</sup> |

| 1  | 1   | Communication | Transmitter active         | high    | low                    |

#### NOTE

## **ABSOLUTE MAXIMUM RATINGS**

According to the IEC 134 Absolute Maximum System; operation is not guaranteed under these conditions; all voltages are referenced to pin 8 (GND); positive currents flow into the IC; unless otherwise specified.

| SYMBOL                | PARAMETER                                   | CONDITIONS                                                                 | MIN. | MAX. | UNIT |

|-----------------------|---------------------------------------------|----------------------------------------------------------------------------|------|------|------|

| $V_{BATT}$            | supply voltage                              |                                                                            | -20  | +24  | V    |

| V <sub>BATT.ld</sub>  | short-term supply voltage                   | load dump; t < 1s                                                          |      | +50  | V    |

| V <sub>BATT.tr1</sub> | transient supply voltage                    | SAE J1113 pulse 1                                                          | -100 |      | V    |

| V <sub>BATT.tr2</sub> | transient supply voltage                    | SAE J1113 pulses 2                                                         |      | +150 | V    |

| V <sub>BATT.tr3</sub> | transient supply voltage                    | SAE J1113 pulses 3A, 3B                                                    | -200 | +200 | V    |

| V <sub>B</sub>        | Bus voltage                                 | $R_f > 10 \text{ k}\Omega$ ; Rb >10Ω <sup>1</sup>                          | -20  | +20  | V    |

| V <sub>B.tr1</sub>    | transient bus voltage                       | SAE J1113 pulse 1                                                          | -50  |      | V    |

| V <sub>B.tr2</sub>    | transient bus voltage                       | SAE J1113 pulses 2                                                         |      | +100 | V    |

| V <sub>B.tr3</sub>    | transient bus voltage                       | SAE J1113 pulses 3A, 3B                                                    | -200 | +200 | V    |

| VI                    | DC voltage on pins TX, R/F, RX, /LB         |                                                                            | -0.3 | 7    | V    |

| ESD <sub>BATT</sub>   | ESD capability of BATT pin                  | Air gap discharge,<br>R=2kΩ, C=150pF                                       | -9   | +9   | kV   |

| ESD <sub>bus</sub>    | ESD capability of BUS_OUT and BUS_IN pins   | Air gap discharge, R=2k $\Omega$ , C=150pF, R <sub>f</sub> > 10 k $\Omega$ | -9   | +9   | kV   |

| ESD <sub>logic</sub>  | ESD capability of TX, RX, R/F, and /LB pins | Human Body, R=1.5kΩ, C=100pF                                               | -2   | +2   | kV   |

| P <sub>tot</sub>      | maximum power dissipation                   | at T <sub>amb</sub> = +125 °C                                              |      | 164  | mW   |

| $\Theta_{JA}$         | thermal impedance                           |                                                                            |      | 152  | °C/W |

| T <sub>amb</sub>      | operating ambient temperature               |                                                                            | -40  | +125 | °C   |

| T <sub>stg</sub>      | storage temperature                         |                                                                            | -40  | +150 | °C   |

| T <sub>vj</sub>       | junction temperature                        |                                                                            | -40  | +150 | °C   |

| T <sub>LEAD</sub>     | Lead temperature                            | Soldering, 10 seconds maximum                                              |      | 265  | °C   |

| I <sub>CL(BUS)</sub>  | Bus output clamp current                    | No latch-up,  V <sub>BUS</sub>   = 25 V                                    |      | 100  | mA   |

| I <sub>CL(BATT)</sub> | Battery clamp current                       | No latch-up or snap back,  V <sub>BATT</sub>   = 25 V                      |      | 100  | mA   |

### NOTE:

<sup>1.</sup> RX outputs the bus state. If the bus level is below the receiver threshold (i.e., all transmitters passive), then RX will be floating (i.e., high, considering external pull-up resistance). Otherwise, if the bus level is above the receiver threshold (i.e., at least one transmitter is active), then RX will be low.

<sup>1.</sup> For bus voltages  $-20V < V_{bus} < -17V$  and  $+17V < V_{bus} < +20V$  the current is limited by the external resistors  $R_b$  and  $R_f$ .

## SAE/J1850/VPW transceiver

AU5780A

## **CHARACTERISTICS**

$-40^{\circ} C < T_{amb} < +125^{\circ} C; \, 6V < V_{BATT} < 16V; \, V_{/LB} > 3V; \, 0 < V_{BUS} < +8.5V; \, 0 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000 < 0.000$

$R_S = 56.2 \text{ k}\Omega \quad R_d = 10 \text{ k}\Omega; \ R_f = 15 \text{ k}\Omega; \ R_b = 10\Omega; \ 300 \ \Omega < R_L < 1.6 \text{ k}\Omega;$  all voltages are referenced to pin 8 (GND); positive currents flow into the IC; unless otherwise specified.

| SYMBOL                 | PARAMETER                                      | CONDITIONS                                                                                      | MIN.                    | TYP. | MAX.  | UNIT |

|------------------------|------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------------------|------|-------|------|

| I <sub>BATT.id</sub>   | supply current; bus idle                       | TX low; Note 1                                                                                  |                         |      | 220   | μΑ   |

| I <sub>BATT.p</sub>    | supply current; passive state                  | TX low                                                                                          |                         |      | 1.5   | mA   |

| I <sub>BATT.oc</sub>   | supply current; no load                        | TX high                                                                                         |                         |      | 8     | mA   |

| I <sub>BATT(SB)</sub>  | supply current; bus output short to battery    | BUS to V <sub>BATT</sub> ; no I <sub>BO</sub> current, V <sub>TX</sub> = high                   |                         |      | 10    | mA   |

| I <sub>BATT.sc</sub>   | supply current; bus short to GND               | TX high, V <sub>BO</sub> = 0V                                                                   |                         |      | 60    | mA   |

| T <sub>sd</sub>        | Thermal shutdown                               |                                                                                                 | 155                     |      | 170   | °C   |

| T <sub>hys</sub>       | Thermal shutdown hysteresis                    |                                                                                                 | 5                       |      | 15    | °C   |

| T <sub>DTYCY24</sub>   | Thermal shutdown, transmit duty cycle, at 24 V | Bus load, $R_{LOAD}$ = 300 $\Omega$ , $C_{LOAD}$ = 16.55 nF, $V_{BATT}$ = 24 V, T = 128 $\mu s$ | 33                      |      |       | %    |

| T <sub>DTYCY20</sub>   | Thermal shutdown, transmit duty cycle, at 20 V | Bus load, $R_{LOAD}$ = 300 $\Omega$ , $C_{LOAD}$ = 16.55 nF, $V_{BATT}$ = 20 V, T = 128 $\mu s$ | 45                      |      |       | %    |

| Pins TX and            | /LB                                            | •                                                                                               |                         |      |       |      |

| V <sub>ih</sub>        | High level input voltage                       | 6 V < V <sub>BATT</sub> < 24 V                                                                  | 3                       |      |       | V    |

| V <sub>ILTX</sub>      | Low level input voltage, TX pin                | 6 V < V <sub>BATT</sub> < 24 V                                                                  |                         |      | 0.9   | V    |

| V <sub>ilB</sub>       | Low level input voltage, LB pin                | 6V < V <sub>BATT</sub> < 24 V                                                                   |                         |      | 0.8   | V    |

| V <sub>h</sub>         | Input hysteresis                               |                                                                                                 | 0.4                     |      |       | V    |

| C <sub>TX</sub>        | TX input capacitance                           | Intrinsic to part                                                                               |                         |      | 5     | pf   |

| I <sub>ih2</sub>       | TX high level input current                    | V <sub>i</sub> = 5V                                                                             | 12                      |      | 50    | μΑ   |

| I <sub>ih6</sub>       | /LB high level input current                   | V <sub>i</sub> = 5V                                                                             | 4                       |      | 10    | μΑ   |

| Pin RX                 |                                                |                                                                                                 | •                       |      |       |      |

| V <sub>ol</sub>        | Low level output voltage                       | I <sub>o</sub> = 1.6 mA                                                                         |                         |      | 0.4   | V    |

| l <sub>ih</sub>        | High level output leakage                      | V <sub>o</sub> = 5V, BUS_IN = low                                                               | -10                     |      | +10   | μΑ   |

| I <sub>rx</sub>        | RX output current                              | V <sub>0</sub> = 5V                                                                             | 4                       |      | 20    | mA   |

| Pin BUS_OU             | т                                              | •                                                                                               | •                       |      |       |      |

| V <sub>olb</sub>       | BUS_OUT in loop-back mode; TX high or low      | /LB low or floating;<br>$0 < V_{BATT} < 24V$ ; $R_L=1.6k\Omega$                                 |                         |      | 0.1   | ٧    |

| V <sub>ol</sub>        | BUS_OUT voltage; passive                       | TX low or floating;<br>0 <v<sub>BATT &lt; 24V; R<sub>L</sub>=1.6k<math>\Omega</math></v<sub>    |                         |      | 0.075 | V    |

| V <sub>oh</sub>        | BUS_OUT voltage; active                        | TX high; Note 2 $9V < V_{BATT} < 24V$ ; $300\Omega < R_L < 1.6k\Omega$ ;                        | 7.3                     |      | 8     | V    |

| V <sub>ohLOWB</sub>    | BUS_OUT voltage; low battery                   | TX high; $6V < V_{BATT} < 9V; \\ 300\Omega < R_L < 1.6k\Omega; \\ Note 2$                       | V <sub>BATT</sub> – 1.7 |      | 8     | V    |

| – I <sub>BO.LIM</sub>  | BUS_OUT source current; bus positive           | TX high; 9V <v<sub>BATT&lt;24V<br/>0V&lt; V<sub>bus</sub> &lt;+6.0V</v<sub>                     |                         | 50   | mA    |      |

| – I <sub>BO.LIMn</sub> | BUS_OUT source current; bus negative           | TX high; 9V <v<sub>BATT&lt;24V<br/>-17V&lt; V<sub>bus</sub> &lt; 0V</v<sub>                     |                         | 55   | mA    |      |

## SAE/J1850/VPW transceiver

AU5780A

| SYMBOL                                      | PARAMETER                                                    | CONDITIONS                                                                                                                                       | MIN.       | TYP. | MAX.                | UNIT |

|---------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|---------------------|------|

| – I <sub>BO.LK.HO</sub>                     | BUS_OUT leakage current; TX high; bus low or operational     | -17 < V <sub>BUS</sub> < 8.5 V;<br>TX = high;<br>0 V < V <sub>BATT</sub> < 24 V                                                                  | -10        |      | I <sub>BO.LIM</sub> | μА   |

| – I <sub>BO.LK.HH</sub>                     | BUS_OUT leakage current; TX high; bus positive               | 8.5 V < V <sub>BUS</sub> < 17 V;<br>TX = high;<br>0 V < V <sub>BATT</sub> < 24 V                                                                 | TX = high; |      |                     | μА   |

| – I <sub>BO.LK</sub>                        | BUS_OUT leakage current; TX low; bus positive                | TX low; 0V <v<sub>BATT&lt;24V;<br/>0.1V&lt; V<sub>bus</sub> &lt;+17V</v<sub>                                                                     | -10        |      | +10                 | μΑ   |

| – I <sub>BO.N</sub>                         | BUS_OUT leakage current; TX low; bus negative                | TX low; 0.1V <v<sub>BATT&lt;24V;<br/>-17V&lt; V<sub>bus</sub> &lt; 0V</v<sub>                                                                    |            |      |                     | μΑ   |

| – I <sub>BO.LOG</sub>                       | BUS_OUT leakage current with loss of ground                  | -17 V < V <sub>BUS</sub> < 17 V;<br>0 V <v<sub>BATT &lt; 1 V</v<sub>                                                                             | -10        |      | 100                 | μА   |

| C <sub>BUSOUT</sub>                         | Bus output capacitance                                       |                                                                                                                                                  |            |      | 20                  | pF   |

| Pin BUS_IN                                  |                                                              |                                                                                                                                                  |            |      |                     |      |

| $V_{ih}$                                    | Input high voltage                                           |                                                                                                                                                  | 4.1        |      |                     | V    |

| V <sub>il</sub>                             | Input low voltage                                            |                                                                                                                                                  |            |      | 3.65                | V    |

| V <sub>h</sub>                              | Input hysteresis                                             |                                                                                                                                                  | 100        |      |                     | mV   |

| I <sub>BIN</sub>                            | Input bias current                                           | $-17V < V_{bus} < +17V$                                                                                                                          | <b>-</b> 5 |      | +5                  | μΑ   |

| I <sub>BIN(MAX)</sub>                       | BUS_IN input current maximum with and without loss of ground | -17 < V <sub>BUS</sub> < 17 V;<br>0 V < V <sub>BATT</sub> < 24 V;<br>VTX high or low                                                             | -100       |      | 100                 | μА   |

| C <sub>BUSIN</sub> ,                        | Bus input capacitance                                        |                                                                                                                                                  | 10         |      | 20                  | pF   |

| T <sub>DRXON</sub> ,<br>t <sub>DRXOFF</sub> | Bus line to RX propagation delay, normal and 4X modes        | Measured at V <sub>BUSIN_HIGH</sub> or V <sub>BUSIN_LOW</sub> to RX; $6 < V_{BATT} < 24 \text{ V}$ ; of R <sub>LOAD</sub> = 10 K $\Omega$ to 5 V | 0.4        |      | 1.7                 | μs   |

## SAE/J1850/VPW transceiver

AU5780A

### **DYNAMIC CHARACTERISTICS**

$-40^{\circ} C < T_{amb} < +125^{\circ} C; \, 9V < V_{BATT} < 16V; \, V_{/LB} > 3V; \, 0V < V_{BUS} < +8.5V; \,$

$$\begin{split} R_S = 56.2 \text{ k}\Omega; \ R_d = 10 \text{ k}\Omega; \ R_f = 15 \text{ k}\Omega; \ R_b = 10\Omega; \ BUS\_OUT: 300\Omega < R_L < 1.6 \text{ k}\Omega; \\ 1.7 \text{ } \mu s < (R_L * C_L) < 5.2 \text{ } \mu s; \ 2.2 \text{ nF} < C_L < 16.55 \text{ nF}; \ R_X: \ C_L < 40 \text{pF}; \ unless otherwise specified.} \end{split}$$

| SYMBOL                                                      | PARAMETER                                                | CONDITIONS                                                                                                                                                                                                         | MIN.                                 | TYP. | MAX.                                     | UNIT  |

|-------------------------------------------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------|------------------------------------------|-------|

| Pins TX, RX,                                                | /LB                                                      |                                                                                                                                                                                                                    |                                      |      |                                          |       |

| t <sub>pl</sub>                                             | Delay TX to RX rising and falling edge in loop-back mode | /LB low<br>6 V < V <sub>BATT</sub> < 24 V                                                                                                                                                                          | 15                                   |      | 24                                       | μs    |

| t <sub>dlb</sub>                                            | Delay /LB to BUS_OUT                                     | TX high, toggle /LB                                                                                                                                                                                                | 1                                    |      | 10                                       | μs    |

| Pin BUS_OU                                                  | T                                                        |                                                                                                                                                                                                                    | •                                    |      | •                                        |       |

| t <sub>bo</sub>                                             | Delay TX to BUS_OUT, normal battery                      | Measured at 3.875V, Note 3                                                                                                                                                                                         | 13                                   |      | 21                                       | μs    |

| t <sub>bo_hibatt</sub>                                      | Delay TX to BUS_OUT, high battery                        | Measured at 3.875V,<br>16V < V <sub>BATT</sub> < 24V, Note 3                                                                                                                                                       | 13                                   |      | 21                                       | μs    |

| t <sub>bo_lobatt</sub>                                      | Delay TX to BUS_OUT, low battery                         | Measured at 3.875V,<br>6V < V <sub>BATT</sub> < 9V, Note 3                                                                                                                                                         | 13                                   |      | 22                                       | μs    |

| t <sub>r</sub> , t <sub>f</sub>                             | BUS_OUT transition times, rise and fall, normal battery  | Measured between 1.5 V and ( $V_{BATT}$ – 2.75 V), 9 < $V_{BATT}$ < 16 V, $t_r$ tested at an additional bus load of $R_{LOAD}$ = 400 $\Omega$ and $C_{LOAD}$ = 22000 pF                                            | 11                                   |      | 18                                       | με    |

| t <sub>r_hibatt</sub> ,<br>t <sub>f_hibatt</sub>            | BUS_OUT transition times, rise and fall, high battery    | Measured between 1.5 V and 6.25 V, $16 < V_{BATT} < 24 V$ , $t_r$ tested at an additional bus load of $R_{LOAD} = 400 \Omega$ and $C_{LOAD} = 22000 \text{ pF}$                                                    | 11                                   |      | 18                                       | μs    |

| <sup>t</sup> r_lobatt <sup>,</sup><br><sup>t</sup> f_lobatt | BUS_OUT transition times, rise and fall, low battery     | Measured between 1.5 V and 6.25 V, 6 < V <sub>BATT</sub> < 9 V, $t_r$ tested at an additional bus load of R <sub>LOAD</sub> = 400 $\Omega$ and C <sub>LOAD</sub> = 22000 pF                                        | (V <sub>BATT</sub> – 4.25)<br>/ 0.43 |      | (V <sub>BATT</sub><br>- 4.25)<br>/ 0.264 | μs    |

| I <sub>sr</sub>                                             | Bus output current slew rate                             | $6V < V_{BATT} < 16V$ ; $R_S = 56.2$ kΩ $R_L = 100\Omega$ ; measured at 30% and 70% of waveform, DC offset 0 to $-2V$                                                                                              | 0.90                                 |      | 2.4                                      | mA/μs |

| V <sub>dB_limit</sub>                                       | Bus emissions voltage output                             | $\begin{array}{l} 0~\text{V} < \text{DC\_offset} < 1~\text{V}, \\ 9~\text{V} < \text{V}_{\text{BATT}} < 24~\text{V}, \\ R_{\text{L}} = 500~\Omega, ~C_{\text{L}} = 6~\text{nF} \end{array}$                        |                                      |      | -50                                      | dBV   |

| V <sub>dB_limit-1</sub>                                     | Bus emissions voltage output, negative bus offset        | $\begin{array}{l} -1 \text{ V} < \text{DC\_offset} < 0 \text{ V}, \\ 9 \text{ V} < \text{V}_{\text{BATT}} < 24 \text{ V}, \\ \text{R}_{\text{L}} = 500 \ \Omega, \ \text{C}_{\text{L}} = 6 \text{ nF} \end{array}$ |                                      |      | -50                                      | dBV   |

| N <sub>R</sub>                                              | Bus noise rejection from battery                         | 30 Hz < f < 250kHz                                                                                                                                                                                                 | 20                                   |      |                                          | dB    |

| N <sub>I</sub>                                              | Bus noise isolation from battery                         | 250 kHz < f < 200 MHz                                                                                                                                                                                              | 17                                   |      |                                          | dB    |

## SAE/J1850/VPW transceiver

AU5780A

| SYMBOL                                      | PARAMETER                                                      | CONDITIONS                                                                                                          | MIN. | TYP. | MAX. | UNIT |

|---------------------------------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Pin BUS_IN                                  |                                                                |                                                                                                                     |      |      |      |      |

| C <sub>BIN</sub>                            | Bus Input capacitance                                          |                                                                                                                     | 10   |      | 20   | pF   |

| T <sub>DRXON</sub> ;<br>t <sub>DRXOFF</sub> | Bus line to RX propagation delay, normal and 4x modes          | Measured at $V_{BUSIN\_HIGH}$ or $V_{BUSIN\_LOW}$ to RX; 6 < $V_{BATT}$ < 24 V; of $R_{LOAD}$ = 10 k $\Omega$ to 5V | 0.4  |      | 1.7  | μs   |

| T <sub>DRX_∆</sub>                          | Bus line to RX propagation delay mismatch, normal and 4x modes | t <sub>DRXOFF</sub> -t <sub>DRXON</sub>                                                                             | -1.3 |      | +1.3 | μs   |

| Pin BATT                                    |                                                                |                                                                                                                     |      |      |      |      |

| t <sub>low_power</sub>                      | time-out to low power state                                    | TX low                                                                                                              | 1    |      | 4    | ms   |

<sup>NOTES;

1. TX < 0.9V for more than 4 ms</li>

2. For 6V < V<sub>BATT</sub> < 9V the bus output voltage is limited by the supply voltage. For 16V < V<sub>BATT</sub> < 24V (jump start) the load is limited by the package power dissipation ratings; the duration of this condition is recommended to be less than 90 seconds.</li>

3. Tested with a bus load of R<sub>LOAD</sub> = 400 Ω and C<sub>LOAD</sub> = 22,000 pF.</sup>

## SAE/J1850/VPW transceiver

AU5780A

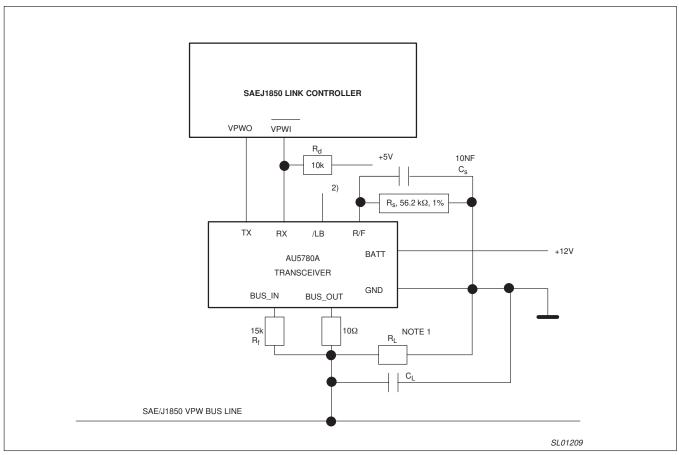

## **APPLICATION INFORMATION**

- 1. Value depends, e.g., on type of bus node. Example: primary node  $R_L$ =1.5k $\Omega$ , secondary node  $R_L$ =10.7k $\Omega$ . 2. For connection of /LB there are different options, e.g., connect to  $V_{CC}$  or to low-active reset or to a port pin. 3. The value of  $C_L$  is suggested to be in the range 330 pF <  $C_L$  < 470 pF.

## SAE/J1850/VPW transceiver

AU5780A

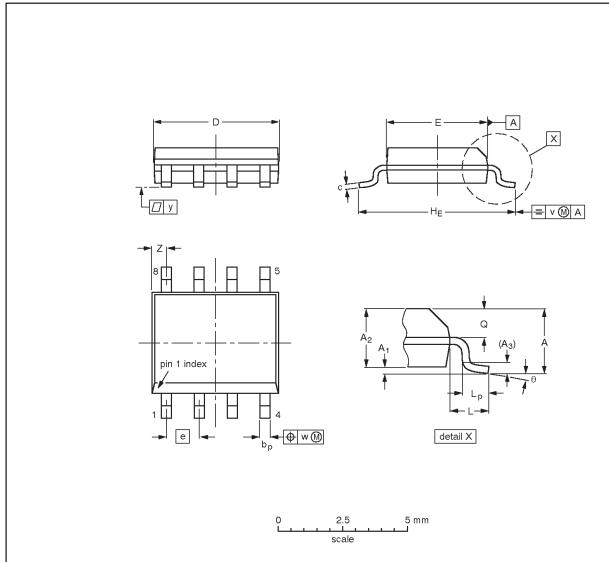

## SO8: plastic small outline package; 8 leads; body width 3.9 mm

SOT96-1

## DIMENSIONS (inch dimensions are derived from the original mm dimensions)

| UNIT   | A<br>max. | Α1             | A <sub>2</sub> | A <sub>3</sub> | bp           | С                | D <sup>(1)</sup> | E <sup>(2)</sup> | е     | HE             | L     | Lp             | Ø          | v    | w    | у     | Z <sup>(1)</sup> | θ  |

|--------|-----------|----------------|----------------|----------------|--------------|------------------|------------------|------------------|-------|----------------|-------|----------------|------------|------|------|-------|------------------|----|

| mm     | 1.75      | 0.25<br>0.10   | 1.45<br>1.25   | 0.25           | 0.49<br>0.36 | 0.25<br>0.19     | 5.0<br>4.8       | 4.0<br>3.8       | 1.27  | 6.2<br>5.8     | 1.05  | 1.0<br>0.4     | 0.7<br>0.6 | 0.25 | 0.25 | 0.1   | 0.7<br>0.3       | 8° |

| inches | 0.069     | 0.010<br>0.004 | 0.057<br>0.049 | 0.01           |              | 0.0100<br>0.0075 | 0.20<br>0.19     | 0.16<br>0.15     | 0.050 | 0.244<br>0.228 | 0.041 | 0.039<br>0.016 |            | 0.01 | 0.01 | 0.004 | 0.028<br>0.012   | 0° |

#### Notes

- 1. Plastic or metal protrusions of 0.15 mm maximum per side are not included.

- 2. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

| OUTLINE | REFERENCES |        |      |  | EUROPEAN   | ISSUE DATE                      |

|---------|------------|--------|------|--|------------|---------------------------------|

| VERSION | IEC        | JEDEC  | EIAJ |  | ISSUE DATE |                                 |

| SOT96-1 | 076E03     | MS-012 |      |  |            | <del>97-05-22</del><br>99-12-27 |

## SAE/J1850/VPW transceiver

AU5780A

#### **Data sheet status**

| Data sheet status <sup>[1]</sup> | Product<br>status <sup>[2]</sup> | Definitions                                                                                                                                                                                                                                                                                                            |

|----------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Objective data                   | Development                      | This data sheet contains data from the objective specification for product development.  Philips Semiconductors reserves the right to change the specification in any manner without notice.                                                                                                                           |

| Preliminary data                 | Qualification                    | This data sheet contains data from the preliminary specification. Supplementary data will be published at a later date. Philips Semiconductors reserves the right to change the specification without notice, in order to improve the design and supply the best possible product.                                     |

| Product data                     | Production                       | This data sheet contains data from the product specification. Philips Semiconductors reserves the right to make changes at any time in order to improve the design, manufacturing and supply. Changes will be communicated according to the Customer Product/Process Change Notification (CPCN) procedure SNW-SQ-650A. |

[1] Please consult the most recently issued datasheet before initiating or completing a design.

[2] The product status of the device(s) described in this data sheet may have changed since this data sheet was published. The latest information is available on the Internet at URL http://www.semiconductors.philips.com.

#### **Definitions**

**Short-form specification** — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

**Limiting values definition** — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

**Application information** — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

## **Disclaimers**

Life support — These products are not designed for use in life support appliances, devices or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

Right to make changes — Philips Semiconductors reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

Philips Semiconductors 811 East Arques Avenue P.O. Box 3409 Sunnyvale, California 94088–3409 Telephone 800-234-7381 © Copyright Philips Electronics North America Corporation 2001 All rights reserved. Printed in U.S.A.

Date of release: 06-01

Document order number: 9397 750 08501

Let's make things better.

Philips Semiconductors