Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 3-channel switching regulator controller BA9706K

The BA9706K is a 3-channel switching regulator controller that uses a pulse width modulation (PWM) system. Channels 1 and 2 are designed for driving PNP transistors, and channel 3 is designed for driving NPN transistors.

#### Applications

DC-DC converters in camcoders, notebook computers, and word processors

#### Features

- Reference voltage precision is ±1%; output stages are based on the push-pull method (resembling the totem-pole method), and ON/OFF currents can be set independently.

- Timer latch circuit protects the IC against short-circuiting.

- Pins allow ON/OFF control of channel 3 only, or all channels at once.

- 4) Undervoltage lockout (UVLO) circuit is built in.

- 5) Dead timer controller is included in channels 1 and 3 to allow various applications.

#### ●Absolute maximum ratings (Ta=25℃)

| Parameter             | Symbol | Limits         | Unit |  |

|-----------------------|--------|----------------|------|--|

| Power supply voltage  | Vcc    | 20             | ٧    |  |

| Power dissipation     | Pd     | 400*           | mW   |  |

| Operating temperature | Topr   | <b>-25~75</b>  | Ĉ    |  |

| Storage temperature   | Tstg   | <b>−55~125</b> | °C   |  |

<sup>\*</sup> Reduce power by 4 mW for each degree above 25℃.

#### Recommended operating conditions

| Parameter                      | Symbol | Limits   | Unit |

|--------------------------------|--------|----------|------|

| Operating power supply voltage | Vcc    | 3.6~18*1 | v    |

<sup>\*1</sup> Should not exceed the Pd-value.

7828999 0018479 721 📟

#### Pin descriptions

| Pin No. | Pin name         | Function                                                                                                                                                                                                               |

|---------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | IN2+             | Channel 2 error amplifier non-inverted input pin                                                                                                                                                                       |

| 2       | IN2-             | Channel 2 error amplifier inverted input pin                                                                                                                                                                           |

| 3       | FB2              | Channel 2 error amplifier output pin; gain setting and phase compensation are controlled by connecting a resistor and capacitor between this pin and the IN2 pin                                                       |

| 4       | OY2              | Channel 2 output transistor off current setting pin; off current of the output transistor is set by connecting a capacitor                                                                                             |

| 5       | OX2              | between the OX2 and OY2 pins                                                                                                                                                                                           |

| 6       | OY1              | Channel 1 output transistor off current setting pin; off current of the output transistor is set by connecting a capacitor                                                                                             |

| 7       | OX1              | between the OX1 and OY1 pins                                                                                                                                                                                           |

| 8       | VE2              | Channel 2 output current setting pin; output current of the OUT2 pin is set by connecting a resistor between this pin and GND                                                                                          |

| 9       | OUT2             | Channel 2 output pin                                                                                                                                                                                                   |

| 10      | DTC1             | Channel 1 rest period setting pin;<br>the rest period of channel 1 is set by dividing the VREF pin voltage<br>with external resistors; a soft start is possible by connecting a capacitor<br>between this pin and VREF |

| 11      | OUT1             | Channel 1 output pin                                                                                                                                                                                                   |

| 12      | VE1              | Channel 1 output current setting pin;<br>output current of the OUT1 pin is set by connecting a resistor<br>between this pin and GND                                                                                    |

| 13      | GND              | Ground pin (0 V)                                                                                                                                                                                                       |

| 14      | VCC1, 2, 3       | Output drive power supply pin                                                                                                                                                                                          |

| 15      | OUT3             | Channel 3 output pin                                                                                                                                                                                                   |

| 16      | VE3              | Channel 3 output current setting pin; output current of OUT3 is set by connecting a resistor between this pin and GND                                                                                                  |

| 17      | ОХЗ              | Channel 3 output transistor off current setting pin; off current of the output                                                                                                                                         |

| 18      | ОҮЗ              | transistor is set by connecting a capacitor between the OX3 and OY3 pins                                                                                                                                               |

| 19      | DTC3             | Channel 3 rest period setting pin; the rest period of channel 3 is set by dividing the VREF pin voltage with external resistors; a soft start is possible by connecting a capacitor between this pin and VREF          |

| 20      | FB3              | Channel 3 error amplifier output pin; g<br>ain setting and phase compensation are controlled by connecting a<br>resistor and capacitor between this pin and the IN3 pin                                                |

| 21      | IN3-             | Channel 3 error amplifier inverted input pin                                                                                                                                                                           |

| 22      | IN3 <sup>+</sup> | Channel 3 error amplifier non-inverted input pin                                                                                                                                                                       |

| 23      | CTL2             | Channel 3 ON/OFF pin; channel 3 operates when the pin is HIGH level, and ceases operation at LOW level; this pin is valid when CTL1 is LOW level                                                                       |

| 24      | CTL1             | Standby mode selection pin; reference voltage and all channel operations stop at HIGH level, and all channels operate at LOW level                                                                                     |

| 25      | Vcc              | Power supply pin                                                                                                                                                                                                       |

| 26      | VREF             | Reference voltage output pin; 2.48 V (typical)                                                                                                                                                                         |

🖿 7828999 OO18481 38T 때

| Pin No. | Pin name | Function                                                                                                                                                                                                                      |

|---------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27      | СТ       | Pin for connecting a frequency setting capacitor in the triangular wave oscillation circuit; triangular wave oscillation frequency is set by connecting a capacitor between this pin and GND                                  |

| 28      | RT       | Pin for connecting a frequency setting resistor in the short-circuit oscillation circuit; triangular wave oscillation frequency is set by connecting a resistor between this pin and GND                                      |

| 29      | SCP      | Pin for connecting a time-constant setting capacitor in the short-circuit protection circuit; time constant for the timer-latched, short-circuit protection circuit is set by connecting a capacitor between this pin and GND |

| 30      | IN1+     | Channel 1 error amplifier non-inverted input pin                                                                                                                                                                              |

| 31      | IN1-     | Channel 1 error amplifier inverted input pin                                                                                                                                                                                  |

| 32      | FB1      | Channel 1 error amplifier output pin; gain setting and phase compensation are controlled by connecting a resistor and capacitor between this pin and the IN1¬pin                                                              |

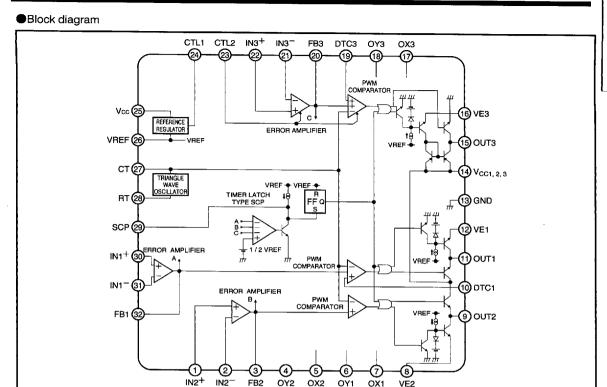

## ●Equivalent circuit

(OUT1)

(OUT2)

**7828999 0018482 216**

| Parameter                                  | Symbol            | Min.                                             | Тур.  | Max.  | Unit     | Conditions                              |

|--------------------------------------------|-------------------|--------------------------------------------------|-------|-------|----------|-----------------------------------------|

| [Total device]                             |                   |                                                  |       |       |          |                                         |

| Average current cumsumption                | lcc               | -                                                | 4.5   | 7.0   | mA       | When output is OFF                      |

| Standby current cumsumption                | Іѕтв              |                                                  | 6     | 11    | μA       |                                         |

| [Reference voltage section]                |                   |                                                  |       |       |          |                                         |

| Output voltage                             | VREF              | 2.435                                            | 2.460 | 2.485 | ν        | IREF=-0.7mA                             |

| Line regulation                            | DvL1              | T - 1                                            | -4    | -10   | m۷       | Vcc=3.6→18V                             |

| Load regulation 1                          | DvL01             | _                                                | 0.5   | 4     | m۷       | IREF=-0.1→-1mA                          |

| Load regulation 2                          | Dvloz             |                                                  | 5     | 10    | mV       | IREF=-0.1→-10mA                         |

| [Triangular wave oscillation section]      |                   | 1                                                |       |       |          |                                         |

| Oscillation frequency 1                    | fosc1             | -                                                | 514   | _     | kHz      | CT=330pF, RT=5.1kΩ                      |

| Frequency variation 1 (Vcc)                | DFVC1             | -1                                               | _     | 1     | %        | CT=330pF, RT=551kΩ,<br>Vcc=3.6→18V      |

| Oscillation waveform upper limit voltage 1 | Vosh1             | 1.89                                             | 1.99  | 2.09  | ٧        | CT=330pF, RT=5.1kΩ                      |

| Oscillation waveform lower limit voltage 1 | Vosl1             | 1.34                                             | 1.46  | 1.56  | v        | CT=330pF, RT=5.1kΩ                      |

| Oscillation frequency 2                    | fosc2             |                                                  | 790   | _     | kHz      | CT=180pF, RT=5.1kΩ                      |

| Frequency variation 2 (Vcc)                | DFVC2             | -1                                               | _     | 1     | %        | CT=180pF, RT=5.1kΩ,<br>Vcc=3.6→18V      |

| Oscillation waveform upper limit voltage 2 | Vosh2             | 1.91                                             | 2.01  | 2.11  | V        | CT=180pF, RT=5.1kΩ                      |

| Oscillation waveform lower limit voltage 2 | Vosl2             | 1.33                                             | 1.43  | 1.53  | V        | CT=180pF, RT=5.1kΩ                      |

| [Error amplifier section]                  |                   |                                                  |       |       |          |                                         |

| Input offset voltage                       | Vio               | _                                                | 2     | 6     | mV       |                                         |

| Input offset current                       | lio               | _                                                | 2     | 30    | nA       |                                         |

| Input bias current                         | IBIAS             |                                                  | 40    | 100   | nA       |                                         |

| Maximum input voltage                      | Vсм               | 1.6                                              | _     | _     | V        |                                         |

| Open loop gain                             | Av                | 60                                               | 78    | _     | dB       |                                         |

| Common mode rejection ratio                | CMRR              | 60                                               | 90    | _     | ďΒ       |                                         |

| Maximum output voltage +                   | Von+              | VREF-0.3                                         |       | _     | V        |                                         |

| Maximum output voltage —                   | Von-              | _                                                | 760   | 900   | mV       |                                         |

| Output sink current                        | lom+              | 2.0                                              | 2.4   | _     | mA       | VFB=1.6V                                |

| Output source current                      | юм-               | -60                                              | -88   | _     | μΑ       | VFB=1.6V                                |

| [PWM comparator section]                   | TOM:              |                                                  |       |       | μ.ν.     | 1.5 1.07                                |

| Input threshold voltage 1                  | Vто               | 1.89                                             | 1.99  | 2.09  | ٧        | Duty ratio = 0% *                       |

| Input threshold voltage 2                  | VT100             | 1.34                                             | 1.46  | 1.56  | v        | Duty ratio = 100% *                     |

| [Dead time control section]                | ¥1100             | 1.04                                             | 1.10  | 1.00  | ,        | Duty Idio = 100%                        |

| Input threshold voltage 1                  | VDO               | 1.89                                             | 1.99  | 2.09  | V        | Duty ratio = 0% (channel 3) *           |

| Input threshold voltage 2                  | V <sub>D100</sub> | 1.34                                             | 1.46  | 1.56  | v        | Duty ratio = 100% (channel 3) *         |

| Input bias current                         | los               |                                                  | 0.40  | 0.84  | μΑ       | VDTC=2.0V                               |

| Source current when Channel 3 is OFF       | IDOF3             | -100                                             | -420  | -     | μA       | VDTC=1.5V                               |

| Latch mode source current                  | IDLM              | -230                                             | -580  | _     | μA       | VDTC=1.5V                               |

| [Protection circuit section]               | IDUM              | 200                                              | 300   |       | <u> </u> | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |

| Input threshold voltage                    | <b>V</b> TI       | 1.72                                             | 1.86  | 2.00  | ν        |                                         |

| nput standby voltage                       | Vstr              | <del>                                     </del> | 23    | 80    | mV       |                                         |

| nput latch voltage                         | VLT               | _                                                | 21    | 80    | mV       |                                         |

| Input source current                       | Isce              | 1.1                                              | 2.2   | 3.1   | μA       |                                         |

| Comparator threshold voltage               | VTC               | 1.16                                             | 1.25  | 1.34  | V        |                                         |

| [Output section]                           | ¥10               |                                                  | 0     | 1.54  | •        |                                         |

| OUT1,2 sink current                        | lo <sub>12</sub>  | 10                                               | 20    | 30    | mA       | RE1=RE2=33 Ω Vcc1, 2=6V                 |

| OUT3 source current                        | los               | -6                                               | 12    | —18   | mA       | RE3=2.7kΩ Vcc3=6V                       |

278

ROHM

|   | g |

|---|---|

|   | ō |

|   | ä |

| • | 5 |

|   | Ž |

| C | ٣ |

| - | _ |

| - | Ĕ |

| 1 | Ē |

| 4 | 2 |

| - | ₹ |

| i | ń |

|   |   |

| Electrical characteristics | (Unless oth | erwise ne | oted, Ta | =25°C ar | nd Vcc=6.0V) | *CT=330P, RT=5.1kΩ |

|----------------------------|-------------|-----------|----------|----------|--------------|--------------------|

| Poromotor                  | O. mala at  |           |          | T        |              |                    |

| Parameter                 | Symbol           | Min. | Тур. | Max. | Unit | Conditions                |

|---------------------------|------------------|------|------|------|------|---------------------------|

| [Control section]         |                  |      |      |      |      | Serialitorio              |

| CTL1 ON condition         | V <sub>ON1</sub> | 3.2  |      | _    | V    |                           |

| CTL1 OFF condition        | Voff1            | _    |      | 2.8  | v    |                           |

| CTL1 pin current          | ICTL1            | 30   | 70   | 110  | μA   | VcTL1=5V                  |

| CTL2 ON condition         | Von2             | 2    |      | _    | V    | Operating mode            |

| CTL2 OFF condition        | Voff2            | _    |      | 1    | V    | Operating mode            |

| CTL2 pin current          | ICTL2            | 30   | 70   | 110  | μΑ   | Operating mode, VcTL2=5V  |

| [U.V.L.O circuit section] |                  |      |      |      | ,    | operating meast, voite ev |

| Threshold voltage (VREF)  | Vutr             | 1.85 | 2.0  | 2.15 | v    |                           |

| Threshold voltage (Vcc)   | Vuтc             | 2.6  | 2.8  | 3.0  | v    |                           |

# ●Guaranteed electrical characteristics (Unless otherwise noted, Ta=25°C and Vcc=6.0V)

| Parameter              | Symbol | Min. | Тур. | Max. | Unit | Conditions |

|------------------------|--------|------|------|------|------|------------|

| OUT1, 2 source current | lo12   | _    | -50  |      | mA   | Co=1000pF  |

| OUT 3 sink current     | Іоз    | _    | 50   | _    | mA   | Co=1000pF  |

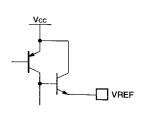

#### Circuit operation

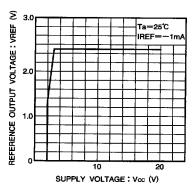

1) Voltage regulator (reference power supply section) Using the power supply voltage fed from  $V_{\rm CC}$  (pin 25), the voltage regulator provides a reference voltage stabilized at 2.5V as the IC internal circuit operating voltage. This voltage is also output from VREF (pin 26). By setting CTL1 (pin 24) to HIGH, the VREF output can be turned OFF and the whole IC can be put in a standby state.

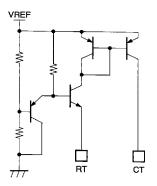

VREF pin I/O equivalent circuit

### 2) Triangular wave oscillator

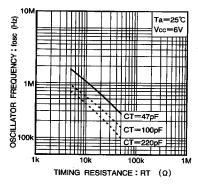

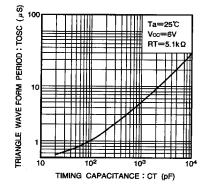

This circuit emits triangular waves to the PWM comparator. A triangular wave is generated by charging and discharging the timing capacitor connected to CT (pin 27), at a set current value determined by the RT (pin 28) resistor.

Standard ranges for CT- and RT-values

RT:  $5.1k\Omega \sim 100k\Omega$ CT:  $100pF \sim 0.22 \mu F$

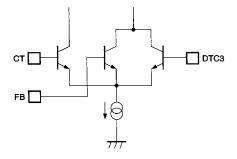

Triangle oscillator I/O equivalent circuit

**7**828999 0018484 099 **1**

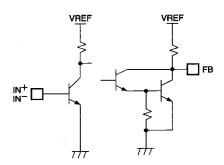

#### 3) Error amplifier

Output voltage is detected by returning the final output stage (load side) of the switching regulator to one input of the amplifier, and providing the reference voltage (VREF) divided by resistors to the other input.

You can set the loop gain arbitrarily by connecting a feedback resistor between the FB and IN<sup>-</sup> pins. We normally recommend using an AC error amplifier feed-

Error AMP I/O equivalent circuit

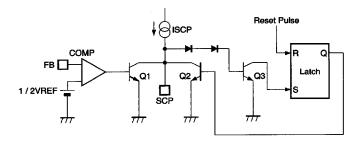

4) Timer-latched, short-circuit protection circuit This circuit prevents the occurrence of excess load in the final output stage of the switching regulator. Q1 turns OFF when FB is below 1/2VREF (1.25V), and the charging of the external capacitor connected to SCP (pin 29) starts with a constant current of Iscp =  $2.2 \,\mu$ A. This state continues until the voltage increases to the level at which Q3 turns ON ( $V_{LT}=1.8V$ ) to set the latch. As a result, the output stage turns OFF and DTC3 (pin 19) switches to HIGH. Furthermore, the capacitor dis-

back system consisting of a capacitor and resistor.

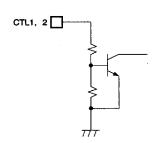

Note that the channel-3 error amplifier can be turned OFF separately by setting CLT2 (pin 23) to LOW; the channel-3 error amplifier turns OFF as a result. Because DTC3 (pin 19) is reset to HIGH at the same time, the soft start mode is reactivated (see also the "PWM comparator" section).

Note: that CTL1 and CTL2 have opposite logic characteristics.

CTL1, 2 I/O equivalent circuit

charges when Q2 turns ON.

This protection state can be reset, once the CLT1 or Voc pin is turned OFF. The timer can be set arbitrarily by changing the capacitance of the capacitor connected to the SCP pin, so that erroneous operations resulting from power rising or transitional load variation can be avoided.

Time setting of timer latch

$T = V_{LT}C/(S)$

Protector equivalent circuit

**■** 7828999 0018485 T25 |

280

ROHM

#### 5) Pulse width modulation comparator

The FB, DTC1 (channel 1), and DTC3 (channel 3) pins are for inverted input, and the CT pin is for non-inverted input. The output transistor (OUT pin) turns on when the triangular wave voltage (CT pin) is higher than both the error voltage (FB pin) and the dead-time control voltage (DTC3 pin). Therefore, the rest period can be adjusted by setting the dead time control voltage between the lower and upper limits (Vosl and Vosh) of oscillation waveform voltage, by using the reference voltage (VREF) divided by resistors. Also, a soft start when turning on the power is possible by connecting a capacitor between the reference voltage pin and each of the DTC1 and DTC3 pins. In step-up and fly-back applications, the dead time control voltage is generally set to a value that results in a duty ratio of about 50%.

PWM comparator I/O equivalent circuit

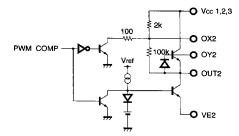

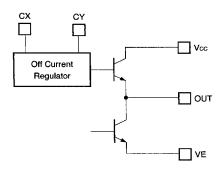

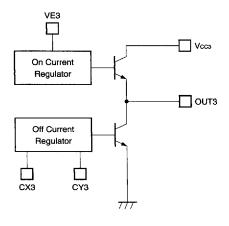

#### 7) Channel 3 output stage

Though the totem-pole output is employed, a fly-back/step-up output application can be compactly configured. On current is set as a constant and off current is set by a time constant, so that direct operation of NPN transistors is possible. Each output current is set by a resistor connected to VE3 (pin 16) and a capacitor connected between CX3 (pin 17) and CY3 (pin 18).

On current is nearly equal to 30/R (A) Off current is nearly proportional to C

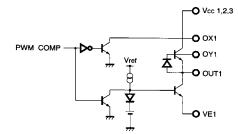

#### 6) Channels 1 and 2 output stages

Though the totem-pole output is employed, a step-down output application can be compactly configured. On current is set as a constant and Off current is set by a time constant, so that direct operation of PNP transistors is possible. Each output current is set by a resistor connected to the VE pin and a capacitor connected between the CX and CY pins.

On current is nearly equal to 0.7/R (A) Off current is nearly proportional to C

Output stage CH1, 2 equivalent circuit

**-** 7828999 0018486 961 **-**

- Precautions for use

- Make sure to use a voltage less than the maximum rating. An excessive voltage input can cause damage to the IC.

- 2) The error amplifier output (FB pin) of any unused channel is set to HIGH, by connecting the IN<sup>+</sup> and IN<sup>-</sup> input pins to VREF and GND, respectively.

- Make sure that the sum of the consumed power at each output plus the power dissipated due to the bias current does not exceed the total power dissipation of the IC.

- 4) Caution is required regarding electromagnetic interference in the switching regulator, because the control transistor functions as a switch. Practically, there will be no problem if proper caution is taken in grounding, wiring, and shielding.

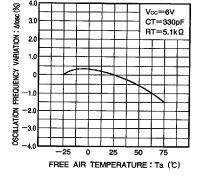

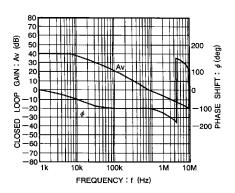

#### Electrical characteristic curves

Fig.1 Reference voltage vs. power supply voltage

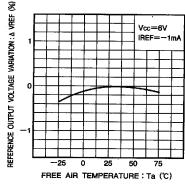

Fig.2 Reference voltage variation vs. ambient temperature

Fig.3 Triangle oscillation frequency vs. timing resistance

Fig.4 Triangle waveform period vs. timing capacitance

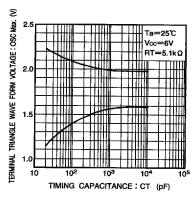

Fig.5 Triangle wave maximum amplified voltage vs. timing capacitance

Fig.6 Triangle oscillation frequency variation vs. timing capacitance

7828999 0018487 8T8

282

ROHM

Measurement circuit

Fig.7 Error amplifier, gain, phase vs. frequency

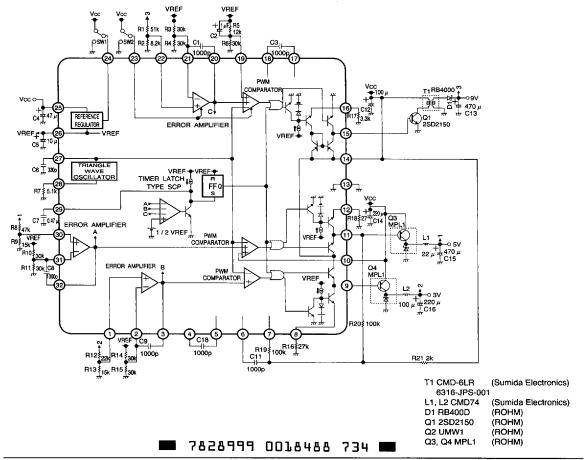

#### Application example

ROHM

283

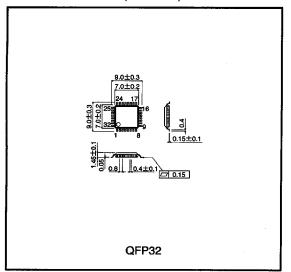

External dimensions (Units: mm)

**■** 7828999 0018489 670 **■**