# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

### Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## **2ch Half-Bridge Gate Driver**

### BD16952EFV-M

#### **General Description**

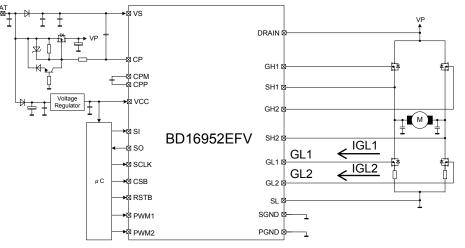

The BD16952EFV is an AEC-Q100 automotive qualified 2-channel Half-Bridge Gate Driver, controlled by an external MCU through a 16-bit Serial Peripheral Interface (SPI). Independent control of low-side and high-side N-MOSFETS allows for several MCU controlled modes. A programmable drive current is available to adjust slew-rates, in order to meet EMI and power dissipation requirements. Diagnostics can be read and reset by an external MCU.

#### Features

- AEC-Q100 Qualified<sup>(Note1)</sup>

- 2ch Half-Bridge Gate Drivers

- 4 external MOSFETs are Controlled Independently

- Half-Bridge Control Modes are Selected by SPI

- Slew Rates are Controlled with Constant Source /Sink Current.

- 500 kHz Oscillation for Charge Pump.

- 16bit SPI (Note1) Grade1

#### Applications

Power window Lifter, Sun Roof Module, Wiper, Seat Belt Tensioner, Seat Positioning etc.

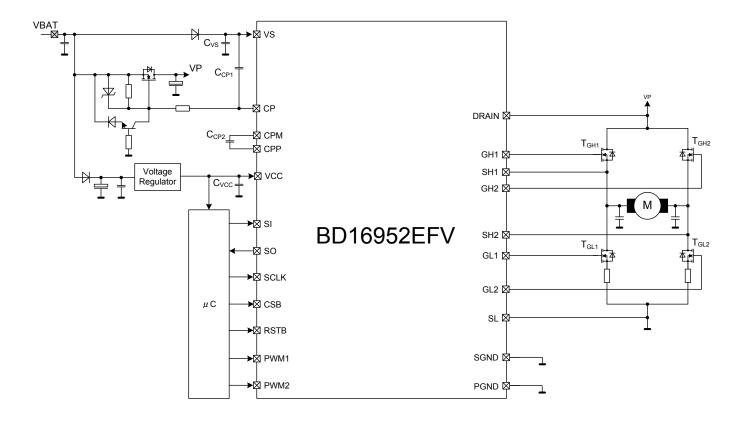

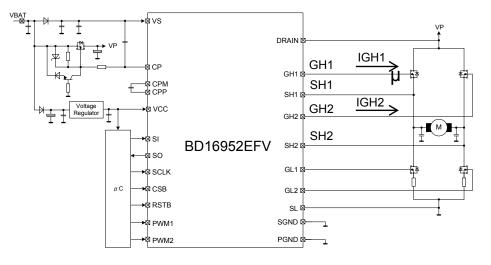

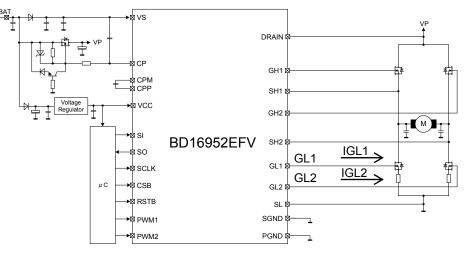

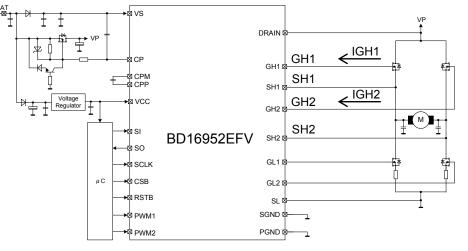

#### **Typical Application Circuit**

#### Key Specifications

| Input Voltage VS:                                           | 5.5V to 40V                  |

|-------------------------------------------------------------|------------------------------|

| Input Voltage VCC:                                          | 3.0V to 5.5V                 |

| <ul> <li>Gate Drive Voltage<br/>for Half-Bridge:</li> </ul> | 11V(Typ)                     |

| VS Quiescent Supply Current:                                | 0µА(Тур)                     |

| VCC Quiescent Supply Current:                               | 2µА(Тур)                     |

| Gate Driver Current                                         | 1mA to 31mA<br>with 1mA step |

| Cross Current Protection Time                               | 0.25µs to 92µs               |

SPI clock 7MHz (Max)

#### Package

HTSSOP-B24

W (Typ) x D (Typ) x H (Max) 7.8mm × 7.6mm × 1.00mm

OProduct structure: Silicon monolithic integrated circuit OThis product has no designed protection against radioactive rays.

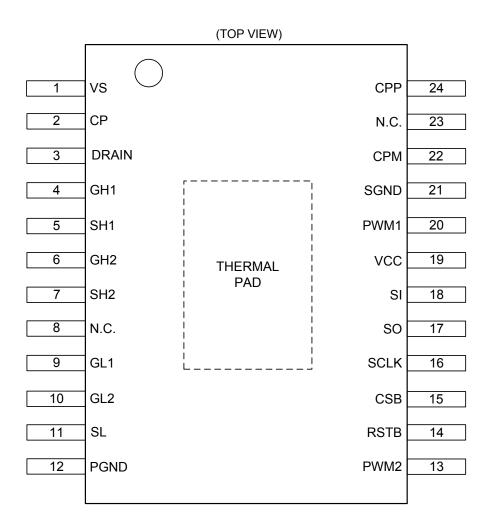

#### Pin Configuration

#### **Pin Description**

| Pin No. | Pin Name         | Function                                                                                                                                                                                                                                        |

|---------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | VS               | Power supply terminal used for charge pump and low side driver.<br>A capacitor ( $C_{VS}$ =1.0µF (Typ)) is recommended to be located as close as possible to this pin and PGND.                                                                 |

| 2       | CP               | Charge pump output. Connect $C_{CP1}=0.1\mu F$ to VS.                                                                                                                                                                                           |

| 3       | DRAIN            | High side monitor input from external MOSFET drain for over current and under voltage protection.                                                                                                                                               |

| 4       | GH1              | Gate driver output to external MOSFET high-side switch in half-bridge. Connect to Gate terminal of high-side external MOSFET.                                                                                                                   |

| 5       | SH1              | Source/Drain of half-bridge.<br>Connect to Source / Drain terminal of external MOSFET high/low-side.                                                                                                                                            |

| 6       | GH2              | Gate driver output to external MOSFET high-side switch in half-bridge. Connect to Gate terminal of high-side external MOSFET.                                                                                                                   |

| 7       | SH2              | Source/Drain of half-bridge.<br>Connect to Source / Drain terminal of external MOSFET high/low-side.                                                                                                                                            |

| 8       | N.C.             | Pin not connected internally. <sup>(Note1)</sup>                                                                                                                                                                                                |

| 9       | GL1              | Gate driver output to external MOSFET low-side switch in half-bridge.<br>Connect to Gate terminal of low-side external MOSFET.                                                                                                                  |

| 10      | GL2              | Gate driver output to external MOSFET low-side switch in half-bridge.<br>Connect to Gate terminal of low-side external MOSFET.                                                                                                                  |

| 11      | SL               | Low-side monitor at external MOSFET Source for over current protection                                                                                                                                                                          |

| 12      | PGND             | Power Ground Connector.<br>Connected to Charge pump, High side driver and Low side driver.                                                                                                                                                      |

| 13      | PWM2             | PWM2 input for Half-bridge (GH2 and GL2) control. This input has a pull-down resister.                                                                                                                                                          |

| 14      | RSTB             | Reset input. The Reset input has a pull-down resistor. RSTB=Low will put the BD16952EFV into Reset condition from any state.                                                                                                                    |

| 15      | CSB              | Chip Select Bar: this input is low active and requires CMOS logic levels.<br>The serial data transfer between BD16952EFV and MCU is enabled by pulling the input CSB to low-level. This input has a pull-up resister.                           |

| 16      | SCLK             | Serial clock input: this input controls the internal shift register of the SPI and requires CMOS logic levels. This input has a pull-down resister.                                                                                             |

| 17      | SO               | Serial data out: SPI data sent to the MCU by the BD16952EFV. When CSB is High, the pin is in the high-impedance state.                                                                                                                          |

| 18      | SI               | Serial data in: the input requires CMOS logic levels and receives serial data from the MCU. The communication is organized in 16bit control words and the most significant bit (MSB) is transferred first. This input has a pull-down resister. |

| 19      | VCC              | Analog blocks and logic voltage supply 3.3V or 5V : for this input a $C_{VCC}$ =0.1µF (Typ) capacitor as close as possible to SGND is recommended.                                                                                              |

| 20      | PWM1             | PWM1 input for Half-bridge (GH1 and GL1) control. This input has a pull-down resister.                                                                                                                                                          |

| 21      | SGND             | Ground terminal Connect to THERMAL PAD for heat dissipation.<br>Connected to Logic and analog circuit.                                                                                                                                          |

| 22      | СРМ              | Charge pump pin for capacitor, negative side.<br>Connect $C_{CP2} = 0.1 \mu F$ (Typ) to CPP terminal.                                                                                                                                           |

| 23      | N.C.             | Pin not connected internally. <sup>(Note1)</sup>                                                                                                                                                                                                |

| 24      | CPP              | Charge pump pin for capacitor, positive side.<br>Connect $C_{CP2} = 0.1 \mu F$ (Typ) to CPM terminal.                                                                                                                                           |

| THER    | MAL PAD          | THERMAL PAD for heat dissipation. Connect to SGND terminal.                                                                                                                                                                                     |

| (Note1  | ) Please be sure | n floating at N.C. pin.                                                                                                                                                                                                                         |

(Note1) Please be sure to floating at N.C. pin.

Ensure that the direction and position are correct when mounting the IC on the PCB. Incorrect mounting may damage the IC. Avoid nearby pins being shorted to each other especially to ground, power supply or output pin. Inter-pin shorts could be due to many reasons such as metal particles, water droplets (in very humid environment) or unintentional solder bridge deposited in between pins during assembly.

#### Selection of Components Externally Connected

#### Input Capacitor Cvs

The input capacitor ( $C_{VS}$ ) lowers the power supply impedance and averages the input current. The  $C_{VS}$  value is selected according to the impedance of the power supply that is used. A ceramic capacitor with a small equivalent series resistance (ESR) should be used. Although the capacitance requirement varies according to the impedance of the power supply that is used as well as the load current value, it is generally in the range of  $1.0\mu$ F.

#### Input Capacitor Cvcc

The input capacitor ( $C_{VCC}$ ) lowers the power supply impedance and averages the input current. The  $C_{VCC}$  value is selected according to the impedance of the power supply that is used. A ceramic capacitor with a small equivalent series resistance (ESR) should be used. A capacitor value of  $0.1\mu$ F is recommended.

#### Charge Pump Capacitor C<sub>CP1</sub>

The Charge pump capacitor  $C_{CP1}$  is required for smoothing the ripple voltage. A capacitor value of  $0.1\mu$ F is recommended. Using a capacitor with a capacitance lower than  $0.1\mu$ F, results in a larger ripple voltage. Conversely, using a capacitor with a capacitance greater than  $0.1\mu$ F results in a larger rush current during start-up, but ripple voltage becomes lower.

#### Charge Pump Capacitor C<sub>CP2</sub>

The charge pump capacitor  $C_{CP2}$  is required for charging up the voltage. A capacitor value of  $0.1\mu$ F is recommended. Using a capacitor with a capacitance lower than  $0.1\mu$ F, results in a larger ripple voltage. Conversely, using a capacitor with a capacitance greater than  $0.1\mu$ F results in a larger rush current during start-up, but ripple voltage becomes lower.

#### **External N-ch MOSFET**

BD16952EFV is the gate driver for high side and low side N-channel MOSFETs. Select MOSFETs with the required current capacity to drive the motor and a Gate-Source breakdown voltage  $\geq$  12V.

#### **External Parts**

| Symbol                 | Part             |

|------------------------|------------------|

| C <sub>VS</sub>        | 1.0μF, -/+10%    |

| Cvcc                   | 0.1µF, -/+10%    |

| C <sub>CP1</sub>       | 0.1µF, -/+10%    |

| C <sub>CP2</sub>       | 0.1µF, -/+10%    |

| Tgh1, Tgh2, Tgl1, Tgl2 | N-Channel MOSFET |

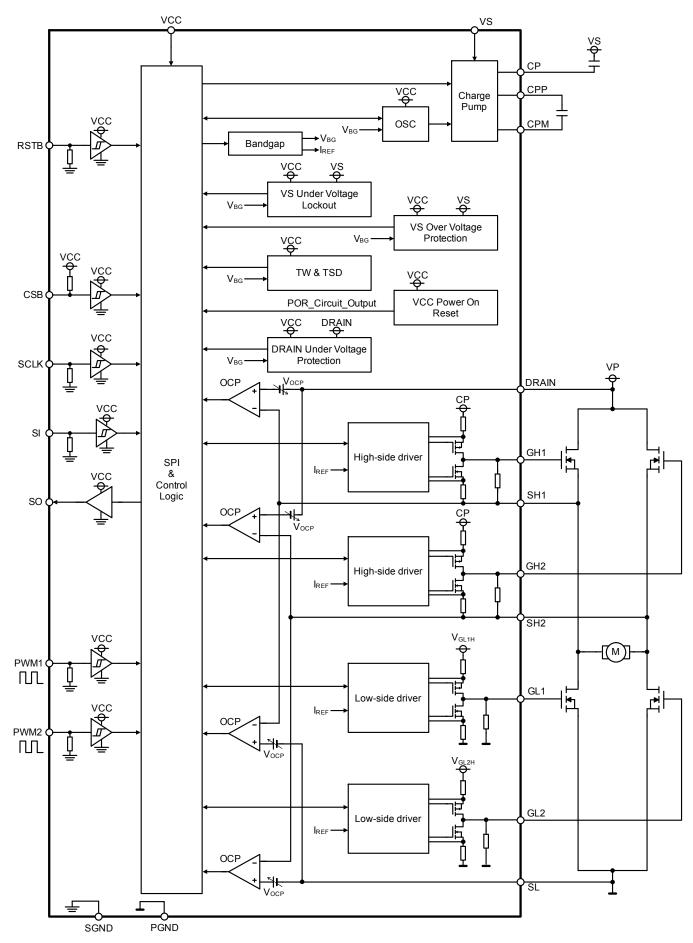

#### Block Diagram

#### Absolute Maximum Ratings (Ta=25°C)

| Parameter                                                         | Symbol             | Ratings                                                           | Unit |

|-------------------------------------------------------------------|--------------------|-------------------------------------------------------------------|------|

| VS Voltage                                                        | VS                 | -0.3 to 40                                                        | V    |

| VCC Voltage                                                       | VCC                | -0.3 to 7.0                                                       | V    |

| Digital I/O Voltage<br>( SI, SO, SCLK, CSB, RSTB,<br>PWM1, PWM2 ) | V <sub>IO</sub>    | -0.3 to 7.0                                                       | V    |

| CP Voltage                                                        | V <sub>CP</sub>    | VS to VS+20                                                       | V    |

| CPM Voltage                                                       | V <sub>CPM</sub>   | -0.3 to +12V+0.3V<br>(V <sub>CPM</sub> < VS)                      | V    |

| CPP Voltage                                                       | VCPP               | VS to VS+20                                                       | V    |

| Gate Voltage for High Side<br>(GH1,GH2)                           | Vgh1, Vgh2         | -0.3 to 60<br>(CP-VS < 12V)                                       | V    |

| Gate Voltage for Low Side<br>(GL1,GL2)                            | VGL1, VGL2         | -0.3 to +12V+0.3V<br>( V <sub>GL1</sub> , V <sub>GL2</sub> < VS ) | V    |

| Bridge output<br>(SH1,SH2)                                        | $V_{SH1}, V_{SH2}$ | -4 to 40                                                          | V    |

| Drain Voltage for High Side                                       | V <sub>DRAIN</sub> | -0.3 to 40                                                        | V    |

| Source Voltage for Low Side                                       | V <sub>SL</sub>    | -0.3 to 7.0                                                       | V    |

| Operating Temperature Range<br>( Ambient temperature range )      | Tamb               | -40 to 125                                                        | °C   |

| Storage Temperature Range                                         | T <sub>stg</sub>   | -55 to 150                                                        | °C   |

| Maximum Junction Temperature                                      | Tjmax              | 150                                                               | °C   |

| Human Body Model<br>( HBM Global Pin ) <sup>(Note1)</sup>         | Vesd, HBM          | ±4                                                                | kV   |

| Human Body Model<br>( HBM Local Pin ) <sup>(Note2)</sup>          | Vesd, HBM          | ±2                                                                | kV   |

| Charged Device Model<br>( CDM Corner Pin ) <sup>(Note3)</sup>     | Vesd,cdm           | ±750                                                              | V    |

| Charged Device Model<br>( CDM Other Pin ) <sup>(Note 4)</sup>     | Vesd,cdm           | ±500                                                              | V    |

(Note 1)Global pins are VS, SH1 and SH2 (A 'local' pin carries signal or power, which enters or leaves the application board ). These voltages are guaranteed by design.

(Note 2)Local pins are except VS, SH1 and SH2 (A 'local' pin carries a signal or power, which does not leave the application board ). These voltages are guaranteed by design.

(Note3)Corner pins are VS, PGND, PWM2 and CPP. These voltages are guaranteed by design.

(Note 4)Other pins are except VS, PGND, PWM2 and CPP. These voltages are guaranteed by design.

#### Thermal Resistance<sup>(Note 1)</sup>

| Parameter                                                      |             | Thermal Res            | - Unit                   |      |  |

|----------------------------------------------------------------|-------------|------------------------|--------------------------|------|--|

| Faianielei                                                     | Symbol      | 1s <sup>(Note 3)</sup> | 2s2p <sup>(Note 4)</sup> | Unit |  |

| HTSSOP-B24                                                     |             |                        |                          |      |  |

| Junction to Ambient                                            | θја         | 143.8                  | 26.4                     | °C/W |  |

| Junction to Top Characterization Parameter <sup>(Note 2)</sup> | $\Psi_{JT}$ | 7                      | 2                        | °C/W |  |

(Note 1)Based on JESD51-2A(Still-Air) (Note 2)The thermal characterization parameter to report the difference between junction temperature and the temperature at the top center of the outside surface of the component package.

#### (Note 3)Using a PCB board based on JESD51-3.

| Layer Number of<br>Measurement Board | Material  | Board Size                 |

|--------------------------------------|-----------|----------------------------|

| Single                               | FR-4      | 114.3mm x 76.2mm x 1.57mmt |

| Тор                                  |           |                            |

| Copper Pattern                       | Thickness |                            |

| Footprints and Traces                | 70µm      |                            |

|                                      |           |                            |

(Note 4)Using a PCB board based on JESD51-5, 7.

| Layer Number of       | Material  | Board Size               |          | Thermal Vi      | mal Via <sup>(NOTE 5)</sup> |  |  |

|-----------------------|-----------|--------------------------|----------|-----------------|-----------------------------|--|--|

| Measurement Board     | watenai   | Pitch                    |          | Diameter        |                             |  |  |

| 4 Layers              | FR-4      | 114.3mm x 76.2mm x       | x 1.6mmt | 1.20mm          | Ф0.30mm                     |  |  |

| Тор                   | Тор       |                          | ers      | Botto           | m                           |  |  |

| Copper Pattern        | Thickness | Copper Pattern Thickness |          | Copper Pattern  | Thickness                   |  |  |

| Footprints and Traces | 70µm      | 74.2mm x 74.2mm          | 35µm     | 74.2mm x 74.2mi | m 70µm                      |  |  |

(Note 5)This thermal via connects with the copper pattern of all layers.

#### **Recommended Operating Conditions**

| Parameter                  | Symbol                             | Min  | Тур  | Max | Unit |

|----------------------------|------------------------------------|------|------|-----|------|

| Supply Voltage1            | VS                                 | 5.5  | 13.5 | 40  | V    |

| Supply Voltage2            | VCC                                | 3.0  | 5    | 5.5 | V    |

| Digital Input Voltage      | SI, SCLK, CSB, RSTB,<br>PWM1, PWM2 | -0.3 | -    | VCC | V    |

| Junction Temperature Range | Tj                                 | -40  | -    | 150 | °C   |

#### **Electrical Characteristics**

(Unless otherwise specified, -40 °C ≤ Tj ≤ +150 °C, VS= 13.5 V, VCC= 5 V, The typical value is defined at Tj = 25 °C)

| Parameter                                                       | Limit                 |       |           |        | 1.1  |                                                              |

|-----------------------------------------------------------------|-----------------------|-------|-----------|--------|------|--------------------------------------------------------------|

|                                                                 | Symbol                | Min   | Тур       | Max    | Unit | Condition                                                    |

|                                                                 |                       | Consu | mption Cu | irrent |      |                                                              |

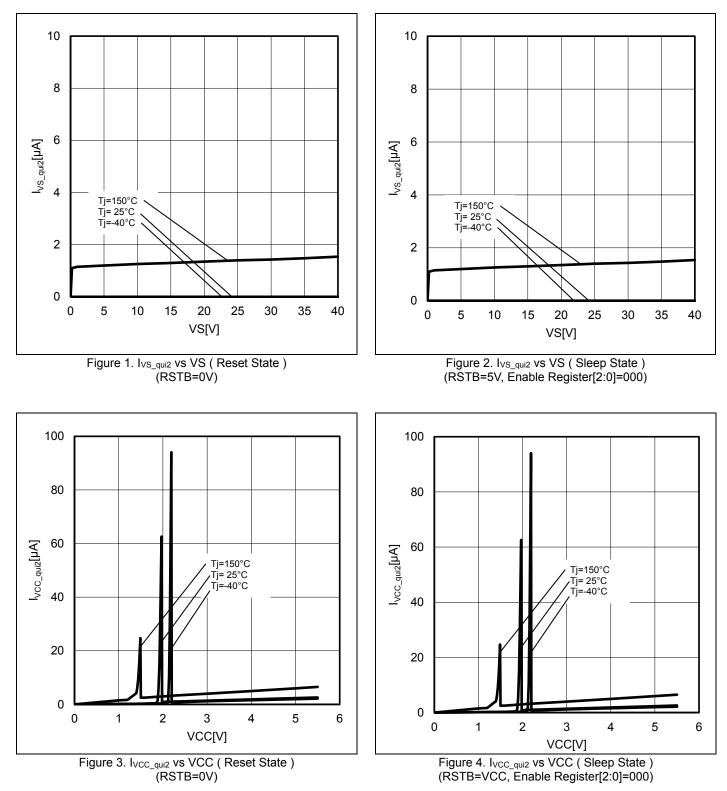

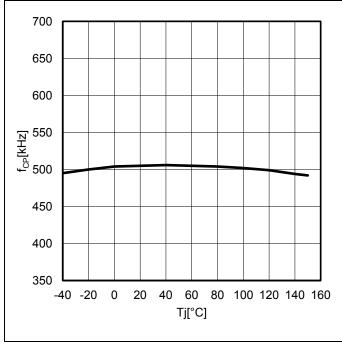

| VS Quiescent Supply Current1<br>(Reset / Sleep State) (Note 1)  | $I_{VS\_qui1}$        | -     | 0         | 10     | μA   | 0V ≤ VS ≤ V <sub>s_OVP1</sub><br>-40 °C ≤ Tj ≤ +105 °C       |

| VS Quiescent Supply Current2<br>(Reset / Sleep State) (Note 1)  | Ivs_qui2              | -     | 0         | 50     | μA   | 0V ≤ VS ≤ V <sub>s_OVP1</sub><br>-40 °C ≤ Tj ≤ +150 °C       |

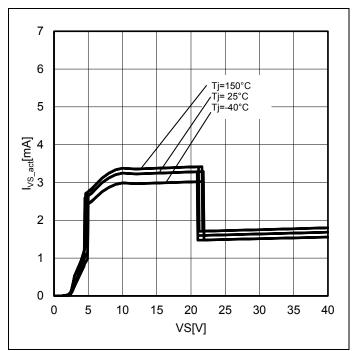

| VS Active Current<br>(Normal State) (Note 1)                    | I <sub>VS_act</sub>   | -     | 3.2       | 6.4    | mA   | SH1=SH2=PGND<br>CUR_SOURCE[4:0]=00000<br>CUR_SINK[4:0]=00000 |

| VCC Quiescent Supply Current1<br>(Reset / Sleep State) (Note 1) | IVCC qui1             | -     | 2         | 10     | μA   | V <sub>CC_POR1</sub> ≤ VCC ≤ 5.5V<br>-40 °C ≤ Tj ≤ +105 °C   |

| VCC Quiescent Supply Current2<br>(Reset / Sleep state) (Note 1) | I <sub>VCC qui2</sub> | -     | 2         | 100    | μA   | V <sub>CC_POR1</sub> ≤ VCC ≤ 5.5V<br>-40 °C ≤ Tj ≤ +150 °C   |

| VCC Active Current<br>(Normal state) ( Note 1)                  | Ivcc_act              | -     | 1.2       | 2.4    | mA   | SH1=SH2=PGND<br>CUR_SOURCE[4:0]=00000<br>CUR_SINK[4:0]=00000 |

|                                                                                                            |                         | Input /      | Output Te    | rminal       |     |                                                                                       |

|------------------------------------------------------------------------------------------------------------|-------------------------|--------------|--------------|--------------|-----|---------------------------------------------------------------------------------------|

| Input High Voltage(PWM1, PWM2,<br>SI, SCLK, CSB, RSTB)                                                     | VIH                     | VCC x<br>0.7 | -            | -            | V   |                                                                                       |

| Input Low Voltage(PWM1, PWM2,<br>SI, SCLK, CSB, RSTB)                                                      | VIL                     | -            | -            | VCC x<br>0.3 | V   |                                                                                       |

| Hysteresis Width                                                                                           | V <sub>HYS</sub>        | -            | VCC x<br>0.1 | -            | V   |                                                                                       |

| Pull-Down Resistance (PWM1,<br>PWM2, SI, SCLK, RSTB)                                                       | Rin1                    | 40           | 100          | 160          | kΩ  |                                                                                       |

| Input Current (PWM1, PWM2, SI,<br>SCLK, RSTB)                                                              | IIL                     | -1           | 0            | -            | μΑ  | PWM1, PWM2, SI, SCLK,<br>RSTB=0V                                                      |

| Pull-Up Resistance at CSB                                                                                  | R <sub>In2</sub>        | 40           | 100          | 160          | kΩ  |                                                                                       |

| Input Current at CSB                                                                                       | Ін                      | -1           | 0            | -            | μA  | CSB=VCC                                                                               |

| Output Voltage High at SO                                                                                  | Vон                     | VCC x<br>0.8 | -            | VCC          | V   | ISO=-1mA ( into the pin )                                                             |

| Output Voltage Low at SO                                                                                   | V <sub>OL</sub>         | -            | -            | VCC x<br>0.2 | V   | ISO=1mA                                                                               |

| PWM Frequency Range                                                                                        | f <sub>РWM</sub>        | -            | -            | 25           | kHz |                                                                                       |

| SH1,SH2 Output Current<br>(Reset/Sleep state) (Note 1)                                                     | ISH1,2_LEAK             | -10          | 0            | -            | μΑ  | GH1-SH1,GH2-SH2=0V                                                                    |

| SH1, SH2 Outflow Current1<br>(Normal state) <sup>(Note 1)</sup>                                            | I <sub>SH1,2_out1</sub> | -280         | -155         | -70          | μA  | GH1=GH2=SH1=SH2=0<br>EN=CPEN=DRVEN=1<br>CUR_SOURCE[4:0]=00000<br>CUR_SINK[4:0]=00000  |

| SH1, SH2 Outflow Current2<br>(Normal state) <sup>(Note 1)</sup>                                            | I <sub>SH1,2_out2</sub> | -280         | -155         | -70          | μA  | GH1=GH2=SH1=SH2=VS<br>EN=CPEN=DRVEN=1<br>CUR_SOURCE[4:0]=00000<br>CUR_SINK[4:0]=00000 |

| GH1,GH2 Pull-Down Resistance<br>(Gate-Source Pull-Down Current)<br>(Reset/Sleep State) ( Note 1)           | $R_{GH1,2\_pulldown}$   | 6            | 15           | 24           | kΩ  |                                                                                       |

| SL Output Current<br>(Reset/Sleep State) <sup>(Note 1)</sup>                                               | Isl1,2_leak             | -10          | 0            | -            | μA  | GL1-SL,GL2-SL=0V                                                                      |

| GL1,GL2 Pull Down Resistance<br>(Gate-Source Pull-Down Current)<br>(Reset/Sleep State) <sup>(Note 1)</sup> |                         | 6            | 15           | 24           | kΩ  |                                                                                       |

(Note 1) Functional statement control is shown on the figure 13.

#### **Electrical Characteristics(continued)**

(Unless otherwise specified, -40 °C  $\leq$  Tj  $\leq$  +150 °C, VS= 13.5 V, VCC= 5 V, The typical value is defined at Tj = 25 °C)

| Parameter                                                          | Symbol               |                     | Limit              |                     | Unit | Condition                                                                           |  |  |  |

|--------------------------------------------------------------------|----------------------|---------------------|--------------------|---------------------|------|-------------------------------------------------------------------------------------|--|--|--|

| Parameter                                                          | Symbol               | Min                 | Тур                | Max                 | Unit | Condition                                                                           |  |  |  |

| Charge Pump                                                        |                      |                     |                    |                     |      |                                                                                     |  |  |  |

| Output Voltage1<br>(Normal State) ( Note 1)                        | V <sub>CP1</sub>     | V <sub>S</sub> +10  | V <sub>S</sub> +11 | V <sub>S</sub> +12  | V    | VS = 13.5V, I <sub>CP</sub> =0mA<br>CUR_SOURCE[4:0]=00000<br>CUR_SINK[4:0]=00000    |  |  |  |

| Output Voltage2<br>(Normal State) ( Note 1)                        | V <sub>CP2</sub>     | V <sub>S</sub> +5.0 | -                  | V <sub>S</sub> +6.0 | V    | VS = 6V, I <sub>CP</sub> =0mA<br>CUR_SOURCE[4:0]=00000<br>CUR_SINK[4:0]=00000       |  |  |  |

| Voltage Drop of Charge Pump1<br>(Normal State) <sup>(Note 1)</sup> | VCP_Drop1            | -                   | -                  | 1.0                 | V    | VS = 13.5V, I <sub>CP</sub> = -10mA<br>CUR_SOURCE[4:0]=00000<br>CUR_SINK[4:0]=00000 |  |  |  |

| Voltage Drop of Charge Pump2<br>(Normal State) <sup>(Note 1)</sup> | VCP_Drop2            | -                   | -                  | 0.5                 | V    | VS = 6V, I <sub>CP</sub> = -2mA<br>CUR_SOURCE[4:0]=00000<br>CUR_SINK[4:0]=00000     |  |  |  |

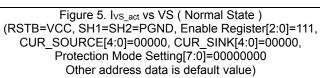

| Charge Pump Operating<br>Frequency<br>(Normal State) ( Note 1)     | f <sub>CP</sub>      | 400                 | 500                | 667                 | kHz  | Charge Pump operating frequency<br>is divided by Clock frequency                    |  |  |  |

| Clock Frequency<br>(Internal Oscillator)                           | f <sub>CLK</sub>     | 3.20                | 4.00               | 5.34                | MHz  |                                                                                     |  |  |  |

| CP Input Current<br>(Reset/Sleep State) ( Note 1)                  | I <sub>CP_LEAK</sub> | -                   | 0                  | 10                  | μA   | EN=0, V <sub>CP</sub> =25.5V, VS=13.5V                                              |  |  |  |

(Note 1) Functional statement control is shown on the figure 13.

#### **Electrical Characteristics(continued)**

(Unless otherwise specified, -40 °C ≤ Tj ≤ +150 °C, VS= 13.5 V, VCC= 5 V, The typical value is defined at Tj = 25 °C)

| Devementer                                                       | Currents el          | Limit      |            |                    | l lucit |                                                                                                                                                        |  |

|------------------------------------------------------------------|----------------------|------------|------------|--------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Parameter                                                        | Symbol               | Min        | Тур        | Max                | Unit    | Condition                                                                                                                                              |  |

|                                                                  | D                    | rivers for | External M | <b>IOSFETs</b>     |         |                                                                                                                                                        |  |

| Accuracy of<br>Gate Driver Current                               | ACCISR               | -25        | -          | +25                | %       | CUR_SOURCE[4:0]=<br>00001 to 11111 <sup>(Note 1)</sup><br>CUR_SINK[4:0]=<br>00001 to 11111 <sup>(Note 1)</sup><br>1mA to 31mA setting<br>with 1mA step |  |

| Pull Down Current (Note 2)<br>(Reset/Sleep State) (Note 3)       | Ipulldown            | 83         | 133        | 334                | μA      | GH1=SH1+2V, GH1=SH2+2V<br>GL1=2V, GL2=2V                                                                                                               |  |

| DNL of Gate Driver Current                                       | ACCDNLISR            | -          | -          | 1                  | LSB     |                                                                                                                                                        |  |

| GH1/GH2 Output High Voltage for High Side(Normal State) (Note 3) | V <sub>GHxH</sub>    | Vs+10      | Vs+11      | V <sub>S</sub> +12 | V       | VS = 13.5V, lcp=0mA                                                                                                                                    |  |

| GL1/GL2 Output High Voltage for Low Side(Normal State) ( Note 3) | $V_{GLxH}$           | 10         | 11         | 12                 | V       | VS = 13.5V                                                                                                                                             |  |

| Cross Current Protection Time                                    | tссрт                | -25        | -          | 25                 | %       | CCPT[5:0]=00000 to 111111<br>0.25µs to 92µs setting                                                                                                    |  |

| DNL of Cross Current Protection<br>Time                          | t <sub>dnlccpt</sub> | -          | -          | 1                  | LSB     |                                                                                                                                                        |  |

| Synchronization Delay Time(Note 4)                               | t <sub>syn</sub>     | 0.56       | -          | 1.25               | μs      |                                                                                                                                                        |  |

| Propagation Delay Time <sup>(Note 5)</sup>                       | t <sub>propa</sub>   | 100        | 250        | 400                | ns      | SH1=SH2=VS<br>CUR_SOURCE[4:0]=11111<br>CUR_SINK[4:0]=11111                                                                                             |  |

| Output on Resistance                                             | Rds_on_gate          | -          | 10         | 20                 | Ω       | Output on resistance<br>CUR_SOURCE[4:0]=11111                                                                                                          |  |

(Note 1) High side source current : GH1=SH1, GH2=SH2, Low side source current : GL1=PGND, GL2=PGND High side sink current : Isink(GH1=GH2=11V, SH1=SH2=PGND) - 15 kΩ pull down current(CPEN=0) Low side sink current : Isink(GL1=GL2=11V) - 15 kΩ pull down current(CPEN=0)

(Note 2) (External MOSFET's gate driver current) = (Accuracy of gate driver current) - (Pull down current)

e.g. condition : CUR\_SOURCE[4:0]=01010(10mA setting),GH1=SH1+2V,

(External MOSFET's gate driver current of GH1) = 10mA(Typ) - 133uA(Typ) = 9.867mA.

Maximum inflow current of pull down resistance is 2mA(12V/6kΩ).GH1/GH2/GL1/GL2 outputs do not rise high voltage in 1mA or 2mA setting.

(Note 3) Functional statement control is shown on the figure 13.

(Note 4) Synchronization delay time : Asynchronous internal delay between PWM signal and high-side or low side of logic signal. This delay time is guaranteed by design.

(Note 5) Propagation delay time : internal delay between high-side or low side of logic signal and GHx or GLx outputs. This delay time is guaranteed by design.

**Electrical Characteristics(continued)** (Unless otherwise specified, -40 °C  $\leq$  Tj  $\leq$  +150 °C, VS= 13.5 V, VCC= 5 V, The typical value is defined at Tj = 25 °C)

| Parameter                                               | Symbol              |      | Limit      |      | Unit | Condition                                                                                                       |

|---------------------------------------------------------|---------------------|------|------------|------|------|-----------------------------------------------------------------------------------------------------------------|

| T didificter                                            | Cymbol              | Min  | Тур        | Max  | Onic | Condition                                                                                                       |

|                                                         |                     |      | Protection |      |      |                                                                                                                 |

| UVLO Voltage Rising                                     | Vs_uvlo1            | 4.5  | 5.0        | 5.5  | V    | VS UVLO                                                                                                         |

| Under Voltage Hysteresis                                | $V_{S\_UV\_hys}$    | 300  | 500        | 700  | mV   |                                                                                                                 |

| OVP Voltage Rising                                      | $V_{S_{OVP1}}$      | 20   | 22         | 24   | V    | VS OVP                                                                                                          |

| Over Voltage Hysteresis                                 | $V_{S_OVP_hys}$     | 0.6  | 1          | 1.4  | V    |                                                                                                                 |

| Power On Reset Rising                                   | VCC_POR1            | 0.75 | 2.00       | 2.95 | V    | VCC POR                                                                                                         |

| Power On Reset Hysteresis                               | Vcc_por_hys         | 0.03 | 0.1        | 0.25 | V    |                                                                                                                 |

| Thermal Warning Trigger <sup>(Note 1)</sup>             | T <sub>TW_TR</sub>  | 125  | 137.5      | 150  | °C   |                                                                                                                 |

| Thermal Warning Release <sup>(Note 1)</sup>             | T <sub>TW_RL</sub>  | 105  | 117.5      | 130  | °C   |                                                                                                                 |

| Thermal Warning Hysteresis <sup>(Note1)</sup>           | T <sub>TWHYS</sub>  | 15   | 20         | 25   | °C   |                                                                                                                 |

| Thermal Shut Down<br>Trigger <sup>(Note 1)</sup>        | T <sub>tsd_tr</sub> | 150  | 175        | 200  | °C   |                                                                                                                 |

| Thermal Shut Down<br>Release <sup>(Note 1)</sup>        | T <sub>TSD_RL</sub> | 135  | 160        | 185  | °C   |                                                                                                                 |

| Thermal Shut Down<br>Hysteresis <sup>(Note 1)</sup>     | T <sub>TSDHYS</sub> | -    | 15         | -    | °C   |                                                                                                                 |

| DRAIN Quiescent Current<br>(Reset/Sleep State) (Note 1) | IDRAIN_qui          | -    | -          | 1    | μA   |                                                                                                                 |

| DRAIN Active Current<br>(Normal State)                  | IDRAIN_act          | -    | 120        | 180  | μA   |                                                                                                                 |

| DRAIN Under Voltage<br>Protection Falling               | VUVP                | 4.4  | 4.9        | 5.4  | V    |                                                                                                                 |

| OCP Detect Voltage<br>( Drain-SH and SH –SL )           | Vocp                | -15  | -          | +15  | %    | OCPHD[2:0]=000 to 111<br>OCPLD[2:0]=000 to 111<br>0.2V, 0.3V, 0.4V, 0.5V, 0.75V, 1.0V<br>1.25V and 1.5V setting |

| OCP Detect FILTER Time                                  | tocp_filter         | -25  | -          | +25  | %    | OCP_FILTER[5:0]=000000 to<br>111111<br>1µs and 63µs setting<br>with 1µs step                                    |

| POR Detect Blanking Time                                | tpor_blanking       | 0.8  | 2          | 3.8  | μs   |                                                                                                                 |

| UVLO Detect Blanking Time                               | tuvlo_blanking      | 48   | 64         | 80   | μs   |                                                                                                                 |

| OVP Detect Blanking Time                                | tovp_blanking       | 48   | 64         | 80   | μs   |                                                                                                                 |

(Note 1) This temperature is guaranteed by design.

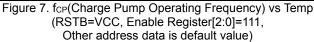

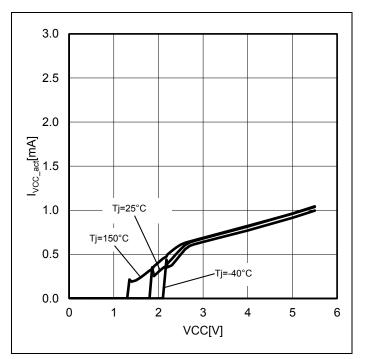

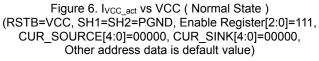

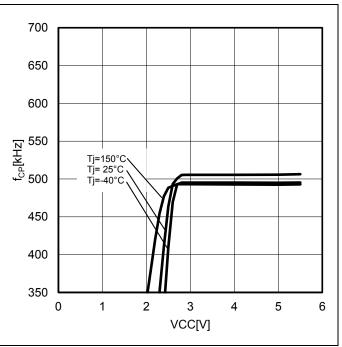

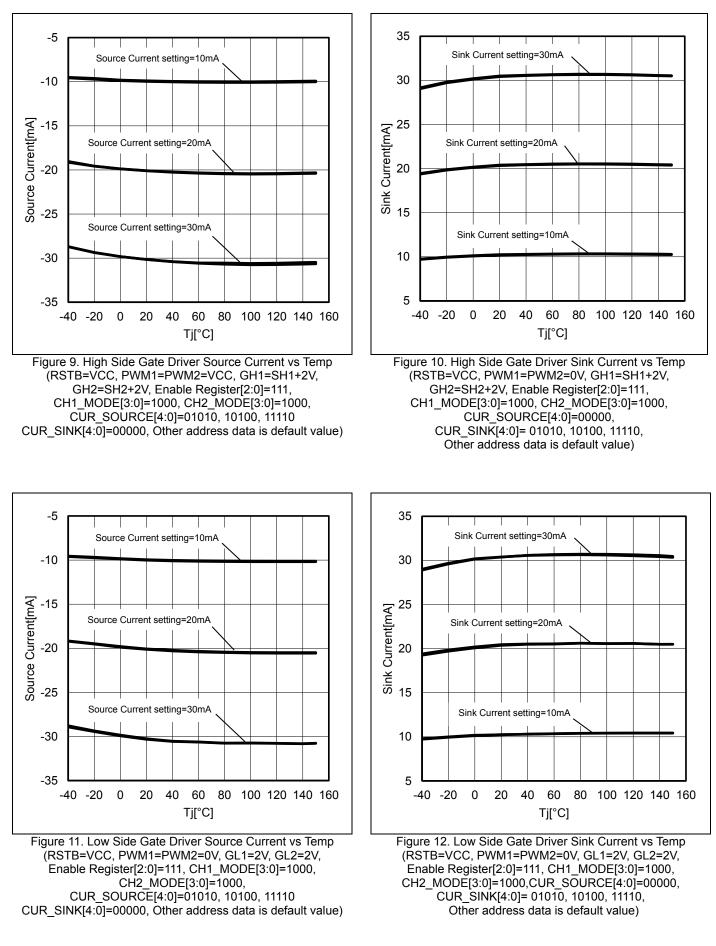

#### **Typical Performance Curves (Reference Data)**

(Unless otherwise specified, -40 °C ≤ Tj ≤ +150 °C, VS= 13.5 V, VCC= 5 V, The typical value is defined at Tj = 25 °C)

#### **Typical Performance Curves (Reference Data)**

(Unless otherwise specified, -40 °C ≤ Tj ≤ +150 °C, VS= 13.5 V, VCC= 5 V, The typical value is defined at Tj = 25 °C)

Figure 8. f<sub>CP</sub>(Charge Pump Operating Frequency) vs VCC (RSTB=VCC, Enable Register[2:0]=111, Other address data is default value)

#### Typical Performance Curves (Reference Data)

(Unless otherwise specified, -40 °C ≤ Tj ≤ +150 °C, VS= 13.5 V, VCC= 5 V, The typical value is defined at Tj = 25 °C)

#### Timing Chart

|                          |                   |                                       | CP (Note 13)                                                                |           |

|--------------------------|-------------------|---------------------------------------|-----------------------------------------------------------------------------|-----------|

|                          | 12V               |                                       |                                                                             |           |

|                          | 120               |                                       | Charge up time : 0.2ms (Max)<br>← C <sub>CP1</sub> =C <sub>CP2</sub> =0.1µF |           |

| VS                       | 0V                | (Nato 6)                              |                                                                             |           |

|                          | 5V (No            | (Note 6)<br>i<br>ote 5)               |                                                                             |           |

| (Note 1)<br>VCC UCC_POR1 | 0V Vcc_porc       |                                       |                                                                             | (Note 15) |

|                          | ote 2) 5V         |                                       | (Note 14)                                                                   |           |

| RSTB                     | ov                |                                       |                                                                             |           |

|                          |                   | (Note 7)<br>→ Filter time : 2µs       |                                                                             |           |

| Filter time : 2µs        | 5V                |                                       |                                                                             |           |

| POR_Circuit_Output       | 0V                |                                       |                                                                             | L~        |

| SPI Command (Note 16)    | (Note 3) (Note 4) | (Note 8) (Note 9)                     | (Note 11) (Note 12)                                                         |           |

| < <u> </u>               | NOP               | NOP   Clear   Status                  | CPEN DRVEN NOP                                                              | >         |

| NOP : Not Operating      |                   |                                       | DRVEN= '0'                                                                  |           |

| CSB                      |                   |                                       |                                                                             |           |

| POR Flag                 |                   | (Not                                  | e 10)                                                                       |           |

| POR='1'                  | POR= '0'          |                                       | POR= '0'                                                                    | POR='1'   |

| State                    |                   |                                       |                                                                             | /         |

| Reset                    | Sleep Normal      | Sleep                                 | Normal                                                                      | Reset     |

|                          |                   | Reset                                 |                                                                             | /         |

|                          | 3.2mA(Typ)        |                                       |                                                                             |           |

| I <sub>VS</sub>          | 0µА(Тур)          |                                       |                                                                             |           |

|                          | 1.2mA(Typ)        | · · · · · · · · · · · · · · · · · · · |                                                                             |           |

| lvcc                     | 2µА(Тур) ▼        |                                       |                                                                             |           |

|                          |                   |                                       |                                                                             |           |

|                          |                   |                                       |                                                                             |           |

| PWM1/PWM2                |                   |                                       |                                                                             |           |

|                          |                   |                                       |                                                                             |           |

| GH1                      |                   |                                       | PWM                                                                         |           |

|                          |                   |                                       |                                                                             |           |

|                          |                   |                                       | PWM                                                                         |           |

| GL1                      |                   |                                       |                                                                             |           |

|                          |                   |                                       |                                                                             |           |

| GH2                      |                   |                                       | PWM                                                                         |           |

|                          |                   |                                       |                                                                             |           |

|                          |                   |                                       | ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓                                       |           |

| GL2                      |                   |                                       |                                                                             |           |

- (Note 1) The Power-On-Reset circuit (POR) monitors the VCC voltage. At power-up, POR is released when VCC ≥ V<sub>CC\_POR1</sub> voltage. The POR circuit has a blanking time for 2µs (Typ) to reject noise. The POR Flag in status resister is set to '1' in reset and is kept after recovery reset.

- (Note 2) RSTB is set high by MCU. State is changed to Sleep state.

- (Note 3) MCU sends the EN='1' command. State is changed to Normal state.

EN='1' command can be sent after 1µs(min) to change RSTB from "Low" to "High".

Consequently, analog circuit becomes active (I<sub>VS\_act</sub>=3.2mA Typ and I<sub>VCC\_act</sub>=1.2mA Typ).

Transition time is 50µs(Max) from "Sleep state" to "Normal state".

- (Note 4) MCU sends "Clear Status" Command. Therefore, POR bit in status register is set to '0' (POR='1' to POR='0').

- (Note 5) VCC voltage drops below V<sub>CC\_POR1</sub> V<sub>CC\_POR\_hys</sub>. POR\_Circuit\_Output voltage is low (logic reset signal). POR bit register is set to '1'. State is changed to Reset state. Consequently, the analog circuit is OFF (I<sub>VS\_qui1</sub>=0µA Typ and I<sub>VCC\_qui1</sub>=2µA Typ).

- (Note 6) VCC voltage rises above V<sub>CC\_POR1</sub>. POR\_Circuit\_Output level is high (logic reset release) after filter time(2µs Typ).

- (Note 7) POR\_Circuit\_Output level is high. Therefore, State is changed to Sleep state.

- (Note 8) MCU sends the EN='1' command. State is changed to Normal state. Therefore, analog circuit becomes active(Ivs\_act=3.2mA Typ and Ivcc\_act=1.2mA Typ).

- (Note 9) MCU sends the "Clear Status" Command. Therefore, the POR bit register is set to '0'(POR='1' to POR='0').

- (Note 10) MCU sends the CPEN='1' command. Charge pump circuit is activated. Charge time is 0.2ms(Max).

- (Note 11) MCU sends the DRVEN='1' command. GH1, GL1, GH2 and GL2 outputs are active(Constant current driving). Each register setting is set before DRVEN='1'.

- (Note 12) MCU sends the DRVEN='0' command. GH1, GL1, GH2 and GL2 outputs are pulled low with a  $10\Omega$  pull down.

- (Note 13) MCU sends the EN='0' command. State is changed to Sleep state. Therefore, analog circuit turns OFF(Ivs\_qui1=0µA Typ, Ivcc\_qui1=2µA Typ and charge pump circuit is OFF).

- (Note 14) RSTB input is set to low level by MCU. State is changed to Reset state. POR bit register is to '1'.Therefore, the SPI interface can't be communicable.

- (Note 15) VCC voltage falls below V<sub>CC\_POR1</sub> V<sub>CC\_POR\_hys</sub>. POR\_Circuit\_Output level is low (logic reset signal).

- (Note 16) CSB falling edge and rising edge are described as below.

Clear NOP EN= Status CSB "falling edge' CSB "rising edge"

#### State Description

Table 1. State Description

| State         | CP  | GH1,GH2                                           | GL1,GL2                          | SPI      |  |

|---------------|-----|---------------------------------------------------|----------------------------------|----------|--|

| Reset         | OFF | 15kΩ pull down                                    | 15kΩ pull down                   | Inactive |  |

| Sleep         | OFF | 15kΩ pull down                                    | 15kΩ pull down                   | Active   |  |

| Normal        |     | ON(DRVEN=1):                                      | ON(DRVEN=1):                     | Active   |  |

|               | ON  | Output is synchronous                             | Output is synchronous            |          |  |

|               |     | with PWM1 <sup>(Note 1)</sup> or                  | with PWM1 <sup>(Note 1)</sup> or | Active   |  |

|               |     | PWM2 <sup>(Note 2)</sup> input                    | PWM2 <sup>(Note 2)</sup> input   |          |  |

|               |     | OFF(DRVEN=0): Outputs are OFF(DRVEN=0): Outputs a |                                  |          |  |

|               |     | Sink Driving Mode                                 | Sink Driving Mode                | Active   |  |

|               |     | (10Ω pull down)                                   | ( 10Ω pull down )                |          |  |

|               | OFF | 15kΩ pull down                                    | 15kΩ pull down / braking         | Active   |  |

|               | OIT |                                                   | mode                             |          |  |

| Protection1 C | ON  | Output is Sink Driving Mode                       | Output is Sink Driving Mode      | Active   |  |

|               | ON  | (10Ω pull down)                                   | ( 10Ω pull down )                |          |  |

| Protection2   | OFF | 15kΩ pull down                                    | 15kΩ pull down / braking         | Active   |  |

| Protection3   | OFF | 15kΩ pull down                                    | 15kΩ pull down                   | Inactive |  |

(Note 1) GH1 and GL1 outputs are synchronized to the PWM1 input.

(Note 2) GH2 and GL2 outputs are synchronized to the  $\ensuremath{\mathsf{PWM2}}$  input.

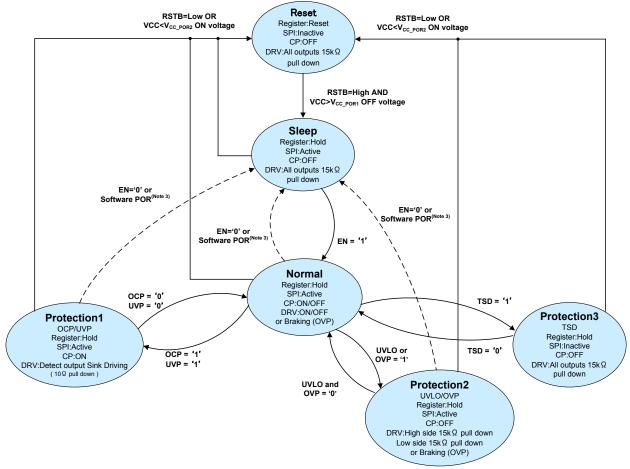

#### **Functional Description State Control**

(Note 3) This is Software POR command. It will set all register to default value. Note default value for POR register is 1.

#### Figure 13. Functional Description State Control

Transition time is  $2\mu$ s(Typ) between each state. This does not include any relevant the blanking time. (e.g. UVLO detect blanking time, OVP detect blanking time etc.).

If settings are changed while IC is in one of the Protection states, the settings become valid except for those which can influence the transition to that particular protection state itself. Transition from Protection states to Reset state or Sleep state occurs immediately. Transition to normal state is only possible when the particular protection condition (e.g. OCP, OVP, UVLO or TSD) is no more existing. Furthermore, only the channels which are having over current move to OCP Protection state. Other channels with normal currents stay in Normal state.

The following table describes validity of individual command settings when changed in Protection states.

| Command                                                    | Address                         | Protection1                          | Protection2                          |

|------------------------------------------------------------|---------------------------------|--------------------------------------|--------------------------------------|

| Software POR, Enable Register,<br>Status Read/Clear Status | 00h, 01h, 09h                   | Valid immediately                    | Valid immediately                    |

| Other Commands                                             | 02h, 03h, 04h, 05h,<br>06h, 07h | Valid immediately <sup>(note1)</sup> | Valid immediately <sup>(note2)</sup> |

(note1) Settings become immediately valid except for the Channel which is in OCP. For those channel, settings would become effective only when they move out of OCP. E.g. if OCP threshold value is changed while a channel is in OCP, the new value would be effective only when the channel moves out of OCP.

(note2) Settings become immediately valid except for those which can influence the transition to protection mode itself. E.g. when state is Protection2 due to UVLO, it cannot be disabled by setting UVLOM as '0'.

#### Reset State (Refer to Table 1, Table 2, Figure 13 and Figure 16)

If RSTB=Low or VCC < V<sub>CC\_POR1</sub> – V<sub>CC\_POR\_hys</sub> Voltage, the state changes to Reset state.

Logic is in Reset state, therefore SPI communication is impossible. All register data is cleared. In the Reset State all analog circuits are OFF, therefore  $I_{VS_{qui1}}=0\mu A$  and  $I_{VCC_{qui1}}=2\mu A$ . The driver outputs of BD16952EFV are pulled down by a 15k $\Omega$  (Typ) internal resistor. The Reset state changes to Sleep state when RSTB=High and VCC > V<sub>CC\_POR1</sub> Voltage.

#### Transition to Reset State

Transition to Reset State can be made with 2 type of operation methods.

1. when RSTB=Low.

2. when VCC <  $V_{CC\_POR1} - V_{CC\_POR\_hys}$  Voltage.

#### Sleep State (Refer to Table 1, Table 2, Figure 13 and Figure 16)

When RSTB=High and VCC >  $V_{CC\_POR1}$ , the state changes to the Sleep state. The logic is released from reset, therefore SPI communication is possible and all registers can be set. In the Sleep State, all analog circuits are OFF, therefore  $I_{VS\_qui1}=0\mu A$  and  $I_{VCC\_qui1}=2\mu A$ . The driver outputs of BD16952EFV are pulled down by a 15k $\Omega$  (Typ) internal resistor. However, the POR circuit remains active in Sleep State. When VCC <  $V_{CC\_POR1} - V_{CC\_POR\_hys}$ , is detected, the logic is reset and the state changes to the Reset State.

#### **Transition to Sleep State**

Transition to the Sleep State can be made with 2 type of operation methods.

- 1. when EN=0 (RSTB=High and VCC >  $V_{CC_POR1}$ )

- 2. by software reset (RSTB=High and VCC >  $V_{CC_POR1}$ ).

#### Normal State (Refer to Table 1 and Figure 13)

The Normal State is the standard operating state for BD16952EFV. When the enable register EN is set to '1', the state changes from Sleep State to Normal State. In the Normal State, all analog circuits are active and SPI communication is possible. Additionally, ON/OFF control of the charge pump and the driver output is possible by setting the registers CPEN and DRVEN. The driver outputs are pulled down with  $15k\Omega$  (Typ) when CPEN=0. However, when both DRVEN=1 and DRVEN=0, the driver outputs are actively driven low with  $10\Omega$  (Typ). When CPEN='1' and DRVEN='1' the driver outputs are synchronized with the PWM1 or PWM2 input.

#### Protection1 State (Refer to Table 1, Table 2, Figure 13 and Figure 25 to 27)

When Over Current Protection (OCP) or DRAIN terminal Under Voltage Protection (UVP) event is detected, the state changes to Protection1 State. In this state, the SPI registers hold their values, SPI communication remains possible and the Charge pump is kept in charged-up state. The driver outputs are actively pulled low with  $10\Omega$  (Typ). For driver output OFF operation of the over current detection, a latch mode and auto recovery mode can be selected. Only the output at which an OCP event is detected will be turned OFF.

#### Protection2 State (Refer to Table 1, Table 2, Figure 13 and Figure 17 to 22)

When a UVLO or OVP event is detected at the VS terminal, the state changes to the Protection2 state. In this state, the SPI registers hold their values, SPI communication remains possible and the charge pump stops charging. The driver outputs can either be pulled down with 15k $\Omega$  (Typ) or operate in braking mode, which is controlled by the MCU in case of a user-generated over-voltage event that is detected by the MCU. Both (UVLO and OVP) detection functions can be disabled, but not during an already detected OVP or UVLO event.

#### Protection3 State (Refer to Table 1, Table 2, Figure 13 and Figure 23)

When a TSD event is detected, the state changes to Protection3 State. In Protection3 state SPI registers hold their values, but SPI is disabled and the charge pump stops charging. The driver outputs are pulled down with  $15k\Omega$  (Typ).

#### **Dual Power Supply: VS and VCC**

The supply voltage VS supplies the charge-pump and low-side driver. An internal charge-pump is used to drive the high-side switches. The supply voltage VCC (3.3V/5V) is used for analog blocks and digital core of the BD16952EFV. Due to the independent VCC supply voltage, the logic control and logic status information is not lost even if the VS supply voltage is switched OFF. In case of power-on (VCC increases above the POR threshold V<sub>CC\_POR1</sub> = 2.00V Typ), the circuit is initialized by an internally generated power-on reset (POR). If the VCC voltage decreases under the POR threshold V<sub>CC\_POR1</sub> – V<sub>CC\_POR\_hys</sub> = 1.90V(Typ), the driver outputs (GH1, GH2, GL1 and GL2) are switched-off and the logic registers are set to default values.

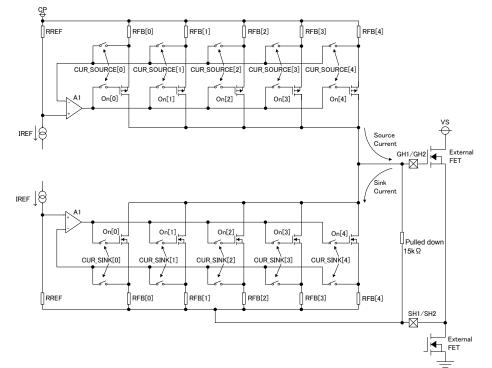

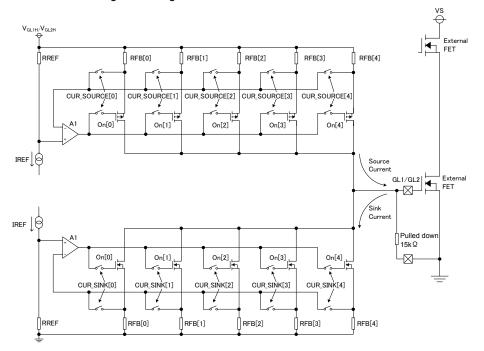

#### **Constant Current Control**

The controlled constant source and sink current values of the gate driver can be set individually by the SPI register. Setting ranges are 'Drivers OFF' and 1mA - 31mA in steps of 1mA. In the 'Drivers OFF' setting, the drivers are set to 0mA setting (CUR\_SINK [4:0] = 5'b00000). They can be synchronized with PWM1 or PWM2 input signal depending on the Half-bridge driver mode.

In Figure 14, the high-side constant current circuit is shown. Figure 15 shows the low-side constant current circuit. The global reference current 'IREF' is mirrored into the channel current to generate a local reference voltage while amplifier A1 forces the voltage across the current sense resistor to match the local reference voltage.

The output device is scaled to give a 5 bit output range so that the source/sink current values can be achieved in range of 1mA to 31mA by steps of 1mA. The source /sink current values do not contain the 15 k $\Omega$  pull down current.

Figure 14. High Side Constant Current Circuit

Figure 15. Low Side Constant Current Circuit

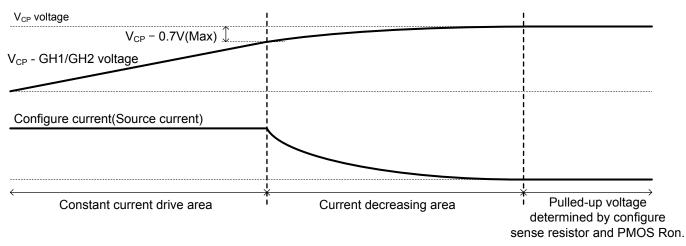

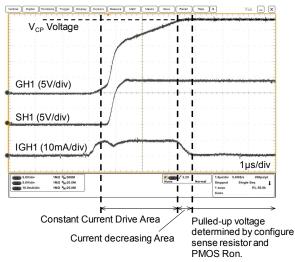

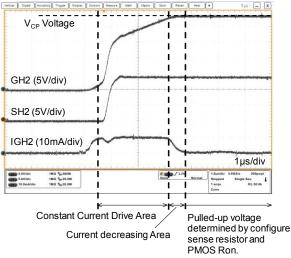

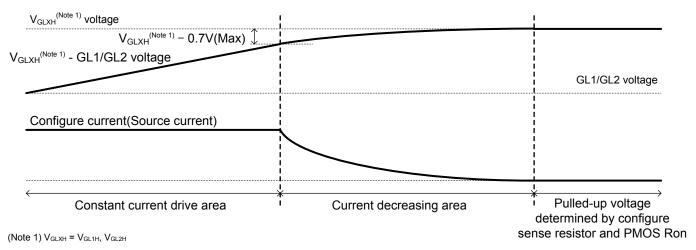

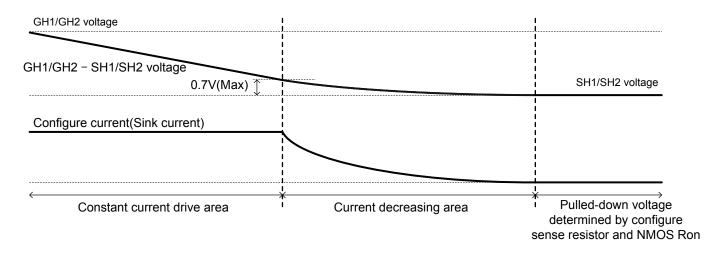

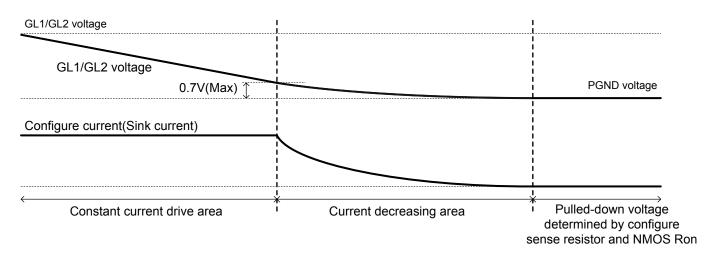

#### High Side Gate Driver Outputs at Saturation Source Current Control

When the GH1/GH2 terminal voltage exceeds  $V_{CP}$ -0.7V (Max), the source current decreases from the setting value. Therefore, the constant current drive range is within GH1/GH2 terminal voltage <  $V_{CP}$ -0.7V(Max). After constant current drive, GH1 and GH2 terminals are pulled up by the current sense resistor and PMOS ON-resistance (current sense resistor(RFB[0], RFB[1], RFB[2], RFB[3] and RFB[4]) and PMOS). The effective resistance value of the pulled-up is determined by current sense resistor and PMOS Ron.

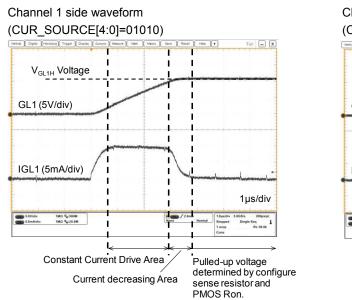

#### Evaluation Example (High Side Gate Voltage and Gate Current)

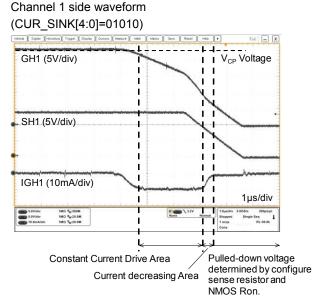

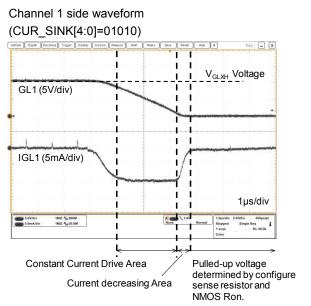

Channel 1 side waveform (CUR\_SOURCE[4:0]=01010)

#### Low Side Gate Driver Outputs at Saturation Source Current Control

When the GL1/GL2 terminal voltage exceeds  $V_{CLAMP}$ -0.7V (Max), the source current decreases from the setting value. Therefore, the constant current drive range is within GL1/GL2 terminal voltage <  $V_{GLXH}$ -0.7V (Max). After constant current drive, GL1 and GL2 terminals are pulled up on a current sense resistor and PMOS Ron (current sense resistor(RFB[0], RFB[1], RFB[2], RFB[3] and RFB[4]) and PMOS). The effective resistance value of the pulled-up is determined by current sense resistor and PMOS Ron.

#### Evaluation Example (High Side Gate Voltage and Gate Current)

Teit - X

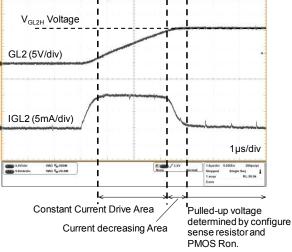

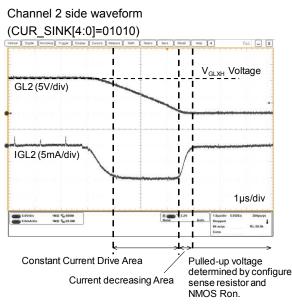

#### High Side Gate Driver Outputs at Saturation Sink Current Control

When GH1/GH2 terminal voltage falls below 0.7V (Max), the sink current decreases from the setting value. Therefore, constant current drive range is within GH1/GH2 terminal voltage > 0.7V (Max). Beyond this range, GH1 and GH2 terminals are pulled down on a current sense resistor and NMOS Ron (current sense resistors RFB[0], RFB[1], RFB[2], RFB[3] and RFB[4] and NMOS). The effective resistance value of the pulled-down is determined by current sense resistor and NMOS Ron.

#### Evaluation Example (High Side Gate Voltage and Gate Current)

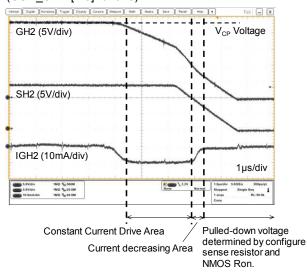

Channel 2 side waveform (CUR\_SINK[4:0]=01010)

#### Low Side Gate Driver Outputs at Saturation Sink Current Control

When GL1/GL2 terminal voltage falls below 0.7V (Max), the sink current decreases from the setting value. Therefore, constant current drive range is within GL1/GL2 terminal voltage > 0.7V (Max). Beyond this range, GL1 and GL2 terminals are pulled down on a current sense resistor and NMOS Ron (current sense resistors RFB[0], RFB[1], RFB[2], RFB[3] and RFB[4] and NMOS).

The effective resistance value of the pulled-down is determined by current sense resistor and NMOS Ron.

#### Evaluation Example (High Side Gate Voltage and Gate Current)

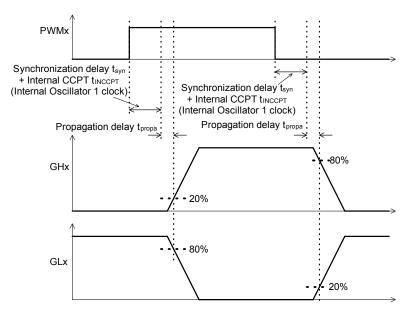

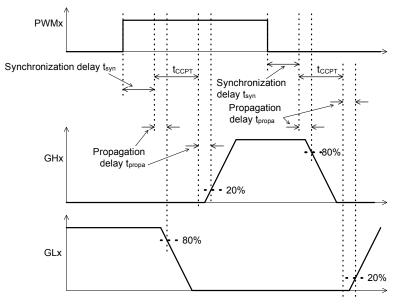

#### **PWM Control**

#### (Active Free Wheeling : Half-Bridge Control Mode=1000. See Mode Configuration on page 37)

The relationship of PWM, GHx and GLx outputs signal are as below. When the BD16952EFV detects the rising edge of the PWM signal, the GHx or GLx are turned on, after an asynchronous delay (Synchronization delay  $t_{syn}$ ). There is also an internal delay time(Propagation delay  $t_{propa}$ ). before GHx or GLx outputs are turned on.

The external MOSFETs in Half-bridge configuration are switched ON with an additional delay time  $t_{CCPT}$  (Cross Current Protection Time) between the sink current start of GL1 / GL2 and the source current start of GH1/GH2 to prevent cross current in the half-bridge. This value can be set by the SPI register in the range:

0.25µs...4µs (0.25µs steps)

4µs...12µs (1µs steps)

12µs...92µs (2µs steps)

#### **PWM Control**

#### ( Passive Free Wheeling : Independent Control Mode : PWM Control Mode. See Mode Configuration on page 37 )

The relationship of PWM, GHx and GLx outputs signal are shown below. When the BD16952EFV is detecting the high edge of the PWM signal, an asynchronous delay is present (Synchronization delay  $t_{syn}$ ) between the PWM signal and high-side source/sink or low-side source/sink of internal logic signal. Then, GHx or GLx are turned on. However, there is an internal delay time(Propagation delay  $t_{propa}$ ) before GHx or GLx outputs are turned on.

The GHx or GLx are switched ON with an additional delay time  $t_{\text{INCCPT}}$  (Internal Cross Current Protection Time) between the sink current end of GHx / GLx and the source current start of GHx / GLx to prevent cross current.