# mail

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

Property Economics

### System LED Drivers for Mobile phones

#### BD2802GU

No.11041EAT12

#### Description

The BD2802GU is a RGB LED driver specifically engineered for decoration purposes. This RGB driver incorporates lighting patterns and illuminates without imposing any load on CPU. This RGB driver is best-suited for illumination using RGB LEDs and decoration using monochrome LEDs. In addition, this RGB driver has been successfully miniaturized through the use of a VCSP85H2 (2.8 mm 0.5 mm pitch) chip size package.

#### Features

- 1) RGB LED driver (dual drivers)

- A slope control function is incorporated (allowing dual drivers to be controlled independently).

- Slope control can be implemented using the DC current.

- Two modes "continuous illumination mode" and "illumination single cycle mode" are supported.

- Independent external ON/OFF synchronizing terminals (of dual drivers) are provided.

- Multiple drivers can be used concurrently by using the I<sup>2</sup>C address change function and supporting reference clock I/O.

- 2) Thermal shutdown

- 3) I<sup>2</sup>C BUS fast mode support (maximum rate: 400 kHz)

- A device address can be changed via an external pin.

- \* This driver has not been designed for anti-radiation.

- This document may be altered without prior notice.

- This document does not provide for delivery.

#### ●Absolute Maximum Ratings(Ta=25°C)

| Parameter                   | Symbol | Limits                  | Unit |

|-----------------------------|--------|-------------------------|------|

| Maximum Applied voltage     | VMAX   | 7                       | V    |

| Power Dissipation           | Pd     | 1250 <sup>(Note1)</sup> | mW   |

| Operating Temperature Range | Topr   | -40 ~ +85               | °C   |

| Storage Temperature Range   | Tstg   | -55 ~ +150              | °C   |

(Note1)Power dissipation deleting is 10.0mW/ $^{\circ}$ C, when it's used in over 25  $^{\circ}$ C. (It's deleting is on the board that is ROHM's standard)

#### ●Recommended Operating Conditions(VBAT≧VIO, Ta=-40~85°C)

| Parameter          | Symbol | Limits     | Unit |

|--------------------|--------|------------|------|

| VBAT input voltage | VBAT   | 2.7 ~ 5.5  | V    |

| VIO pin voltage    | VIO    | 1.65 ~ 3.3 | V    |

#### ● Electrical Characteristics(Unless otherwise specified, Ta=25°C, VBAT=3.6V, VIO=1.8V)

|                                                  |                |                  | · · · · · · · · · · · · · · · · · · · | VDA1-0.0V | , 10-1.  |                                                                                         |

|--------------------------------------------------|----------------|------------------|---------------------------------------|-----------|----------|-----------------------------------------------------------------------------------------|

| Parameter                                        | Symbol         | Min.             | Limits<br>Typ.                        | Max.      | Unit     | Condition                                                                               |

| [Circuit Current]                                |                | IVIIII.          | тур.                                  | IvidX.    |          |                                                                                         |

| VBAT Circuit current 1                           | IBAT1          | -                | 0.1                                   | 3.0       | μA       | RESETB=0V, VIO =0V                                                                      |

| VBAT Circuit current 1<br>VBAT Circuit current 2 | IBAT1<br>IBAT2 | -                | 0.1                                   | 3.0       | μΑ       | RESETB=0V, VIO=1.8V                                                                     |

| VBAT Circuit current 2                           | IDAI 2         | -                | 0.5                                   | 3.0       | μΑ       | ,                                                                                       |

| VBAT Circuit current 3                           | IBAT3          | -                | 0.8                                   | 1.2       | mA       | LED 6Ch ON, ILED=10mA setting<br>Exclusive of LED current,<br>RGBISET =120k $\Omega$    |

| 【LED Driver】                                     |                |                  |                                       |           |          |                                                                                         |

| LED current Step                                 | ILEDSTP        |                  | 128                                   |           | step     | RGB1 group, RGB2 group                                                                  |

| LED Maximum setup<br>curren                      | IMAX           | -                | -                                     | 30.48     | mA       | RGB1 group, RGB2 group<br>RGBISET=100kΩ                                                 |

| LED current accurate                             | ILED           | 18               | 20                                    | 22        | mA       | RGB1 group, RGB2 group,<br>Terminal voltage =1V<br>ILED=20mA setting, RGBISET<br>=120kΩ |

| LED current Matching                             | ILEDMT         | -                | 5                                     | 10        | %        | RGB1 group, between RGB2 group,<br>Terminal voltage =1V<br>ILED=20mA setting            |

| LED OFF Leak current                             | ILKL           | -                | -                                     | 1.0       | μA       |                                                                                         |

| [OSC]                                            |                |                  |                                       |           |          | ·                                                                                       |

| OSC oscillation frequency                        | fosc           | 0.8              | 1.0                                   | 1.2       | MHz      |                                                                                         |

| [SDA, SCL] (I2C interfac                         | e)             |                  |                                       |           |          |                                                                                         |

| L level input voltage                            | VILI           | -0.3             | -                                     | 0.25×VIO  | V        |                                                                                         |

| H level input voltage                            | VIHI           | 0.75×VIO         | -                                     | VBAT+0.3  | V        |                                                                                         |

| Hysteresis of Schmitt<br>trigger input           | Vhysl          | 0.05×VIO         | -                                     | -         | V        |                                                                                         |

| L level output voltage                           | VOLI           | 0                | -                                     | 0.3       | V        | SDA pin, IOL=3 mA                                                                       |

| Input current                                    | linl           | -10              | -                                     | 10        | μA       | Input voltage = 0.1×VIO~0.9×VIO                                                         |

| 【RESETB】(CMOS input                              | pin)           | L                | I                                     | 1         |          | 1                                                                                       |

| L level input voltage                            | VILR           | -0.3             | -                                     | 0.25×VIO  | V        |                                                                                         |

| H level input voltage                            | VIHR           | 0.75×VIO         | -                                     | VBAT+0.3  | V        |                                                                                         |

| Input current                                    | linR           | -10              | -                                     | 10        | μA       | Input voltage = 0.1×VIO~0.9×VIO                                                         |

| 【ADDSEL】 (CMOS input                             | pin)           | I                | I                                     |           |          |                                                                                         |

| L level input voltage                            | VILADD         | -0.3             | -                                     | 0.25×VBAT | V        |                                                                                         |

| H level input voltage                            | VIHADD         | 0.7 ×VBAT        | -                                     | VBAT+0.3  | V        |                                                                                         |

| Input current                                    | linADD         | -10              | -                                     | 10        | μA       | Input voltage = 0.1×VBAT~0.9×VBAT                                                       |

| •                                                |                | out pin with     | Pull-down r                           |           | <b>1</b> |                                                                                         |

| L level input voltage                            | VILCNT         | -0.3             | -                                     | 0.25×VIO  | V        |                                                                                         |

| H level input voltage                            | VILOINT        | 0.75×VIO         | -                                     | VBAT+0.3  | V        |                                                                                         |

| Input current                                    | linCNT         | -                | 3.6                                   | 10        | μA       | Input voltage = 1.8V                                                                    |

| [CLKIO(Output)] (CMOS                            |                | )                | 0.0                                   |           | μ.,      |                                                                                         |

| L level output voltage                           | VOLCLK         | -                | -                                     | 0.2       | V        | IOL=1mA                                                                                 |

| H level output voltage                           | VOLCLK         | VIO-0.2          |                                       | -         | V        | IOH=1mA                                                                                 |

| Output frequency                                 | fclk           | 200              | 250                                   | 300       | kHz      |                                                                                         |

| [CLKIO (Input)] (CMOS                            |                | 200              | 200                                   | 500       | ΝIΖ      |                                                                                         |

| L level input voltage                            | VILCLK         | -0.3             | -                                     | 0.25×VIO  | V        |                                                                                         |

| H level input voltage                            | VILCLK         | -0.3<br>0.75×VIO | -                                     | VIO+0.3   | V        |                                                                                         |

|                                                  |                | 0.75×VIU         | -                                     |           |          |                                                                                         |

| Input current                                    | linCLK         | -                | 3.6                                   | 10        | μA       | Input voltage = 1.8V                                                                    |

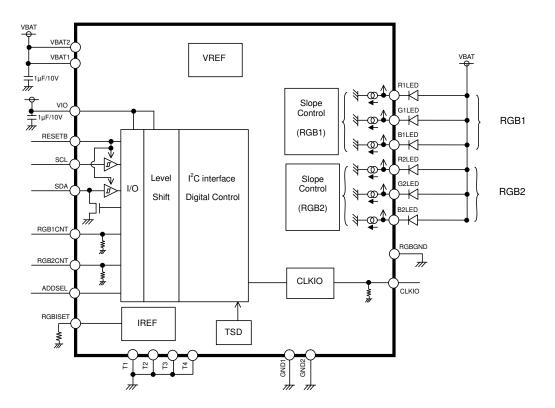

#### Block Diagram / Application Circuit example

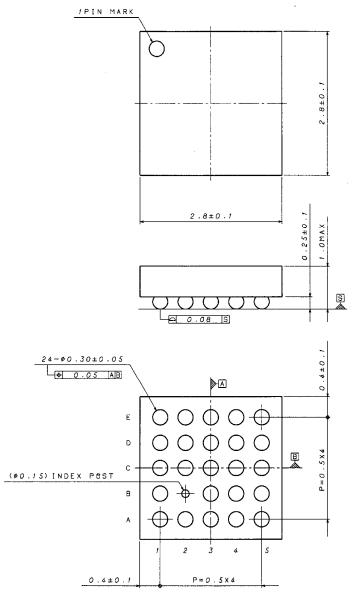

#### •Pin Arrangement [Bottom View]

| E | T4    | G2LED   | RGBGND  | G1LED  | Т3    |

|---|-------|---------|---------|--------|-------|

| D | B2LED | R2LED   | B1LED   | R1LED  | VBAT1 |

| С | VBAT2 | RGBISE  | RGB1CNT | ADDSEL | GND2  |

| В | GND1  | index   | CLKIO   | SCL    | SDA   |

| А | T1    | RGB2CNT | VIO     | RESETB | T2    |

|   | 1     | 2       | 3       | 4      | 5     |

#### Outside size figure

VCSP85H2 CSP small Package Size : 2.8mm×2.8mm (Tolerance : ± 0.1mm each side) height 1.0mm max Ball pitch : 0.5 mm

(UNIT:mm)

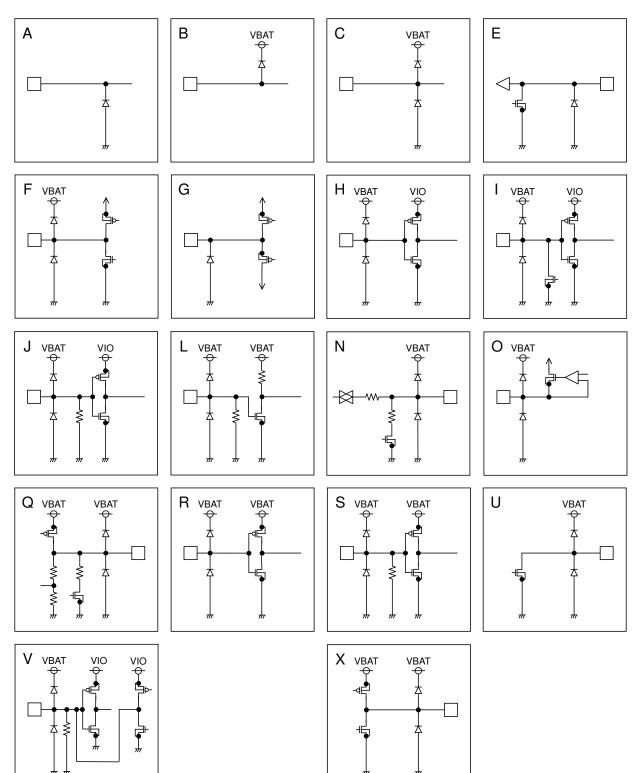

#### Pin Functions

| No | Pin No. | Pin Name | I/O | Input<br>For Power | Level<br>For GND | ESD Diode                                               | Functions |

|----|---------|----------|-----|--------------------|------------------|---------------------------------------------------------|-----------|

| 1  | D5      | VBAT1    | -   | -                  | GND              | Battery is connected                                    | Α         |

| 2  | C1      | VBAT2    | -   | -                  | GND              | Battery is connected                                    | А         |

| 3  | A1      | T1       | -   | VBAT               | GND              | Test Pin (short to GND)                                 | S         |

| 4  | A5      | T2       | -   | VBAT               | GND              | GND Test Pin (short to GND)                             |           |

| 5  | E5      | Т3       | -   | VBAT               | GND              | Test Pin (short to GND)                                 | S         |

| 6  | E1      | T4       | -   | VBAT               | -                | Test Pin (short to GND)                                 | В         |

| 7  | A3      | VIO      | -   | VBAT               | GND              | I/O voltage source is connected                         | С         |

| 8  | A4      | RESETB   | I   | VBAT               | GND              | Reset input (L: RESET, H: RESET cancel)                 | Н         |

| 9  | B5      | SDA      | I/O | VBAT               | GND              | I <sup>2</sup> C data input                             | I         |

| 10 | B4      | SCL      | I   | VBAT               | GND              | I <sup>2</sup> C clock input                            | н         |

| 11 | B1      | GND1     | -   | VBAT               | -                | Ground                                                  | В         |

| 12 | C5      | GND2     | -   | VBAT               | -                | Ground                                                  | В         |

| 13 | E3      | RGBGND   | -   | VBAT               | -                | Ground                                                  | В         |

| 14 | C2      | RGBISET  | I   | VBAT               | GND              | RGB LED reference current                               | 0         |

| 15 | D4      | R1LED    | I   | -                  | GND              | Red LED1 connected                                      | E         |

| 16 | E4      | G1LED    | I   | -                  | GND              | Green LED1 connected                                    | E         |

| 17 | D3      | B1LED    | I   | -                  | GND              | Blue LED1 connected                                     | E         |

| 18 | D2      | R2LED    | I   | -                  | GND              | Red LED2 connected                                      | E         |

| 19 | E2      | G2LED    | I   | -                  | GND              | Green LED2 connected                                    | E         |

| 20 | D1      | B2LED    | I   | -                  | GND              | Blue LED2 connected                                     | E         |

| 21 | C3      | RGB1CNT  | I   | VBAT               | GND              | RGB1 LED external ON/OFF Synchronism (L : OFF, H : ON)* | J         |

| 22 | A2      | RGB2CNT  | I   | VBAT               | GND              | RGB2 LED external ON/OFF Synchronism (L : OFF, H : ON)* | J         |

| 23 | C4      | ADDSEL   | I   | VBAT               | GND              | I <sup>2</sup> C device address change terminal         | R         |

| 24 | B3      | CLKIO    | I/O | VBAT               | GND              | Standard clock input-and-output terminal                | V         |

\* A setup of a register is separately necessary to validate it.

#### Equivalent circuit diagram

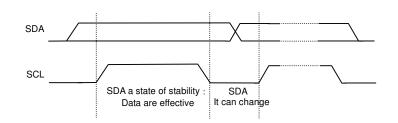

#### ●I<sup>2</sup>C BUS format

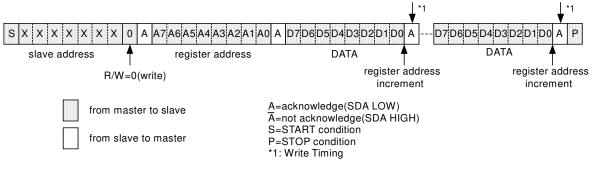

The writing operation is based on the I<sup>2</sup>C slave standard.

Slave address

| ac |          |    |    |    |    |    |    |    |     |  |  |  |

|----|----------|----|----|----|----|----|----|----|-----|--|--|--|

|    |          | A7 | A6 | A5 | A4 | A3 | A2 | A1 | R/W |  |  |  |

|    | ADDSEL=L | 0  | 0  | 1  | 1  | 0  | 1  | 0  | 0   |  |  |  |

|    | ADDSEL=H | 0  | 0  | 1  | 1  | 0  | 1  | 1  | 0   |  |  |  |

|    |          |    |    |    |    |    |    |    |     |  |  |  |

Slave address can be changed with the external terminal ADDSEL.

Bit Transfer

SCL transfers 1-bit data during H. SCL cannot change signal of SDA during H at the time of bit transfer. If SDA changes while SCL is H, START conditions or STOP conditions will occur and it will be interpreted as a control signal.

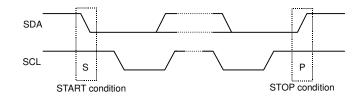

START and STOP condition

When SDA and SCL are H, data is not transferred on the  $I^2$ C- bus. This condition indicates, if SDA changes from H to L while SCL has been H, it will become START (S) conditions, and an access start, if SDA changes from L to H while SCL has been H, it will become STOP (P) conditions and an access end.

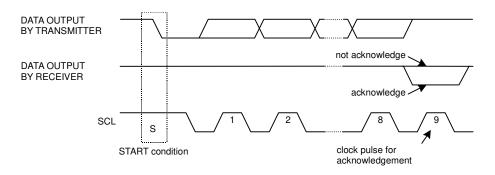

#### Acknowledge

It transfers data 8 bits each after the occurrence of START condition. A transmitter opens SDA after transfer 8 bits data, and a receiver returns the acknowledge signal by setting SDA to L.

#### Writing protocol

A register address is transferred by the next 1 byte that transferred the slave address and the write-in command. The 3rd byte writes data in the internal register written in by the 2nd byte, and after 4th byte or, the increment of register address is carried out automatically. However, when a register address turns into the last address, it is set to 00h by the next transmission. After the transmission end, the increment of the address is carried out.

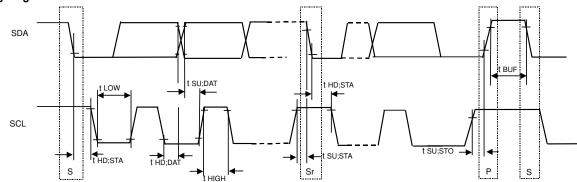

#### Timing diagram

#### ●Electrical Characteristics(Unless otherwise specified, Ta=25 °C, VBAT=3.6V, VIO=1.8V)

| Parameter                                       | Cumbol  | Sta  | andard-m | ode  | F    | ast-mode |      | Unit |

|-------------------------------------------------|---------|------|----------|------|------|----------|------|------|

| Parameter                                       | Symbol  | Min. | Тур.     | Max. | Min. | Тур.     | Max. | Unit |

| [I <sup>2</sup> C BUS format]                   |         |      |          |      |      |          |      |      |

| SCL clock frequency                             | fscl    | 0    | -        | 100  | 0    | -        | 400  | kHz  |

| LOW period of the SCL clock                     | tLOW    | 4.7  | -        | -    | 1.3  | -        | -    | μs   |

| HIGH period of the SCL clock                    | thigh   | 4.0  | -        | -    | 0.6  | -        | -    | μs   |

| Hold time (repeated) START condition            | thd;sta | 4.0  | -        |      | 0.6  | -        | -    |      |

| After this period, the first clock is generated |         | 4.0  |          | -    | 0.0  |          |      | μs   |

| Set-up time for a repeated START                | toutota | 4.7  |          |      | 0.6  | -        | -    | 110  |

| condition                                       | tsu;sta | 4.7  | -        | -    | 0.6  |          |      | μs   |

| Data hold time                                  | thd;dat | 0    | -        | 3.45 | 0    | -        | 0.9  | μs   |

| Data set-up time                                | tsu;dat | 250  | -        | -    | 100  | -        | -    | ns   |

| Set-up time for STOP condition                  | tsu;sto | 4.0  | -        | -    | 0.6  | -        | -    | μs   |

| Bus free time between a STOP                    | 4       | 47   |          |      | 1.0  |          |      |      |

| and START condition                             | tBUF    | 4.7  | -        | -    | 1.3  | -        | -    | μs   |

| Address | W/R |           |           |           | Resiste   | er data |          |          |          | Function               |  |

|---------|-----|-----------|-----------|-----------|-----------|---------|----------|----------|----------|------------------------|--|

| Audiess | W/n | D7        | D6        | D5        | D4        | D3      | D2       | D1       | D0       | Tunction               |  |

| 00h     | W   | -         | -         | CLKMD     | CLKEN     | -       | -        | -        | SFTRST   | Soft Reset clock setup |  |

| 01h     | W   | -         | RGB2MEL   | RGB2OS    | RGB2EN    | -       | RGB1MEL  | RGB1OS   | RGB1EN   | RBG-LED control        |  |

| 02h     | W   | SFRGB1(1) | SFRGB1(0) | SRRGB1(1) | SRRGB1(0) | -       | TRGB1(2) | TRGB1(1) | TRGB1(0) | RGB1-hour setup        |  |

| 03h     | W   | -         | IR11(6)   | IR11(5)   | IR11(4)   | IR11(3) | IR11(2)  | IR11(1)  | IR11(0)  | R1 current 1 setup     |  |

| 04h     | W   | -         | IR12(6)   | IR12(5)   | IR12(4)   | IR12(3) | IR12(2)  | IR12(1)  | IR12(0)  | R1 current 2 setup     |  |

| 05h     | W   | -         | -         | -         | -         | PR1(3)  | PR1(2)   | PR1(1)   | PR1(0)   | R1 Wave patturn setup  |  |

| 06h     | W   | -         | IG11(6)   | IG11(5)   | IG11(4)   | IG11(3) | IG11(2)  | IG11(1)  | IG11(0)  | G1 current 1 setup     |  |

| 07h     | W   | -         | IG12(6)   | IG12(5)   | IG12(4)   | IG12(3) | IG12(2)  | IG12(1)  | IG12(0)  | G1 current 2 setup     |  |

| 08h     | W   | -         | -         | -         | -         | PG1(3)  | PG1(2)   | PG1(1)   | PG1(0)   | G1 Wave patturn setup  |  |

| 09h     | W   | -         | IB11(6)   | IB11(5)   | IB11(4)   | IB11(3) | IB11(2)  | IB11(1)  | IB11(0)  | B1 current 1 setup     |  |

| 0Ah     | W   | -         | IB12(6)   | IB12(5)   | IB12(4)   | IB12(3) | IB12(2)  | IB12(1)  | IB12(0)  | B1 current 2 setup     |  |

| 0Bh     | W   | -         | -         | -         | -         | PB1(3)  | PB1(2)   | PB1(1)   | PB1(0)   | B1 Wave patturn setup  |  |

| 0Ch     | W   | SFRGB2(1) | SFRGB2(0) | SRRGB2(1) | SRRGB2(0) | -       | TRGB2(2) | TRGB2(1) | TRGB2(0) | RGB2-hour setup        |  |

| 0Dh     | W   | -         | IR21(6)   | IR21(5)   | IR21(4)   | IR21(3) | IR21(2)  | IR21(1)  | IR21(0)  | R2 current 1 setup     |  |

| 0Eh     | W   | -         | IR22(6)   | IR22(5)   | IR22(4)   | IR22(3) | IR22(2)  | IR22(1)  | IR22(0)  | R2 current 2 setup     |  |

| 0Fh     | W   | -         | -         | -         | -         | PR2(3)  | PR2(2)   | PR2(1)   | PR2(0)   | R2 Wave patturn        |  |

| 10h     | W   | -         | IG21(6)   | IG21(5)   | IG21(4)   | IG21(3) | IG21(2)  | IG21(1)  | IG21(0)  | G2 current 1 setup     |  |

| 11h     | W   | -         | IG22(6)   | IG22(5)   | IG22(4)   | IG22(3) | IG22(2)  | IG22(1)  | IG22(0)  | G2 current 2 setup     |  |

| 12h     | W   | -         | -         | -         | -         | PG2(3)  | PG2(2)   | PG2(1)   | PG2(0)   | G2 Wave patturn setup  |  |

| 13h     | W   | -         | IB21(6)   | IB21(5)   | IB21(4)   | IB21(3) | IB21(2)  | IB21(1)  | IB21(0)  | B2 current 1 setup     |  |

| 14h     | W   | -         | IB22(6)   | IB22(5)   | IB22(4)   | IB22(3) | IB22(2)  | IB22(1)  | IB22(0)  | B2 current 2 setup     |  |

| 15h     | W   | -         | -         | -         | -         | PB2(3)  | PB2(2)   | PB2(1)   | PB2(0)   | B2 Wave patturn setup  |  |

#### Register map

Input "0" for "-". Vacancy address may be use for test. Prohibit to accessing the address that isn't mentioned and the register for test.

#### Register Description

Adress 00h <Soft Reset>

| ріт | BIT Name | Initial | Fu                             | nction                           |

|-----|----------|---------|--------------------------------|----------------------------------|

| DII | Name     | miliai  | 0                              | 1                                |

| D7  | -        | -       | -                              | -                                |

| D6  | -        | -       | -                              | -                                |

| D5  | CLKMD    | 0       | Clock Input mode               | Clock Output mode                |

| D4  | CLKEN    | 0       | Clock input and output invalid | Clock input and output Effective |

| D3  | -        | -       | -                              | -                                |

| D2  | -        | -       | -                              | -                                |

| D1  | -        | -       | -                              | -                                |

| D0  | SFTRST   | 0       | Reset Release                  | Reset                            |

#### Adress 01h <RGB LED control >

| BIT | Name    | Init | Func                          | otion                       |

|-----|---------|------|-------------------------------|-----------------------------|

| DII | Name    | mint | 0                             | 1                           |

| D7  | -       | -    | -                             | -                           |

| D6  | RGB2MEL | 0    | RGB2 external control invalid | RGB2 external control valid |

| D5  | RGB2OS  | 0    | RGB2 Stop                     | RGB2 1 periodic operation   |

| D4  | RGB2EN  | 0    | RGB2 Stop                     | RGB2 continuous operation   |

| D3  | -       | -    | -                             | -                           |

| D2  | RGB1MEL | 0    | RGB1 external control invalid | RGB1 external control valid |

| D1  | RGB1OS  | 0    | RGB1 Stop                     | RGB1 1 periodic operation   |

| D0  | RGB1EN  | 0    | RGB1 Stop                     | RGB1 continuous operation   |

\* RGB\*OS returns to 0 automatically after 1 cycle operation.

\* RGB\*EN precedes to RGB\*OS. In use in 1 cycle operation, there is the necessity for RGB\*EN=0.

Adress 02h <RGB1 time>

| BIT          | Name      | Init       | Function                                                                                                                                                            |          |                                            |                                                        |  |  |  |  |

|--------------|-----------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------------------------------|--------------------------------------------------------|--|--|--|--|

|              |           |            |                                                                                                                                                                     | 0        |                                            | 1                                                      |  |  |  |  |

|              |           |            | SFRGB1(                                                                                                                                                             | 1)       | SFRGB1(0)                                  | Slope Down transition                                  |  |  |  |  |

| D7           | SFRGB1(1) | 0          | 0                                                                                                                                                                   |          | 0                                          | 0                                                      |  |  |  |  |

|              |           |            | 0                                                                                                                                                                   |          | 1                                          | Wave form cycle / 16                                   |  |  |  |  |

|              |           |            | 1                                                                                                                                                                   |          | 0                                          | Wave form cycle / 8                                    |  |  |  |  |

|              |           |            | 1                                                                                                                                                                   |          | 1                                          | Wave form cycle / 4                                    |  |  |  |  |

| D6           | SFRGB1(0) | 0          |                                                                                                                                                                     |          | control, and the reactime from a slope sta | tion time of the analog section is art to a slope end. |  |  |  |  |

|              |           |            | SRRGB1(                                                                                                                                                             | 1)       | SRRGB1(0)                                  | Slope Up transition                                    |  |  |  |  |

| D5 SRRGB1(1) | (1) 0     | 0          |                                                                                                                                                                     | 0        | 0                                          |                                                        |  |  |  |  |

|              |           |            | 0                                                                                                                                                                   |          | 1                                          | Wave form cycle / 16                                   |  |  |  |  |

|              |           |            | 1                                                                                                                                                                   |          | 0                                          | Wave form cycle / 8                                    |  |  |  |  |

|              |           | (0) 0      | 1                                                                                                                                                                   |          | 1                                          | Wave form cycle / 4                                    |  |  |  |  |

| D4           | SRRGB1(0) |            | It is a theoretical value on logic control, and the reaction time of the analog section is not included."Slope time" is the time from a slope start to a slope end. |          |                                            |                                                        |  |  |  |  |

| D3           | -         | -          |                                                                                                                                                                     | -        |                                            | -                                                      |  |  |  |  |

|              |           |            | TRGB1(2)                                                                                                                                                            | TRGB1(1) | TRGB1(0)                                   | Wave form cycle                                        |  |  |  |  |

| D2           | TRGB1(2)  | 0          | 0                                                                                                                                                                   | 0        | 0                                          | 0.131 s                                                |  |  |  |  |

|              |           |            | 0                                                                                                                                                                   | 0        | 1                                          | 0.52 s                                                 |  |  |  |  |

|              |           |            | 0                                                                                                                                                                   | 1        | 0                                          | 1.05 s                                                 |  |  |  |  |

| D1           | TRGB1(1)  | 0          | 0                                                                                                                                                                   | 1        | 1                                          | 2.10 s                                                 |  |  |  |  |

|              |           |            | 1                                                                                                                                                                   | 0        | 0                                          | 4.19 s                                                 |  |  |  |  |

|              |           |            | 1                                                                                                                                                                   | 0        | 1                                          | 8.39 s                                                 |  |  |  |  |

| D0           | TRGB1(0)  | (RGB1(0) 0 | 1                                                                                                                                                                   | 1        | 0                                          | 12.6 s                                                 |  |  |  |  |

|              | (0)       | U U        | 1                                                                                                                                                                   | 1        | 1                                          | 16.8 s                                                 |  |  |  |  |

Setting time is counted based on the frequency of OSC. The above-mentioned value is a value at the time of Typ (1MHz). When operating by the external clock, input frequency is a value at the time of Typ (250kHz).

Adress 03h <R1 current 1setup >

| BIT | Name    | Init  |           |           |           | Fur     | nction  |         |         |                |  |

|-----|---------|-------|-----------|-----------|-----------|---------|---------|---------|---------|----------------|--|

| DII | iname   | IIIIL |           | 0         |           |         |         | 1       |         |                |  |

| D7  | -       | -     |           | -         |           |         |         |         | -       |                |  |

| D6  | IR11(6) | 0     | IR11(6)   | IR11(5)   | IR11(4)   | IR11(3) | IR11(2) | IR11(1) | IR11(0) | Current        |  |

| D5  | IR11(5) | 0     | 0         | 0         | 0         | 0       | 0       | 0       | 0       | 0              |  |

| D4  | IR11(4) | 0     | 0         | 0         | 0         | 0       | 0       | 0       | 1       | 0.2mA          |  |

| D3  | IR11(3) | 0     | •         | •         |           | •       | •       |         | •       | 0.2mA          |  |

| D2  | IR11(2) | 0     | 1         | •         | 1         | •       | 1       | 1       | •       | step<br>25.2mA |  |

| D1  | IR11(1) | 0     | 1         | 1         | 1         | 1       | 1       | 1       | 1       | 25.4mA         |  |

| D0  | IR11(0) | 0     | At RGBISE | Tpin 120k | Ω connect | ion     |         |         |         |                |  |

#### Adress 04h <R1 current2 setup >

| BIT | Name    | Init  |                                |         |         | Fun     | oction  |         |         |         |  |

|-----|---------|-------|--------------------------------|---------|---------|---------|---------|---------|---------|---------|--|

| DII | Name    | IIIIL |                                | C       | )       |         | 1       |         |         |         |  |

| D7  | -       | -     |                                | -       |         |         |         |         | -       |         |  |

| D6  | IR12(6) | 0     | IR12(6)                        | IR12(5) | IR12(4) | IR12(3) | IR12(2) | IR12(1) | IR12(0) | Current |  |

| D5  | IR12(5) | 0     | 0                              | 0       | 0       | 0       | 0       | 0       | 0       | 0       |  |

| D4  | IR12(4) | 0     | 0                              | 0       | 0       | 0       | 0       | 0       | 1       | 0.2mA   |  |

| D3  | IR12(3) | 0     | •                              | •       | •       | •       | •       | •       | •       | 0.2mA   |  |

|     |         | •     | •                              | •       | •       | •       | •       | •       | •       | step    |  |

| D2  | IR12(2) | 0     | 1                              | 1       | 1       | 1       | 1       | 1       | 0       | 25.2mA  |  |

| D1  | IR12(1) | 0     | 1 1 1 1 1 1 1 25.4mA           |         |         |         |         |         | 25.4mA  |         |  |

| D0  | IR12(0) | 0     | At RGBISETpin 120kΩ connection |         |         |         |         |         |         |         |  |

#### Adress 05h <R1 Wave Pattern >

| BIT        | Name     | Init |        |        | Fu     | nction |           |  |  |

|------------|----------|------|--------|--------|--------|--------|-----------|--|--|

| ЫТ         | Name     |      |        | 0      |        |        | 1         |  |  |

| D7         | -        | -    |        | -      |        | -      |           |  |  |

| D6         | -        | -    |        | -      |        |        | -         |  |  |

| D5         | -        | -    |        | -      |        |        | -         |  |  |

| D4         | -        | -    |        | -      |        |        | -         |  |  |

| D3         | PR1(3)   | 0    | PR1(3) | PR1(2) | PR1(1) | PR1(0) | Wave      |  |  |

| 00         | 111(0)   | 0    | 0      | 0      | 0      | 0      | Pattern1  |  |  |

|            |          |      | 0      | 0      | 0      | 1      | Pattern2  |  |  |

| D2         | PR1(2)   | 1    | 0      | 0      | 1      | 0      | Pattern3  |  |  |

|            |          |      | •      | •      | •      | •      | •         |  |  |

|            |          |      | •      | •      | -      | •      |           |  |  |

| D1         | PR1(1)   | 1    | •      | •      | •      | •      | •         |  |  |

|            |          |      | 1      | 1      | 0      | 1      | Pattern14 |  |  |

| <b>D</b> 0 |          |      | 1      | 1      | 1      | 0      | Pattern15 |  |  |

| D0         | 0 PR1(0) |      | 1      | 1      | 1      | 1      | Pattern16 |  |  |

#### Adress 06h <G1 current1 setup >

| BIT | Name    | Init | Function                       |         |         |         |         |         |         |               |

|-----|---------|------|--------------------------------|---------|---------|---------|---------|---------|---------|---------------|

| DII | Name    | ITIL |                                | (       | )       |         |         |         | 1       |               |

| D7  | -       | -    |                                |         | -       |         |         |         | -       |               |

| D6  | IG11(6) | 0    | IG11(6)                        | IG11(5) | IG11(4) | IG11(3) | IG11(2) | IG11(1) | IG11(0) | Current       |

| D5  | IG11(5) | 0    | 0                              | 0       | 0       | 0       | 0       | 0       | 0       | 0             |

| D4  | IG11(4) | 0    | 0                              | 0       | 0       | 0       | 0       | 0       | 1       | 0.2mA         |

| D3  | IG11(3) | 0    |                                |         | •       | •       | •       |         | •       | 0.2mA<br>step |

| D2  | IG11(2) | 0    | 1                              | 1       | 1       | 1       | 1       | 1       | 0       | 25.2mA        |

| D1  | IG11(1) | 0    | 1                              | 1       | 1       | 1       | 1       | 1       | 1       | 25.4mA        |

| D0  | IG11(0) | 0    | At RGBISETpin 120kΩ connection |         |         |         |         |         |         |               |

Adress 07h <G1 current2 setup >

| BIT | Name    | Init  |           | Function                       |         |         |         |         |         |               |  |  |

|-----|---------|-------|-----------|--------------------------------|---------|---------|---------|---------|---------|---------------|--|--|

| DII | Name    | ITIIL |           | (                              | )       |         |         | 1       |         |               |  |  |

| D7  | -       | -     |           |                                | -       |         |         |         | -       |               |  |  |

| D6  | IG12(6) | 0     | IG12(6)   | IG12(5)                        | IG12(4) | IG12(3) | IG12(2) | IG12(1) | IG12(0) | Current       |  |  |

| D5  | IG12(5) | 0     | 0         | 0                              | 0       | 0       | 0       | 0       | 0       | 0             |  |  |

| D4  | IG12(4) | 0     | 0         | 0                              | 0       | 0       | 0       | 0       | 1       | 0.2mA         |  |  |

| D3  | IG12(3) | 0     |           | •                              | •       | •       | •       | •       | •       | 0.2mA<br>step |  |  |

| D2  | IG12(2) | 0     | 1         | 1                              | 1       | 1       | 1       | 1       | 0       | 25.2mA        |  |  |

| D1  | IG12(1) | 0     |           |                                |         |         |         |         | 25.4mA  |               |  |  |

| D0  | IG12(0) | 0     | At RGBISE | At RGBISETpin 120kΩ connection |         |         |         |         |         |               |  |  |

#### Adress 08h <G1 G1 Wave Pattern >

| BIT | Name      | Init   |          |        | Fun    | ction  |            |            |  |

|-----|-----------|--------|----------|--------|--------|--------|------------|------------|--|

| DII | Name      | IIII   |          | 0      |        | 1      |            |            |  |

| D7  | -         | -      |          | -      |        | -      |            |            |  |

| D6  | -         | -      |          | -      |        |        | -          |            |  |

| D5  | -         | -      |          | -      |        |        | -          |            |  |

| D4  | -         | -      |          | -      |        |        | -          |            |  |

| DO  |           |        | PG1(3)   | PG1(2) | PG1(1) | PG1(0) | Wave       |            |  |

| D3  | PG1(3)    | 0      | 0        | 0      | 0      | 0      | Pattern 1  |            |  |

|     |           |        | 0        | 0      | 0      | 1      | Pattern 2  |            |  |

| D2  | PG1(2)    | 1      | 0        | 0      | 1      | 0      | Pattern 3  |            |  |

|     |           |        | •        | •      | •      | •      | •          |            |  |

|     |           |        | •        | •      | •      | •      | -          |            |  |

| D1  | PG1(1)    | 1      | •        | •      | •      | •      | -          |            |  |

|     |           |        | 1        | 1      | 0      | 1      | Pattern 14 |            |  |

| DO  | D0 PG1(0) | PC1(0) | PG1(0) 1 | 1      | 1      | 1      | 0          | Pattern 15 |  |

| 50  |           | 1      | 1        | 1      | 1      | 1      | Pattern 16 |            |  |

#### Adress 09h <B1 current1setup >

| BIT | Name    | Init  |                                |         | nction  | ion     |         |         |         |               |  |  |

|-----|---------|-------|--------------------------------|---------|---------|---------|---------|---------|---------|---------------|--|--|

| ЫТ  | Maine   | 11111 |                                |         | 0       |         |         | 1       |         |               |  |  |

| D7  | -       | -     |                                |         | -       |         |         |         | -       |               |  |  |

| D6  | IB11(6) | 0     | IB11(6)                        | IB11(5) | IB11(4) | IB11(3) | IB11(2) | IB11(1) | IB11(0) | Current       |  |  |

| D5  | IB11(5) | 0     | 0                              | 0       | 0       | 0       | 0       | 0       | 0       | 0             |  |  |

| D4  | IB11(4) | 0     | 0                              | 0       | 0       | 0       | 0       | 0       | 1       | 0.2mA         |  |  |

| D3  | IB11(3) | 0     |                                |         |         | •       | •       | •       |         | 0.2mA<br>step |  |  |

| D2  | IB11(2) | 0     | 1                              | 1       | 1       | 1       | 1       | 1       | 0       | 25.2mA        |  |  |

| D1  | IB11(1) | 0     | 1                              | 1       | 1       | 1       | 1       | 1       | 1       | 25.4mA        |  |  |

| D0  | IB11(0) | 0     | At RGBISETpin 120kΩ connection |         |         |         |         |         |         |               |  |  |

#### Adress 0Ah <B1 current2setup >

| BIT | Name    | Init |                                |         |         | iction  | วท      |         |         |               |  |

|-----|---------|------|--------------------------------|---------|---------|---------|---------|---------|---------|---------------|--|

| DII | Name    | IIII |                                | (       | )       |         | 1       |         |         |               |  |

| D7  | -       | -    |                                |         | -       |         |         |         | -       |               |  |

| D6  | IB12(6) | 0    | IB12(6)                        | IB12(5) | IB12(4) | IB12(3) | IB12(2) | IB12(1) | IB12(0) | Current       |  |

| D5  | IB12(5) | 0    | 0                              | 0       | 0       | 0       | 0       | 0       | 0       | 0             |  |

| D4  | IB12(4) | 0    | 0                              | 0       | 0       | 0       | 0       | 0       | 1       | 0.2mA         |  |

| D3  | IB12(3) | 0    |                                |         |         |         |         | •       | •       | 0.2mA<br>step |  |

| D2  | IB12(2) | 0    | 1                              | 1       | 1       | 1       | 1       | 1       | 0       | 25.2mA        |  |

| D1  | IB12(1) | 0    | 1                              | 1       | 1       | 1       | 1       | 1       | 1       | 25.4mA        |  |

| D0  | IB12(0) | 0    | At RGBISETpin 120kΩ connection |         |         |         |         |         |         |               |  |

Adress 0Bh <B1 Wave Pattern >

| BIT | Name     | Init  |        |        | Fur    | nction |           |  |  |

|-----|----------|-------|--------|--------|--------|--------|-----------|--|--|

| DIT | Inallie  | 11111 |        | 0      |        | 1      |           |  |  |

| D7  | -        | -     |        | -      |        | -      |           |  |  |

| D6  | -        | -     |        | -      |        |        | -         |  |  |

| D5  | -        | -     |        | -      |        |        | -         |  |  |

| D4  | -        | -     |        | -      |        |        | -         |  |  |

| D3  | PB1(3)   | 0     | PB1(3) | PB1(2) | PB1(1) | PB1(0) | Wave      |  |  |

| 50  | 1 01(0)  | 0     | 0      | 0      | 0      | 0      | Pattern1  |  |  |

|     |          |       | 0      | 0      | 0      | 1      | Pattern2  |  |  |

| D2  | PB1(2)   | 1     | 0      | 0      | 1      | 0      | Pattern3  |  |  |

|     |          |       | •      | •      | •      | •      |           |  |  |

|     |          |       | •      | •      | •      | •      |           |  |  |

| D1  | PB1(1)   | 1     | •      | •      | •      | •      |           |  |  |

|     |          |       | 1      | 1      | 0      | 1      | Pattern14 |  |  |

| Do  | PB1(0) 1 |       | 1      | 1      | 1      | 0      | Pattern15 |  |  |

| D0  |          |       | 1      | 1      | 1      | 1      | Pattern16 |  |  |

Adress 0Ch <RGB2 time >

| BIT | Name        | Init  |               |          | Function                                       |                                          |

|-----|-------------|-------|---------------|----------|------------------------------------------------|------------------------------------------|

| ЫТ  | Iname       | 11111 |               | 0        |                                                | 1                                        |

|     |             |       | SFRGB2(1      | )        | SFRGB2(0)                                      | Slope Down transition                    |

| D7  | SFRGB2(1)   | 0     | 0             |          | 0                                              | 0                                        |

|     |             |       | 0             |          | 1                                              | Wave form cycle / 16                     |

| -   |             |       | 1             |          | 0                                              | Wave form cycle / 8                      |

|     |             |       | 1             |          | 1                                              | Wave form cycle / 4                      |

| D6  | SFRGB2(0)   | 0     | not included. | C C      | ntrol, and the reactine start to a slope e     | on time of the analog section is nd.     |

|     |             |       | SRRGB2(1      | )        | SRRGB2(0)                                      | Slope up transition                      |

| D5  | SRRGB2(1)   | 0     | 0             | ,        | 0                                              | 0                                        |

| 20  |             | Ũ     | 0             |          | 1                                              | Wave form cycle / 16                     |

|     |             |       | 1             |          | 0                                              | Wave form cycle / 8                      |

|     |             |       | 1             |          | 1                                              | Wave form cycle / 4                      |

| D4  | SRRGB2(0)   | 0     | included.     | C C      | bl, and the reaction<br>le start to a slope en | time of the analog section is not<br>nd. |

| D3  | -           | -     |               | -        |                                                | -                                        |

|     |             | _     | TRGB2(2)      | TRGB2(1) | TRGB2(0)                                       | Wave form cycle                          |

| D2  | TRGB2(2)    | 0     | 0             | 0        | 0                                              | 0.131 s                                  |

|     |             |       | 0             | 0        | 1                                              | 0.52 s                                   |

|     |             |       | 0             | 1        | 0                                              | 1.05 s                                   |

| D1  | TRGB2(1)    | 0     | 0             | 1        | 1                                              | 2.10 s                                   |

|     |             |       | 1             | 0        | 0                                              | 4.19 s                                   |

|     |             |       | 1             | 0        | 1                                              | 8.39 s                                   |

| D0  | D0 TRGB2(0) | 0     |               |          | 0                                              | 12.6 s                                   |

|     | (-)         |       | 1             | 1        | 1                                              | 16.8 s                                   |

Setting time is counted based on the frequency of OSC. The above-mentioned value is a value at the time of Typ (1MHz). When operating by the external clock, input frequency is a value at the time of Typ (250kHz)

Adress 0Dh <R2 current 1setup>

| ріт | Name    | Init |                                |         |         | Fun     | ction   |         |         |               |  |  |

|-----|---------|------|--------------------------------|---------|---------|---------|---------|---------|---------|---------------|--|--|

| BIT | Name    | IIII |                                | (       | )       |         | 1       |         |         |               |  |  |

| D7  | -       | -    |                                |         | -       |         |         |         | -       |               |  |  |

| D6  | IR21(6) | 0    | IR21(6)                        | IR21(5) | IR21(4) | IR21(3) | IR21(2) | IR21(1) | IR21(0) | Current       |  |  |

| D5  | IR21(5) | 0    | 0                              | 0       | 0       | 0       | 0       | 0       | 0       | 0             |  |  |

| D4  | IR21(4) | 0    | 0                              | 0       | 0       | 0       | 0       | 0       | 1       | 0.2mA         |  |  |

| D3  | IR21(3) | 0    |                                |         | •       | •       |         | •       |         | 0.2mA<br>step |  |  |

| D2  | IR21(2) | 0    | 1                              | 1       | 1       | 1       | 1       | 1       | 0       | 25.2mA        |  |  |

| D1  | IR21(1) | 0    | 1                              | 1       | 1       | 1       | 1       | 1       | 1       | 25.4mA        |  |  |

| D0  | IR21(0) | 0    | At RGBISETpin 120kΩ connection |         |         |         |         |         |         |               |  |  |

#### Adress 0Eh <R2 current 2setup>

| BIT | Nama    | Init  | Function                       |         |         |         |         |         |         |         |  |  |

|-----|---------|-------|--------------------------------|---------|---------|---------|---------|---------|---------|---------|--|--|

| DII | Name    | ITIIL |                                | (       | )       |         |         | 1       |         |         |  |  |

| D7  | -       | -     |                                |         | -       |         |         |         | -       |         |  |  |

| D6  | IR22(6) | 0     | IR22(6)                        | IR22(5) | IR22(4) | IR22(3) | IR22(2) | IR22(1) | IR22(0) | Current |  |  |

| D5  | IR22(5) | 0     | 0                              | 0       | 0       | 0       | 0       | 0       | 0       | 0       |  |  |

| D4  | IR22(4) | 0     | 0                              | 0       | 0       | 0       | 0       | 0       | 1       | 0.2mA   |  |  |

| D3  | IR22(3) | 0     | •                              | •       | •       | •       | •       | •       | •       | 0.2mA   |  |  |

| 50  | ,       | 0     | •                              | •       | •       | •       | •       | •       | •       | step    |  |  |

| D2  | IR22(2) | 0     | 1                              | 1       | 1       | 1       | 1       | 1       | 0       | 25.2mA  |  |  |

| D1  | IR22(1) | 0     | 1                              | 1       | 1       | 1       | 1       | 1       | 1       | 25.4mA  |  |  |

| D0  | IR22(0) | 0     | At RGBISETpin 120kΩ connection |         |         |         |         |         |         |         |  |  |

#### Adress 0Fh <R2 Wave Pattern setup>

| BIT | Name      | Init  |        |        | Fun    | iction |            |  |  |

|-----|-----------|-------|--------|--------|--------|--------|------------|--|--|

| DII | Name      | ITIIL |        | 0      |        |        | 1          |  |  |

| D7  | -         | -     |        | -      |        | -      |            |  |  |

| D6  | -         | -     |        | -      |        |        | -          |  |  |

| D5  | -         | -     |        | -      |        |        | -          |  |  |

| D4  | -         | -     |        | -      |        |        | -          |  |  |

| D3  |           | 0     | PR2(3) | PR2(2) | PR2(1) | PR2(0) | Wave       |  |  |

| 00  | PR2(3)    | 0     | 0      | 0      | 0      | 0      | Pattern 1  |  |  |

|     |           |       | 0      | 0      | 0      | 1      | Pattern 2  |  |  |

| D2  | PR2(2)    | 1     | 0      | 0      | 1      | 0      | Pattern 3  |  |  |

|     |           |       | •      | •      |        | •      |            |  |  |

|     |           |       | •      | •      |        | •      |            |  |  |

| D1  | PR2(1)    | 1     | •      | •      | •      | •      | •          |  |  |

|     |           |       | 1      | 1      | 0      | 1      | Pattern 14 |  |  |

| D0  |           | 4     | 1      | 1      | 1      | 0      | Pattern 15 |  |  |

| 00  | D0 PR2(0) |       | 1      | 1      | 1      | 1      | Pattern 16 |  |  |

#### Adress 10h <G2 current 1setup>

| DIT | Neme    | الما | Function  |                                |         |         |         |         |         |               |  |  |

|-----|---------|------|-----------|--------------------------------|---------|---------|---------|---------|---------|---------------|--|--|

| BIT | Name    | Init |           | 0                              |         |         |         |         | 1       |               |  |  |

| D7  | -       | -    |           | -                              |         |         |         |         | -       |               |  |  |

| D6  | IG21(6) | 0    | IG21(6)   | IG21(5)                        | IG21(4) | IG21(3) | IG21(2) | IG21(1) | IG21(0) | Current       |  |  |

| D5  | IG21(5) | 0    | 0         | 0                              | 0       | 0       | 0       | 0       | 0       | 0             |  |  |

| D4  | IG21(4) | 0    | 0         | 0                              | 0       | 0       | 0       | 0       | 1       | 0.2mA         |  |  |

| D3  | IG21(3) | 0    |           |                                |         |         | •       | •       |         | 0.2mA<br>step |  |  |

| D2  | IG21(2) | 0    | 1         | 1                              | 1       | 1       | 1       | 1       | 0       | 25.2mA        |  |  |

| D1  | IG21(1) | 0    | 1         | 1                              | 1       | 1       | 1       | 1       | 1       | 25.4mA        |  |  |

| D0  | IG21(0) | 0    | At RGBISE | At RGBISETpin 120kΩ connection |         |         |         |         |         |               |  |  |

Adress 11h <G2 current 2setup>

| ріт | Neme    | ا الم | Function  |                                |         |         |         |         |         |               |  |

|-----|---------|-------|-----------|--------------------------------|---------|---------|---------|---------|---------|---------------|--|

| BIT | Name    | Init  |           | 0                              |         |         |         | 1       |         |               |  |

| D7  | -       | -     |           |                                |         |         | -       |         |         |               |  |

| D6  | IG22(6) | 0     | IG22(6)   | IG22(5)                        | IG22(4) | IG22(3) | IG22(2) | IG22(1) | IG22(0) | Current       |  |

| D5  | IG22(5) | 0     | 0         | 0                              | 0       | 0       | 0       | 0       | 0       | 0             |  |

| D4  | IG22(4) | 0     | 0         | 0                              | 0       | 0       | 0       | 0       | 1       | 0.2mA         |  |

| D3  | IG22(3) | 0     | 11 :      |                                |         |         |         |         |         | 0.2mA<br>step |  |

| D2  | IG22(2) | 0     | 1         | 1                              | 1       | 1       | 1       | 1       | 0       | 25.2mA        |  |

| D1  | IG22(1) | 0     | 1         | 1                              | 1       | 1       | 1       | 1       | 1       | 25.4mA        |  |

| D0  | IG22(0) | 0     | At RGBISE | At RGBISETpin 120kΩ connection |         |         |         |         |         |               |  |

#### Adress 12h <G2 Wave Pattern setup >

| BIT | Name   | Init  | Function |        |        |        |            |           |   |

|-----|--------|-------|----------|--------|--------|--------|------------|-----------|---|

| DII | Name   | ITIIL |          | 0      |        | 1      |            |           |   |

| D7  | -      | -     |          | -      |        |        | -          |           |   |

| D6  | -      | -     |          | -      |        |        | -          |           |   |

| D5  | -      | -     |          | -      |        |        | -          |           |   |

| D4  | -      | -     |          | -      |        |        | -          |           |   |

| DO  |        |       |          | PG2(3) | PG2(2) | PG2(1) | PG2(0)     | Wave      |   |

| D3  | PG2(3) | 0     | 0        | 0      | 0      | 0      | Pattern 1  |           |   |

|     |        | 1     | 1        | 0      | 0      | 0      | 1          | Pattern 2 |   |

| D2  | PG2(2) |       |          | 1      | 1      | 1      | 0          | 0         | 1 |

|     | ( )    |       | •        | •      | •      | •      | •          |           |   |

|     |        |       | •        | •      | •      | •      | •          |           |   |

| D1  | PG2(1) | 1     | •        | •      | •      | •      | •          |           |   |

|     |        |       | 1        | 1      | 0      | 1      | Pattern 14 |           |   |

| D0  | PG2(0) | 1     | 1        | 1      | 1      | 0      | Pattern 15 |           |   |

| 50  | FG2(0) | 1     | 1        | 1      | 1      | 1      | Pattern 16 |           |   |

#### Adress 13h <B2 current 1setup>

| BIT | Name    | Init | Function  |                                |         |         |         |         |         |         |  |

|-----|---------|------|-----------|--------------------------------|---------|---------|---------|---------|---------|---------|--|

| DII | Name    | mm   |           | 0                              |         |         |         | 1       |         |         |  |

| D7  | -       | -    |           |                                | -       |         |         |         | -       |         |  |

| D6  | IB21(6) | 0    | IB21(6)   | IB21(5)                        | IB21(4) | IB21(3) | IB21(2) | IB21(1) | IB21(0) | Current |  |

| D5  | IB21(5) | 0    | 0         | 0                              | 0       | 0       | 0       | 0       | 0       | 0       |  |

| D4  | IB21(4) | 0    | 0         | 0                              | 0       | 0       | 0       | 0       | 1       | 0.2mA   |  |

| D3  | IB21(3) | 0    | •         | •                              | •       | •       | •       | •       | •       | 0.2mA   |  |

| D0  | . ,     | 0    | •         | •                              | •       | •       | •       | •       | •       | step    |  |

| D2  | IB21(2) | 0    | 1         | 1                              | 1       | 1       | 1       | 1       | 0       | 25.2mA  |  |

| D1  | IB21(1) | 0    | 1         | 1                              | 1       | 1       | 1       | 1       | 1       | 25.4mA  |  |

| D0  | IB21(0) | 0    | At RGBISE | At RGBISETpin 120kΩ connection |         |         |         |         |         |         |  |

#### Adress 14h <B2 current 2setup>

| ріт | Name    | Init  | Function  |                                |         |         |         |         |         |               |  |  |

|-----|---------|-------|-----------|--------------------------------|---------|---------|---------|---------|---------|---------------|--|--|

| BIT | Name    | IIIIL |           | 0                              |         |         |         |         | 1       |               |  |  |

| D7  | -       | -     |           |                                | -       |         |         | -       |         |               |  |  |

| D6  | IB22(6) | 0     | IB22(6)   | IB22(5)                        | IB22(4) | IB22(3) | IB22(2) | IB22(1) | IB22(0) | Current       |  |  |

| D5  | IB22(5) | 0     | 0         | 0                              | 0       | 0       | 0       | 0       | 0       | 0             |  |  |

| D4  | IB22(4) | 0     | 0         | 0                              | 0       | 0       | 0       | 0       | 1       | 0.2mA         |  |  |

| D3  | IB22(3) | 0     |           |                                |         |         |         |         |         | 0.2mA<br>step |  |  |

| D2  | IB22(2) | 0     | 1         | 1                              | 1       | 1       | 1       | 1       | 0       | 25.2mA        |  |  |

| D1  | IB22(1) | 0     | 1         | 1                              | 1       | 1       | 1       | 1       | 1       | 25.4mA        |  |  |

| D0  | IB22(0) | 0     | At RGBISE | At RGBISETpin 120kΩ connection |         |         |         |         |         |               |  |  |

Adress 15h <B2 Wave Pattern setup >

| DIT | Name          | Init     |   | Function |   |        |            |        |           |      |   |   |   |   |

|-----|---------------|----------|---|----------|---|--------|------------|--------|-----------|------|---|---|---|---|

| BIT | BII Naille II |          |   | 0        |   | 1      |            |        |           |      |   |   |   |   |

| D7  | -             | -        |   | -        |   |        | -          |        |           |      |   |   |   |   |

| D6  | -             | -        |   | -        |   |        | -          |        |           |      |   |   |   |   |

| D5  | -             | -        |   | -        |   |        | -          |        |           |      |   |   |   |   |

| D4  | -             | -        |   | -        |   |        | -          |        |           |      |   |   |   |   |

| DO  |               |          |   |          |   | PB2(3) | PB2(2)     | PB2(1) | PB2(0)    | Wave |   |   |   |   |

| D3  | PB2(3)        | PB2(3) 0 | 0 | 0        | 0 | 0      | Pattern 1  |        |           |      |   |   |   |   |

|     |               | 1        | 1 | 1        | 0 | 0      | 0          | 1      | Pattern 2 |      |   |   |   |   |

| D2  | PB2(2)        |          |   |          | 1 | 1      | 1          | 1      | 1         | 1    | 1 | 1 | 0 | 0 |

|     | ( )           |          | • | •        | • | •      | •          |        |           |      |   |   |   |   |

|     |               |          | • | •        | • | •      |            |        |           |      |   |   |   |   |

| D1  | PB2(1)        | 1        | • | •        | • | •      |            |        |           |      |   |   |   |   |

|     |               |          | 1 | 1        | 0 | 1      | Pattern 14 |        |           |      |   |   |   |   |

| D0  | PB2(0)        | - 1      | 1 | 1        | 1 | 0      | Pattern 15 |        |           |      |   |   |   |   |

| 00  |               | PB2(0) 1 | 1 | 1        | 1 | 1      | Pattern 16 |        |           |      |   |   |   |   |

#### RGB LED Driver Operation Description

- Two drivers "RGB1 (R1LED, G1LED, B1LED)" and "RGB2 (R2LED, G2LED, B2LED)" are mounted.

- A slope function is incorporated to control drivers independently.

- Refer to RGB Waveform Setting for more information about output waveform setting.

- The LED current can be set via a resistance value (RISET) to be connected to the RGBISET terminal. The maximum current value can be derived from the following expression:

ILEDmax [A] =  $3.048 / \text{RISET} [k\Omega] (Typ)$ However, this setting must be made so that the maximum current value can be less than or equal to 30.48mA. In addition, the RGBISET terminal has an overcurrent protection circuit to prevent the excessive LED current from flowing for low impedance to the ground.

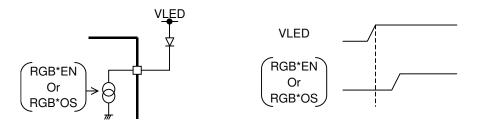

- Note that the setting voltage shall be higher than or equal to a saturation voltage (0.2V) in the constant current circuit. When LED Vf is large, the LED destination shall be connected to another step-up circuit.

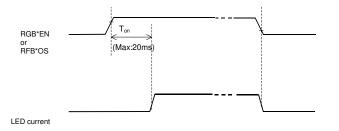

- The LED destination is fixed before on (RGB\*EN=Hi or RGB\*OS=Hi).

#### The synchronism of RGB1/RGB2

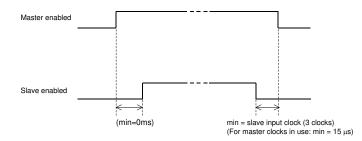

The period of RGB1 and RGB2 and start, stop timing can be set up independently. When synchronizes RGB1 and RGB2, You must start an internal counter at the same time under the state of resetting. (Internal Counter are prepared for each of RGB1 and RGB2, so You must reset both.)

<How to reset internal Counter> Inside Counter can be reset by carrying out one of following actions.

- Reset by hard reset (RSTB\_IL). (RGB1, RGB2 is reset together.)

- Reset by soft reset. (RGB1, RGB2 is reset together.)

- It is written register of the current setup (I1 I2), the slope setup, the period setup and the pattern setup. Internal Counter of RGB1 is reset when it is written between Address=0Bh from 02h. Internal Counter of RGB2 is reset when it is written between Address=15h from 0Ch. Counter is reset as to overwriting the same value.

Note)

Internal Counter isn't reset if write RGB1EN =L and RGB2EN =L. (Address=01h). When it write RGB1EN=L (RGB2EN=L), inside Counter is held, and IC will operate from the held state at next restart.

#### RGB Waveform Setting

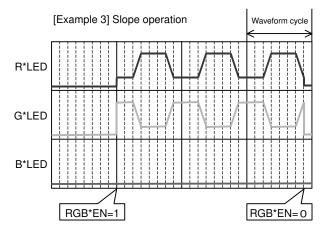

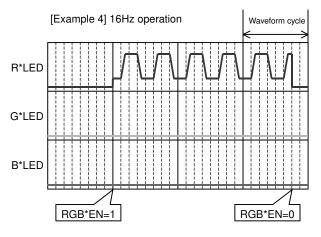

Various kinds of RGB control can be implemented by designating waveform cycles, waveform patterns, current settings 1, 2 and rising/falling slope times.

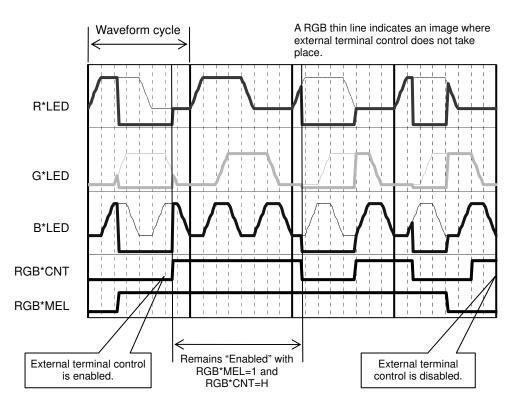

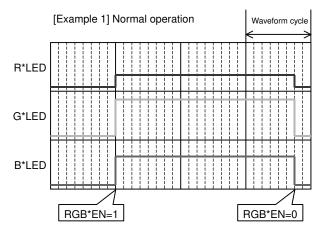

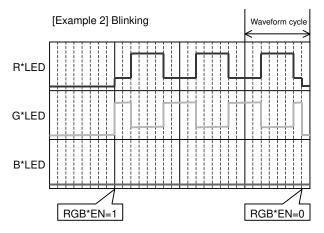

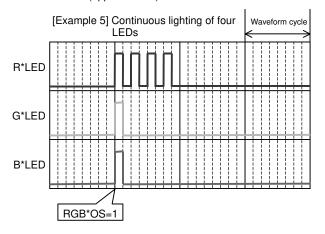

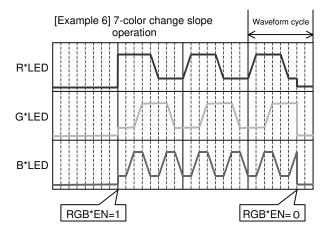

To activate a RGB waveform, a continuous operation via RGB\*EN or a single-shot operation via RGB\*OS can be selected. In addition, when control via the external terminal RGB\*CNT is enabled via RGB\*MEL, the corresponding LED can be lit in synchronization with the external signal.

- 1. Waveform cycle

- A single cycle time is set for a waveform pattern.

- This setting can be made independently for RGB1 and RGB2.

- 2. Waveform pattern

- A pattern in a waveform cycle is set.

- · Sixteen types of waveform patterns can be set in units of waveform patterns.

- For concrete waveform patterns, refer to the timing diagram shown on the next page.

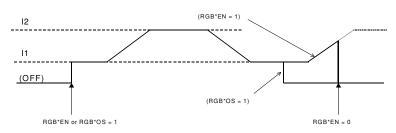

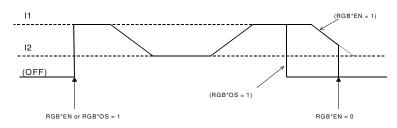

- 3. Current settings 1 and 2 (I1, I2)

- Two currents in a waveform pattern are set.

- When the maximum current value is 25.4mA, it is possible to set the current ranging from 0 to 25.4mA with an increment of 0.2mA (128 steps).

- The polarity of a waveform is determined by the greater-than/ less-than relationship in the current setting.

- This setting can be made in units of terminals.

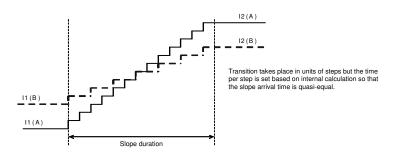

- 4. Rising/falling slope time

- A current change time during switching between current settings 1 and 2 is set.

- A time per step (0.2mA) is calculated based on a difference between the currents selected in current settings 1, 2 and a setting slope time.

- For this reason, a time per step (0.2mA) is short when a difference between setting currents I1 and I2 is large. In contrast, it is long when a difference between setting currents I1 and I2 is small.

- Regardless of current settings 1 and 2, a rising slope time applies at current increase and a falling slope time applies at current decrease. For concrete waveform images, refer to the timing diagram shown on the next page.

External terminal synchronization control

When control via the external terminal RGB\*CNT is enabled via RGB\*MEL, lighting is enabled if the input external signal goes "H." In contrast, it is disabled if the external input signal goes "L." In this way, synchronization with the external signal signal is enabled so that LED can be blinked in conjunction with a ringing tone (a melody signaling a ringtone).

|                 |               |           |         |          | Wave          | cycle       |          |    |                   |

|-----------------|---------------|-----------|---------|----------|---------------|-------------|----------|----|-------------------|

| -               | ster data     |           |         |          |               |             |          |    |                   |

| Wave pattern 1  | (00h)         | 1         |         |          |               | 12          |          |    |                   |

| Wave pattern2   | (01h)         | l         | 1       |          |               | l           | 2        |    |                   |

| Wave pattern 3  | (02h)         |           | 11      |          |               |             | 12       |    |                   |

| Wave pattern 4  | (03h)         |           | l       | 1        |               |             | 12       | 2  |                   |

| Wave pattern 5  | (04h)         |           |         | 11       |               |             |          | 12 |                   |

| Wave pattern 6  | (05h)         |           |         | l        | 1             |             |          |    | 2                 |

| Wave pattern 7  | (06h)         |           |         |          | 1             |             |          |    | 12                |

| Wave pattern 8  | (07h)         |           |         |          | 11            |             |          |    |                   |

| Wave pattern 9  | (08h)         |           | 1       | l        | 2             |             | <u> </u> | 1  |                   |

| Wave pattern 10 | (09h)         |           | I       | 1        |               |             | 2        |    | 1                 |

| Wave pattern 11 | (0Ah)         | 1         | l       | 2        |               |             |          | 2  | 1                 |

| Wave pattern 12 | (0Bh)         | I         | 1       | I        | 2             | I           | 1        |    | 12                |

| Wave pattern 13 | (0Ch)         | 1         |         | <u> </u> | 2             |             |          | 1  |                   |

| Wave pattern 14 | (0Dh)         | I         | 1       |          | 12            | 2           |          |    | 1                 |

| Wave pattern 15 | (0Eh)         |           | 11      |          |               | l           | 2        |    | 1                 |

| Wave pattern 16 | (0Fh)         | 1         | 12      | 1        | 12            | 1           | 12       | 1  | 12                |

| (ex             | ) The imag    | e of curr | ent cha | nge of V |               |             |          |    |                   |

| C               | Current 2(12) |           |         |          | Slope D       | own tra     | nsition  |    |                   |